#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 8KB (2.75K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 1.5K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 9x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

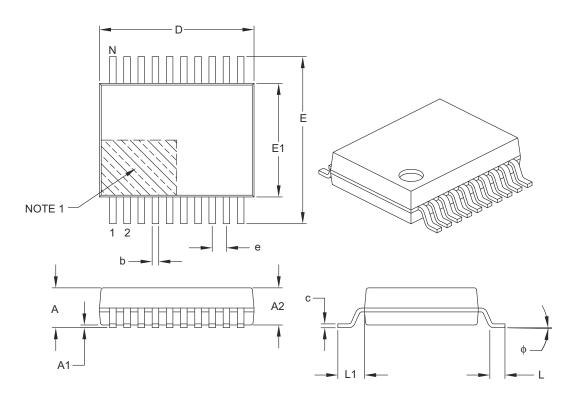

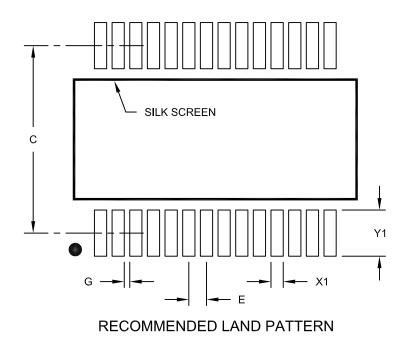

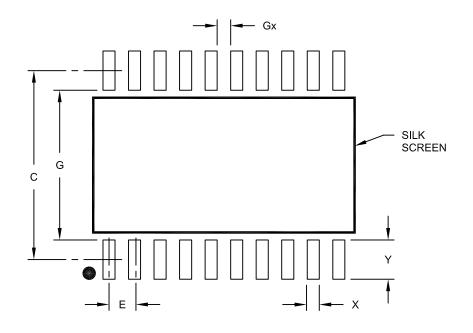

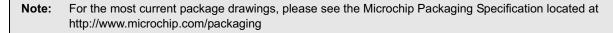

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 28-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08ka102-e-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                              | Pin I         | Number                        |               |     |                 |                                                              |

|----------|------------------------------|---------------|-------------------------------|---------------|-----|-----------------|--------------------------------------------------------------|

| Function | 20-Pin<br>PDIP/SSOP/<br>SOIC | 20-Pin<br>QFN | 28-Pin<br>SPDIP/<br>SSOP/SOIC | 28-Pin<br>QFN | I/O | Input<br>Buffer | Description                                                  |

| T1CK     | 10                           | 7             | 12                            | 9             | I   | ST              | Timer1 Clock                                                 |

| T2CK     | 18                           | 15            | 26                            | 23            | I   | ST              | Timer2 Clock                                                 |

| T3CK     | 18                           | 15            | 26                            | 23            | I   | ST              | Timer3 Clock                                                 |

| U1CTS    | 12                           | 9             | 17                            | 14            | I   | ST              | UART1 Clear to Send Input                                    |

| U1RTS    | 13                           | 10            | 18                            | 15            | 0   | _               | UART1 Request to Send Output                                 |

| U1RX     | 6                            | 3             | 6                             | 3             | I   | ST              | UART1 Receive                                                |

| U1TX     | 11                           | 8             | 16                            | 13            | 0   |                 | UART1 Transmit Output                                        |

| Vdd      | 20                           | 17            | 13, 28                        | 10, 25        | Р   | —               | Positive Supply for Peripheral Digital Logic and<br>I/O Pins |

| Vpp      | 1                            | 18            | 1                             | 26            | Р   |                 | Programming Mode Entry Voltage                               |

| VREF-    | 3                            | 20            | 3                             | 28            | I   | ANA             | A/D and Comparator Reference Voltage (low)<br>Input          |

| VREF+    | 2                            | 19            | 2                             | 27            | I   | ANA             | A/D and Comparator Reference Voltage (high)<br>Input         |

| Vss      | 19                           | 16            | 8, 27                         | 5, 24         | Р   | —               | Ground Reference for Logic and I/O Pin                       |

## TABLE 1-2: PIC24F16KA102 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

**Legend:** ST = Schmitt Trigger input buffer, ANA = Analog level input/output,  $I^2C^{TM} = I^2C/SMB$ us input buffer

Note 1: Alternative multiplexing when the I2C1SEL Configuration bit is cleared.

| Register(s) Name | Description                                    |

|------------------|------------------------------------------------|

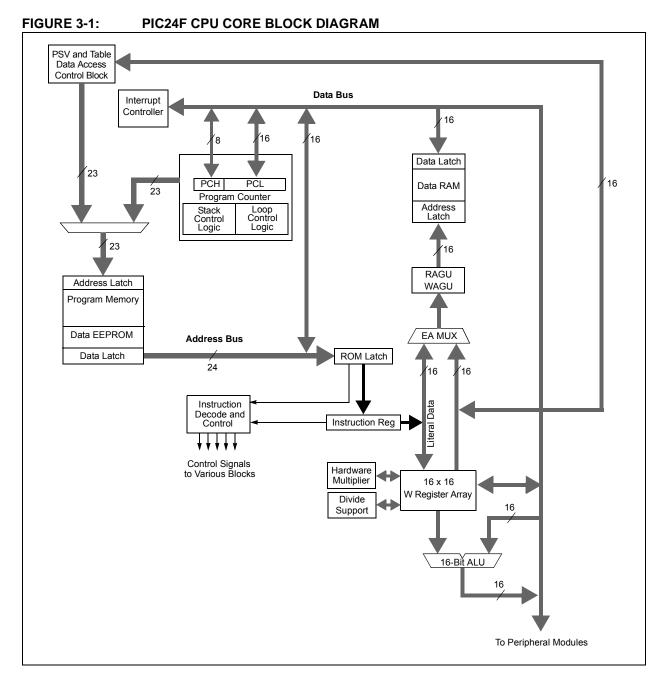

| W0 through W15   | Working Register Array                         |

| PC               | 23-Bit Program Counter                         |

| SR               | ALU STATUS Register                            |

| SPLIM            | Stack Pointer Limit Value Register             |

| TBLPAG           | Table Memory Page Address Register             |

| PSVPAG           | Program Space Visibility Page Address Register |

| RCOUNT           | Repeat Loop Counter Register                   |

| CORCON           | CPU Control Register                           |

| IADLL        | <b>-</b> -J. |        |        |        |        |        |        |        |             |               |           |             |                |              |             |       |       |

|--------------|--------------|--------|--------|--------|--------|--------|--------|--------|-------------|---------------|-----------|-------------|----------------|--------------|-------------|-------|-------|

| File<br>Name | Addr         | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8       | Bit 7         | Bit 6     | Bit 5       | Bit 4          | Bit 3        | Bit 2       | Bit 1 | Bit 0 |

| WREG0        | 0000         |        |        |        |        |        |        |        | Working I   | Register 0    |           |             |                |              |             |       |       |

| WREG1        | 0002         |        |        |        |        |        |        |        | Working I   | Register 1    |           |             |                |              |             |       |       |

| WREG2        | 0004         |        |        |        |        |        |        |        | Working I   | Register 2    |           |             |                |              |             |       |       |

| WREG3        | 0006         |        |        |        |        |        |        |        | Working I   | Register 3    |           |             |                |              |             |       |       |

| WREG4        | 0008         |        |        |        |        |        |        |        | Working I   | Register 4    |           |             |                |              |             |       |       |

| WREG5        | 000A         |        |        |        |        |        |        |        | Working I   | Register 5    |           |             |                |              |             |       |       |

| WREG6        | 000C         |        |        |        |        |        |        |        | Working I   | Register 6    |           |             |                |              |             |       |       |

| WREG7        | 000E         |        |        |        |        |        |        |        | Working I   | Register 7    |           |             |                |              |             |       |       |

| WREG8        | 0010         |        |        |        |        |        |        |        | Working I   | Register 8    |           |             |                |              |             |       |       |

| WREG9        | 0012         |        |        |        |        |        |        |        | Working I   | Register 9    |           |             |                |              |             |       |       |

| WREG10       | 0014         |        |        |        |        |        |        |        | Working F   | Register 10   |           |             |                |              |             |       |       |

| WREG11       | 0016         |        |        |        |        |        |        |        | Working F   | Register 11   |           |             |                |              |             |       |       |

| WREG12       | 0018         |        |        |        |        |        |        |        | Working F   | Register 12   |           |             |                |              |             |       |       |

| WREG13       | 001A         |        |        |        |        |        |        |        | Working F   | Register 13   |           |             |                |              |             |       |       |

| WREG14       | 001C         |        |        |        |        |        |        |        | Working F   | Register 14   |           |             |                |              |             |       |       |

| WREG15       | 001E         |        |        |        |        |        |        |        | Working F   | Register 15   |           |             |                |              |             |       |       |

| SPLIM        | 0020         |        |        |        |        |        |        | Stack  | Pointer Lin | nit Value Re  | egister   |             |                |              |             |       |       |

| PCL          | 002E         |        |        |        |        |        |        | Progra | m Counter   | Low Byte R    | egister   |             |                |              |             |       |       |

| PCH          | 0030         | _      | _      | _      | _      | _      | _      | _      | _           |               |           | Progra      | m Counter      | Register Hig | gh Byte     |       |       |

| TBLPAG       | 0032         | _      | _      | _      | _      | _      | _      | _      | _           |               |           | Table M     | lemory Pag     | e Address F  | Register    |       |       |

| PSVPAG       | 0034         | —      | _      | _      | _      | —      | —      | _      | —           |               | F         | Program Spa | ace Visibility | Page Addr    | ess Registe | er    |       |

| RCOUNT       | 0036         |        |        |        |        |        |        | REP    | EAT Loop C  | Counter Reg   | jister    |             |                |              |             |       |       |

| SR           | 0042         | —      | —      | _      | —      | —      | —      |        | DC          | IPL2          | IPL1      | IPL0        | RA             | N            | OV          | Z     | С     |

| CORCON       | 0044         | _      | _      | _      | —      | —      | —      | _      | —           | _             | —         |             | _              | IPL3         | PSV         | —     | —     |

| DISICNT      | 0052         | _      | _      |        |        |        |        |        | Disab       | le Interrupts | Counter R | egister     |                |              |             |       |       |

|              |              |        |        |        |        |        |        |        |             |               |           |             |                |              |             |       |       |

#### TABLE 4-3: **CPU CORE REGISTERS MAP**

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All

xxxx

| IABLE 4      | -15: | A/D RE | GISIER |        |        |        |        |        |          |            |       |       |        |        |        |        |        |            |

|--------------|------|--------|--------|--------|--------|--------|--------|--------|----------|------------|-------|-------|--------|--------|--------|--------|--------|------------|

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8    | Bit 7      | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All Resets |

| ADC1BUF0     | 0300 |        |        |        |        |        |        |        | A/D Data | a Buffer 0 |       |       |        |        |        |        |        | xxxx       |

| ADC1BUF1     | 0302 |        |        |        |        |        |        |        | A/D Data | a Buffer 1 |       |       |        |        |        |        |        | xxxx       |

| ADC1BUF2     | 0304 |        |        |        |        |        |        |        | A/D Data | a Buffer 2 |       |       |        |        |        |        |        | xxxx       |

| ADC1BUF3     | 0306 |        |        |        |        |        |        |        | A/D Data | a Buffer 3 |       |       |        |        |        |        |        | xxxx       |

| ADC1BUF4     | 0308 |        |        |        |        |        |        |        | A/D Data | a Buffer 4 |       |       |        |        |        |        |        | xxxx       |

| ADC1BUF5     | 030A |        |        |        |        |        |        |        | A/D Data | a Buffer 5 |       |       |        |        |        |        |        | xxxx       |

| ADC1BUF6     | 030C |        |        |        |        |        |        |        | A/D Data | a Buffer 6 |       |       |        |        |        |        |        | xxxx       |

| ADC1BUF7     | 030E |        |        |        |        |        |        |        | A/D Data | a Buffer 7 |       |       |        |        |        |        |        | xxxx       |

| ADC1BUF8     | 0310 |        |        |        |        |        |        |        | A/D Data | a Buffer 8 |       |       |        |        |        |        |        | xxxx       |

| ADC1BUF9     | 0312 |        |        |        |        |        |        |        | A/D Data | a Buffer 9 |       |       |        |        |        |        |        | xxxx       |

| ADC1BUFA     | 0314 |        |        |        |        |        |        |        | A/D Data | Buffer 10  |       |       |        |        |        |        |        | xxxx       |

| ADC1BUFB     | 0316 |        |        |        |        |        |        |        | A/D Data | Buffer 11  |       |       |        |        |        |        |        | xxxx       |

| ADC1BUFC     | 0318 |        |        |        |        |        |        |        | A/D Data | Buffer 12  |       |       |        |        |        |        |        | xxxx       |

| ADC1BUFD     |      |        |        |        |        |        |        |        | A/D Data |            |       |       |        |        |        |        |        | xxxx       |

| ADC1BUFE     | 031C |        |        |        |        |        |        |        | A/D Data | Buffer 14  |       |       |        |        |        |        |        | xxxx       |

| ADC1BUFF     | 031E |        |        | 1      |        |        |        | 1      | A/D Data |            |       |       |        |        | 1      |        | 1      | xxxx       |

| AD1CON1      | 0320 | ADON   |        | ADSIDL | _      | _      | _      | FORM1  | FORM0    | SSRC2      | SSRC1 | SSRC0 | —      | —      | ASAM   | SAMP   | DONE   | 0000       |

| AD1CON2      | 0322 | VCFG2  | VCFG1  | VCFG0  | OFFCAL | —      | CSCNA  | —      | —        | BUFS       | —     | SMPI3 | SMPI2  | SMPI1  | SMPI0  | BUFM   | ALTS   | 0000       |

| AD1CON3      | 0324 | ADRC   | _      | —      | SAMC4  | SAMC3  | SAMC2  | SAMC1  | SAMC0    | —          | _     | ADCS5 | ADCS4  | ADCS3  | ADCS2  | ADCS1  | ADCS0  | 0000       |

| AD1CHS       | 0328 | CH0NB  | _      | —      | —      | CH0SB3 | CH0SB2 | CH0SB1 | CH0SB0   | CH0NA      | _     | —     | CH0SA4 | CH0SA3 | CH0SA2 | CH0SA1 | CH0SA0 | 0000       |

| AD1PCFG      | 032C | —      | _      | —      | PCFG12 | PCFG11 | PCFG10 | _      | —        | _          | _     | PCFG5 | PCFG4  | PCFG3  | PCFG2  | PCFG1  | PCFG0  | 0000       |

| AD1CSSL      | 0330 | —      | _      |        | CSSL12 | CSSL11 | CSSL10 |        | —        |            | _     | CSSL5 | CSSL4  | CSSL3  | CSSL2  | CSSL1  | CSSL0  | 0000       |

#### TABLE 4-15: A/D REGISTER MAP

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-16: CTMU REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10   | Bit 9   | Bit 8  | Bit 7   | Bit 6    | Bit 5    | Bit 4   | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|------|--------|--------|----------|--------|--------|----------|---------|--------|---------|----------|----------|---------|----------|----------|----------|----------|---------------|

| CTMUCON      | 033C | CTMUEN | —      | CTMUSIDL | TGEN   | EDGEN  | EDGSEQEN | IDISSEN | CTTRIG | EDG2POL | EDG2SEL1 | EDG2SEL0 | EDG1POL | EDG1SEL1 | EDG1SEL0 | EDG2STAT | EDG1STAT | 0000          |

| CTMUICON     | 033E | ITRIM5 | ITRIM4 | ITRIM3   | ITRIM2 | ITRIM1 | ITRIM0   | IRNG1   | IRNG0  |         |          |          |         | —        | _        | _        | —        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-20: CLOCK CONTROL REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6 | Bit 5  | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|--------|---------|-------|--------|-------|--------|--------|--------|--------|---------------|

| RCON      | 0740 | TRAPR  | IOPUWR | SBOREN | _      | _      | DPSLP  | _      | PMSLP  | EXTR    | SWR   | SWDTEN | WDTO  | SLEEP  | IDLE   | BOR    | POR    | (Note 1)      |

| OSCCON    | 0742 | -      | COSC2  | COSC1  | COSC0  | _      | NOSC2  | NOSC1  | NOSC0  | CLKLOCK | _     | LOCK   | —     | CF     | _      | SOSCEN | OSWEN  | (Note 2)      |

| CLKDIV    | 0744 | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | RCDIV2 | RCDIV1 | RCDIV0 | _       | _     | _      | _     | _      | _      | —      | —      | 3140          |

| OSCTUN    | 0748 | —      |        | _      |        | _      | _      |        | —      | _       | -     | TUN5   | TUN4  | TUN3   | TUN2   | TUN1   | TUN0   | 0000          |

| REFOCON   | 074E | ROEN   |        | ROSSLP | ROSEL  | RODIV3 | RODIV2 | RODIV1 | RODIV0 | _       | _     | _      | _     | _      | _      | —      | _      | 0000          |

| HLVDCON   | 0756 | HLVDEN | _      | HLSIDL | _      | _      | _      | _      | _      | VDIR    | BGVST | IRVST  | _     | HLVDL3 | HLVDL2 | HLVDL1 | HLVDL0 | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on configuration fuses and by type of Reset.

#### TABLE 4-21: DEEP SLEEP REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8       | Bit 7        | Bit 6      | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1 | Bit 0   | All<br>Resets <sup>(1)</sup> |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|-------------|--------------|------------|-------|-------|--------|--------|-------|---------|------------------------------|

| DSCON     | 0758 | DSEN   | _      | _      | _      | _      | —      | _      | _           | —            |            |       |       | _      | _      | DSBOR | RELEASE | 0000                         |

| DSWAKE    | 075A | _      | _      | _      |        |        | _      | _      | DSINT0      | DSFLT        | _          | _     | DSWDT | DSRTCC | DSMCLR | _     | DSPOR   | 0000                         |

| DSGPR0    | 075C |        |        |        |        |        |        | Deep S | leep Genera | al Purpose I | Register 0 |       |       |        |        |       |         | 0000                         |

| DSGPR1    | 075E |        |        |        |        |        |        | Deep S | leep Genera | al Purpose I | Register 1 |       |       |        |        |       |         | 0000                         |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The Deep Sleep registers are only reset on a VDD POR event.

### TABLE 4-22: NVM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets   |

|-----------|------|--------|--------|--------|---------|--------|--------|-------|-------|---------|---------|---------|---------|---------|---------|---------|---------|-----------------|

| NVMCON    | 0760 | WR     | WREN   | WRERR  | PGMONLY | _      | _      | _     | _     | _       | ERASE   | NVMOP5  | NVMOP4  | NVMOP3  | NVMOP2  | NVMOP1  | NVMOP0  | 0000 <b>(1)</b> |

| NVMKEY    | 0766 | —      | —      | -      | —       | —      |        | -     |       | NVMKEY7 | NVMKEY6 | NVMKEY5 | NVMKEY4 | NVMKEY3 | NVMKEY2 | NVMKEY1 | NVMKEY0 | 0000            |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset value shown is for POR only. Value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

# TABLE 4-23: PMD REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|--------|--------|--------|--------|------------|

| PMD1      | 0770 | —      | _      | T3MD   | T2MD   | T1MD   | _      | _      | _     | I2C1MD | U2MD  | U1MD  |       | SPI1MD | _      | _      | ADC1MD | 0000       |

| PMD2      | 0772 | _      | -      |        | —      | —      |        | _      | IC1MD | _      |       | _     | _     | _      | _      | _      | OC1MD  | 0000       |

| PMD3      | 0774 | _      | -      |        | —      | —      | CMPMD  | RTCCMD | _     | CRCPMD |       | _     | _     | _      | _      | _      | _      | 0000       |

| PMD4      | 0776 | —      | Ι      | _      |        | _      | _      | —      | —     | _      | _     | _     | EEMD  | REFOMD | CTMUMD | HLVDMD |        | 0000       |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| REGISTER           | 8-4: INICC                                                                          | JNZ: INTERR                                                                                                                                        | UPI CONTI                                     | ROL REGIST       | EKZ              |                 |        |

|--------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------|------------------|-----------------|--------|

| R/W-0              | R-0, HSC                                                                            | U-0                                                                                                                                                | U-0                                           | U-0              | U-0              | U-0             | U-0    |

| ALTIVT             | DISI                                                                                | —                                                                                                                                                  | _                                             | —                | —                | —               | _      |

| bit 15             |                                                                                     |                                                                                                                                                    |                                               |                  |                  |                 | bit    |

|                    |                                                                                     |                                                                                                                                                    |                                               |                  |                  |                 |        |

| U-0                | U-0                                                                                 | U-0                                                                                                                                                | U-0                                           | U-0              | R/W-0            | R/W-0           | R/W-0  |

| —                  | —                                                                                   | _                                                                                                                                                  |                                               | —                | INT2EP           | INT1EP          | INT0EP |

| bit 7              |                                                                                     |                                                                                                                                                    |                                               |                  |                  |                 | bit    |

|                    |                                                                                     |                                                                                                                                                    |                                               |                  |                  |                 |        |

| Legend:            |                                                                                     | HSC = Hardw                                                                                                                                        | are Settable/C                                |                  |                  |                 |        |

| R = Readabl        | le bit                                                                              | W = Writable                                                                                                                                       | bit                                           | U = Unimple      | mented bit, read | d as '0'        |        |

| -n = Value at      | t POR                                                                               | '1' = Bit is set                                                                                                                                   |                                               | '0' = Bit is cle | eared            | x = Bit is unkr | nown   |

| bit 14<br>bit 13-3 | 1 = Use Alterr<br>0 = Use stand<br>DISI: DISI In:<br>1 = DISI inst<br>0 = DISI inst | Ne Alternate Internate Internate Interrupt V<br>lard (default) ve<br>struction Status<br>ruction is active<br>ruction is not ac<br>ted: Read as '0 | ector Table<br>ector table<br>s bit<br>ective |                  |                  |                 |        |

| bit 2              | •                                                                                   | rnal Interrupt 2                                                                                                                                   |                                               | Dolority Soloot  | hit              |                 |        |

| Dit 2              | 1 = Interrupt c                                                                     | on negative edge                                                                                                                                   | je                                            |                  | Dit              |                 |        |

| bit 1              | 1 = Interrupt c                                                                     | rnal Interrupt 1<br>on negative edg<br>on positive edge                                                                                            | je                                            | Polarity Select  | bit              |                 |        |

| bit 0              | 1 = Interrupt c                                                                     | rnal Interrupt 0<br>on negative edg<br>on positive edge                                                                                            | je                                            | Polarity Select  | bit              |                 |        |

|                    |                                                                                     |                                                                                                                                                    |                                               |                  |                  |                 |        |

## REGISTER 8-4: INTCON2: INTERRUPT CONTROL REGISTER2

| R/W-0         | U-0             | R/W-0                             | R/W-0            | R/W-0             | R/W-0           | R/W-0           | R/W-0         |

|---------------|-----------------|-----------------------------------|------------------|-------------------|-----------------|-----------------|---------------|

| NVMIE         | 0-0             | AD1IE                             | U1TXIE           | U1RXIE            | SPI1IE          | SPF1IE          | T3IE          |

| bit 15        |                 | ADTIL                             | UTTAL            | UIIXIL            | SITTL           | SITTL           | bit           |

|               |                 |                                   |                  |                   |                 |                 | bit           |

| R/W-0         | U-0             | U-0                               | U-0              | R/W-0             | R/W-0           | R/W-0           | R/W-0         |

| T2IE          | —               | _                                 | _                | T1IE              | OC1IE           | IC1IE           | <b>INTOIE</b> |

| bit 7         |                 |                                   |                  |                   |                 |                 | bit           |

| Legend:       |                 |                                   |                  |                   |                 |                 |               |

| R = Readabl   | e bit           | W = Writable                      | bit              | U = Unimplem      | ented bit, read | d as '0'        |               |

| -n = Value at | POR             | '1' = Bit is set                  |                  | '0' = Bit is clea | ared            | x = Bit is unkn | own           |

| bit 15        |                 | Interrupt Enab                    | le hit           |                   |                 |                 |               |

|               |                 | request is enab                   |                  |                   |                 |                 |               |

|               |                 | equest is not e                   |                  |                   |                 |                 |               |

| bit 14        | Unimplemen      | ted: Read as '                    | )'               |                   |                 |                 |               |

| bit 13        | AD1IE: A/D C    | Conversion Con                    | nplete Interrupt | Enable bit        |                 |                 |               |

|               |                 | equest is enab<br>equest is not e |                  |                   |                 |                 |               |

| bit 12        | -               | RT1 Transmitter                   |                  | ole bit           |                 |                 |               |

|               |                 | equest is enab                    | -                |                   |                 |                 |               |

|               | 0 = Interrupt r | equest is not e                   | nabled           |                   |                 |                 |               |

| bit 11        |                 | RT1 Receiver Ir                   | -                | bit               |                 |                 |               |

|               | •               | equest is enab                    |                  |                   |                 |                 |               |

|               | -               | equest is not e                   |                  |                   |                 |                 |               |

| bit 10        |                 | Transfer Comp                     | •                | -nable bit        |                 |                 |               |

|               |                 | equest is enab<br>equest is not e |                  |                   |                 |                 |               |

| bit 9         | -               | Fault Interrupt                   |                  |                   |                 |                 |               |

|               |                 | equest is enab                    |                  |                   |                 |                 |               |

|               |                 | equest is not e                   |                  |                   |                 |                 |               |

| bit 8         | T3IE: Timer3    | Interrupt Enabl                   | e bit            |                   |                 |                 |               |

|               |                 | equest is enab                    |                  |                   |                 |                 |               |

|               |                 | equest is not e                   |                  |                   |                 |                 |               |

| bit 7         |                 | Interrupt Enabl                   |                  |                   |                 |                 |               |

|               |                 | equest is enab<br>equest not is e |                  |                   |                 |                 |               |

| bit 6-4       | Unimplemen      | ted: Read as '                    | )'               |                   |                 |                 |               |

| bit 3         | T1IE: Timer1    | Interrupt Enabl                   | e bit            |                   |                 |                 |               |

|               |                 | equest is enab<br>equest is not e |                  |                   |                 |                 |               |

| bit 2         |                 | ut Compare Ch                     |                  | pt Enable bit     |                 |                 |               |

|               | •               | equest is enab                    |                  | •                 |                 |                 |               |

|               |                 | equest is not e                   |                  |                   |                 |                 |               |

| bit 1         | IC1IE: Input C  | Capture Channe                    | el 1 Interrupt E | nable bit         |                 |                 |               |

|               |                 | equest is enab<br>equest is not e |                  |                   |                 |                 |               |

| bit 0         | •               | nal Interrupt 0                   |                  |                   |                 |                 |               |

|               |                 | equest is enab                    |                  |                   |                 |                 |               |

|               | ±               | oquoot io onuo                    | ica              |                   |                 |                 |               |

## REGISTER 8-11: IEC3: INTERRUPT ENABLE CONTROL REGISTER 3

| U-0     | R/W-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|-------|-----|-----|-----|-----|-----|-------|

| —       | RTCIE | —   | —   | —   | —   | —   | —     |

| bit 15  |       |     |     |     |     |     | bit 8 |

|         |       |     |     |     |     |     |       |

| U-0     | U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

| _       | —     | —   | —   | —   | —   | —   | _     |

| bit 7   |       |     |     |     |     |     | bit 0 |

|         |       |     |     |     |     |     |       |

| Legend: |       |     |     |     |     |     |       |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 15 Unimplemented: Read as '0'

bit 14 RTCIE: Real-Time Clock and Calendar Interrupt Enable bit

1 = Interrupt request is enabled

- 0 = Interrupt request is not enabled

- bit 13-0 Unimplemented: Read as '0'

| U-0                                  |                                                                                                                                                      |                                                                                                                                                                         |                                                                                               |                     |                  |                 |         |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------|------------------|-----------------|---------|

|                                      | R/W-1                                                                                                                                                | R/W-0                                                                                                                                                                   | R/W-0                                                                                         | U-0                 | R/W-1            | R/W-0           | R/W-0   |

|                                      | T1IP2                                                                                                                                                | T1IP1                                                                                                                                                                   | T1IP0                                                                                         | —                   | OC1IP2           | OC1IP1          | OC1IP0  |

| bit 15                               |                                                                                                                                                      |                                                                                                                                                                         |                                                                                               |                     |                  |                 | bit     |

| U-0                                  | R/W-1                                                                                                                                                | R/W-0                                                                                                                                                                   | R/W-0                                                                                         | U-0                 | R/W-1            | R/W-0           | R/W-0   |

| _                                    | IC1IP2                                                                                                                                               | IC1IP1                                                                                                                                                                  | IC1IP0                                                                                        | _                   | INT0IP2          | INT0IP1         | INT0IP0 |

| bit 7                                |                                                                                                                                                      |                                                                                                                                                                         |                                                                                               |                     |                  |                 | bit     |

| Legend:                              |                                                                                                                                                      |                                                                                                                                                                         |                                                                                               |                     |                  |                 |         |

| R = Readat                           | ole bit                                                                                                                                              | W = Writable b                                                                                                                                                          | bit                                                                                           | U = Unimpler        | mented bit, read | d as '0'        |         |

| -n = Value a                         |                                                                                                                                                      | '1' = Bit is set                                                                                                                                                        |                                                                                               | '0' = Bit is cle    |                  | x = Bit is unkr | nown    |

|                                      |                                                                                                                                                      |                                                                                                                                                                         |                                                                                               |                     |                  |                 | -       |

| bit 15                               | Unimpleme                                                                                                                                            | nted: Read as '0                                                                                                                                                        | ,                                                                                             |                     |                  |                 |         |

| bit 14-12                            | T1IP<2:0>:                                                                                                                                           | Timer1 Interrupt I                                                                                                                                                      | Priority bits                                                                                 |                     |                  |                 |         |

|                                      | 111 = Interro                                                                                                                                        | upt is Priority 7 (h                                                                                                                                                    | nighest priority                                                                              | interrupt)          |                  |                 |         |

|                                      | •                                                                                                                                                    |                                                                                                                                                                         |                                                                                               |                     |                  |                 |         |

|                                      | •                                                                                                                                                    |                                                                                                                                                                         |                                                                                               |                     |                  |                 |         |

|                                      | •<br>001 - Interr                                                                                                                                    | upt is Priority 1                                                                                                                                                       |                                                                                               |                     |                  |                 |         |

|                                      |                                                                                                                                                      | upt source is disa                                                                                                                                                      | abled                                                                                         |                     |                  |                 |         |

| bit 11                               |                                                                                                                                                      | nted: Read as '0                                                                                                                                                        |                                                                                               |                     |                  |                 |         |

| bit 10-8                             | -                                                                                                                                                    | ·: Output Compar                                                                                                                                                        |                                                                                               | nterrunt Priorit    | v hits           |                 |         |

|                                      |                                                                                                                                                      | upt is Priority 7 (h                                                                                                                                                    |                                                                                               | -                   |                  |                 |         |

|                                      | 111 Intony                                                                                                                                           |                                                                                                                                                                         | inghoot phone;                                                                                | internapt)          |                  |                 |         |

|                                      | •                                                                                                                                                    |                                                                                                                                                                         |                                                                                               |                     |                  |                 |         |

|                                      | •                                                                                                                                                    |                                                                                                                                                                         |                                                                                               |                     |                  |                 |         |

|                                      | •                                                                                                                                                    |                                                                                                                                                                         |                                                                                               |                     |                  |                 |         |

|                                      |                                                                                                                                                      | upt is Priority 1                                                                                                                                                       | bled                                                                                          |                     |                  |                 |         |

| hit 7                                | 000 = Interre                                                                                                                                        | upt source is disa                                                                                                                                                      |                                                                                               |                     |                  |                 |         |

|                                      | 000 = Interro<br>Unimpleme                                                                                                                           | upt source is disa<br>nted: Read as '0                                                                                                                                  | 3                                                                                             | runt Drineit, / bit | -                |                 |         |

|                                      | 000 = Interr<br>Unimpleme<br>IC1IP<2:0>:                                                                                                             | upt source is disa<br>nted: Read as '0<br>Input Capture Cl                                                                                                              | ,<br>hannel 1 Inter                                                                           |                     | S                |                 |         |

|                                      | 000 = Interr<br>Unimpleme<br>IC1IP<2:0>:                                                                                                             | upt source is disa<br>nted: Read as '0                                                                                                                                  | ,<br>hannel 1 Inter                                                                           |                     | s                |                 |         |

|                                      | 000 = Interr<br>Unimpleme<br>IC1IP<2:0>:                                                                                                             | upt source is disa<br>nted: Read as '0<br>Input Capture Cl                                                                                                              | ,<br>hannel 1 Inter                                                                           |                     | S                |                 |         |

|                                      | 000 = Intern<br>Unimpleme<br>IC1IP<2:0>:<br>111 = Intern<br>•<br>•                                                                                   | upt source is disa<br>nted: Read as '0<br>Input Capture Cl<br>upt is Priority 7 (h                                                                                      | ,<br>hannel 1 Inter                                                                           |                     | S                |                 |         |

|                                      | 000 = Intern<br>Unimpleme<br>IC1IP<2:0>:<br>111 = Intern<br>•<br>•<br>•<br>001 = Intern                                                              | upt source is disa<br>nted: Read as '0<br>Input Capture Cl<br>upt is Priority 7 (h<br>upt is Priority 1                                                                 | ,<br>hannel 1 Inter<br>nighest priority                                                       |                     | S                |                 |         |

| bit 6-4                              | 000 = Intern<br>Unimpleme<br>IC1IP<2:0>:<br>111 = Intern<br>•<br>•<br>001 = Intern<br>000 = Intern                                                   | upt source is disa<br>nted: Read as '0<br>Input Capture Cl<br>upt is Priority 7 (h<br>upt is Priority 1<br>upt source is disa                                           | ,<br>hannel 1 Inter<br>nighest priority<br>abled                                              |                     | s                |                 |         |

| bit 6-4<br>bit 3                     | 000 = Intern<br>Unimpleme<br>IC1IP<2:0>:<br>111 = Intern<br>•<br>•<br>001 = Intern<br>000 = Intern<br>Unimpleme                                      | upt source is disa<br>nted: Read as '0<br>Input Capture Cl<br>upt is Priority 7 (h<br>upt is Priority 1<br>upt source is disa<br>nted: Read as '0                       | ,<br>hannel 1 Inter<br>nighest priority<br>abled                                              | r interrupt)        | S                |                 |         |

| bit 6-4<br>bit 3                     | 000 = Intern<br>Unimpleme<br>IC1IP<2:0>:<br>111 = Intern<br>•<br>•<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>INT0IP<2:0>                       | upt source is disa<br>nted: Read as '0<br>Input Capture Cl<br>upt is Priority 7 (h<br>upt is Priority 1<br>upt source is disa<br>nted: Read as '0<br>>: External Interr | ,<br>hannel 1 Inter<br>highest priority<br>abled<br>,<br>upt 0 Priority b                     | v interrupt)        | S                |                 |         |

| bit 6-4<br>bit 3                     | 000 = Intern<br>Unimpleme<br>IC1IP<2:0>:<br>111 = Intern<br>•<br>•<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>INT0IP<2:0>                       | upt source is disa<br>nted: Read as '0<br>Input Capture Cl<br>upt is Priority 7 (h<br>upt is Priority 1<br>upt source is disa<br>nted: Read as '0                       | ,<br>hannel 1 Inter<br>highest priority<br>abled<br>,<br>upt 0 Priority b                     | v interrupt)        | S                |                 |         |

| bit 6-4<br>bit 3                     | 000 = Intern<br>Unimpleme<br>IC1IP<2:0>:<br>111 = Intern<br>•<br>•<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>INT0IP<2:0>                       | upt source is disa<br>nted: Read as '0<br>Input Capture Cl<br>upt is Priority 7 (h<br>upt is Priority 1<br>upt source is disa<br>nted: Read as '0<br>>: External Interr | ,<br>hannel 1 Inter<br>highest priority<br>abled<br>,<br>upt 0 Priority b                     | v interrupt)        | S                |                 |         |

| bit 7<br>bit 6-4<br>bit 3<br>bit 2-0 | 000 = Intern<br>Unimpleme<br>IC1IP<2:0>:<br>111 = Intern<br>•<br>•<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>INT0IP<2:0>                       | upt source is disa<br>nted: Read as '0<br>Input Capture Cl<br>upt is Priority 7 (h<br>upt is Priority 1<br>upt source is disa<br>nted: Read as '0<br>>: External Interr | ,<br>hannel 1 Inter<br>highest priority<br>abled<br>,<br>upt 0 Priority b                     | v interrupt)        | S                |                 |         |

| bit 6-4<br>bit 3                     | 000 = Intern<br>Unimpleme<br>IC1IP<2:0>:<br>111 = Intern<br>001 = Intern<br>000 = Intern<br>Unimpleme<br>INT0IP<2:0><br>111 = Intern<br>001 = Intern | upt source is disa<br>nted: Read as '0<br>Input Capture Cl<br>upt is Priority 7 (h<br>upt is Priority 1<br>upt source is disa<br>nted: Read as '0<br>>: External Interr | ,<br>hannel 1 Inter<br>highest priority<br>abled<br>,<br>upt 0 Priority b<br>highest priority | v interrupt)        | S                |                 |         |

## REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

| bit 7 | CLKLOCK: Clock Selection Lock Enabled bit<br><u>If FSCM is enabled (FCKSM1 = 1):</u><br>1 = Clock and PLL selections are locked<br>0 = Clock and PLL selections are not locked and may be modified by setting the OSWEN bit<br><u>If FSCM is disabled (FCKSM1 = 0):</u><br>Clock and PLL selections are never locked and may be modified by setting the OSWEN bit. |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                         |

| bit 5 | LOCK: PLL Lock Status bit <sup>(2)</sup><br>1 = PLL module is in lock or PLL module start-up timer is satisfied<br>0 = PLL module is out of lock, PLL start-up timer is running or PLL is disabled                                                                                                                                                                 |

| bit 4 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                         |

| bit 3 | <b>CF:</b> Clock Fail Detect bit<br>1 = FSCM has detected a clock failure<br>0 = No clock failure has been detected                                                                                                                                                                                                                                                |

| bit 2 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                         |

| bit 1 | <b>SOSCEN:</b> 32 kHz Secondary Oscillator (SOSC) Enable bit<br>1 = Enable secondary oscillator<br>0 = Disable secondary oscillator                                                                                                                                                                                                                                |

| bit 0 | <b>OSWEN:</b> Oscillator Switch Enable bit<br>1 = Initiate an oscillator switch to clock source specified by NOSC<2:0> bits<br>0 = Oscillator switch is complete                                                                                                                                                                                                   |

- Note 1: Reset values for these bits are determined by the FNOSC Configuration bits.

- 2: Also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

NOTES:

# EXAMPLE 15-1: PWM PERIOD AND DUTY CYCLE CALCULATIONS<sup>(1)</sup>

1. Find the Timer Period register value for a desired PWM frequency of 52.08 kHz, where Fosc = 8 MHz with PLL (32 MHz device clock rate) and a Timer2 prescaler setting of 1:1.

Tcy = 2 \* Tosc = 62.5 ns

PWM Period = 1/PWM Frequency = 1/52.08 kHz =  $19.2 \mu$ s

PWM Period = (PR2 + 1) • Tcy • (Timer 2 Prescale Value)

19.2 µs = (PR2 + 1) • 62.5 ns • 1

PR2 = 306

2. Find the maximum resolution of the duty cycle that can be used with a 52.08 kHz frequency and a 32 MHz device clock rate:

PWM Resolution =  $log_{10}(FCY/FPWM)/log_{10}2)$  bits

= (log<sub>10</sub>(16 MHz/52.08 kHz)/log<sub>10</sub>2) bits

= 8.3 bits

**Note 1:** Based on Tcy = 2 \* Tosc; Doze mode and PLL are disabled.

## TABLE 15-1: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 4 MIPS (Fcy = 4 MHz)<sup>(1)</sup>

| PWM Frequency         | 7.6 Hz | 61 Hz | 122 Hz | 977 Hz | 3.9 kHz | 31.3 kHz | 125 kHz |

|-----------------------|--------|-------|--------|--------|---------|----------|---------|

| Timer Prescaler Ratio | 8      | 1     | 1      | 1      | 1       | 1        | 1       |

| Period Register Value | FFFFh  | FFFFh | 7FFFh  | 0FFFh  | 03FFh   | 007Fh    | 001Fh   |

| Resolution (bits)     | 16     | 16    | 15     | 12     | 10      | 7        | 5       |

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

## TABLE 15-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 16 MIPS (Fcy = 16 MHz)<sup>(1)</sup>

| PWM Frequency         | 30.5 Hz | 244 Hz | 488 Hz | 3.9 kHz | 15.6 kHz | 125 kHz | 500 kHz |

|-----------------------|---------|--------|--------|---------|----------|---------|---------|

| Timer Prescaler Ratio | 8       | 1      | 1      | 1       | 1        | 1       | 1       |

| Period Register Value | FFFFh   | FFFFh  | 7FFFh  | 0FFFh   | 03FFh    | 007Fh   | 001Fh   |

| Resolution (bits)     | 16      | 16     | 15     | 12      | 10       | 7       | 5       |

**Note 1:** Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

# 19.3 Calibration

The real-time crystal input can be calibrated using the periodic auto-adjust feature. When properly calibrated, the RTCC can provide an error of less than 3 seconds per month. This is accomplished by finding the number of error clock pulses and storing the value into the lower half of the RCFGCAL register. The 8-bit signed value loaded into the lower half of RCFGCAL is multiplied by four and will either be added or subtracted from the RTCC timer, once every minute. Refer to the steps below for RTCC calibration:

- 1. Using another timer resource on the device, the user must find the error of the 32.768 kHz crystal.

- 2. Once the error is known, it must be converted to the number of error clock pulses per minute.

- 3. a) If the oscillator is faster than ideal (negative result form Step 2), the RCFGCAL register value must be negative. This causes the specified number of clock pulses to be subtracted from the timer counter, once every minute.

b) If the oscillator is slower than ideal (positive result from Step 2), the RCFGCAL register value must be positive. This causes the specified number of clock pulses to be subtracted from the timer counter, once every minute.

Divide the number of error clocks, per minute by 4, to get the correct calibration value and load the RCFGCAL register with the correct value. (Each 1-bit increment in the calibration adds or subtracts 4 pulses).

## EQUATION 19-1:

(Ideal Frequency<sup>+</sup> – Measured Frequency) \* 60 = Clocks per Minute

† Ideal Frequency = 32,768 Hz

Writes to the lower half of the RCFGCAL register should only occur when the timer is turned off, or immediately after the rising edge of the seconds pulse.

| Note: |                                                |

|-------|------------------------------------------------|

|       | value, the initial error of the crystal; drift |

|       | due to temperature and drift due to crystal    |

|       | aging.                                         |

# 19.4 Alarm

- · Configurable from half second to one year

- Enabled using the ALRMEN bit (ALCFGRPT<15>)

- One-time alarm and repeat alarm options available

## 19.4.1 CONFIGURING THE ALARM

The alarm feature is enabled using the ALRMEN bit. This bit is cleared when an alarm is issued. Writes to ALRMVAL should only take place when ALRMEN = 0.

As displayed in Figure 19-2, the interval selection of the alarm is configured through the AMASK bits (ALCFGRPT<13:10>). These bits determine which and how many digits of the alarm must match the clock value for the alarm to occur.

The alarm can also be configured to repeat based on a preconfigured interval. The amount of times this occurs, once the alarm is enabled, is stored in the ARPT<7:0> bits (ALCFGRPT<7:0>). When the value of the ARPT bits equals 00h and the CHIME bit (ALCFGRPT<14>) is cleared, the repeat function is disabled and only a single alarm will occur. The alarm can be repeated, up to 255 times, by loading ARPT<7:0> with FFh.

After each alarm is issued, the value of the ARPT bits is decremented by one. Once the value has reached 00h, the alarm will be issued one last time, after which, the ALRMEN bit will be cleared automatically and the alarm will turn off.

Indefinite repetition of the alarm can occur if the CHIME bit = 1. Instead of the alarm being disabled when the value of the ARPT bits reaches 00h, it rolls over to FFh and continues counting indefinitely while CHIME is set.

## 19.4.2 ALARM INTERRUPT

At every alarm event, an interrupt is generated. In addition, an alarm pulse output is provided that operates at half the frequency of the alarm. This output is completely synchronous to the RTCC clock and can be used as a trigger clock to other peripherals.

Note: Changing any of the registers, other than the RCFGCAL and ALCFGRPT registers, and the CHIME bit while the alarm is enabled (ALRMEN = 1), can result in a false alarm event leading to a false alarm interrupt. To avoid a false alarm event, the timer and alarm values should only be changed while the alarm is disabled (ALRMEN = 0). It is recommended that the ALCFGRPT register and the CHIME bit be changed when RTCSYNC = 0.

### TABLE 29-3: DC CHARACTERISTICS: TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARACTERISTICS |        |                                                                     | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |   |     |      |                                   |  |

|--------------------|--------|---------------------------------------------------------------------|------------------------------------------------------|---|-----|------|-----------------------------------|--|

| Param<br>No.       | Symbol | Characteristic                                                      | Min Typ <sup>(1)</sup> Max Units Conditions          |   |     |      | Conditions                        |  |

| DC10               | Vdd    | Supply Voltage                                                      | 1.8                                                  | _ | 3.6 | V    |                                   |  |

| DC12               | Vdr    | RAM Data Retention<br>Voltage <sup>(2)</sup>                        | 1.5                                                  | _ | _   | V    |                                   |  |

| DC16               | VPOR   | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal    | Vss                                                  | — | 0.7 | V    |                                   |  |

| DC17               | Svdd   | <b>VDD Rise Rate</b><br>to Ensure Internal<br>Power-on Reset Signal | 0.05                                                 | _ |     | V/ms | 0-3.3V in 0.1s<br>0-2.5V in 60 ms |  |

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: This is the limit to which VDD can be lowered without losing RAM data.

## TABLE 29-4: HIGH/LOW–VOLTAGE DETECT CHARACTERISTICS

# Standard Operating Conditions (unless otherwise stated)

Operating temperature  $-40^{\circ}C \le TA \le +85^{\circ}C$  for industrial

$-40^{\circ}C \le TA \le +125^{\circ}C$  for Extended

| Param<br>No. | Symbol | Charact             | aracteristic      |      | Тур  | Max  | Units | Conditions |

|--------------|--------|---------------------|-------------------|------|------|------|-------|------------|

| DC18         | Vhlvd  | HLVD Voltage on VDD | HLVDL<3:0> = 0000 | _    | 1.85 | 1.94 | V     |            |

|              |        | Transition          | HLVDL<3:0> = 0001 | 1.81 | 1.90 | 2.00 | V     |            |

|              |        |                     | HLVDL<3:0> = 0010 | 1.85 | 1.95 | 2.05 | V     |            |

|              |        |                     | HLVDL<3:0> = 0011 | 1.90 | 2.00 | 2.10 | V     |            |

|              |        |                     | HLVDL<3:0> = 0100 | 1.95 | 2.05 | 2.15 | V     |            |

|              |        |                     | HLVDL<3:0> = 0101 | 2.06 | 2.17 | 2.28 | V     |            |

|              |        |                     | HLVDL<3:0> = 0110 | 2.12 | 2.23 | 2.34 | V     |            |

|              |        |                     | HLVDL<3:0> = 0111 | 2.24 | 2.36 | 2.48 | V     |            |

|              |        |                     | HLVDL<3:0> = 1000 | 2.31 | 2.43 | 2.55 | V     |            |

|              |        |                     | HLVDL<3:0> = 1001 | 2.47 | 2.60 | 2.73 | V     |            |

|              |        |                     | HLVDL<3:0> = 1010 | 2.64 | 2.78 | 2.92 | V     |            |

|              |        |                     | HLVDL<3:0> = 1011 | 2.74 | 2.88 | 3.02 | V     |            |

|              |        |                     | HLVDL<3:0> = 1100 | 2.85 | 3.00 | 3.15 | V     |            |

|              |        |                     | HLVDL<3:0> = 1101 | 2.96 | 3.12 | 3.28 | V     |            |

|              |        |                     | HLVDL<3:0> = 1110 | 3.22 | 3.39 | 3.56 | V     |            |

## TABLE 29-22: AC SPECIFICATIONS

| Symbol   | Characteristics                                                  | Min        | Тур                  | Max          | Units |

|----------|------------------------------------------------------------------|------------|----------------------|--------------|-------|

| TLW      | BCLKx High Time                                                  | 20         | Tcy/2                |              | ns    |

| THW      | BCLKx Low Time                                                   | 20         | (TCY * BRGx) + TCY/2 | —            | ns    |

| TBLD     | BCLKx Falling Edge Delay from UxTX                               | -50        | —                    | 50           | ns    |

| Твно     | BCLKx Rising Edge Delay from UxTX                                | Тсү/2 – 50 | —                    | TCY/2 + 50   | ns    |

| Twak     | Min. Low on UxRX Line to Cause Wake-up                           | —          | 1                    | —            | μS    |

| TCTS     | Min. Low on UxCTS Line to Start<br>Transmission                  | Тсү        | —                    | _            | ns    |

| TSETUP   | Start bit Falling Edge to System Clock Rising<br>Edge Setup Time | 3          | —                    | —            | ns    |

| TSTDELAY | Maximum Delay in the Detection of the Start bit Falling Edge     | —          | _                    | TCY + TSETUP | ns    |

# TABLE 29-23: A/D CONVERSION TIMING REQUIREMENTS<sup>(1)</sup>

| A/D CH       | A/D CHARACTERISTICS |                                                      |         | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |          |       |                                                 |  |  |

|--------------|---------------------|------------------------------------------------------|---------|------------------------------------------------------|----------|-------|-------------------------------------------------|--|--|

| Param<br>No. | Symbol              | Characteristic                                       | Min.    | Тур                                                  | Max.     | Units | Conditions                                      |  |  |

|              |                     | Clock P                                              | aramete | ers                                                  |          |       |                                                 |  |  |

| AD50         | Tad                 | A/D Clock Period                                     | 75      | _                                                    | —        | ns    | Tcy = 75 ns, AD1CON3<br>is in the default state |  |  |