#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 8KB (2.75K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 1.5K × 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 9x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

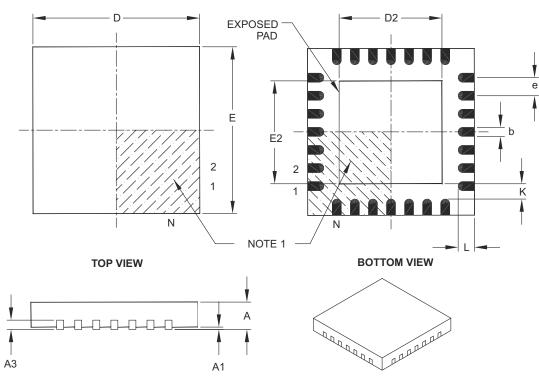

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 28-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08ka102-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- PIC24F08KA101

- PIC24F16KA101

- PIC24F08KA102

- PIC24F16KA102

The PIC24F16KA102 family introduces a new line of extreme low-power Microchip devices: a 16-bit microcontroller family with a broad peripheral feature set and enhanced computational performance. It also offers a new migration option for those high-performance applications, which may be outgrowing their 8-bit platforms, but do not require the numerical processing power of a digital signal processor.

#### 1.1 Core Features

#### 1.1.1 16-BIT ARCHITECTURE

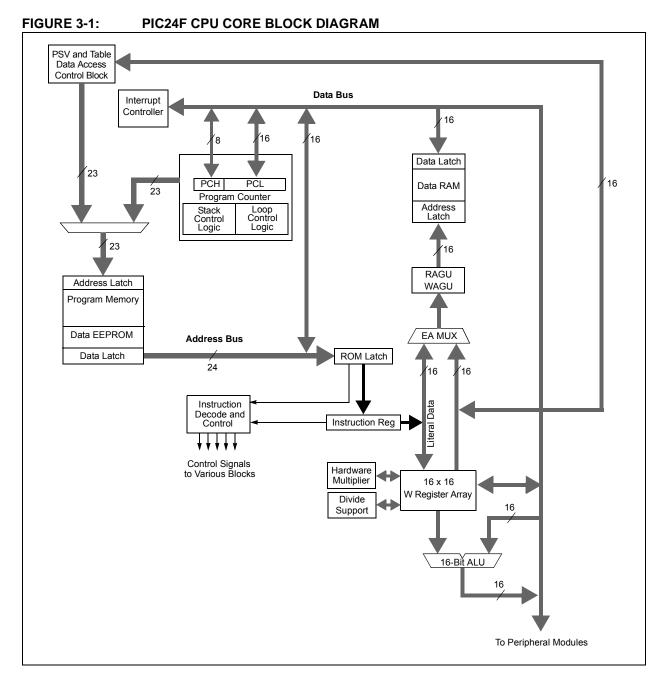

Central to all PIC24F devices is the 16-bit modified Harvard architecture, first introduced with Microchip's dsPIC<sup>®</sup> digital signal controllers. The PIC24F CPU core offers a wide range of enhancements, such as:

- 16-bit data and 24-bit address paths with the ability to move information between data and memory spaces

- Linear addressing of up to 12 Mbytes (program space) and 64 Kbytes (data)

- A 16-element working register array with built-in software stack support

- A 17 x 17 hardware multiplier with support for integer math

- Hardware support for 32-bit by 16-bit division

- An instruction set that supports multiple addressing modes and is optimized for high-level languages, such as C

- Operational performance up to 16 MIPS

#### 1.1.2 POWER-SAVING TECHNOLOGY

All of the devices in the PIC24F16KA102 family incorporate a range of features that can significantly reduce power consumption during operation. Key items include:

- On-the-Fly Clock Switching: The device clock can be changed under software control to the Timer1 source or the internal, low-power RC oscillator during operation, allowing users to incorporate power-saving ideas into their software designs.

- Doze Mode Operation: When timing-sensitive applications, such as serial communications, require the uninterrupted operation of peripherals, the CPU clock speed can be selectively reduced, allowing incremental power savings without missing a beat.

- Instruction-Based Power-Saving Modes: There are three instruction-based power-saving modes:

- Idle Mode: The core is shut down while leaving the peripherals active.

- Sleep Mode: The core and peripherals that require the system clock are shut down, leaving the peripherals that use their own clock, or the clock from other devices, active.

- Deep Sleep Mode: The core, peripherals (except RTCC and DSWDT), Flash and SRAM are shut down.

# 1.1.3 OSCILLATOR OPTIONS AND FEATURES

The PIC24F16KA102 family offers five different oscillator options, allowing users a range of choices in developing application hardware. These include:

- Two Crystal modes using crystals or ceramic resonators.

- Two External Clock modes offering the option of a divide-by-2 clock output.

- Two Fast Internal Oscillators (FRCs): One with a nominal 8 MHz output and the other with a nominal 500 kHz output. These outputs can also be divided under software control to provide clock speed as low as 31 kHz or 2 kHz.

- A Phase Locked Loop (PLL) frequency multiplier, available to the External Oscillator modes and the 8 MHz FRC oscillator, which allows clock speeds of up to 32 MHz.

- A separate Internal RC oscillator (LPRC) with a fixed 31 kHz output, which provides a low-power option for timing-insensitive applications.

## 2.4.1 CONSIDERATIONS FOR CERAMIC CAPACITORS

In recent years, large value, low-voltage, surface-mount ceramic capacitors have become very cost effective in sizes up to a few tens of microfarad. The low-ESR, small physical size and other properties make ceramic capacitors very attractive in many types of applications.

Ceramic capacitors are suitable for use with the internal voltage regulator of this microcontroller. However, some care is needed in selecting the capacitor to ensure that it maintains sufficient capacitance over the intended operating range of the application.

Typical low-cost, 10  $\mu$ F ceramic capacitors are available in X5R, X7R and Y5V dielectric ratings (other types are also available, but are less common). The initial tolerance specifications for these types of capacitors are often specified as ±10% to ±20% (X5R and X7R), or -20%/+80% (Y5V). However, the effective capacitance that these capacitors provide in an application circuit will also vary based on additional factors, such as the applied DC bias voltage and the temperature. The total in-circuit tolerance is, therefore, much wider than the initial tolerance specification.

The X5R and X7R capacitors typically exhibit satisfactory temperature stability (ex:  $\pm 15\%$  over a wide temperature range, but consult the manufacturer's data sheets for exact specifications). However, Y5V capacitors typically have extreme temperature tolerance specifications of  $\pm 22\%$ . Due to the extreme temperature tolerance, a 10  $\mu$ F nominal rated Y5V type capacitor may not deliver enough total capacitance to meet minimum internal voltage regulator stability and transient response requirements. Therefore, Y5V capacitors are not recommended for use with the internal regulator if the application must operate over a wide temperature range.

In addition to temperature tolerance, the effective capacitance of large value ceramic capacitors can vary substantially, based on the amount of DC voltage applied to the capacitor. This effect can be very significant, but is often overlooked or is not always documented.

A typical DC bias voltage vs. capacitance graph for X7R type capacitors is shown in Figure 2-4.

#### FIGURE 2-4: DC BIAS VOLTAGE vs. CAPACITANCE **CHARACTERISTICS** Change (%) 0 -10 6V Capacitor -20 -30 pacitance -40 10V Capacitor -50 -60 -70 6.3V Capacitor 10 11 12 2 8 9 13 16 DC Bias Voltage (VDC)

When selecting a ceramic capacitor to be used with the internal voltage regulator, it is suggested to select a high-voltage rating, so that the operating voltage is a small percentage of the maximum rated capacitor voltage. For example, choose a ceramic capacitor rated at 16V for the 3.3V or 2.5V core voltage. Suggested capacitors are shown in Table 2-1.

### 2.5 ICSP Pins

The PGC and PGD pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed 100 $\Omega$ .

Pull-up resistors, series diodes and capacitors on the PGC and PGD pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pin input voltage high (VIH) and input low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGCx/PGDx pins), programmed into the device, matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to

| Register(s) Name | Description                                    |

|------------------|------------------------------------------------|

| W0 through W15   | Working Register Array                         |

| PC               | 23-Bit Program Counter                         |

| SR               | ALU STATUS Register                            |

| SPLIM            | Stack Pointer Limit Value Register             |

| TBLPAG           | Table Memory Page Address Register             |

| PSVPAG           | Program Space Visibility Page Address Register |

| RCOUNT           | Repeat Loop Counter Register                   |

| CORCON           | CPU Control Register                           |

#### 7.2.1 POR AND LONG OSCILLATOR START-UP TIMES

The oscillator start-up circuitry and its associated delay timers are not linked to the device Reset delays that occur at power-up. Some crystal circuits (especially low-frequency crystals) will have a relatively long start-up time. Therefore, one or more of the following conditions is possible after SYSRST is released:

- The oscillator circuit has not begun to oscillate.

- The Oscillator Start-up Timer (OST) has not expired (if a crystal oscillator is used).

- The PLL has not achieved a lock (if PLL is used).

The device will not begin to execute code until a valid clock source has been released to the system. Therefore, the oscillator and PLL start-up delays must be considered when the Reset delay time must be known.

#### 7.2.2 FAIL-SAFE CLOCK MONITOR (FSCM) AND DEVICE RESETS

If the FSCM is enabled, it will begin to monitor the system clock source when SYSRST is released. If a valid clock source is not available at this time, the device will automatically switch to the FRC oscillator and the user can switch to the desired crystal oscillator in the Trap Service Routine (TSR).

#### 7.3 Special Function Register Reset States

Most of the Special Function Registers (SFRs) associated with the PIC24F CPU and peripherals are reset to a particular value at a device Reset. The SFRs are grouped by their peripheral or CPU function and their Reset values are specified in each section of this manual.

The Reset value for each SFR does not depend on the type of Reset with the exception of four registers. The Reset value for the Reset Control register, RCON, will depend on the type of device Reset. The Reset value for the Oscillator Control register, OSCCON, will depend on the type of Reset and the programmed values of the FNOSC bits in the Flash Configuration Word (FOSCSEL); see Table 7-2. The RCFGCAL and NVMCON registers are only affected by a POR.

### 7.4 Deep Sleep BOR (DSBOR)

Deep Sleep BOR is a very low-power BOR circuitry, used when the device is in Deep Sleep mode. Due to low-current consumption, accuracy may vary.

The DSBOR trip point is around 2.0V. DSBOR is enabled by configuring DSBOREN (FDS<6>) = 1. DSBOREN will re-arm the POR to ensure the device will reset if VDD drops below the POR threshold.

### 7.5 Brown-out Reset (BOR)

The PIC24F16KA102 family devices implement a BOR circuit, which provides the user several configuration and power-saving options. The BOR is controlled by the BORV<1:0> and BOREN<1:0> Configuration bits (FPOR<6:5,1:0>). There are a total of four BOR configurations, which are provided in Table 7-3.

The BOR threshold is set by the BORV<1:0> bits. If BOR is enabled (any values of BOREN<1:0>, except '00'), any drop of VDD below the set threshold point will reset the device. The chip will remain in BOR until VDD rises above threshold.

If the Power-up Timer is enabled, it will be invoked after VDD rises above the threshold. Then, it will keep the chip in Reset for an additional time delay, TPWRT, if VDD drops below the threshold while the Power-up Timer is running. The chip goes back into a BOR and the Power-up Timer will be initialized. Once VDD rises above the threshold, the Power-up Timer will execute the additional time delay.

BOR and the Power-up Timer are independently configured. Enabling the BOR Reset does not automatically enable the PWRT.

### 7.5.1 SOFTWARE ENABLED BOR

When BOREN<1:0> = 01, the BOR can be enabled or disabled by the user in software. This is done with the control bit, SBOREN (RCON<13>). Setting SBOREN enables the BOR to function as previously described. Clearing the SBOREN disables the BOR entirely. The SBOREN bit operates only in this mode; otherwise, it is read as '0'.

Placing BOR under software control gives the user the additional flexibility of tailoring the application to its environment without having to reprogram the device to change the BOR configuration. It also allows the user to tailor the incremental current that the BOR consumes. While the BOR current is typically very small, it may have some impact in low-power applications.

Note: Even when the BOR is under software control, the BOR Reset voltage level is still set by the BORV<1:0> Configuration bits; it can not be changed in software.

| REGISTER     | R 8-8: IFS4                                                                                            |                                      | FLAG STAT      | US REGISTE        | R 4              |                 |           |

|--------------|--------------------------------------------------------------------------------------------------------|--------------------------------------|----------------|-------------------|------------------|-----------------|-----------|

| U-0          | U-0                                                                                                    | R/W-0, HS                            | U-0            | U-0               | U-0              | U-0             | R/W-0, HS |

|              | —                                                                                                      | CTMUIF                               |                | _                 | —                | —               | HLVDIF    |

| bit 15       |                                                                                                        |                                      |                |                   |                  |                 | bit 8     |

|              |                                                                                                        |                                      |                |                   |                  |                 |           |

| U-0          | U-0                                                                                                    | U-0                                  | U-0            | R/W-0, HS         | R/W-0, HS        | R/W-0, HS       | U-0       |

| —            | —                                                                                                      | —                                    |                | CRCIF             | U2ERIF           | U1ERIF          | —         |

| bit 7        |                                                                                                        |                                      |                |                   |                  |                 | bit 0     |

| Legend:      |                                                                                                        | HS = Hardward                        | e Settable bit |                   |                  |                 |           |

| R = Readat   | ole bit                                                                                                | W = Writable b                       | oit            | U = Unimplem      | nented bit, read | d as '0'        |           |

| -n = Value a | at POR                                                                                                 | '1' = Bit is set                     |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown      |

| bit 15-14    | Unimplemer                                                                                             | nted: Read as '0                     | 3              |                   |                  |                 |           |

| bit 13       | CTMUIF: CT                                                                                             | MU Interrupt Fla                     | g Status bit   |                   |                  |                 |           |

|              |                                                                                                        | request has occur<br>request has not |                |                   |                  |                 |           |

| bit 12-9     | Unimplemer                                                                                             | nted: Read as '0                     | ,              |                   |                  |                 |           |

| bit 8        | HLVDIF: Hig                                                                                            | h/Low-Voltage D                      | etect Interrup | t Flag Status bi  | t                |                 |           |

|              |                                                                                                        | request has occurrequest has not     |                |                   |                  |                 |           |

| bit 7-4      | Unimplemer                                                                                             | nted: Read as '0                     | 3              |                   |                  |                 |           |

| bit 3        | CRCIF: CRC                                                                                             | Generator Inter                      | rupt Flag Stat | us bit            |                  |                 |           |

|              | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |                                      |                |                   |                  |                 |           |

| bit 2        | U2ERIF: UART2 Error Interrupt Flag Status bit                                                          |                                      |                |                   |                  |                 |           |

|              | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |                                      |                |                   |                  |                 |           |

| bit 1        | U1ERIF: UART1 Error Interrupt Flag Status bit                                                          |                                      |                |                   |                  |                 |           |

|              |                                                                                                        | request has occur<br>request has not |                |                   |                  |                 |           |

| bit 0        | Unimplemer                                                                                             | nted: Read as '0                     | 3              |                   |                  |                 |           |

|              |                                                                                                        |                                      |                |                   |                  |                 |           |

#### REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

| bit 7 | CLKLOCK: Clock Selection Lock Enabled bit<br><u>If FSCM is enabled (FCKSM1 = 1):</u><br>1 = Clock and PLL selections are locked<br>0 = Clock and PLL selections are not locked and may be modified by setting the OSWEN bit<br><u>If FSCM is disabled (FCKSM1 = 0):</u><br>Clock and PLL selections are never locked and may be modified by setting the OSWEN bit. |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                         |

| bit 5 | LOCK: PLL Lock Status bit <sup>(2)</sup><br>1 = PLL module is in lock or PLL module start-up timer is satisfied<br>0 = PLL module is out of lock, PLL start-up timer is running or PLL is disabled                                                                                                                                                                 |

| bit 4 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                         |

| bit 3 | <b>CF:</b> Clock Fail Detect bit<br>1 = FSCM has detected a clock failure<br>0 = No clock failure has been detected                                                                                                                                                                                                                                                |

| bit 2 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                         |

| bit 1 | <b>SOSCEN:</b> 32 kHz Secondary Oscillator (SOSC) Enable bit<br>1 = Enable secondary oscillator<br>0 = Disable secondary oscillator                                                                                                                                                                                                                                |

| bit 0 | <b>OSWEN:</b> Oscillator Switch Enable bit<br>1 = Initiate an oscillator switch to clock source specified by NOSC<2:0> bits<br>0 = Oscillator switch is complete                                                                                                                                                                                                   |

- Note 1: Reset values for these bits are determined by the FNOSC Configuration bits.

- 2: Also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

#### 9.4 Clock Switching Operation

With few limitations, applications are free to switch between any of the four clock sources (POSC, SOSC, FRC and LPRC) under software control and at any time. To limit the possible side effects that could result from this flexibility, PIC24F devices have a safeguard lock built into the switching process.

**Note:** The Primary Oscillator mode has three different submodes (XT, HS and EC), which are determined by the POSCMDx Configuration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch between the different primary submodes without reprogramming the device.

#### 9.4.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the FOSC Configuration register must be programmed to '0'. (Refer to **Section 26.1 "Configuration Bits"** for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and FSCM function are disabled; this is the default setting.

The NOSCx control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSCx bits (OSCCON<14:12>) will reflect the clock source selected by the FNOSCx Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled; it is held at '0' at all times.

#### 9.4.2 OSCILLATOR SWITCHING SEQUENCE

At a minimum, performing a clock switch requires this basic sequence:

- 1. If desired, read the COSCx bits (OSCCON<14:12>), to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- 3. Write the appropriate value to the NOSCx bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically as follows:

- 1. The clock switching hardware compares the COSCx bits with the new value of the NOSCx bits. If they are the same, then the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the LOCK (OSCCON<5>) and CF (OSCCON<3>) bits are cleared.

- The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware will wait until the OST expires. If the new source is using the PLL, then the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- 5. The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSCx bits value is transferred to the COSCx bits.

- The old clock source is turned off at this time, with the exception of LPRC (if WDT, FSCM or RTCC with LPRC as clock source are enabled) or SOSC (if SOSCEN remains enabled).

Note 1: The processor will continue to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

### 11.0 I/O PORTS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the I/O ports, refer to the "PIC24F Family Reference Manual", Section 12. "I/O Ports with Peripheral Pin Select (PPS)" (DS39711). Note that the PIC24F16KA102 family devices do not support Peripheral Pin Select features.

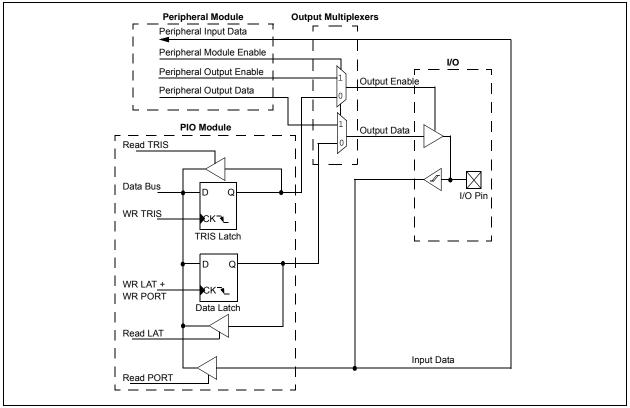

All of the device pins (except VDD and VSS) are shared between the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

### 11.1 Parallel I/O (PIO) Ports

A parallel I/O port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 displays how ports are shared with other peripherals and the associated I/O pin to which they are connected. When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin may be read, but the output driver for the parallel port bit will be disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin may be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the Data Latch register (LATx), read the latch. Writes to the latch, write the latch. Reads from the port (PORTx), read the port pins, while writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers, and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

Note: The I/O pins retain their state during Deep Sleep. They will retain this state at wake-up until the software restore bit (RELEASE) is cleared.

© 2008-2011 Microchip Technology Inc.

NOTES:

### 16.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Serial Peripheral Interface, refer to the *"PIC24F Family Reference Manual"*, Section 23. *"Serial Peripheral Interface (SPI)"* (DS39699).

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial data EEPROMs, shift registers, display drivers, A/D Converters, etc. The SPI module is compatible with the SPI and SIOP interfaces from Motorola<sup>®</sup>.

The module supports operation in two buffer modes. In Standard mode, data is shifted through a single serial buffer. In Enhanced Buffer mode, data is shifted through an 8-level FIFO buffer.

Note: Do not perform read-modify-write operations (such as bit-oriented instructions) on the SPI1BUF register in either Standard or Enhanced Buffer mode.

The module also supports a basic framed SPI protocol while operating in either Master or Slave mode. A total of four framed SPI configurations are supported.

The SPI serial interface consists of four pins:

- SDI1: Serial Data Input

- SDO1: Serial Data Output

- SCK1: Shift Clock Input or Output

- SS1: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPI module can be configured to operate using 2, 3 or 4 pins. In the 3-pin mode, SS1 is not used. In the 2-pin mode, both SDO1 and SS1 are not used.

Block diagrams of the module in Standard and Enhanced Buffer modes are displayed in Figure 16-1 and Figure 16-2. The devices of the PIC24F16KA102 family offer one SPI module on a device.

Note: In this section, the SPI module is referred to as SPI1, or separately as SPI1. Special Function Registers (SFRs) will follow a similar notation. For example, SPI1CON1 or SPI1CON2 refers to the control register for the SPI1 module.

To set up the SPI module for the Standard Master mode of operation:

- 1. If using interrupts:

- a) Clear the respective SPI1IF bit in the IFS0 register.

- b) Set the respective SPI1IE bit in the IEC0 register.

- c) Write the respective SPI1IPx bits in the IPC2 register to set the interrupt priority.

- Write the desired settings to the SPI1CON1 and SPI1CON2 registers with the MSTEN bit (SPI1CON1<5>) = 1.

- 3. Clear the SPIROV bit (SPI1STAT<6>).

- 4. Enable SPI operation by setting the SPIEN bit (SPI1STAT<15>).

- 5. Write the data to be transmitted to the SPI1BUF register. Transmission (and reception) will start as soon as data is written to the SPI1BUF register.

To set up the SPI module for the Standard Slave mode of operation:

- 1. Clear the SPI1BUF register.

- 2. If using interrupts:

- a) Clear the respective SPI1IF bit in the IFS0 register.

- b) Set the respective SPI1IE bit in the IEC0 register.

- c) Write the respective SPI1IP bits in the IPC2 register to set the interrupt priority.

- Write the desired settings to the SPI1CON1 and SPI1CON2 registers with the MSTEN bit (SPI1CON1<5>) = 0.

- 4. Clear the SMP bit.

- 5. If the CKE bit is set, then the SSEN bit (SPI1CON1<7>) must be set to enable the SS1 pin.

- 6. Clear the SPIROV bit (SPI1STAT<6>).

- 7. Enable SPI operation by setting the SPIEN bit (SPI1STAT<15>).

| U-0           | U-0                                     | U-0                                   | R/W-0           | R/W-0             | R/W-0             | R/W-0            | R/W-0              |

|---------------|-----------------------------------------|---------------------------------------|-----------------|-------------------|-------------------|------------------|--------------------|

| _             | —                                       | —                                     | DISSCK          | DISSDO            | MODE16            | SMP              | CKE <sup>(1)</sup> |

| bit 15        |                                         |                                       |                 |                   |                   |                  | bit 8              |

| R/W-0         | R/W-0                                   | R/W-0                                 | R/W-0           | R/W-0             | R/W-0             | R/W-0            | R/W-0              |

| SSEN          | CKP                                     | MSTEN                                 | SPRE2           | SPRE1             | SPRE0             | PPRE1            | PPRE0              |

| bit 7         |                                         | ·                                     |                 | •                 | ·                 |                  | bit (              |

| Legend:       |                                         |                                       |                 |                   |                   |                  |                    |

| R = Readable  | e bit                                   | W = Writable                          | bit             | U = Unimplen      | nented bit, read  | as '0'           |                    |

| -n = Value at | POR                                     | '1' = Bit is set                      |                 | '0' = Bit is cle  | ared              | x = Bit is unkr  | nown               |

| bit 15-13     | Unimplemen                              | ted: Read as '                        | )'              |                   |                   |                  |                    |

| bit 12        | DISSCK: Disa                            | able SCK1 pin                         | bit (SPI Master | r modes only)     |                   |                  |                    |

|               |                                         | PI clock is disa<br>PI clock is enal  | · •             | ions as I/O       |                   |                  |                    |

| bit 11        |                                         | ables SDO1 pir                        |                 |                   |                   |                  |                    |

|               | 1 = SDO1 pir                            | n is not used by<br>n is controlled b | v module; pin f | unctions as I/O   |                   |                  |                    |

| bit 10        | -                                       | ord/Byte Comm                         | -               | ct bit            |                   |                  |                    |

|               | 1 = Commun                              | ication is word-                      | wide (16 bits)  |                   |                   |                  |                    |

|               | 0 = Communication is byte-wide (8 bits) |                                       |                 |                   |                   |                  |                    |

| bit 9         | SMP: SPI1 D                             | ata Input Samp                        | le Phase bit    |                   |                   |                  |                    |

|               | Master mode:                            |                                       |                 |                   |                   |                  |                    |

|               |                                         | a is sampled at                       |                 |                   | •                 |                  |                    |

|               | Slave mode:                             | a is sampled at                       |                 |                   | e                 |                  |                    |

|               |                                         | cleared when                          | SPI1 is used ir | n Slave mode.     |                   |                  |                    |

| bit 8         |                                         | lock Edge Sele                        |                 |                   |                   |                  |                    |

|               |                                         | •                                     |                 | n from active c   | lock state to Idl | e clock state (s | see bit 6)         |

|               |                                         |                                       |                 |                   | ck state to activ |                  |                    |

| bit 7         | SSEN: Slave                             | Select Enable                         | bit (Slave mod  | e)                |                   |                  |                    |

|               |                                         | s used for Slav                       |                 |                   |                   |                  |                    |

|               | •                                       | s not used by t                       | •               | is controlled b   | y port function   |                  |                    |

| bit 6         |                                         | olarity Select b                      |                 |                   |                   |                  |                    |

|               |                                         | for clock is a h                      | •               |                   |                   |                  |                    |

| bit 5         |                                         | for clock is a lot<br>ter Mode Enab   |                 | e state is a high | level             |                  |                    |

| bit 5         | 1 = Master m                            |                                       |                 |                   |                   |                  |                    |

|               | 0 = Slave mo                            |                                       |                 |                   |                   |                  |                    |

| bit 4-2       | SPRE<2:0>:                              | Secondary Pre                         | scale bits (Mas | ster mode)        |                   |                  |                    |

|               | 111 = Second                            | dary prescale 1                       | :1              |                   |                   |                  |                    |

|               |                                         | dary prescale 2                       |                 |                   |                   |                  |                    |

|               | •                                       |                                       |                 |                   |                   |                  |                    |

|               | •                                       |                                       |                 |                   |                   |                  |                    |

|               | •<br>000 = Second                       | dary prescale 8                       | :1              |                   |                   |                  |                    |

| Note 1: Th    |                                         | t used in the Fi                      |                 |                   |                   |                  |                    |

### REGISTER 16-2: SPI1CON1: SPI1 CONTROL REGISTER 1

SPI modes (FRMEN = 1).

### EQUATION 16-1: RELATIONSHIP BETWEEN DEVICE AND SPI CLOCK SPEED<sup>(1)</sup>

FCY

FSCK = Primary Prescaler \* Secondary Prescaler

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

### TABLE 16-1: SAMPLE SCK FREQUENCIES<sup>(1,2)</sup>

| Fcy = 16 MHz               |      | Secondary Prescaler Settings |      |      |      |      |  |

|----------------------------|------|------------------------------|------|------|------|------|--|

|                            |      | 1:1                          | 2:1  | 4:1  | 6:1  | 8:1  |  |

| Primary Prescaler Settings | 1:1  | Invalid                      | 8000 | 4000 | 2667 | 2000 |  |

|                            | 4:1  | 4000                         | 2000 | 1000 | 667  | 500  |  |

|                            | 16:1 | 1000                         | 500  | 250  | 167  | 125  |  |

|                            | 64:1 | 250                          | 125  | 63   | 42   | 31   |  |

| Fcy = 5 MHz                |      |                              |      |      |      |      |  |

| Primary Prescaler Settings | 1:1  | 5000                         | 2500 | 1250 | 833  | 625  |  |

|                            | 4:1  | 1250                         | 625  | 313  | 208  | 156  |  |

|                            | 16:1 | 313                          | 156  | 78   | 52   | 39   |  |

|                            | 64:1 | 78                           | 39   | 20   | 13   | 10   |  |

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

2: SCK1 frequencies are indicated in kHz.

### REGISTER 17-2: I2C1STAT: I2C1 STATUS REGISTER (CONTINUED)

| bit 3 | S: Start bit                                                                                               |

|-------|------------------------------------------------------------------------------------------------------------|

|       | 1 = Indicates that a Start (or Repeated Start) bit has been detected last                                  |

|       | 0 = Start bit was not detected last                                                                        |

|       | Hardware is set or clear when Start, Repeated Start or Stop is detected.                                   |

| bit 2 | R/W: Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                 |

|       | 1 = Read – indicates the data transfer is output from slave                                                |

|       | 0 = Write – indicates the data transfer is input to slave                                                  |

|       | Hardware is set or clear after reception of I <sup>2</sup> C device address byte.                          |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                        |

|       | 1 = Receive complete, I2C1RCV is full                                                                      |

|       | 0 = Receive not complete, I2C1RCV is empty                                                                 |

|       | Hardware is set when I2C1RCV is written with received byte; hardware is clear when software reads I2C1RCV. |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                       |

|       | 1 = Transmit in progress, I2C1TRN is full                                                                  |

0 = Transmit complete, I2C1TRN is empty

Hardware is set when software writes to I2C1TRN; hardware is clear at completion of data transmission.

| UARTEN<br>bit 15 |                                                                       |                                            |                     |                                          |                                            |                                                        |                 |

|------------------|-----------------------------------------------------------------------|--------------------------------------------|---------------------|------------------------------------------|--------------------------------------------|--------------------------------------------------------|-----------------|

| bit 15           |                                                                       | USIDL                                      | IREN <sup>(1)</sup> | RTSMD                                    | —                                          | UEN1                                                   | UEN0            |

|                  |                                                                       |                                            |                     |                                          |                                            |                                                        | bit             |

| R/C-0, HC        | R/W-0                                                                 | R/W-0, HC                                  | R/W-0               | R/W-0                                    | R/W-0                                      | R/W-0                                                  | R/W-0           |

| WAKE             | LPBACK                                                                | ABAUD                                      | RXINV               | BRGH                                     | PDSEL1                                     | PDSEL0                                                 | STSEL           |

| bit 7            |                                                                       | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,    | TOUTV               | Brion                                    | 1 DOLLI                                    | 1 DOLLO                                                | bit             |

| Legend:          |                                                                       | C = Clearable                              | bit                 | HC = Hardwa                              | are Clearable bi                           | it                                                     |                 |

| R = Readable     | e bit                                                                 | W = Writable                               |                     | U = Unimpler                             | nented bit, read                           | d as '0'                                               |                 |

| -n = Value at    |                                                                       | '1' = Bit is set                           |                     | '0' = Bit is cle                         |                                            | x = Bit is unkn                                        | own             |

|                  |                                                                       |                                            |                     |                                          |                                            |                                                        |                 |

| bit 15           | UARTEN: UA                                                            | RTx Enable bit                             |                     |                                          |                                            |                                                        |                 |

|                  | 1 = UARTx is                                                          | s enabled; all U                           | ARTx pins are       | controlled by l                          | JARTx as defin                             | ed by UEN<1:0                                          | )>              |

|                  | 0 = UARTx is<br>minimal                                               | s disabled; all l                          | JARTx pins ar       | e controlled by                          | port latches; l                            | JARTx power c                                          | onsumption i    |

| bit 14           | Unimplemen                                                            | ted: Read as '                             | )'                  |                                          |                                            |                                                        |                 |

| bit 13           | USIDL: Stop                                                           | in Idle Mode bit                           |                     |                                          |                                            |                                                        |                 |

|                  | 1 = Discontinue module operation when device enters Idle mode         |                                            |                     |                                          |                                            |                                                        |                 |

|                  | 0 = Continue module operation in Idle mode                            |                                            |                     |                                          |                                            |                                                        |                 |

| bit 12           | IREN: IrDA <sup>®</sup> Encoder and Decoder Enable bit <sup>(1)</sup> |                                            |                     |                                          |                                            |                                                        |                 |

|                  |                                                                       | oder and decoo<br>oder and decoo           |                     |                                          |                                            |                                                        |                 |

| bit 11           | RTSMD: Mod                                                            | le Selection for                           | UxRTS Pin bi        | t                                        |                                            |                                                        |                 |

|                  |                                                                       | in is in Simplex<br>in is in Flow Co       |                     |                                          |                                            |                                                        |                 |

| bit 10           | Unimplemen                                                            | ted: Read as '                             | )'                  |                                          |                                            |                                                        |                 |

| bit 9-8          | UEN<1:0>: U                                                           | ARTx Enable b                              | its <sup>(2)</sup>  |                                          |                                            |                                                        |                 |

|                  | 10 = UxTX, U<br>01 = UxTX, U                                          | JxRX, UxCTS a<br>JxRX and UxR <sup>*</sup> | and UxRTS pir       | ns are enabled<br>abled <u>and us</u> ed | an <u>d used</u><br>d; <u>UxCTS</u> pin is | is controlled by<br>controlled by p<br>CLK pins are co | ort latches     |

| bit 7            | WAKE: Wake                                                            | -up on Start Bi                            | Detect During       | g Sleep Mode E                           | Enable bit                                 |                                                        |                 |

|                  |                                                                       | vill continue to a on the followir         |                     | RX pin; interru                          | ot generated or                            | n falling edge, b                                      | it is cleared i |

|                  | 0 = No wake                                                           | -up is enabled                             |                     |                                          |                                            |                                                        |                 |

| bit 6            |                                                                       | RTx Loopback                               | Mode Select         | bit                                      |                                            |                                                        |                 |

|                  |                                                                       | oopback mode<br>k mode is disat            | led                 |                                          |                                            |                                                        |                 |

| bit 5            | ABAUD: Auto                                                           | o-Baud Enable                              | bit                 |                                          |                                            |                                                        |                 |

|                  | cleared in                                                            | n hardware upo                             | n completion        |                                          | er – requires re                           | ception of a Sy                                        | nc field (55h   |

|                  |                                                                       | e measurement                              |                     | completed                                |                                            |                                                        |                 |

| bit 4            |                                                                       | ive Polarity Inv                           | ersion bit          |                                          |                                            |                                                        |                 |

|                  | 1 = UxRX IdI<br>0 = UxRX IdI                                          |                                            |                     |                                          |                                            |                                                        |                 |

| Note 1: Th       | is feature is on                                                      | ly available for                           | the 16x BRG i       | mode (BRGH =                             | • 0).                                      |                                                        |                 |

#### REGISTER 23-1: CMxCON: COMPARATOR x CONTROL REGISTERS

| R/W-0         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                 | R/W-0        | U-0                                  | U-0            | R/W-0            | R-0            |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------|--------------------------------------|----------------|------------------|----------------|--|--|

| CON           | COE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CPOL                                                                                                                  | CLPWR        |                                      |                | CEVT             | COUT           |  |  |

| bit 15        | - 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                                                                                     |              |                                      |                |                  | bit 8          |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                       |              |                                      |                |                  |                |  |  |

| R/W-0         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | U-0                                                                                                                   | R/W-0        | U-0                                  | U-0            | R/W-0            | R/W-0          |  |  |

| EVPOL1        | EVPOL0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | —                                                                                                                     | CREF         | —                                    | —              | CCH1             | CCH0           |  |  |

| bit 7         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                       |              |                                      |                |                  | bit 0          |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                       |              |                                      |                |                  |                |  |  |

| Legend:       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                       |              |                                      |                |                  |                |  |  |

| R = Readabl   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | W = Writable                                                                                                          |              | U = Unimplem                         |                |                  |                |  |  |

| -n = Value at | POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | '1' = Bit is set                                                                                                      |              | '0' = Bit is clea                    | ared           | x = Bit is unkr  | iown           |  |  |

| bit 15        | CON: Compo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | rator Enable b                                                                                                        | :+           |                                      |                |                  |                |  |  |

| DIL 15        | <ul> <li>CON: Comparator Enable bit</li> <li>1 = Comparator is enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                       |              |                                      |                |                  |                |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ator is disabled                                                                                                      |              |                                      |                |                  |                |  |  |