Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 24                                                                            |

| Program Memory Size        | 8KB (2.75K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1.5K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 9x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

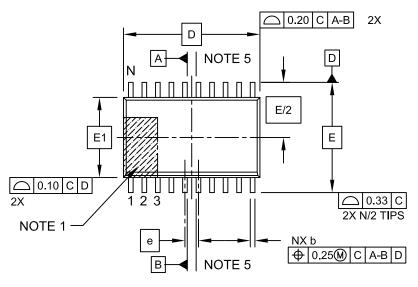

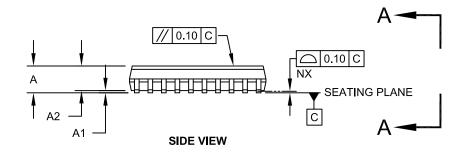

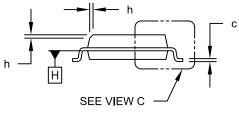

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 28-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08ka102t-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The internal oscillator block also provides a stable reference source for the Fail-Safe Clock Monitor (FSCM). This option constantly monitors the main clock source against a reference signal provided by the internal oscillator and enables the controller to switch to the internal oscillator, allowing for continued low-speed operation or a safe application shutdown.

## 1.1.4 EASY MIGRATION

Regardless of the memory size, all the devices share the same rich set of peripherals, allowing for a smooth migration path as applications grow and evolve.

The consistent pinout scheme used throughout the entire family also helps in migrating to the next larger device. This is true when moving between devices with the same pin count, or even jumping from 20-pin to 28-pin devices.

The PIC24F family is pin compatible with devices in the dsPIC33 family, and shares some compatibility with the pinout schema for PIC18 and dsPIC30. This extends the ability of applications to grow from the relatively simple, to the powerful and complex.

# 1.2 Other Special Features

- Communications: The PIC24F16KA102 family incorporates a range of serial communication peripherals to handle a range of application requirements. There is an I<sup>2</sup>C<sup>™</sup> module that supports both the Master and Slave modes of operation. It also comprises UARTs with built-in IrDA<sup>®</sup> encoders/decoders and an SPI module.

- Real-Time Clock/Calendar: This module implements a full-featured clock and calendar with alarm functions in hardware, freeing up timer resources and program memory space for use of the core application.

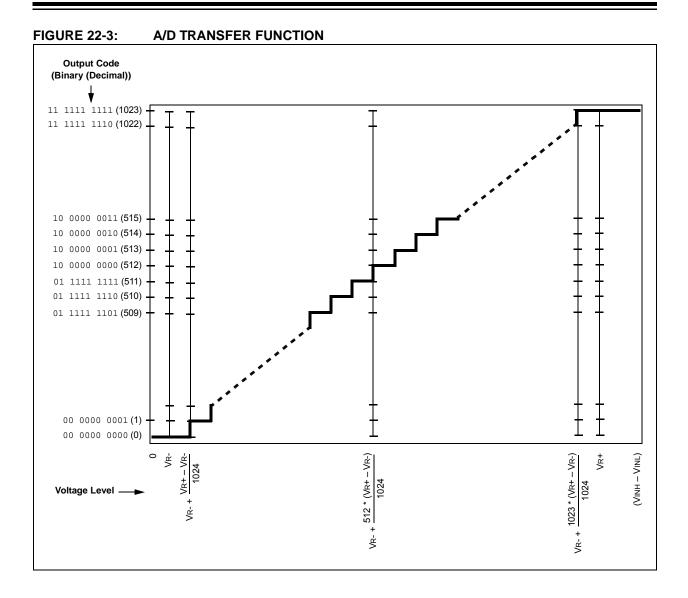

- **10-Bit A/D Converter:** This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period, and faster sampling speed. The 16-deep result buffer can be used either in Sleep to reduce power, or in Active mode to improve throughput.

- Charge Time Measurement Unit (CTMU) Interface: The PIC24F16KA102 family includes the new CTMU interface module, which can be used for capacitive touch sensing, proximity sensing and also for precision time measurement and pulse generation.

# 1.3 Details on Individual Family Members

Devices in the PIC24F16KA102 family are available in 20-pin and 28-pin packages. The general block diagram for all devices is displayed in Figure 1-1.

The devices are different from each other in two ways:

- 1. Flash program memory (8 Kbytes for PIC24F08KA devices, 16 Kbytes for PIC24F16KA devices).

- 2. Available I/O pins and ports (18 pins on two ports for 20-pin devices and 24 pins on two ports for 28-pin devices).

- 3. Alternate SCLx and SDAx pins are available only in 28-pin devices and not in 20-pin devices.

All other features for devices in this family are identical; these are summarized in Table 1-1.

A list of the pin features available on the PIC24F16KA102 family devices, sorted by function, is provided in Table 1-2.

Note: Table 1-1 provides the pin location of individual peripheral features and not how they are multiplexed on the same pin. This information is provided in the pinout diagrams on pages 4, 5 and 6 of the data sheet. Multiplexed features are sorted by the priority given to a feature, with the highest priority peripheral being listed first.

# 3.2 CPU Control Registers

## REGISTER 3-1: SR: ALU STATUS REGISTER

| U-0                       | U-0                       | U-0                       | U-0      | U-0        | U-0        | U-0        | R/W-0, HSC |

|---------------------------|---------------------------|---------------------------|----------|------------|------------|------------|------------|

| —                         | —                         | —                         | _        | —          | —          | —          | DC         |

| bit 15                    |                           |                           |          |            |            |            | bit 8      |

|                           |                           |                           |          |            |            |            |            |

| R/W-0, HSC <sup>(1)</sup> | R/W-0, HSC <sup>(1)</sup> | R/W-0, HSC <sup>(1)</sup> | R-0, HSC | R/W-0, HSC | R/W-0, HSC | R/W-0, HSC | R/W-0, HSC |

| R/W-0, HSC <sup>(1)</sup> | R/W-0, HSC <sup>(1)</sup> | R/W-0, HSC <sup>(1)</sup> | R-0, HSC | R/W-0, HSC | R/W-0, HSC | R/W-0, HSC | R/W-0, HSC |

|---------------------------|---------------------------|---------------------------|----------|------------|------------|------------|------------|

| IPL2 <sup>(2)</sup>       | IPL1 <sup>(2)</sup>       | IPL0 <sup>(2)</sup>       | RA       | N          | OV         | Z          | С          |

| bit 7                     |                           |                           |          |            |            |            | bit 0      |

| Legend:           | HSC = Hardware Settable/Clearable bit |                                    |                    |  |  |  |  |

|-------------------|---------------------------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

| bit 15-9      | Unimplemented: Read as '0'                                                                                                          |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------|

| bit 8         | DC: ALU Half Carry/Borrow bit                                                                                                       |

|               | 1 = A carry-out from the 4 <sup>th</sup> low-order bit (for byte-sized data) or 8 <sup>th</sup> low-order bit (for word-sized data) |

|               | of the result occurred<br>0 = No carry-out from the 4 <sup>th</sup> or 8 <sup>th</sup> low-order bit of the result has occurred     |

| bit 7-5       | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(1,2)</sup>                                                                 |

| DIL 7-5       | 111 = CPU interrupt priority level is 7 (15); user interrupts disabled                                                              |

|               | 111 = CPU interrupt priority level is 7 (13), user interrupts disabled<br>110 = CPU interrupt priority level is 6 (14)              |

|               | 101 = CPU Interrupt priority level is 5 (13)                                                                                        |

|               | 100 = CPU interrupt priority level is 4 (12)                                                                                        |

|               | 011 = CPU interrupt priority level is 3 (11)<br>010 = CPU interrupt priority level is 2 (10)                                        |

|               | 010 = CPU interrupt priority level is 2 (10)<br>001 = CPU interrupt priority level is 1 (9)                                         |

|               | 000 = CPU interrupt priority level is 0 (8)                                                                                         |

| bit 4         | RA: REPEAT Loop Active bit                                                                                                          |

|               | 1 = REPEAT loop in progress                                                                                                         |

|               | 0 = REPEAT loop not in progress                                                                                                     |

| bit 3         | N: ALU Negative bit                                                                                                                 |

|               | 1 = Result was negative                                                                                                             |

| <b>h</b> :+ 0 | 0 = Result was non-negative (zero or positive)<br><b>OV:</b> ALU Overflow bit                                                       |

| bit 2         | 1 = Overflow occurred for signed (2's complement) arithmetic in this arithmetic operation                                           |

|               | 0 = No overflow has occurred                                                                                                        |

| bit 1         | Z: ALU Zero bit                                                                                                                     |

|               | 1 = An operation, which effects the Z bit, has set it at some time in the past                                                      |

|               | 0 = The most recent operation, which effects the Z bit, has cleared it (i.e., a non-zero result)                                    |

| bit 0         | C: ALU Carry/Borrow bit                                                                                                             |

|               | 1 = A carry-out from the Most Significant bit (MSb) of the result occurred                                                          |

|               | 0 = No carry-out from the Most Significant bit (MSb) of the result occurred                                                         |

| Note 1:       | The IPL Status bits are read-only when NSTDIS (INTCON1<15>) = 1.                                                                    |

| 2:            | The IPL Status bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU Interrupt Priority                               |

|               | Level (IPL). The value in parentheses indicates the IPL when IPL3 = 1.                                                              |

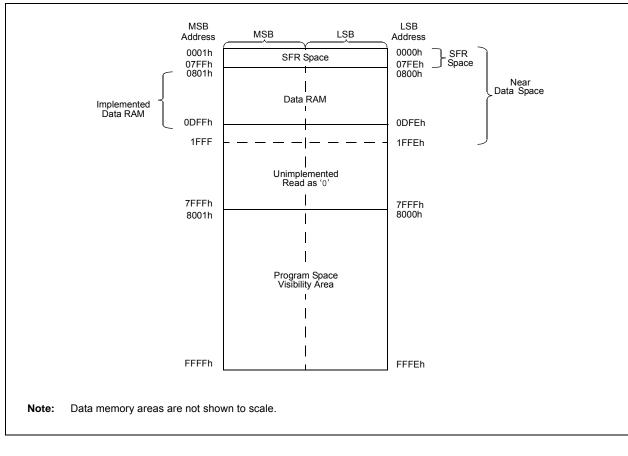

# 4.2 Data Address Space

The PIC24F core has a separate, 16-bit wide data memory space, addressable as a single linear range. The data space is accessed using two Address Generation Units (AGUs), one each for read and write operations. The data space memory map is displayed in Figure 4-3.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the data space. This gives a data space address range of 64 Kbytes or 32K words. The lower half of the data memory space (that is, when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility (PSV) area (see Section 4.3.3 "Reading Data From Program Memory Using Program Space Visibility").

PIC24F16KA102 family devices implement a total of 768 words of data memory. Should an EA point to a location outside of this area, an all zero word or byte will be returned.

## 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byte-addressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all the data space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

#### FIGURE 4-3: DATA SPACE MEMORY MAP FOR PIC24F16KA102 FAMILY DEVICES

# TABLE 4-4: ICN REGISTER MAP

| File<br>Name | Addr | Bit 15                 | Bit 14  | Bit 13  | Bit 12  | Bit 11                 | Bit 10 | Bit 9  | Bit 8                  | Bit 7                 | Bit 6   | Bit 5   | Bit 4  | Bit 3         | Bit 2  | Bit 1  | Bit 0                  | All<br>Resets |

|--------------|------|------------------------|---------|---------|---------|------------------------|--------|--------|------------------------|-----------------------|---------|---------|--------|---------------|--------|--------|------------------------|---------------|

| CNEN1        | 0060 | CN15IE <sup>(1)</sup>  | CN14IE  | CN13IE  | CN12IE  | CN11IE <sup>(1)</sup>  |        | CN9IE  | CN8IE                  | CN7IE <sup>(1)</sup>  | CN6IE   | CN5IE   | CN4IE  | CN3IE         | CN2IE  | CN1IE  | CN0IE                  | 0000          |

| CNEN2        | 0062 | _                      | CN30IE  | CN29IE  | _       | CN27IE <sup>(1)</sup>  | _      | _      | CN24IE <sup>(1)</sup>  | CN23IE                | CN22IE  | CN21IE  | _      | _             | _      | _      | CN16IE <sup>(1)</sup>  | 0000          |

| CNPU1        | 0068 | CN15PUE <sup>(1)</sup> | CN14PUE | CN13PUE | CN12PUE | CN11PUE <sup>(1)</sup> | _      | CN9PUE | CN8PUE                 | CN7PUE <sup>(1)</sup> | CN6PUE  | CN5PUE  | CN4PUE | <b>CN3PUE</b> | CN2PUE | CN1PUE | CN0PUE                 | 0000          |

| CNPU2        | 006A | _                      | CN30PUE | CN29PUE |         | CN27PUE <sup>(1)</sup> | _      | _      | CN24PUE <sup>(1)</sup> | CN23PUE               | CN22PUE | CN21PUE |        | _             | _      |        | CN16PUE <sup>(1)</sup> | 0000          |

| CNPD1        | 0070 | CN15PDE <sup>(1)</sup> | CN14PDE | CN13PDE | CN12PDE | CN11PDE <sup>(1)</sup> | _      | CN9PDE | CN8PDE                 | CN7PDE <sup>(1)</sup> | CN6PDE  | CN5PDE  | CN4PDE | CN3PDE        | CN2PDE | CN1PDE | CN0PDE                 | 0000          |

| CNPD2        | 0072 | —                      | CN30PDE | CN29PDE | _       | CN27PDE <sup>(1)</sup> | _      | _      | CN24PDE <sup>(1)</sup> | CN23PDE               | CN22PDE | CN21PDE | _      | _             | _      | _      | CN16PDE <sup>(1)</sup> | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits are not implemented in 20-pin devices.

#### TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10  | Bit 9   | Bit 8   | Bit 7 | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|--------------|------|--------|---------|---------|---------|--------|---------|---------|---------|-------|---------|---------|---------|---------|---------|---------|---------|---------------|

| INTCON1      | 0080 | NSTDIS | _       | _       | _       | _      | _       | _       | _       | _     | _       | —       | MATHERR | ADDRERR | STKERR  | OSCFAIL | —       | 0000          |

| INTCON2      | 0082 | ALTIVT | DISI    | -       | _       |        | _       | _       | _       | _     | _       | _       | _       | _       | INT2EP  | INT1EP  | INT0EP  | 0000          |

| IFS0         | 0084 | NVMIF  | -       | AD1IF   | U1TXIF  | U1RXIF | SPI1IF  | SPF1IF  | T3IF    | T2IF  | _       | _       | _       | T1IF    | OC1IF   | IC1IF   | INT0IF  | 0000          |

| IFS1         | 0086 | U2TXIF | U2RXIF  | INT2IF  | —       | _      |         |         | —       | —     |         |         | INT1IF  | CNIF    | CMIF    | MI2C1IF | SI2C1IF | 0000          |

| IFS3         | 008A | —      | RTCIF   | _       | —       | _      |         |         | —       | —     |         |         |         |         | —       | _       | —       | 0000          |

| IFS4         | 008C | —      | _       | CTMUIF  | —       | _      |         |         | HLVDIF  | —     |         |         |         | CRCIF   | U2ERIF  | U1ERIF  | —       | 0000          |

| IEC0         | 0094 | NVMIE  | _       | AD1IE   | U1TXIE  | U1RXIE | SPI1IE  | SPF1IE  | T3IE    | T2IE  |         |         |         | T1IE    | OC1IE   | IC1IE   | INT0IE  | 0000          |

| IEC1         | 0096 | U2TXIE | U2RXIE  | INT2IE  | _       | _      |         |         | —       | —     |         |         | INT1IE  | CNIE    | CMIE    | MI2C1IE | SI2C1IE | 0000          |

| IEC3         | 009A | —      | RTCIE   | -       | _       |        | _       | _       | _       | _     | _       | _       | _       | _       | _       | _       | _       | 0000          |

| IEC4         | 009C | _      | -       | CTMUIE  | _       |        | _       | _       | HLVDIE  | _     | _       | _       | _       | CRCIE   | U2ERIE  | U1ERIE  | _       | 0000          |

| IPC0         | 00A4 | —      | T1IP2   | T1IP1   | T1IP0   | _      | OC1IP2  | OC1IP1  | OC1IP0  | —     | IC1IP2  | IC1IP1  | IC1IP0  |         | INT0IP2 | INT0IP1 | INT0IP0 | 4444          |

| IPC1         | 00A6 | —      | T2IP2   | T2IP1   | T2IP0   | _      |         |         | —       | —     |         |         |         |         | —       | _       | —       | 4444          |

| IPC2         | 00A8 | —      | U1RXIP2 | U1RXIP1 | U1RXIP0 | _      | SPI1IP2 | SPI1IP1 | SPI1IP0 | —     | SPF1IP2 | SPF1IP1 | SPF1IP0 |         | T3IP2   | T3IP1   | T3IP0   | 4444          |

| IPC3         | 00AA | —      | NVMIP2  | NVMIP1  | NVMIP0  | _      |         |         | —       | —     | AD1IP2  | AD1IP1  | AD1IP0  |         | U1TXIP2 | U1TXIP1 | U1TXIP0 | 4044          |

| IPC4         | 00AC | —      | CNIP2   | CNIP1   | CNIP0   | _      | CMIP2   | CMIP1   | CMIP0   | —     | MI2C1P2 | MI2C1P1 | MI2C1P0 |         | SI2C1P2 | SI2C1P1 | SI2C1P0 | 4444          |

| IPC5         | 00AE | —      | _       | _       | —       | _      |         |         | —       | —     |         |         |         |         | INT1IP2 | INT1IP1 | INT1IP0 | 0004          |

| IPC7         | 00B2 | —      | U2TXIP2 | U2TXIP1 | U2TXIP0 | _      | U2RXIP2 | U2RXIP1 | U2RXIP0 | —     | INT2IP2 | INT2IP1 | INT2IP0 |         | —       | _       | —       | 4440          |

| IPC15        | 00C2 | —      | _       | _       | —       | _      | RTCIP2  | RTCIP1  | RTCIP0  | —     |         |         |         |         | —       | _       | —       | 0400          |

| IPC16        | 00C4 | —      | CRCIP2  | CRCIP1  | CRCIP0  |        | U2ERIP2 | U2ERIP1 | U2ERIP0 | _     | U1ERIP2 | U1ERIP1 | U1ERIP0 | -       | —       | —       | —       | 4440          |

| IPC18        | 00C8 | _      | _       | _       | —       | _      | —       | —       | —       | _     | _       | _       | _       | —       | HLVDIP2 | HLVDIP1 | HLVDIP0 | 0004          |

| IPC19        | 00CA | _      | _       | _       | _       | _      | _       | —       | _       | _     | CTMUIP2 | CTMUIP1 | CTMUIP0 | —       | _       | _       | _       | 0040          |

| INTTREG      | 00E0 | CPUIRQ | _       | VHOLD   | _       | ILR3   | ILR2    | ILR1    | ILR0    | _     | VECNUM6 | VECNUM5 | VECNUM4 | VECNUM3 | VECNUM2 | VECNUM1 | VECNUM0 | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| Vector Number | IVT Address | AIVT Address | Trap Source        |

|---------------|-------------|--------------|--------------------|

| 0             | 000004h     | 000104h      | Reserved           |

| 1             | 000006h     | 000106h      | Oscillator Failure |

| 2             | 000008h     | 000108h      | Address Error      |

| 3             | 00000Ah     | 00010Ah      | Stack Error        |

| 4             | 00000Ch     | 00010Ch      | Math Error         |

| 5             | 00000Eh     | 00010Eh      | Reserved           |

| 6             | 000010h     | 000110h      | Reserved           |

| 7             | 000012h     | 000112h      | Reserved           |

# TABLE 8-1: TRAP VECTOR DETAILS

#### TABLE 8-2: IMPLEMENTED INTERRUPT VECTORS

| had a more than the second   | Vector |             | AIVT    | Inte     | rrupt Bit Locat | ions         |

|------------------------------|--------|-------------|---------|----------|-----------------|--------------|

| Interrupt Source             | Number | IVT Address | Address | Flag     | Enable          | Priority     |

| ADC1 Conversion Done         | 13     | 00002Eh     | 00012Eh | IFS0<13> | IEC0<13>        | IPC3<6:4>    |

| Comparator Event             | 18     | 000038h     | 000138h | IFS1<2>  | IEC1<2>         | IPC4<10:8>   |

| CRC Generator                | 67     | 00009Ah     | 00019Ah | IFS4<3>  | IEC4<3>         | IPC16<14:12> |

| СТМИ                         | 77     | 0000AEh     | 0001AEh | IFS4<13> | IEC4<13>        | IPC19<6:4>   |

| External Interrupt 0         | 0      | 000014h     | 000114h | IFS0<0>  | IEC0<0>         | IPC0<2:0>    |

| External Interrupt 1         | 20     | 00003Ch     | 00013Ch | IFS1<4>  | IEC1<4>         | IPC5<2:0>    |

| External Interrupt 2         | 29     | 00004Eh     | 00014Eh | IFS1<13> | IEC1<13>        | IPC7<6:4>    |

| I2C1 Master Event            | 17     | 000036h     | 000136h | IFS1<1>  | IEC1<1>         | IPC4<6:4>    |

| I2C1 Slave Event             | 16     | 000034h     | 000134h | IFS1<0>  | IEC1<0>         | IPC4<2:0>    |

| Input Capture 1              | 1      | 000016h     | 000116h | IFS0<1>  | IEC0<1>         | IPC0<6:4>    |

| Input Change Notification    | 19     | 00003Ah     | 00013Ah | IFS1<3>  | IEC1<3>         | IPC4<14:12>  |

| HLVD High/Low-Voltage Detect | 72     | 0000A4h     | 0001A4h | IFS4<8>  | IEC4<8>         | IPC17<2:0>   |

| NVM – NVM Write Complete     | 15     | 000032h     | 000132h | IFS0<15> | IEC0<15>        | IPC3<14:12>  |

| Output Compare 1             | 2      | 000018h     | 000118h | IFS0<2>  | IEC0<2>         | IPC0<10:8>   |

| Real-Time Clock/Calendar     | 62     | 000090h     | 000190h | IFS3<14> | IEC3<14>        | IPC15<10:8>  |

| SPI1 Error                   | 9      | 000026h     | 000126h | IFS0<9>  | IEC0<9>         | IPC2<6:4>    |

| SPI1 Event                   | 10     | 000028h     | 000128h | IFS0<10> | IEC0<10>        | IPC2<10:8>   |

| Timer1                       | 3      | 00001Ah     | 00011Ah | IFS0<3>  | IEC0<3>         | IPC0<14:12>  |

| Timer2                       | 7      | 000022h     | 000122h | IFS0<7>  | IEC0<7>         | IPC1<14:12>  |

| Timer3                       | 8      | 000024h     | 000124h | IFS0<8>  | IEC0<8>         | IPC2<2:0>    |

| UART1 Error                  | 65     | 000096h     | 000196h | IFS4<1>  | IEC4<1>         | IPC16<6:4>   |

| UART1 Receiver               | 11     | 00002Ah     | 00012Ah | IFS0<11> | IEC0<11>        | IPC2<14:12>  |

| UART1 Transmitter            | 12     | 00002Ch     | 00012Ch | IFS0<12> | IEC0<12>        | IPC3<2:0>    |

| UART2 Error                  | 66     | 000098h     | 000198h | IFS4<2>  | IEC4<2>         | IPC16<10:8>  |

| UART2 Receiver               | 30     | 000050h     | 000150h | IFS1<14> | IEC1<14>        | IPC7<10:8>   |

| UART2 Transmitter            | 31     | 000052h     | 000152h | IFS1<15> | IEC1<15>        | IPC7<14:12>  |

# 9.3 Control Registers

The operation of the oscillator is controlled by three Special Function Registers (SFRs):

- OSCCON

- CLKDIV

- OSCTUN

The OSCCON register (Register 9-1) is the main control register for the oscillator. It controls clock source switching and allows the monitoring of clock sources. The Clock Divider register (Register 9-2) controls the features associated with Doze mode, as well as the postscaler for the FRC oscillator.

The FRC Oscillator Tune register (Register 9-3) allows the user to fine tune the FRC oscillator over a range of approximately  $\pm 5.25\%$ . Each bit increment or decrement changes the factory calibrated frequency of the FRC oscillator by a fixed amount.

## REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0    | R-0, HSC | R-0, HSC | R-0, HSC | U-0 | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> |

|--------|----------|----------|----------|-----|----------------------|----------------------|----------------------|

| _      | COSC2    | COSC1    | COSC0    | —   | NOSC2                | NOSC1                | NOSC0                |

| bit 15 |          |          |          |     |                      |                      | bit 8                |

| R/SO-0, HSC | U-0 | R-0, HSC <b><sup>(2)</sup></b> | U-0 | R/CO-0, HS | U-0 | R/W-0  | R/W-0 |

|-------------|-----|--------------------------------|-----|------------|-----|--------|-------|

| CLKLOCK     | —   | LOCK                           | —   | CF         | —   | SOSCEN | OSWEN |

| bit 7       |     |                                |     |            |     |        | bit 0 |

| Legend:                | CO = Clearable Only bit    |                            |                    |

|------------------------|----------------------------|----------------------------|--------------------|

| SO = Settable Only bit | HS = Hardware Settable bit | HSC = Hardware Settable/   | Clearable bit      |

| R = Readable bit       | W = Writable bit           | U = Unimplemented bit, rea | ad as '0'          |

| -n = Value at POR      | '1' = Bit is set           | '0' = Bit is cleared       | x = Bit is unknown |

bit 15 Unimplemented: Read as '0'

- bit 14-12 **COSC<2:0>:** Current Oscillator Selection bits

- 111 = 8 MHz Fast RC Oscillator with Postscaler (FRCDIV)

- 110 = 500 kHz Low-Power Fast RC Oscillator (FRC) with Postscaler (LPFRCDIV)

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (SOSC)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)

- 010 = Primary Oscillator (XT, HS, EC)

- 001 = 8 MHz FRC Oscillator with Postscaler and PLL module (FRCPLL)

- 000 = 8 MHz FRC Oscillator (FRC)

- bit 11 Unimplemented: Read as '0'

#### bit 10-8 NOSC<2:0>: New Oscillator Selection bits<sup>(1)</sup>

- 111 = 8 MHz Fast RC Oscillator with Postscaler (FRCDIV)

- 110 = 500 kHz Low-Power Fast RC Oscillator (FRC) with Postscaler (LPFRCDIV)

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (SOSC)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)

- 010 = Primary Oscillator (XT, HS, EC)

- 001 = 8 MHz FRC Oscillator with Postscaler and PLL module (FRCPLL)

- 000 = 8 MHz FRC Oscillator (FRC)

- Note 1: Reset values for these bits are determined by the FNOSC Configuration bits.

- 2: Also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

# REGISTER 16-1: SPI1STAT: SPI1 STATUS AND CONTROL REGISTER

| R/W-0      | U-0                                                                                                                                                             | R/W-0                                                                                       | U-0                | U-0               | R-0, HSC        | R-0, HSC        | R-0, HSC    |  |  |  |  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------|-------------------|-----------------|-----------------|-------------|--|--|--|--|

| SPIEN      | _                                                                                                                                                               | SPISIDL                                                                                     |                    |                   | SPIBEC2         | SPIBEC1         | SPIBEC0     |  |  |  |  |

| bit 15     |                                                                                                                                                                 |                                                                                             |                    |                   |                 |                 | bit 8       |  |  |  |  |

|            |                                                                                                                                                                 |                                                                                             |                    |                   |                 |                 |             |  |  |  |  |

| R-0,HSC    | R/C-0, HS                                                                                                                                                       | R/W-0, HSC                                                                                  | R/W-0              | R/W-0             | R/W-0           | R-0, HSC        | R-0, HSC    |  |  |  |  |

| SRMPT      | SPIROV                                                                                                                                                          | SRXMPT                                                                                      | SISEL2             | SISEL1            | SISEL0          | SPITBF          | SPIRBF      |  |  |  |  |

| bit 7      |                                                                                                                                                                 |                                                                                             |                    |                   |                 |                 | bit (       |  |  |  |  |

|            |                                                                                                                                                                 |                                                                                             |                    |                   |                 |                 |             |  |  |  |  |

| Legend:    |                                                                                                                                                                 | U = Unimplemente                                                                            | d bit, read as '0' | HSC = Hardwa      | re Settable/Cle | earable bit     |             |  |  |  |  |

| R = Reada  | ble bit                                                                                                                                                         | W = Writable bit                                                                            |                    | H = Hardware      | Settable bit    | C = Clearable   | e bit       |  |  |  |  |

| -n = Value | at POR                                                                                                                                                          | '1' = Bit is set                                                                            |                    | '0' = Bit is clea | red             | x = Bit is unkr | nown        |  |  |  |  |

|            |                                                                                                                                                                 |                                                                                             |                    |                   |                 |                 |             |  |  |  |  |

| bit 15     | SPIEN: SPI1                                                                                                                                                     |                                                                                             |                    | 1 CDI1 and CO     | <u>.</u>        | + n:no          |             |  |  |  |  |

|            | <ul> <li>1 = Enables</li> <li>0 = Disables</li> </ul>                                                                                                           | module and configi                                                                          | lies SCK1, SDU     | 1, SDIT and SS    | r as senai por  | t pins          |             |  |  |  |  |

| bit 14     |                                                                                                                                                                 | nted: Read as '0'                                                                           |                    |                   |                 |                 |             |  |  |  |  |

| bit 13     | -                                                                                                                                                               | op in Idle Mode bit                                                                         |                    |                   |                 |                 |             |  |  |  |  |

|            |                                                                                                                                                                 | ues module opera                                                                            | ion when device    | enters Idle mod   | le              |                 |             |  |  |  |  |

|            |                                                                                                                                                                 | s module operation                                                                          |                    |                   |                 |                 |             |  |  |  |  |

| bit 12-11  | Unimplemen                                                                                                                                                      | nted: Read as '0'                                                                           |                    |                   |                 |                 |             |  |  |  |  |

| bit 10-8   | SPIBEC<2:0                                                                                                                                                      | >: SPI1 Buffer Eler                                                                         | ment Count bits (  | valid in Enhanc   | ed Buffer mod   | e)              |             |  |  |  |  |

|            | <u>Master mode:</u><br>Number of SPI transfers are pending.                                                                                                     |                                                                                             |                    |                   |                 |                 |             |  |  |  |  |

|            |                                                                                                                                                                 | -                                                                                           | naing.             |                   |                 |                 |             |  |  |  |  |

|            | Slave mode:<br>Number of S                                                                                                                                      | PI transfers are un                                                                         | read.              |                   |                 |                 |             |  |  |  |  |

| bit 7      |                                                                                                                                                                 | t Register (SPI1SR                                                                          |                    | d in Enhanced B   | uffer mode)     |                 |             |  |  |  |  |

|            |                                                                                                                                                                 | ift register is empty                                                                       |                    |                   | ,               |                 |             |  |  |  |  |

|            |                                                                                                                                                                 | ift register is not en                                                                      |                    |                   |                 |                 |             |  |  |  |  |

| bit 6      | SPIROV: Receive Overflow Flag bit                                                                                                                               |                                                                                             |                    |                   |                 |                 |             |  |  |  |  |

|            | <ul> <li>1 = A new byte/word is completely received and discarded</li> <li>The user software has not read the previous data in the SPI1BUF register.</li> </ul> |                                                                                             |                    |                   |                 |                 |             |  |  |  |  |

|            |                                                                                                                                                                 | r software has not i<br>flow has occurred                                                   | read the previous  | data in the SPI   | 1BUF register   | -<br>-          |             |  |  |  |  |

| bit 5      |                                                                                                                                                                 |                                                                                             | hit (valid in Enha | anced Buffer mo   | de)             |                 |             |  |  |  |  |

| bit 0      |                                                                                                                                                                 | SRXMPT: Receive FIFO Empty bit (valid in Enhanced Buffer mode)<br>1 = Receive FIFO is empty |                    |                   |                 |                 |             |  |  |  |  |

|            |                                                                                                                                                                 | FIFO is not empty                                                                           |                    |                   |                 |                 |             |  |  |  |  |

| bit 4-2    | SISEL<2:0>:                                                                                                                                                     | SPI1 Buffer Interr                                                                          | upt Mode bits (va  | lid in Enhanced   | Buffer mode)    |                 |             |  |  |  |  |

|            |                                                                                                                                                                 | upt when the SPI1                                                                           |                    |                   |                 |                 |             |  |  |  |  |

|            |                                                                                                                                                                 | upt when the last b                                                                         |                    |                   |                 |                 |             |  |  |  |  |

|            |                                                                                                                                                                 | upt when the last b<br>upt when one data b                                                  |                    |                   |                 | •               | e open spot |  |  |  |  |

|            |                                                                                                                                                                 | upt when the SPI1                                                                           |                    |                   |                 |                 | o opon opor |  |  |  |  |

|            |                                                                                                                                                                 | upt when the SPI1                                                                           |                    |                   |                 |                 |             |  |  |  |  |

|            | 001 = Interrupt when data is available in receive buffer (SRMPT bit is set)                                                                                     |                                                                                             |                    |                   |                 |                 |             |  |  |  |  |

|            | 000 = Interrupt when the last data in the receive buffer is read; as a result, the buffer is empty (SRXMPT bit is set)                                          |                                                                                             |                    |                   |                 |                 |             |  |  |  |  |

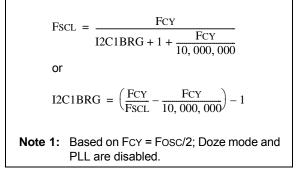

## 17.3 Setting Baud Rate When Operating as a Bus Master

To compute the Baud Rate Generator (BRG) reload value, use Equation 17-1.

# EQUATION 17-1: COMPUTING BAUD RATE RELOAD VALUE<sup>(1)</sup>

## TABLE 17-1: I<sup>2</sup>C<sup>™</sup> CLOCK RATES<sup>(1)</sup>

## 17.4 Slave Address Masking

The I2C1MSK register (Register 17-3) designates address bit positions as "don't care" for both 7-Bit and 10-Bit Addressing modes. Setting a particular bit location (= 1) in the I2C1MSK register causes the slave module to respond whether the corresponding address bit value is '0' or '1'. For example, when I2C1MSK is set to '00100000', the slave module will detect both addresses: '0000000' and '00100000'.

To enable address masking, the Intelligent Peripheral Management Interface (IPMI) must be disabled by clearing the IPMIEN bit (I2C1CON<11>).

**Note:** As a result of changes in the I<sup>2</sup>C protocol, the addresses in Table 17-2 are reserved and will not be Acknowledged in Slave mode. This includes any address mask settings that include any of these addresses.

| Required       |        | I2C1B     | Actual        |           |

|----------------|--------|-----------|---------------|-----------|

| System<br>FscL | FCY    | (Decimal) | (Hexadecimal) | FSCL      |

| 100 kHz        | 16 MHz | 157       | 9D            | 100 kHz   |

| 100 kHz        | 8 MHz  | 78        | 4E            | 100 kHz   |

| 100 kHz        | 4 MHz  | 39        | 27            | 99 kHz    |

| 400 kHz        | 16 MHz | 37        | 25            | 404 kHz   |

| 400 kHz        | 8 MHz  | 18        | 12            | 404 kHz   |

| 400 kHz        | 4 MHz  | 9         | 9             | 385 kHz   |

| 400 kHz        | 2 MHz  | 4         | 4             | 385 kHz   |

| 1 MHz          | 16 MHz | 13        | D             | 1.026 MHz |

| 1 MHz          | 8 MHz  | 6         | 6             | 1.026 MHz |

| 1 MHz          | 4 MHz  | 3         | 3             | 0.909 MHz |

Note 1: Based on Fcy = Fosc/2; Doze mode and PLL are disabled;

#### TABLE 17-2: I<sup>2</sup>C<sup>™</sup> RESERVED ADDRESSES<sup>(1)</sup>

| Slave<br>Address | R/W<br>Bit | Description                            |

|------------------|------------|----------------------------------------|

| 0000 000         | 0          | General Call Address <sup>(2)</sup>    |

| 0000 000         | 1          | Start Byte                             |

| 0000 001         | x          | Cbus Address                           |

| 0000 010         | x          | Reserved                               |

| 0000 011         | x          | Reserved                               |

| 0000 1xx         | x          | HS Mode Master Code                    |

| 1111 1xx         | x          | Reserved                               |

| 1111 0xx         | x          | 10-Bit Slave Upper Byte <sup>(3)</sup> |

Note 1: The address bits listed here will never cause an address match, independent of the address mask settings.

- 2: The address will be Acknowledged only if GCEN = 1.

- 3: A match on this address can only occur on the upper byte in 10-Bit Addressing mode.

#### REGISTER 17-3: I2C1MSK: I2C1 SLAVE MODE ADDRESS MASK REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-------|-------|

| —      |     |     |     | —   |     | AMSK9 | AMSK8 |

| bit 15 |     | -   | -   |     |     |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| AMSK7 | AMSK6 | AMSK5 | AMSK4 | AMSK3 | AMSK2 | AMSK1 | AMSK0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 15-10 Unimplemented: Read as '0'

bit 9-0

AMSK<9:0>: Mask for Address Bit x Select bits

1 = Enable masking for bit x of incoming message address; bit match is not required in this position

0 = Disable masking for bit x; bit match is required in this position

#### REGISTER 17-4: PADCFG1: PAD CONFIGURATION CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | _   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-0    | R/W-0                    | R/W-0                      | R/W-0                      | U-0   |

|-------|-----|-----|----------|--------------------------|----------------------------|----------------------------|-------|

| —     | —   | —   | SMBUSDEL | OC1TRIS <sup>(2,3)</sup> | RTSECSEL1 <sup>(1,3)</sup> | RTSECSEL0 <sup>(1,3)</sup> | —     |

| bit 7 |     |     |          |                          |                            |                            | bit 0 |

| Legend:           |                  |                                |                    |

|-------------------|------------------|--------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as | s 'O'              |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared           | x = Bit is unknown |

bit 15-5 Unimplemented: Read as '0'

bit 4 SMBUSDEL: SMBus SDA Input Delay Select bit

1 = The  $I^2C$  module is configured for a longer SMBus input delay (nominal 300 ns delay)

0 = The 1<sup>2</sup>C module is configured for a legacy input delay (nominal 150 ns delay)

#### bit 0 Unimplemented: Read as '0'

Note 1: To enable the actual RTCC output, the RTCOE (RCFGCAL<10>) bit needs to be set.

2: To enable the actual OC1 output, the OCPWM1 module has to be enabled.

**3:** Bits<3:1> are described in related chapters.

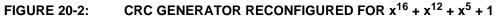

#### 20.1 User Interface

#### 20.1.1 DATA INTERFACE

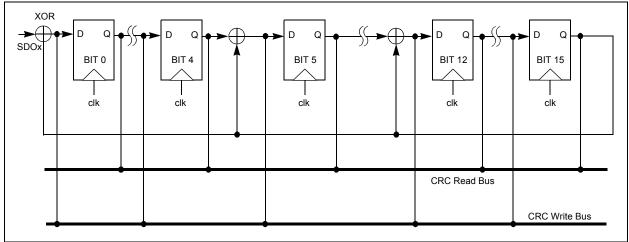

To start serial shifting, a value of '1' must be written to the CRCGO bit.

The module incorporates a FIFO that is 8-level deep when PLEN<3:0> > 7 and 16-deep, otherwise. The data for which the CRC is to be calculated must first be written into the FIFO. The smallest data element that can be written into the FIFO is one byte.

For example, if PLEN = 5, then the size of the data is PLEN + 1 = 6. The data must be written as follows:

```

data<5:0> = crc_input<5:0>

data<7:6> = bxx

```

Once data is written into the CRCWDAT MSb (as defined by PLEN), the value of the VWORD bits (CRCCON<12:8>) increments by one. The serial shifter starts shifting data into the CRC engine when CRCGO = 1 and VWORD<4:0> > 0. When the Most Significant bit (MSb) is shifted out, the VWORD bits decrement by one. The serial shifter continues shifting until the VWORD bits reach zero. Therefore, for a given value of PLEN, it will take (PLEN + 1) \* VWORD number of clock cycles to complete the CRC calculations.

When the VWORD bits reach 8 (or 16), the CRCFUL bit will be set. When the VWORD bits reach 0, the CRCMPT bit will be set.

To continually feed data into the CRC engine, the recommended mode of operation is to initially "prime" the FIFO with a sufficient number of words so no interrupt is generated before the next word can be written. Once that is done, start the CRC by setting the CRCGO bit to '1'. From that point onward, the VWORD bits should be polled. If they read less than 8 or 16, another word can be written into the FIFO.

To empty words already written into a FIFO, the CRCGO bit must be set to '1' and the CRC shifter allowed to run until the CRCMPT bit is set.

Also, to get the correct CRC reading, it will be necessary to wait for the CRCMPT bit to go high before reading the CRCWDAT register.

If a word is written when the CRCFUL bit is set, the VWORD Pointer will roll over to 0. The hardware will then behave as if the FIFO is empty. However, the condition to generate an interrupt will not be met; therefore, no interrupt will be generated (see **Section 20.1.2 "Interrupt Operation"**).

At least one instruction cycle must pass after a write to CRCWDAT before a read of the VWORD bits is done.

#### 20.1.2 INTERRUPT OPERATION

When the VWORD<4:0> bits make a transition from a value of '1' to '0', an interrupt will be generated.

#### 20.2 Operation in Power Save Modes

#### 20.2.1 SLEEP MODE

If Sleep mode is entered while the module is operating, the module will be suspended in its current state until clock execution resumes.

#### 20.2.2 IDLE MODE

To continue full module operation in Idle mode, the CSIDL bit must be cleared prior to entry into the mode.

If CSIDL = 1, the module will behave the same way as it does in Sleep mode; pending interrupt events will be passed on, even though the module clocks are not available.

| U-0          | U-0                                                                                                                                                                         | U-0                                                                             | U-0                                                                                 | U-0               | U-0              | U-0             | U-0   |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------|------------------|-----------------|-------|--|--|--|--|--|

| _            | —                                                                                                                                                                           | —                                                                               | _                                                                                   | —                 | —                | —               |       |  |  |  |  |  |

| bit 15       | ·                                                                                                                                                                           |                                                                                 |                                                                                     |                   |                  |                 | bit 8 |  |  |  |  |  |

|              |                                                                                                                                                                             |                                                                                 |                                                                                     |                   |                  |                 |       |  |  |  |  |  |

| R/W-0        | R/W-0                                                                                                                                                                       | R/W-0                                                                           | R/W-0                                                                               | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |  |

| CVREN        | CVROE                                                                                                                                                                       | CVRR                                                                            | CVRSS                                                                               | CVR3              | CVR2             | CVR1            | CVR0  |  |  |  |  |  |

| bit 7        |                                                                                                                                                                             |                                                                                 |                                                                                     |                   |                  |                 | bit ( |  |  |  |  |  |

| Legend:      |                                                                                                                                                                             |                                                                                 |                                                                                     |                   |                  |                 |       |  |  |  |  |  |

| R = Readab   | le bit                                                                                                                                                                      | W = Writable                                                                    | oit                                                                                 | U = Unimplem      | nented bit, read | d as '0'        |       |  |  |  |  |  |

| -n = Value a | t POR                                                                                                                                                                       | '1' = Bit is set                                                                |                                                                                     | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |  |  |  |  |  |

|              |                                                                                                                                                                             |                                                                                 |                                                                                     |                   |                  |                 |       |  |  |  |  |  |

| bit 15-8     | Unimplemen                                                                                                                                                                  | ted: Read as '0                                                                 | )'                                                                                  |                   |                  |                 |       |  |  |  |  |  |

| bit 7        |                                                                                                                                                                             | CVREN: Comparator Voltage Reference Enable bit                                  |                                                                                     |                   |                  |                 |       |  |  |  |  |  |

|              | 1 = CVREF circuit is powered on                                                                                                                                             |                                                                                 |                                                                                     |                   |                  |                 |       |  |  |  |  |  |

|              | 0 = CVREF circuit is powered down                                                                                                                                           |                                                                                 |                                                                                     |                   |                  |                 |       |  |  |  |  |  |

| bit 6        | CVROE: Comparator VREF Output Enable bit                                                                                                                                    |                                                                                 |                                                                                     |                   |                  |                 |       |  |  |  |  |  |

|              | 1 = CVREF voltage level is output on CVREF pin                                                                                                                              |                                                                                 |                                                                                     |                   |                  |                 |       |  |  |  |  |  |

| 6.4 <i>F</i> | 0 = CVREF voltage level is disconnected from CVREF pin                                                                                                                      |                                                                                 |                                                                                     |                   |                  |                 |       |  |  |  |  |  |

| bit 5        | CVRR: Comparator VREF Range Selection bit                                                                                                                                   |                                                                                 |                                                                                     |                   |                  |                 |       |  |  |  |  |  |

|              | <ul> <li>1 = CVRSRC range should be 0 to 0.625 CVRSRC with CVRSRC/24 step size</li> <li>0 = CVRSRC range should be 0.25 to 0.719 CVRSRC with CVRSRC/32 step size</li> </ul> |                                                                                 |                                                                                     |                   |                  |                 |       |  |  |  |  |  |

| bit 4        |                                                                                                                                                                             | •                                                                               |                                                                                     |                   |                  | F               |       |  |  |  |  |  |

|              | CVRSS: Comparator VREF Source Selection bit<br>1 = Comparator reference source, CVRSRC = VREF+ – VREF-                                                                      |                                                                                 |                                                                                     |                   |                  |                 |       |  |  |  |  |  |

|              | 0 = Comparator reference source, CVRsRc = AVDD – AVss                                                                                                                       |                                                                                 |                                                                                     |                   |                  |                 |       |  |  |  |  |  |

| bit 3-0      | <b>CVR3:CVR0:</b> Comparator VREF Value Selection $0 \le CVR<3:0> \le 15$ bits                                                                                              |                                                                                 |                                                                                     |                   |                  |                 |       |  |  |  |  |  |

|              | When CVRR = 1 and CVRSS = 0:<br>CVREF = (CVR<3:0>/24) * (CVRSRC)                                                                                                            |                                                                                 |                                                                                     |                   |                  |                 |       |  |  |  |  |  |

|              |                                                                                                                                                                             | R<3:0>/24) * (C                                                                 | VRSRC)                                                                              |                   |                  |                 |       |  |  |  |  |  |

|              | CVREF = (CVI<br><u>When CVRR</u>                                                                                                                                            | R<3:0>/24) * (C<br><u>= 0 and CVRS</u><br>CVRSRC) + (CV                         | <u>S = 0:</u>                                                                       | (CVRSRC)          |                  |                 |       |  |  |  |  |  |

|              | CVREF = (CVI<br>When CVRR<br>CVREF = 1/4 (<br>When CVRR                                                                                                                     | <u>= 0 and CVRS</u><br>CVRSRC) + (CV<br>= 1 and CVRS                            | <u>S = 0:</u><br>/R<3:0>/32) * (<br><u>S = 1:</u>                                   |                   |                  |                 |       |  |  |  |  |  |

|              | CVREF = (CVI<br>When CVRR<br>CVREF = 1/4 (<br>When CVRR<br>CVREF = ((CV                                                                                                     | <u>= 0 and CVRS</u><br>CVRSRC) + (CV<br><u>= 1 and CVRS</u><br>(R<3:0>/24) * (0 | <u>S = 0:</u><br>/R<3:0>/32) * (<br><u>S = 1:</u><br>CVRSRC)) + VR                  |                   |                  |                 |       |  |  |  |  |  |

|              | CVREF = (CVI<br>When CVRR<br>CVREF = 1/4 (<br><u>When CVRR</u><br>CVREF = ((CV<br>When CVRR                                                                                 | <u>= 0 and CVRS</u><br>CVRSRC) + (CV<br>= 1 and CVRS                            | <u>S = 0:</u><br>/R<3:0>/32) * (<br><u>S = 1:</u><br>CVRSRC)) + VR<br><u>S = 1:</u> | EF-               |                  |                 |       |  |  |  |  |  |

| R/P-1               | R/P-1                  | R/P-1                                | R/P-1                        | R/P-1                          | U-0             | R/P-1           | R/P-1             |

|---------------------|------------------------|--------------------------------------|------------------------------|--------------------------------|-----------------|-----------------|-------------------|

| MCLRE <sup>(2</sup> | ) BORV1 <sup>(3)</sup> | BORV0 <sup>(3)</sup>                 | I2C1SEL <sup>(1)</sup>       | PWRTEN                         | _               | BOREN1          | BOREN0            |

| bit 7               | ·                      |                                      |                              |                                |                 |                 | bit 0             |

|                     |                        |                                      |                              |                                |                 |                 |                   |

| Legend:             |                        |                                      |                              |                                |                 |                 |                   |

| R = Reada           | able bit               | P = Program                          | nable bit                    | U = Unimplem                   | nented bit, rea | d as '0'        |                   |

| -n = Value          | at POR                 | '1' = Bit is set                     |                              | '0' = Bit is clea              | ared            | x = Bit is unkr | nown              |

| bit 7               | MCLRE: MCL             | <br>R Pin Enable b                   | <sub>it</sub> (2)            |                                |                 |                 |                   |

| 2                   |                        | is enabled; RA                       |                              | isabled                        |                 |                 |                   |

|                     |                        | pin is enabled;                      |                              |                                |                 |                 |                   |

| bit 6-5             | BORV<1:0>:             | Brown-out Rese                       | et Enable bits <sup>(3</sup> | )                              |                 |                 |                   |

|                     |                        | ut Reset is set t                    | o the lowest vo              | oltage                         |                 |                 |                   |

|                     | 10 <b>= Brown-o</b> u  |                                      |                              |                                |                 |                 |                   |

|                     |                        | ut Reset is set t<br>/er Brown-out F |                              |                                |                 |                 |                   |

| bit 4               |                        | ernate I2C1 Pin                      |                              | 00110 2.0 V                    |                 |                 |                   |

| DIL 4               |                        | ocation for SCL                      |                              |                                |                 |                 |                   |

|                     |                        | cation for SCL1                      |                              |                                |                 |                 |                   |

| bit 3               | PWRTEN: Po             | wer-up Timer E                       | nable bit                    |                                |                 |                 |                   |

|                     | 0 = PWRT is c          | disabled                             |                              |                                |                 |                 |                   |

|                     | 1 = PWRT is e          | enabled                              |                              |                                |                 |                 |                   |

| bit 2               | Unimplement            | ted: Read as '0                      | ,                            |                                |                 |                 |                   |

| bit 1-0             | BOREN<1:0>             | : Brown-out Re                       | set Enable bits              |                                |                 |                 |                   |

|                     |                        |                                      |                              | re; SBOREN bit                 |                 |                 |                   |

|                     |                        |                                      | •                            |                                |                 | Sleep; SBOREN   | l bit is disabled |

|                     |                        |                                      |                              | SBOREN bit se<br>re; SBOREN bi | 0               |                 |                   |

| Note 1:             | Applies only to 2      |                                      |                              | -,                             |                 |                 |                   |

|                     | The MCLRE fuse         | •                                    | nanged when u                | sing the Vpp-B:                | ased ICSP™ i    | mode entry. Thi | s prevents a      |

|                     | user from accide       |                                      |                              |                                |                 |                 |                   |

| 3.                  | Refer to Section       | 29.0 Electrical                      | Characteristics              | for the BOR w                  | oltanes         |                 |                   |

3: Refer to Section 29.0, Electrical Characteristics for the BOR voltages.

#### TABLE 29-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD) (CONTINUED)

| DC CHARACTERISTICS         |                        |     | $ \begin{array}{ll} \mbox{Standard Operating Conditions: 1.8V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array} $ |        |      |               |  |

|----------------------------|------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|---------------|--|

| Parameter No.              | Typical <sup>(1)</sup> | Max | Units Conditions                                                                                                                                                                                                                                                               |        |      |               |  |

| IDD Current <sup>(2)</sup> | •                      |     | •                                                                                                                                                                                                                                                                              | •      |      |               |  |

| DC31                       |                        | 28  |                                                                                                                                                                                                                                                                                | -40°C  |      | LPRC (31 kHz) |  |

| DC31a                      |                        | 28  | μΑ                                                                                                                                                                                                                                                                             | +25°C  | 1.8V |               |  |

| DC31b                      | 8                      | 28  |                                                                                                                                                                                                                                                                                | +60°C  |      |               |  |

| DC31c                      |                        | 28  |                                                                                                                                                                                                                                                                                | +85°C  |      |               |  |

| DC31d                      |                        | 55  |                                                                                                                                                                                                                                                                                | -40°C  |      |               |  |

| DC31e                      |                        | 55  |                                                                                                                                                                                                                                                                                | +25°C  |      |               |  |

| DC31f                      | 15                     | 55  | μA                                                                                                                                                                                                                                                                             | +60°C  | 3.3V |               |  |