# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 24                                                                            |

| Program Memory Size        | 8KB (2.75K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1.5K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 9x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 28-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f08ka102t-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

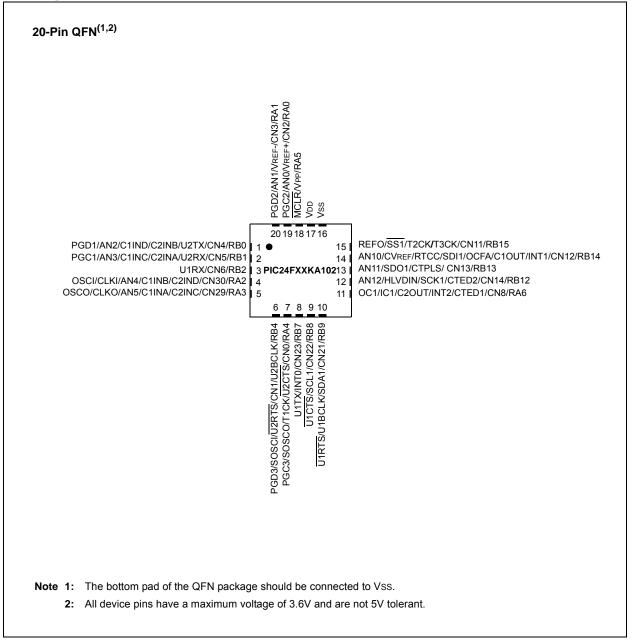

### **Pin Diagrams (Continued)**

FIGURE 2-1:

### 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT MICROCONTROLLERS

### 2.1 Basic Connection Requirements

Getting started with the PIC24F16KA102 family family of 16-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVss pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

VCAP pins (see Section 2.4 "Voltage Regulator Pin (VCAP)")

These pins must also be connected if they are being used in the end application:

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for analog modules is implemented

**Note:** The AVDD and AVss pins must always be connected, regardless of whether any of the analog modules are being used.

The minimum mandatory connections are shown in Figure 2-1.

#### **MINIMUM CONNECTIONS** C2<sup>(2)</sup> Vdd ۷DD Vss ŹR1 R2 MCI R VCAP (1)C1 PIC24FXXKXX<sup>(3)</sup> Ī VDD Vss C6<sup>(2)</sup>-C3(2) Vdd Vss AVDD AVSS 9 /SS C4(2) C5<sup>(2)</sup>

RECOMMENDED

### Key (all values are recommendations):

C1 through C6: 0.1  $\mu\text{F},$  20V ceramic

C7: 10 µF, 16V tantalum or ceramic

R1: 10 kΩ

R2: 100Ω to 470Ω

- Note 1: See Section 2.4 "Voltage Regulator Pin (VCAP)" for explanation of VCAP pin connections.

- 2: The example shown is for a PIC24F device with five VDD/VSs and AVDD/AVSs pairs. Other devices may have more or less pairs; adjust the number of decoupling capacitors appropriately.

- **3:** Some PIC24F K parts do not have a regulator.

### 3.0 CPU

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the CPU, refer to the *"PIC24F Family Reference Manual"*, Section 2. "CPU" (DS39703).

The PIC24F CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set and a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M instructions of user program memory space. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the REPEAT instructions, which are interruptible at any point.

PIC24F devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can act as a data, address or address offset register. The 16<sup>th</sup> working register (W15) operates as a Software Stack Pointer (SSP) for interrupts and calls.

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K word boundary of either program memory or data EEPROM memory defined by the 8-bit Program Space Visibility Page Address (PSVPAG) register. The program to data space mapping feature lets any instruction access program space as if it were data space.

The Instruction Set Architecture (ISA) has been significantly enhanced beyond that of the PIC18, but maintains an acceptable level of backward compatibility. All PIC18 instructions and addressing modes are supported, either directly, or through simple macros. Many of the ISA enhancements have been driven by compiler efficiency needs.

The core supports Inherent (no operand), Relative, Literal, Memory Direct and three groups of addressing modes. All modes support Register Direct and various Register Indirect modes. Each group offers up to seven addressing modes. Instructions are associated with predefined addressing modes depending upon their functional requirements. For most instructions, the core is capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing trinary operations (that is, A + B = C) to be executed in a single cycle.

A high-speed, 17-bit by 17-bit multiplier has been included to significantly enhance the core arithmetic capability and throughput. The multiplier supports Signed, Unsigned and Mixed mode, 16-bit by 16-bit or 8-bit by 8-bit integer multiplication. All multiply instructions execute in a single cycle.

The 16-bit ALU has been enhanced with integer divide assist hardware that supports an iterative non-restoring divide algorithm. It operates in conjunction with the REPEAT instruction looping mechanism and a selection of iterative divide instructions to support 32-bit (or 16-bit), divided by 16-bit integer signed and unsigned division. All divide operations require 19 cycles to complete but are interruptible at any cycle boundary.

The PIC24F has a vectored exception scheme with up to eight sources of non-maskable traps and up to 118 interrupt sources. Each interrupt source can be assigned to one of seven priority levels.

A block diagram of the CPU is illustrated in Figure 3-1.

### 3.1 Programmer's Model

Figure 3-2 displays the programmer's model for the PIC24F. All registers in the programmer's model are memory mapped and can be manipulated directly by instructions.

Table 3-1 provides a description of each register. All registers associated with the programmer's model are memory mapped.

| IADLL        | <b>-</b> -J. |        |                    |        |        |        |        |        |             |               |           |             |                |              |             |       |       |

|--------------|--------------|--------|--------------------|--------|--------|--------|--------|--------|-------------|---------------|-----------|-------------|----------------|--------------|-------------|-------|-------|

| File<br>Name | Addr         | Bit 15 | Bit 14             | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8       | Bit 7         | Bit 6     | Bit 5       | Bit 4          | Bit 3        | Bit 2       | Bit 1 | Bit 0 |

| WREG0        | 0000         |        | Working Register 0 |        |        |        |        |        |             |               |           |             |                |              |             |       |       |

| WREG1        | 0002         |        | Working Register 1 |        |        |        |        |        |             |               |           |             |                |              |             |       |       |

| WREG2        | 0004         |        | Working Register 2 |        |        |        |        |        |             |               |           |             |                |              |             |       |       |

| WREG3        | 0006         |        |                    |        |        |        |        |        | Working I   | Register 3    |           |             |                |              |             |       |       |

| WREG4        | 0008         |        |                    |        |        |        |        |        | Working I   | Register 4    |           |             |                |              |             |       |       |

| WREG5        | 000A         |        |                    |        |        |        |        |        | Working I   | Register 5    |           |             |                |              |             |       |       |

| WREG6        | 000C         |        |                    |        |        |        |        |        | Working I   | Register 6    |           |             |                |              |             |       |       |

| WREG7        | 000E         |        |                    |        |        |        |        |        | Working I   | Register 7    |           |             |                |              |             |       |       |

| WREG8        | 0010         |        |                    |        |        |        |        |        | Working I   | Register 8    |           |             |                |              |             |       |       |

| WREG9        | 0012         |        |                    |        |        |        |        |        | Working I   | Register 9    |           |             |                |              |             |       |       |

| WREG10       | 0014         |        |                    |        |        |        |        |        | Working F   | Register 10   |           |             |                |              |             |       |       |

| WREG11       | 0016         |        |                    |        |        |        |        |        | Working F   | Register 11   |           |             |                |              |             |       |       |

| WREG12       | 0018         |        |                    |        |        |        |        |        | Working F   | Register 12   |           |             |                |              |             |       |       |

| WREG13       | 001A         |        |                    |        |        |        |        |        | Working F   | Register 13   |           |             |                |              |             |       |       |

| WREG14       | 001C         |        |                    |        |        |        |        |        | Working F   | Register 14   |           |             |                |              |             |       |       |

| WREG15       | 001E         |        |                    |        |        |        |        |        | Working F   | Register 15   |           |             |                |              |             |       |       |

| SPLIM        | 0020         |        |                    |        |        |        |        | Stack  | Pointer Lin | nit Value Re  | egister   |             |                |              |             |       |       |

| PCL          | 002E         |        |                    |        |        |        |        | Progra | m Counter   | Low Byte R    | egister   |             |                |              |             |       |       |

| PCH          | 0030         | _      | _                  | _      | _      | _      | _      | _      | _           |               |           | Progra      | m Counter      | Register Hig | gh Byte     |       |       |

| TBLPAG       | 0032         | _      | _                  | _      | _      | _      | _      | _      | _           |               |           | Table M     | lemory Pag     | e Address F  | Register    |       |       |

| PSVPAG       | 0034         | —      | _                  | _      | _      | —      | —      | _      | —           |               | F         | Program Spa | ace Visibility | Page Addr    | ess Registe | er    |       |

| RCOUNT       | 0036         |        |                    |        |        |        |        | REP    | EAT Loop C  | Counter Reg   | jister    |             |                |              |             |       |       |

| SR           | 0042         | —      | —                  | _      | —      | —      | —      |        | DC          | IPL2          | IPL1      | IPL0        | RA             | N            | OV          | Z     | С     |

| CORCON       | 0044         | _      | _                  | _      | —      | —      | —      | _      | —           | _             | —         |             | _              | IPL3         | PSV         | —     | —     |

| DISICNT      | 0052         | _      | _                  |        |        |        |        |        | Disab       | le Interrupts | Counter R | egister     |                |              |             |       |       |

|              |              |        |                    |        |        |        |        |        |             |               |           |             |                |              |             |       |       |

#### TABLE 4-3: **CPU CORE REGISTERS MAP**

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All

xxxx

### REGISTER 5-1: NVMCON: FLASH MEMORY CONTROL REGISTER

| R/SO-0, HC | R/W-0 | R/W-0 | R/W-0                  | U-0 | U-0 | U-0 | U-0   |

|------------|-------|-------|------------------------|-----|-----|-----|-------|

| WR         | WREN  | WRERR | PGMONLY <sup>(4)</sup> | —   | —   | —   | —     |

| bit 15     |       |       |                        |     |     |     | bit 8 |

| U-0   | R/W-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|-------|-------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| —     | ERASE | NVMOP5 <sup>(1)</sup> | NVMOP4 <sup>(1)</sup> | NVMOP3 <sup>(1)</sup> | NVMOP2 <sup>(1)</sup> | NVMOP1 <sup>(1)</sup> | NVMOP0 <sup>(1)</sup> |

| bit 7 |       |                       |                       |                       |                       |                       | bit 0                 |

| Legend:              | SO = Settable Only bit | HC = Hardware Clearat  | ole bit          |  |

|----------------------|------------------------|------------------------|------------------|--|

| -n = Value at POR    | '1' = Bit is set       | R = Readable bit       | W = Writable bit |  |

| '0' = Bit is cleared | x = Bit is unknown     | U = Unimplemented bit, | , read as '0'    |  |

bit 15 WR: Write Control bit

- 1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the bit is cleared by hardware once the operation is complete

- 0 = Program or erase operation is complete and inactive

### bit 14 WREN: Write Enable bit

- 1 = Enable Flash program/erase operations

- 0 = Inhibit Flash program/erase operations

- bit 13 WRERR: Write Sequence Error Flag bit

- 1 = An improper program or erase sequence attempt or termination has occurred (bit is set automatically on any set attempt of the WR bit)

- 0 = The program or erase operation completed normally

- bit 12 **PGMONLY:** Program Only Enable bit<sup>(4)</sup>

- bit 11-7 Unimplemented: Read as '0'

- bit 6 ERASE: Erase/Program Enable bit

- 1 = Perform the erase operation specified by NVMOP<5:0> on the next WR command

- 0 = Perform the program operation specified by NVMOP<5:0> on the next WR command

- bit 5-0 NVMOP<5:0>: Programming Operation Command Byte bits<sup>(1)</sup>

Erase Operations (when ERASE bit is '1'):

- 1010xx = Erase entire boot block (including code-protected boot block)<sup>(2)</sup>

- 1001xx = Erase entire memory (including boot block, configuration block, general block)<sup>(2)</sup>

- 011010 = Erase 4 rows of Flash memory<sup>(3)</sup>

- 011001 = Erase 2 rows of Flash memory(3)

- 011000 = Erase 1 row of Flash memory<sup>(3)</sup>

- 0101xx = Erase entire configuration block (except code protection bits)

- 0100xx = Erase entire data EEPROM<sup>(4)</sup>

- 0011xx = Erase entire general memory block programming operations

- 0001xx = Write 1 row of Flash memory (when ERASE bit is '0')(3)

- **Note 1:** All other combinations of NVMOP<5:0> are no operation.

- 2: Available in ICSP<sup>™</sup> mode only. Refer to device programming specification.

- 3: The address in the Table Pointer decides which rows will be erased.

- 4: This bit is used only while accessing data EEPROM.

### EXAMPLE 5-5: INITIATING A PROGRAMMING SEQUENCE – ASSEMBLY LANGUAGE CODE

| DISI | #5          | ; | Block all interrupts<br>for next 5 instructions |

|------|-------------|---|-------------------------------------------------|

| MOV  | #0x55, W0   |   |                                                 |

| MOV  | W0, NVMKEY  | ; | Write the 55 key                                |

| MOV  | #0xAA, W1   | ; |                                                 |

| MOV  | W1, NVMKEY  | ; | Write the AA key                                |

| BSET | NVMCON, #WR | ; | Start the erase sequence                        |

| NOP  |             | ; | 2 NOPs required after setting WR                |

| NOP  |             | ; |                                                 |

| BTSC | NVMCON, #15 | ; | Wait for the sequence to be completed           |

| BRA  | \$-2        | ; |                                                 |

|      |             |   |                                                 |

### EXAMPLE 5-6: INITIATING A PROGRAMMING SEQUENCE – 'C' LANGUAGE CODE

| // C example using MPLAB C30 |                                                 |

|------------------------------|-------------------------------------------------|

| asm("DISI #5");              | // Block all interrupts for next 5 instructions |

| builtin_write_NVM();         | // Perform unlock sequence and set WR           |

| REGISTER           | 8-4: INICC                                                                          | JNZ: INTERR                                                                                                                                        | UPI CONTI                                     | ROL REGIST       | EKZ              |            |        |

|--------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------|------------------|------------|--------|

| R/W-0              | R-0, HSC                                                                            | U-0                                                                                                                                                | U-0                                           | U-0              | U-0              | U-0        | U-0    |

| ALTIVT             | DISI                                                                                | —                                                                                                                                                  | _                                             | —                | —                | —          | _      |

| bit 15             |                                                                                     |                                                                                                                                                    |                                               |                  |                  |            | bit    |

|                    |                                                                                     |                                                                                                                                                    |                                               |                  |                  |            |        |

| U-0                | U-0                                                                                 | U-0                                                                                                                                                | U-0                                           | U-0              | R/W-0            | R/W-0      | R/W-0  |

| —                  | —                                                                                   | _                                                                                                                                                  |                                               | —                | INT2EP           | INT1EP     | INT0EP |

| bit 7              |                                                                                     |                                                                                                                                                    |                                               |                  |                  |            | bit    |

|                    |                                                                                     |                                                                                                                                                    |                                               |                  |                  |            |        |

| Legend:            |                                                                                     | HSC = Hardw                                                                                                                                        | are Settable/C                                |                  |                  |            |        |

| R = Readabl        | le bit                                                                              | W = Writable                                                                                                                                       | bit                                           | U = Unimple      | mented bit, read | d as '0'   |        |

| -n = Value at      | t POR                                                                               | '1' = Bit is set                                                                                                                                   |                                               | '0' = Bit is cle | x = Bit is unkr  | is unknown |        |

| bit 14<br>bit 13-3 | 1 = Use Alterr<br>0 = Use stand<br>DISI: DISI In:<br>1 = DISI inst<br>0 = DISI inst | Ne Alternate Internate Internate Interrupt V<br>lard (default) ve<br>struction Status<br>ruction is active<br>ruction is not ac<br>ted: Read as '0 | ector Table<br>ector table<br>s bit<br>ective |                  |                  |            |        |

| bit 2              | •                                                                                   | rnal Interrupt 2                                                                                                                                   |                                               | Dolority Soloot  | hit              |            |        |

| Dit 2              | 1 = Interrupt c                                                                     | on negative edge                                                                                                                                   | je                                            |                  | Dit              |            |        |

| bit 1              | 1 = Interrupt c                                                                     | rnal Interrupt 1<br>on negative edg<br>on positive edge                                                                                            | je                                            | Polarity Select  | bit              |            |        |

| bit 0              | 1 = Interrupt c                                                                     | rnal Interrupt 0<br>on negative edg<br>on positive edge                                                                                            | je                                            | Polarity Select  | bit              |            |        |

|                    |                                                                                     |                                                                                                                                                    |                                               |                  |                  |            |        |

### REGISTER 8-4: INTCON2: INTERRUPT CONTROL REGISTER2

| REGISTER     | R 8-12: IEC4                                                                                   | : INTERRUPT                                                                                    | ENABLE C      | ONTROL REG        | GISTER 4        |                    |        |  |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------|-------------------|-----------------|--------------------|--------|--|--|--|--|--|

| U-0          | U-0                                                                                            | R/W-0                                                                                          | U-0           | U-0               | U-0             | U-0                | R/W-0  |  |  |  |  |  |

| _            | —                                                                                              | CTMUIE                                                                                         | _             | —                 | —               | _                  | HLVDIE |  |  |  |  |  |

| bit 15       | ·                                                                                              |                                                                                                |               |                   |                 |                    | bit 8  |  |  |  |  |  |

|              |                                                                                                |                                                                                                |               |                   |                 |                    |        |  |  |  |  |  |

| U-0          | U-0                                                                                            | U-0                                                                                            | U-0           | R/W-0             | R/W-0           | R/W-0              | U-0    |  |  |  |  |  |

| _            | _                                                                                              | —                                                                                              | _             | CRCIE             | U2ERIE          | U1ERIE             | —      |  |  |  |  |  |

| bit 7        |                                                                                                |                                                                                                |               |                   |                 |                    | bit C  |  |  |  |  |  |

|              |                                                                                                |                                                                                                |               |                   |                 |                    |        |  |  |  |  |  |

| Legend:      |                                                                                                |                                                                                                |               |                   |                 |                    |        |  |  |  |  |  |

| R = Readab   | ole bit                                                                                        | W = Writable b                                                                                 | bit           | U = Unimplen      | nented bit, rea | d as '0'           |        |  |  |  |  |  |

| -n = Value a | at POR                                                                                         | '1' = Bit is set                                                                               |               | '0' = Bit is clea | ared            | x = Bit is unknown |        |  |  |  |  |  |

|              |                                                                                                |                                                                                                |               |                   |                 |                    |        |  |  |  |  |  |

| bit 15-14    | Unimplemer                                                                                     | nted: Read as '0                                                                               | 3             |                   |                 |                    |        |  |  |  |  |  |

| bit 13       |                                                                                                | MU Interrupt En                                                                                |               |                   |                 |                    |        |  |  |  |  |  |

|              |                                                                                                | <ol> <li>I = Interrupt request is enabled</li> <li>Interrupt request is not enabled</li> </ol> |               |                   |                 |                    |        |  |  |  |  |  |

| bit 12-9     |                                                                                                | nted: Read as '0                                                                               |               |                   |                 |                    |        |  |  |  |  |  |

| bit 8        | •                                                                                              |                                                                                                |               | t Enable bit      |                 |                    |        |  |  |  |  |  |

|              | HLVDIE: High/Low-Voltage Detect Interrupt Enable bit<br>1 = Interrupt request is enabled       |                                                                                                |               |                   |                 |                    |        |  |  |  |  |  |

|              | 0 = Interrupt request is not enabled                                                           |                                                                                                |               |                   |                 |                    |        |  |  |  |  |  |

| bit 7-4      | Unimplemer                                                                                     | ted: Read as '0                                                                                | ,             |                   |                 |                    |        |  |  |  |  |  |

| bit 3        | CRCIE: CRC                                                                                     | Generator Inter                                                                                | rupt Enable b | pit               |                 |                    |        |  |  |  |  |  |

|              |                                                                                                | 1 = Interrupt request is enabled                                                               |               |                   |                 |                    |        |  |  |  |  |  |

|              | 0 = Interrupt                                                                                  | 0 = Interrupt request is not enabled                                                           |               |                   |                 |                    |        |  |  |  |  |  |

| bit 2        |                                                                                                | U2ERIE: UART2 Error Interrupt Enable bit                                                       |               |                   |                 |                    |        |  |  |  |  |  |

|              | <ol> <li>I = Interrupt request is enabled</li> <li>Interrupt request is not enabled</li> </ol> |                                                                                                |               |                   |                 |                    |        |  |  |  |  |  |

| bit 1        | •                                                                                              | RT1 Error Interru                                                                              |               |                   |                 |                    |        |  |  |  |  |  |

| DILI         |                                                                                                | request is enable                                                                              | •             |                   |                 |                    |        |  |  |  |  |  |

|              |                                                                                                | request is not er                                                                              |               |                   |                 |                    |        |  |  |  |  |  |

| bit 0        | -                                                                                              | nted: Read as '0                                                                               |               |                   |                 |                    |        |  |  |  |  |  |

|              | •                                                                                              |                                                                                                |               |                   |                 |                    |        |  |  |  |  |  |

|                  | R/W-1                                                                                   | R/W-0                                                                                                                             | R/W-0                                                  | U-0               | R/W-1                              | R/W-0           | R/W-0   |  |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------|------------------------------------|-----------------|---------|--|--|--|--|--|--|--|--|

| _                | U2TXIP2                                                                                 | U2TXIP1                                                                                                                           | U2TXIP0                                                | _                 | U2RXIP2                            | U2RXIP1         | U2RXIP0 |  |  |  |  |  |  |  |  |

| bit 15           |                                                                                         |                                                                                                                                   |                                                        |                   | 1                                  |                 | bit 8   |  |  |  |  |  |  |  |  |

|                  |                                                                                         |                                                                                                                                   |                                                        |                   |                                    |                 |         |  |  |  |  |  |  |  |  |

| U-0              | R/W-1                                                                                   | R/W-0                                                                                                                             | R/W-0                                                  | U-0               | U-0                                | U-0             | U-0     |  |  |  |  |  |  |  |  |

| —                | INT2IP2                                                                                 | INT2IP1                                                                                                                           | INT2IP0                                                | —                 | —                                  | —               | —       |  |  |  |  |  |  |  |  |

| bit 7            |                                                                                         |                                                                                                                                   |                                                        |                   |                                    |                 | bit (   |  |  |  |  |  |  |  |  |

| Legend:          |                                                                                         |                                                                                                                                   |                                                        |                   |                                    |                 |         |  |  |  |  |  |  |  |  |

| R = Readat       | ole bit                                                                                 | W = Writable                                                                                                                      | bit                                                    | U = Unimplem      | nented bit, read                   | 1 as '0'        |         |  |  |  |  |  |  |  |  |

| -n = Value a     | at POR                                                                                  | '1' = Bit is set                                                                                                                  |                                                        | '0' = Bit is clea | ared                               | x = Bit is unkr | nown    |  |  |  |  |  |  |  |  |

| bit 15           | Unimplemen                                                                              | ted: Read as '                                                                                                                    | o'                                                     |                   |                                    |                 |         |  |  |  |  |  |  |  |  |

| bit 14-12        | =                                                                                       |                                                                                                                                   |                                                        | t Driarity bita   |                                    |                 |         |  |  |  |  |  |  |  |  |

| DIL 14-12        |                                                                                         | <b>U2TXIP&lt;2:0&gt;:</b> UART2 Transmitter Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                                                        |                   |                                    |                 |         |  |  |  |  |  |  |  |  |

|                  | •                                                                                       | •                                                                                                                                 |                                                        |                   |                                    |                 |         |  |  |  |  |  |  |  |  |

|                  | •                                                                                       | •                                                                                                                                 |                                                        |                   |                                    |                 |         |  |  |  |  |  |  |  |  |

|                  | •                                                                                       |                                                                                                                                   |                                                        |                   |                                    |                 |         |  |  |  |  |  |  |  |  |

|                  | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled                     |                                                                                                                                   |                                                        |                   |                                    |                 |         |  |  |  |  |  |  |  |  |

|                  |                                                                                         | -                                                                                                                                 |                                                        |                   |                                    |                 |         |  |  |  |  |  |  |  |  |

| bit 11           | -                                                                                       | ted: Read as '                                                                                                                    |                                                        |                   |                                    |                 |         |  |  |  |  |  |  |  |  |

| bit 10-8         | U2RXIP<2:0>: UART2 Receiver Interrupt Priority bits                                     |                                                                                                                                   |                                                        |                   |                                    |                 |         |  |  |  |  |  |  |  |  |

|                  | 111 = Interrupt is Priority 7 (highest priority interrupt)                              |                                                                                                                                   |                                                        |                   |                                    |                 |         |  |  |  |  |  |  |  |  |

|                  | •                                                                                       |                                                                                                                                   |                                                        |                   |                                    |                 |         |  |  |  |  |  |  |  |  |

|                  | •                                                                                       |                                                                                                                                   |                                                        |                   |                                    |                 |         |  |  |  |  |  |  |  |  |

|                  | •                                                                                       |                                                                                                                                   |                                                        |                   | •<br>001 = Interrupt is Priority 1 |                 |         |  |  |  |  |  |  |  |  |

|                  | •<br>001 = Interru                                                                      | pt is Priority 1                                                                                                                  |                                                        |                   |                                    |                 |         |  |  |  |  |  |  |  |  |

|                  |                                                                                         | pt is Priority 1<br>pt source is dis                                                                                              | abled                                                  |                   |                                    |                 |         |  |  |  |  |  |  |  |  |

| bit 7            | 000 = Interru                                                                           |                                                                                                                                   |                                                        |                   |                                    |                 |         |  |  |  |  |  |  |  |  |

| bit 7<br>bit 6-4 | 000 = Interru<br>Unimplemen                                                             | pt source is dis<br>ited: Read as '                                                                                               | כ'                                                     | pits              |                                    |                 |         |  |  |  |  |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>INT2IP<2:0>                                              | pt source is dis                                                                                                                  | o'<br><b>upt 2 Priority b</b>                          |                   |                                    |                 |         |  |  |  |  |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>INT2IP<2:0>                                              | pt source is dis<br>ited: Read as '<br>External Intern                                                                            | o'<br><b>upt 2 Priority b</b>                          |                   |                                    |                 |         |  |  |  |  |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>INT2IP<2:0>                                              | pt source is dis<br>ited: Read as '<br>External Intern                                                                            | o'<br><b>upt 2 Priority b</b>                          |                   |                                    |                 |         |  |  |  |  |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>INT2IP<2:0><br>111 = Interru<br>•<br>•                   | pt source is dis<br>ited: Read as f<br>: External Interr<br>pt is Priority 7 (                                                    | o'<br><b>upt 2 Priority b</b>                          |                   |                                    |                 |         |  |  |  |  |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>INT2IP<2:0>:<br>111 = Interru<br>•<br>•<br>001 = Interru | pt source is dis<br>ited: Read as '<br>External Intern                                                                            | <sub>0</sub> '<br>upt 2 Priority b<br>highest priority |                   |                                    |                 |         |  |  |  |  |  |  |  |  |

### REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

| bit 7 | CLKLOCK: Clock Selection Lock Enabled bit<br><u>If FSCM is enabled (FCKSM1 = 1):</u><br>1 = Clock and PLL selections are locked<br>0 = Clock and PLL selections are not locked and may be modified by setting the OSWEN bit<br><u>If FSCM is disabled (FCKSM1 = 0):</u><br>Clock and PLL selections are never locked and may be modified by setting the OSWEN bit. |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                         |

| bit 5 | LOCK: PLL Lock Status bit <sup>(2)</sup><br>1 = PLL module is in lock or PLL module start-up timer is satisfied<br>0 = PLL module is out of lock, PLL start-up timer is running or PLL is disabled                                                                                                                                                                 |

| bit 4 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                         |

| bit 3 | <b>CF:</b> Clock Fail Detect bit<br>1 = FSCM has detected a clock failure<br>0 = No clock failure has been detected                                                                                                                                                                                                                                                |

| bit 2 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                         |

| bit 1 | <b>SOSCEN:</b> 32 kHz Secondary Oscillator (SOSC) Enable bit<br>1 = Enable secondary oscillator<br>0 = Disable secondary oscillator                                                                                                                                                                                                                                |

| bit 0 | <b>OSWEN:</b> Oscillator Switch Enable bit<br>1 = Initiate an oscillator switch to clock source specified by NOSC<2:0> bits<br>0 = Oscillator switch is complete                                                                                                                                                                                                   |

- Note 1: Reset values for these bits are determined by the FNOSC Configuration bits.

- 2: Also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

| U-0                               | U-0                      | U-0                 | U-0                       | U-0                                | U-0                 | U-0                 | U-0                 |  |  |  |  |  |

|-----------------------------------|--------------------------|---------------------|---------------------------|------------------------------------|---------------------|---------------------|---------------------|--|--|--|--|--|

|                                   | —                        |                     | —                         | —                                  | —                   | —                   | —                   |  |  |  |  |  |

| bit 15                            |                          |                     |                           |                                    |                     |                     | bit 8               |  |  |  |  |  |

|                                   |                          |                     |                           |                                    |                     |                     |                     |  |  |  |  |  |

| U-0                               | U-0                      | R/W-0               | R/W-0                     | R/W-0                              | R/W-0               | R/W-0               | R/W-0               |  |  |  |  |  |

| _                                 | _                        | TUN5 <sup>(1)</sup> | TUN4 <sup>(1)</sup>       | TUN3 <sup>(1)</sup>                | TUN2 <sup>(1)</sup> | TUN1 <sup>(1)</sup> | TUN0 <sup>(1)</sup> |  |  |  |  |  |

| bit 7                             | ÷                        |                     | •                         | ·                                  | •                   | •                   | bit 0               |  |  |  |  |  |

|                                   |                          |                     |                           |                                    |                     |                     |                     |  |  |  |  |  |

| Legend:                           |                          |                     |                           |                                    |                     |                     |                     |  |  |  |  |  |

| R = Readable bit W = Writable bit |                          |                     |                           | U = Unimplemented bit, read as '0' |                     |                     |                     |  |  |  |  |  |

| -n = Value a                      | t POR                    | '1' = Bit is set    |                           | '0' = Bit is clea                  | ared                | x = Bit is unknown  |                     |  |  |  |  |  |

|                                   |                          |                     |                           |                                    |                     |                     |                     |  |  |  |  |  |

| bit 15-6                          | Unimplemen               | ted: Read as '      | 0'                        |                                    |                     |                     |                     |  |  |  |  |  |

| bit 5-0                           | <b>TUN&lt;5:0&gt;:</b> F | RC Oscillator 1     | uning bits <sup>(1)</sup> |                                    |                     |                     |                     |  |  |  |  |  |

|                                   | 011111 <b>= Ma</b>       | iximum frequer      | ncy deviation             |                                    |                     |                     |                     |  |  |  |  |  |

|                                   | 011110                   |                     |                           |                                    |                     |                     |                     |  |  |  |  |  |

|                                   | •                        |                     |                           |                                    |                     |                     |                     |  |  |  |  |  |

|                                   | •                        |                     |                           |                                    |                     |                     |                     |  |  |  |  |  |

|                                   | 000001                   | 000001              |                           |                                    |                     |                     |                     |  |  |  |  |  |

|                                   |                          | nter frequency      | , oscillator is ru        | inning at factory                  | / calibrated free   | quency              |                     |  |  |  |  |  |

|                                   | 111111                   |                     |                           |                                    |                     |                     |                     |  |  |  |  |  |

|                                   | •                        |                     |                           |                                    |                     |                     |                     |  |  |  |  |  |

|                                   | •                        |                     |                           |                                    |                     |                     |                     |  |  |  |  |  |

|                                   | 100001                   |                     |                           |                                    |                     |                     |                     |  |  |  |  |  |

|                                   | 100000 <b>= Mi</b>       | nimum frequen       | cy deviation              |                                    |                     |                     |                     |  |  |  |  |  |

|                                   |                          |                     |                           |                                    |                     |                     |                     |  |  |  |  |  |

### REGISTER 9-3: OSCTUN: FRC OSCILLATOR TUNE REGISTER

**Note 1:** Increments or decrements of TUN<5:0> may not change the FRC frequency in equal steps over the FRC tuning range and may not be monotonic.

NOTES:

### 15.4 Output Compare Register

### REGISTER 15-1: OC1CON: OUTPUT COMPARE 1 CONTROL REGISTER

| U-0    | U-0 | R/W-0  | U-0     | U-0    | U-0   | U-0   | U-0   |

|--------|-----|--------|---------|--------|-------|-------|-------|

| —      | —   | OCSIDL | —       | —      | _     |       | —     |

| bit 15 |     |        |         |        |       |       | bit 8 |

|        |     |        |         |        |       |       |       |

| U-0    | U-0 | U-0    | R-0, HC | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

| —      | —   | —      | OCFLT   | OCTSEL | OCM2  | OCM1  | OCM0  |

| bit 7  |     |        |         |        |       |       | bit 0 |

| Legend:           | HC = Hardware Clearable bit                         |                      |                    |  |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |  |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | OCSIDL: Stop Output Compare 1 in Idle Mode Control bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|           | <ul> <li>1 = Output Compare 1 will halt in CPU Idle mode</li> <li>0 = Output Compare 1 will continue to operate in CPU Idle mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 12-5  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| bit 4     | OCFLT: PWM Fault Condition Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|           | <ul> <li>1 = PWM Fault condition has occurred (cleared in HW only)</li> <li>0 = No PWM Fault condition has occurred (this bit is only used when OCM&lt;2:0&gt; = 111)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                               |

| bit 3     | OCTSEL: Output Compare 1 Timer Select bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|           | <ul> <li>1 = Timer3 is the clock source for Output Compare 1</li> <li>0 = Timer2 is the clock source for Output Compare 1</li> <li>Refer to the device data sheet for specific time bases available to the output compare module.</li> </ul>                                                                                                                                                                                                                                                                                                                   |

| bit 2-0   | OCM<2:0>: Output Compare 1 Mode Select bits<br>111 = PWM mode on OC1, Fault pin; OCF1 enabled <sup>(1)</sup><br>110 = PWM mode on OC1, Fault pin; OCF1 disabled <sup>(1)</sup><br>101 = Initialize OC1 pin low, generate continuous output pulses on OC1 pin<br>100 = Initialize OC1 pin low, generate single output pulse on OC1 pin<br>011 = Compare event toggles OC1 pin<br>010 = Initialize OC1 pin high, compare event forces OC1 pin low<br>001 = Initialize OC1 pin low, compare event forces OC1 pin high<br>000 = Output compare channel is disabled |

Note 1: The OCFA pin controls the OC1 channel.

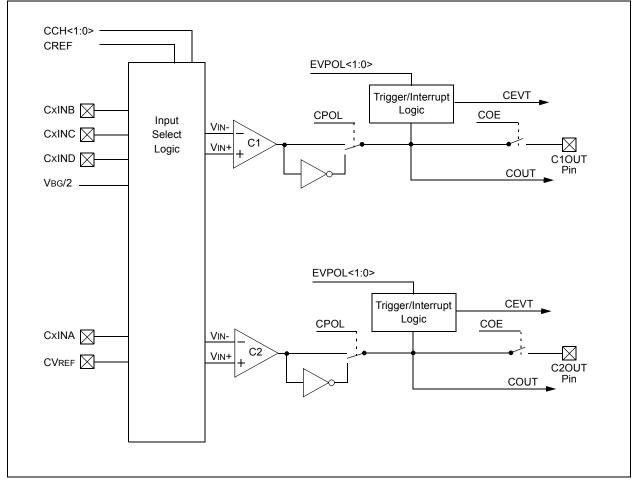

### 23.0 COMPARATOR MODULE

| Note: | This data sheet summarizes the features<br>of this group of PIC24F devices. It is not |

|-------|---------------------------------------------------------------------------------------|

|       |                                                                                       |

|       | intended to be a comprehensive refer-                                                 |

|       | ence source. For more information on the                                              |

|       | Comparator module, refer to the "PIC24F                                               |

|       | Family Reference Manual", Section 46.                                                 |

|       | "Scalable Comparator Module"                                                          |

|       | (DS39734).                                                                            |

The comparator module provides two dual input comparators. The inputs to the comparator can be configured to use any one of four external analog inputs, as well as a voltage reference input from either the internal band gap reference, divided by 2 (VBG/2), or the comparator voltage reference generator.

The comparator outputs may be directly connected to the CxOUT pins. When the respective COE equals '1', the I/O pad logic makes the unsynchronized output of the comparator available on the pin.

A simplified block diagram of the module is displayed in Figure 23-1. Diagrams of the possible individual comparator configurations are displayed in Figure 23-2.

Each comparator has its own control register, CMxCON (Register 23-1), for enabling and configuring its operation. The output and event status of all three comparators is provided in the CMSTAT register (Register 23-2).

### FIGURE 23-1: COMPARATOR MODULE BLOCK DIAGRAM

### **REGISTER 23-1: CMxCON: COMPARATOR x CONTROL REGISTERS (CONTINUED)**

- bit 5 Unimplemented: Read as '0'

- bit 4 **CREF:** Comparator Reference Select bit (non-inverting input) 1 = Non-inverting input connects to the internal CVREF voltage

- 0 = Non-inverting input connects to the CxINA pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Channel Select bits

- 11 = Inverting input of comparator connects to VBG/2

- 10 = Inverting input of comparator connects to CxIND pin

- 01 = Inverting input of comparator connects to CxINC pin

- 00 = Inverting input of comparator connects to CxINB pin

### REGISTER 23-2: CMSTAT: COMPARATOR MODULE STATUS REGISTER

| R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0 | R-0, HSC | R-0, HSC |

|--------|-----|-----|-----|-----|-----|----------|----------|

| CMIDL  |     | —   | —   | —   | _   | C2EVT    | C1EVT    |

| bit 15 |     |     |     |     |     |          | bit 8    |

|        |     |     |     |     |     |          |          |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R-0, HSC | R-0, HSC |

\_\_\_\_

| bit | 7 |

|-----|---|

| Legend:           | HSC = Hardware Settable/Clearable bit               |                      |                    |  |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |  |

| bit 15    | CMIDL: Comparator Stop in Idle Mode bit                                                                                                                                                     |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | <ul> <li>1 = Disable comparator interrupts when the device enters Idle mode; the module is still enabled</li> <li>0 = Continue operation of all enabled comparators in Idle mode</li> </ul> |

| bit 14-10 | Unimplemented: Read as '0'                                                                                                                                                                  |

| bit 9     | C2EVT: Comparator 2 Event Status bit (read-only)                                                                                                                                            |

|           | Shows the current event status of Comparator 2 (CM2CON<9>).                                                                                                                                 |

| bit 8     | C1EVT: Comparator 1 Event Status bit (read-only)                                                                                                                                            |

|           | Shows the current event status of Comparator 1 (CM1CON<9>).                                                                                                                                 |

| bit 7-2   | Unimplemented: Read as '0'                                                                                                                                                                  |

| bit 1     | C2OUT: Comparator 2 Output Status bit (read-only)                                                                                                                                           |

|           | Shows the current output of Comparator 2 (CM2CON<8>).                                                                                                                                       |

| bit 0     | C1OUT: Comparator 1 Output Status bit (read-only)                                                                                                                                           |

|           | Shows the current output of Comparator 1 (CM1CON<8>).                                                                                                                                       |

C2OUT

C10UT

bit 0

| R/P-1         | R/P-1                            | R/P-1            | R/P-1            | R/P-1             | R/P-1            | R/P-1           | R/P-1        |

|---------------|----------------------------------|------------------|------------------|-------------------|------------------|-----------------|--------------|

| DSWDTEN       | DSBOREN                          | RTCOSC           | DSWDTOSC         | DSWDTPS3          | DSWDTPS2         | DSWDTPS1        | DSWDTPS0     |

| bit 7         |                                  |                  |                  |                   |                  |                 | bit 0        |

|               |                                  |                  |                  |                   |                  |                 |              |

| Legend:       |                                  |                  |                  |                   |                  |                 |              |

| R = Readabl   | e bit                            | P = Program      | nable bit        | U = Unimplem      | nented bit, read | 1 as '0'        |              |

| -n = Value at | POR                              | '1' = Bit is set |                  | '0' = Bit is clea | ared             | x = Bit is unkr | nown         |

| bit 7         | DSWDTEN: D                       | eep Sleep Wat    | chdog Timer Er   | able bit          |                  |                 |              |

|               | 1 = DSWDT is                     |                  | U                |                   |                  |                 |              |

|               | 0 = DSWDT is                     | disabled         |                  |                   |                  |                 |              |

| bit 6         | DSBOREN: De                      | eep Sleep/Low-   | Power BOR Ena    | able bit (does n  | ot affect operat | ion in non Deep | Sleep modes) |

|               |                                  |                  | led in Deep Sle  |                   |                  |                 |              |

|               |                                  |                  | oled in Deep Sle |                   |                  |                 |              |

| bit 5         |                                  |                  | Clock Select bit |                   |                  |                 |              |

|               | 1 = RTCC use<br>0 = RTCC use     |                  | eference clock   |                   |                  |                 |              |

| bit 4         |                                  |                  | ence Clock Sele  | ect bit           |                  |                 |              |

|               |                                  |                  | reference clock  |                   |                  |                 |              |

|               | 0 = DSWDT us                     | ses SOSC as a    | a reference cloc | k                 |                  |                 |              |

| bit 3-0       | DSWDTPS<3:                       | 0>: Deep Slee    | p Watchdog Tin   | ner Postscale S   | Select bits      |                 |              |

|               |                                  |                  | this creates an  | ••                | ase time unit o  | f 1 ms.         |              |