#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I²C, IrDA, SPI, UART/USART                                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 18                                                                          |

| Program Memory Size        | 16KB (5.5K x 24)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 512 x 8                                                                     |

| RAM Size                   | 1.5K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 9x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 20-PDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16ka101-e-p |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2009

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2008-2011, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 978-1-61341-690-7

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.

#### **Table of Contents**

| 1.0  | Device Overview                                             | 9   |

|------|-------------------------------------------------------------|-----|

| 2.0  | Guidelines for Getting Started with 16-Bit Microcontrollers | 17  |

| 3.0  | CPU                                                         |     |

| 4.0  | Memory Organization                                         |     |

| 5.0  | Flash Program Memory                                        | 45  |

| 6.0  | Data EEPROM Memory                                          | 51  |

| 7.0  | Resets                                                      | 57  |

| 8.0  | Interrupt Controller                                        |     |

| 9.0  | Oscillator Configuration                                    |     |

| 10.0 | Power-Saving Features                                       | 101 |

| 11.0 | I/O Ports                                                   | 113 |

| 12.0 | Timer1                                                      | 115 |

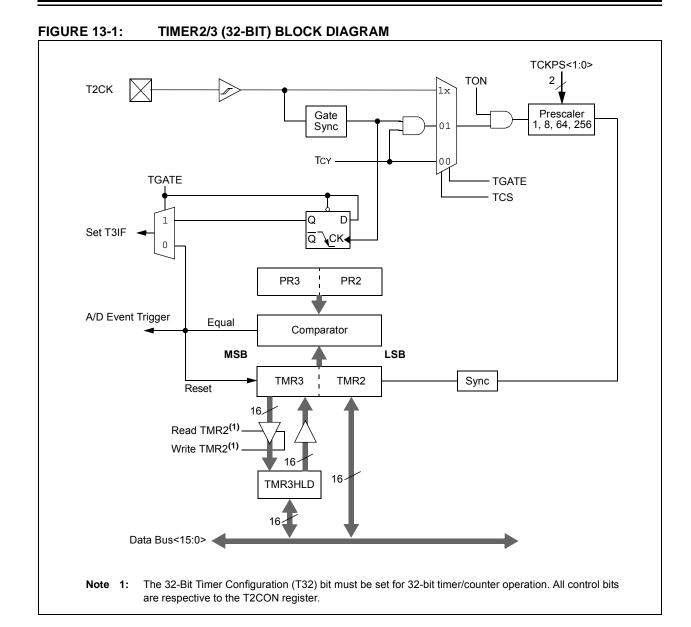

| 13.0 | Timer2/3                                                    | 117 |

| 14.0 | Input Capture                                               | 123 |

| 15.0 | Output Compare                                              | 125 |

| 16.0 | Serial Peripheral Interface (SPI)                           |     |

| 17.0 |                                                             |     |

| 18.0 |                                                             |     |

| 19.0 |                                                             |     |

| 20.0 |                                                             |     |

| 21.0 | High/Low-Voltage Detect (HLVD)                              |     |

| 22.0 |                                                             |     |

| 23.0 |                                                             |     |

| 24.0 | · · · · · · · · · · · · · · · · · · ·                       |     |

| 25.0 |                                                             |     |

| 26.0 |                                                             |     |

| 27.0 | F F F                                                       |     |

| 28.0 |                                                             |     |

| 29.0 |                                                             |     |

|      | Packaging Information                                       |     |

|      | endix A: Revision History                                   |     |

|      | (                                                           |     |

|      | Microchip Web Site                                          |     |

|      | omer Change Notification Service                            |     |

|      | omer Support                                                |     |

|      | ler Response                                                |     |

| Prod | uct Identification System                                   |     |

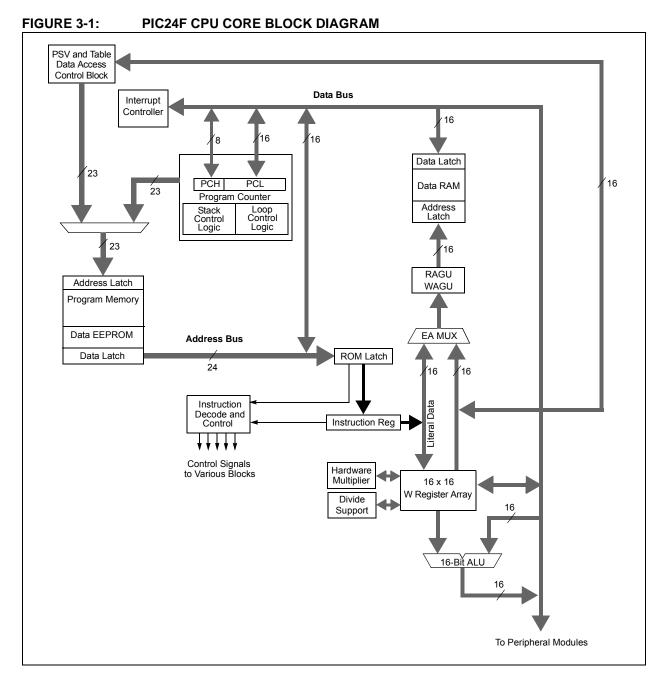

| Register(s) Name | Description                                    |

|------------------|------------------------------------------------|

| W0 through W15   | Working Register Array                         |

| PC               | 23-Bit Program Counter                         |

| SR               | ALU STATUS Register                            |

| SPLIM            | Stack Pointer Limit Value Register             |

| TBLPAG           | Table Memory Page Address Register             |

| PSVPAG           | Program Space Visibility Page Address Register |

| RCOUNT           | Repeat Loop Counter Register                   |

| CORCON           | CPU Control Register                           |

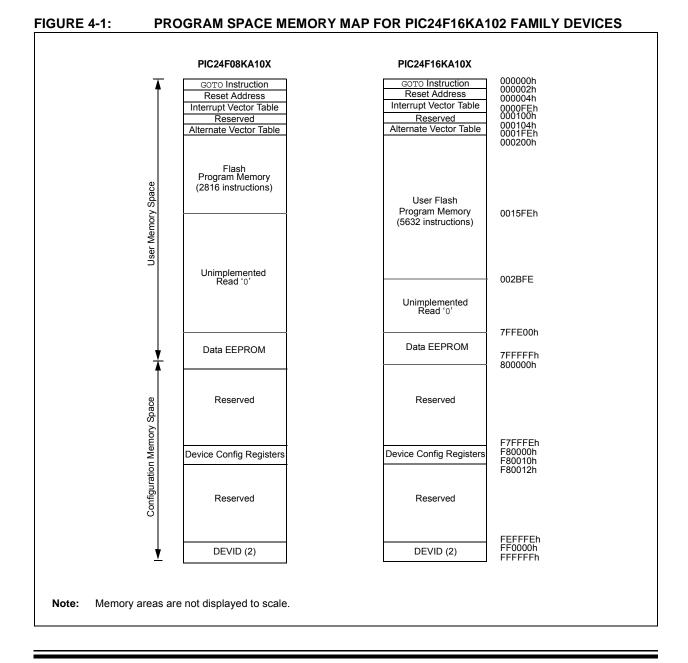

### 4.0 MEMORY ORGANIZATION

As with Harvard architecture devices, the PIC24F microcontrollers feature separate program and data memory space and busing. This architecture also allows the direct access of program memory from the data space during code execution.

#### 4.1 **Program Address Space**

The program address memory space of the PIC24F devices is 4M instructions. The space is addressable by a 24-bit value derived from either the 23-bit Program Counter (PC) during program execution, or from a table operation or data space remapping, as described in Section 4.3 "Interfacing Program and Data Memory Spaces".

The user access to the program memory space is restricted to the lower half of the address range (000000h to 7FFFFh). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

Memory maps for the PIC24F16KA102 family of devices are displayed in Figure 4-1.

| File Name | Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7 | Bit 6 | Bit 5      | Bit 4       | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|---------|--------|---------|--------|--------|--------|--------|-------|-------|-------|------------|-------------|--------------|-------|-------|-------|---------------|

| I2C1RCV   | 0200 |         | _      | _       | _      | _      |        | _      | _     |       |       |            | I2C1 Recei  | ve Register  |       |       |       | 0000          |

| I2C1TRN   | 0202 | _       | _      | —       | —      | _      | -      | _      | _     |       |       |            | I2C1 Transı | nit Register |       |       |       | 00FF          |

| I2C1BRG   | 0204 | _       | _      | _       | _      | _      | _      | _      |       |       | Ľ     | 2C1 Baud F | Rate Genera | ator Registe | r     |       |       | 0000          |

| I2C1CON   | 0206 | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN  | GCEN  | STREN | ACKDT      | ACKEN       | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT  | 0208 | ACKSTAT | TRSTAT | _       | _      | -      | BCL    | GCSTAT | ADD10 | IWCOL | I2COV | D/A        | Р           | S            | R/W   | RBF   | TBF   | 0000          |

| I2C1ADD   | 020A | _       | _      | _       | _      | _      | _      |        |       |       |       | I2C1 Addre | ss Register |              |       |       |       | 0000          |

| I2C1MSK   | 020C |         | _      | _       | _      | -      |        | AMSK9  | AMSK8 | AMSK7 | AMSK6 | AMSK5      | AMSK4       | AMSK3        | AMSK2 | AMSK1 | AMSK0 | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in h.5adecimal.

#### TABLE 4-10: UART REGISTER MAP

| File<br>Name | Addr | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8      | Bit 7          | Bit 6    | Bit 5     | Bit 4        | Bit 3 | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|------|----------|--------|----------|--------|--------|--------|--------|------------|----------------|----------|-----------|--------------|-------|--------|--------|-------|---------------|

| U1MODE       | 0220 | UARTEN   | _      | USIDL    | IREN   | RTSMD  | _      | UEN1   | UEN0       | WAKE           | LPBACK   | ABAUD     | RXINV        | BRGH  | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA        | 0222 | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF  | TRMT       | URXISEL1       | URXISEL0 | ADDEN     | RIDLE        | PERR  | FERR   | OERR   | URXDA | 0110          |

| U1TXREG      | 0224 | _        | _      | _        | _      | _      |        | _      |            |                |          | UART1 Tra | ansmit Regi  | ster  |        |        |       | 0000          |

| U1RXREG      | 0226 | _        | _      | _        | _      | _      |        | _      |            |                |          | UART1 Re  | eceive Regis | ster  |        |        |       | 0000          |

| U1BRG        | 0228 |          |        |          |        |        |        | Baud R | ate Genera | ator Prescaler | Register |           |              |       |        |        |       | 0000          |

| U2MODE       | 0230 | UARTEN   | _      | USIDL    | IREN   | RTSMD  |        | UEN1   | UEN0       | WAKE           | LPBACK   | ABAUD     | RXINV        | BRGH  | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA        | 0232 | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF  | TRMT       | URXISEL1       | URXISEL0 | ADDEN     | RIDLE        | PERR  | FERR   | OERR   | URXDA | 0110          |

| U2TXREG      | 0234 | _        | _      | —        | _      | _      | _      | _      |            |                |          | UART2 Tra | ansmit Regi  | ster  |        |        |       | 0000          |

| U2RXREG      | 0236 | _        |        |          |        |        |        |        |            |                | 0000     |           |              |       |        |        |       |               |

| U2BRG        | 0238 |          |        |          |        |        |        | Bau    | ud Rate Ge | enerator Prese | caler    |           |              |       |        |        |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-11: SPI REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10  | Bit 9   | Bit 8        | Bit 7      | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|--------|--------|---------|--------|--------|---------|---------|--------------|------------|--------|--------|--------|--------|--------|--------|--------|---------------|

| SPI1STAT     | 0240 | SPIEN  | _      | SPISIDL | _      | _      | SPIBEC2 | SPIBEC1 | SPIBEC0      | SRMPT      | SPIROV | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI1CON1     | 0242 |        | _      | -       | DISSCK | DISSDO | MODE16  | SMP     | CKE          | SSEN       | CKP    | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI1CON2     | 0244 | FRMEN  | SPIFSD | SPIFPOL | —      | _      | _       | _       | —            | _          | _      | —      | _      | _      | —      | SPIFE  | SPIBEN | 0000          |

| SPI1BUF      | 0248 |        |        |         |        |        |         | SP      | 11 Transmit/ | Receive Bu | ffer   |        |        |        |        |        |        | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| U-0          | R/W-1         | R/W-0              | R/W-0            | U-0               | U-0              | U-0             | U-0   |

|--------------|---------------|--------------------|------------------|-------------------|------------------|-----------------|-------|

| _            | T2IP2         | T2IP1              | T2IP0            | _                 | _                | —               | _     |

| bit 15       |               |                    |                  | -                 |                  |                 | bit 8 |

|              |               |                    |                  |                   |                  |                 |       |

| U-0          | U-0           | U-0                | U-0              | U-0               | U-0              | U-0             | U-0   |

| _            | _             |                    | _                |                   |                  | _               | _     |

| bit 7        | ·             |                    | •                | ÷                 | •                |                 | bit 0 |

|              |               |                    |                  |                   |                  |                 |       |

| Legend:      |               |                    |                  |                   |                  |                 |       |

| R = Readab   | le bit        | W = Writable       | bit              | U = Unimplem      | nented bit, read | d as '0'        |       |

| -n = Value a | t POR         | '1' = Bit is set   |                  | '0' = Bit is clea | ared             | x = Bit is unkn | own   |

|              |               |                    |                  |                   |                  |                 |       |

| bit 15       | Unimplemen    | ted: Read as '     | 0'               |                   |                  |                 |       |

| bit 14-12    | T2IP<2:0>: ⊺  | imer2 Interrupt    | Priority bits    |                   |                  |                 |       |

|              | 111 = Interru | pt is Priority 7 ( | highest priority | / interrupt)      |                  |                 |       |

|              | •             |                    |                  |                   |                  |                 |       |

|              | •             |                    |                  |                   |                  |                 |       |

|              | •             |                    |                  |                   |                  |                 |       |

|              | 001 = Interru |                    | ablad            |                   |                  |                 |       |

|              |               | pt source is dis   |                  |                   |                  |                 |       |

| bit 11-0     | Unimplemen    | ted: Read as '     | 0'               |                   |                  |                 |       |

#### REGISTER 8-14: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

|                  | R/W-1                                                                                   | R/W-0                                                                          | R/W-0                                                  | U-0               | R/W-1            | R/W-0           | R/W-0   |

|------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------|-------------------|------------------|-----------------|---------|

| _                | U2TXIP2                                                                                 | U2TXIP1                                                                        | U2TXIP0                                                | _                 | U2RXIP2          | U2RXIP1         | U2RXIP0 |

| bit 15           |                                                                                         |                                                                                |                                                        |                   | 1                |                 | bit 8   |

|                  |                                                                                         |                                                                                |                                                        |                   |                  |                 |         |

| U-0              | R/W-1                                                                                   | R/W-0                                                                          | R/W-0                                                  | U-0               | U-0              | U-0             | U-0     |

| —                | INT2IP2                                                                                 | INT2IP1                                                                        | INT2IP0                                                | —                 | —                | —               | —       |

| bit 7            |                                                                                         |                                                                                |                                                        |                   |                  |                 | bit (   |

| Legend:          |                                                                                         |                                                                                |                                                        |                   |                  |                 |         |

| R = Readat       | ole bit                                                                                 | W = Writable                                                                   | bit                                                    | U = Unimplem      | nented bit, read | 1 as '0'        |         |

| -n = Value a     | at POR                                                                                  | '1' = Bit is set                                                               |                                                        | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |

| bit 15           | Unimplemen                                                                              | ted: Read as '                                                                 | o'                                                     |                   |                  |                 |         |

| bit 14-12        | =                                                                                       | : UART2 Trans                                                                  |                                                        | t Driarity bita   |                  |                 |         |

| DIL 14-12        |                                                                                         | pt is Priority 7 (                                                             | •                                                      | •                 |                  |                 |         |

|                  | •                                                                                       |                                                                                | nighest phoney                                         | (interrupt)       |                  |                 |         |

|                  | •                                                                                       |                                                                                |                                                        |                   |                  |                 |         |

|                  | •                                                                                       |                                                                                |                                                        |                   |                  |                 |         |

|                  |                                                                                         | pt is Priority 1                                                               |                                                        |                   |                  |                 |         |

|                  |                                                                                         | pt source is dis                                                               |                                                        |                   |                  |                 |         |

| bit 11           | -                                                                                       | ted: Read as '                                                                 |                                                        |                   |                  |                 |         |

| bit 10-8         |                                                                                         | >: UART2 Rece                                                                  | •                                                      | •                 |                  |                 |         |

|                  | 111 = Interru                                                                           | pt is Priority 7 (                                                             | highest priority                                       | v interrupt)      |                  |                 |         |

|                  | •                                                                                       |                                                                                |                                                        |                   |                  |                 |         |

|                  | •                                                                                       |                                                                                |                                                        |                   |                  |                 |         |

|                  | •                                                                                       |                                                                                |                                                        |                   |                  |                 |         |

|                  | •<br>001 = Interru                                                                      | pt is Priority 1                                                               |                                                        |                   |                  |                 |         |

|                  |                                                                                         | pt is Priority 1<br>pt source is dis                                           | abled                                                  |                   |                  |                 |         |

| bit 7            | 000 = Interru                                                                           |                                                                                |                                                        |                   |                  |                 |         |

| bit 7<br>bit 6-4 | 000 = Interru<br>Unimplemen                                                             | pt source is dis<br>ited: Read as '                                            | כ'                                                     | pits              |                  |                 |         |

|                  | 000 = Interru<br>Unimplemen<br>INT2IP<2:0>                                              | pt source is dis                                                               | o'<br><b>upt 2 Priority b</b>                          |                   |                  |                 |         |

|                  | 000 = Interru<br>Unimplemen<br>INT2IP<2:0>                                              | pt source is dis<br>ited: Read as '<br>External Intern                         | o'<br><b>upt 2 Priority b</b>                          |                   |                  |                 |         |

|                  | 000 = Interru<br>Unimplemen<br>INT2IP<2:0>                                              | pt source is dis<br>ited: Read as '<br>External Intern                         | o'<br><b>upt 2 Priority b</b>                          |                   |                  |                 |         |

|                  | 000 = Interru<br>Unimplemen<br>INT2IP<2:0><br>111 = Interru<br>•<br>•                   | pt source is dis<br>ited: Read as f<br>: External Interr<br>pt is Priority 7 ( | o'<br><b>upt 2 Priority b</b>                          |                   |                  |                 |         |

|                  | 000 = Interru<br>Unimplemen<br>INT2IP<2:0>:<br>111 = Interru<br>•<br>•<br>001 = Interru | pt source is dis<br>ited: Read as '<br>External Intern                         | <sub>0</sub> '<br>upt 2 Priority b<br>highest priority |                   |                  |                 |         |

#### 10.2.4.5 Deep Sleep WDT

To enable the DSWDT in Deep Sleep mode, program the Configuration bit, DSWDTEN (FDS<7>). The device Watchdog Timer (WDT) need not be enabled for the DSWDT to function. Entry into Deep Sleep mode automatically resets the DSWDT.

The DSWDT clock source is selected by the DSWDTOSC Configuration bit (FDS<4>). The postscaler options are programmed by the DSWDTPS<3:0> Configuration bits (FDS<3:0>). The minimum time-out period that can be achieved is 2.1 ms and the maximum is 25.7 days. For more details on the FDS Configuration register and DSWDT configuration options, refer to Section 26.0 "Special Features".

#### 10.2.4.6 Switching Clocks in Deep Sleep Mode

Both the RTCC and the DSWDT may run from either SOSC or the LPRC clock source. This allows both the RTCC and DSWDT to run without requiring both the LPRC and SOSC to be enabled together, reducing power consumption.

Running the RTCC from LPRC will result in a loss of accuracy in the RTCC of approximately 5 to 10%. If a more accurate RTCC is required, it must be run from the SOSC clock source. The RTCC clock source is selected with the RTCOSC Configuration bit (FDS<5>).

Under certain circumstances, it is possible for the DSWDT clock source to be off when entering Deep Sleep mode. In this case, the clock source is turned on automatically (if DSWDT is enabled), without the need for software intervention. However, this can cause a delay in the start of the DSWDT counters. In order to avoid this delay when using SOSC as a clock source, the application can activate SOSC prior to entering Deep Sleep mode.

#### 10.2.4.7 Checking and Clearing the Status of Deep Sleep

Upon entry into Deep Sleep mode, the status bit DPSLP (RCON<10>), becomes set and must be cleared by software.

On power-up, the software should read this status bit to determine if the Reset was due to an exit from Deep Sleep mode and clear the bit if it is set. Of the four possible combinations of DPSLP and POR bit states, three cases can be considered:

- Both the DPSLP and POR bits are cleared. In this case, the Reset was due to some event other than a Deep Sleep mode exit.

- The DPSLP bit is clear, but the POR bit is set. This is a normal POR.

- Both the DPSLP and POR bits are set. This means that Deep Sleep mode was entered, the device was powered down and Deep Sleep mode was exited.

#### 10.2.4.8 Power-on Resets (PORs)

VDD voltage is monitored to produce PORs. Since exiting from Deep Sleep functionally looks like a POR, the technique described in Section 10.2.4.7 "Checking and Clearing the Status of Deep Sleep" should be used to distinguish between Deep Sleep and a true POR event.

When a true POR occurs, the entire device, including all Deep Sleep logic (Deep Sleep registers, RTCC, DSWDT, etc.) is reset.

#### 10.2.4.9 Summary of Deep Sleep Sequence

To review, these are the necessary steps involved in invoking and exiting Deep Sleep mode:

- 1. Device exits Reset and begins to execute its application code.

- 2. If DSWDT functionality is required, program the appropriate Configuration bit.

- 3. Select the appropriate clock(s) for the DSWDT and RTCC (optional).

- 4. Enable and configure the DSWDT (optional).

- 5. Enable and configure the RTCC (optional).

- 6. Write context data to the DSGPRx registers (optional).

- 7. Enable the INT0 interrupt (optional).

- 8. Set the DSEN bit in the DSCON register.

- 9. Enter Deep Sleep by issuing a PWRSV #SLEEP\_MODE command.

- 10. Device exits Deep Sleep when a wake-up event occurs.

- 11. The DSEN bit is automatically cleared.

- 12. Read and clear the DPSLP status bit in RCON, and the DSWAKE status bits.

- 13. Read the DSGPRx registers (optional).

- 14. Once all state related configurations are complete, clear the RELEASE bit.

- 15. Application resumes normal operation.

### EXAMPLE 15-1: PWM PERIOD AND DUTY CYCLE CALCULATIONS<sup>(1)</sup>

1. Find the Timer Period register value for a desired PWM frequency of 52.08 kHz, where Fosc = 8 MHz with PLL (32 MHz device clock rate) and a Timer2 prescaler setting of 1:1.

Tcy = 2 \* Tosc = 62.5 ns

PWM Period = 1/PWM Frequency =  $1/52.08 \text{ kHz} = 19.2 \mu \text{s}$

PWM Period = (PR2 + 1) • Tcy • (Timer 2 Prescale Value)

19.2 µs = (PR2 + 1) • 62.5 ns • 1

PR2 = 306

2. Find the maximum resolution of the duty cycle that can be used with a 52.08 kHz frequency and a 32 MHz device clock rate:

PWM Resolution =  $log_{10}(FCY/FPWM)/log_{10}2)$  bits

= (log<sub>10</sub>(16 MHz/52.08 kHz)/log<sub>10</sub>2) bits

= 8.3 bits

**Note 1:** Based on Tcy = 2 \* Tosc; Doze mode and PLL are disabled.

#### TABLE 15-1: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 4 MIPS (Fcy = 4 MHz)<sup>(1)</sup>

| PWM Frequency         | 7.6 Hz | 61 Hz | 122 Hz | 977 Hz | 3.9 kHz | 31.3 kHz | 125 kHz |

|-----------------------|--------|-------|--------|--------|---------|----------|---------|

| Timer Prescaler Ratio | 8      | 1     | 1      | 1      | 1       | 1        | 1       |

| Period Register Value | FFFFh  | FFFFh | 7FFFh  | 0FFFh  | 03FFh   | 007Fh    | 001Fh   |

| Resolution (bits)     | 16     | 16    | 15     | 12     | 10      | 7        | 5       |

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

#### TABLE 15-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 16 MIPS (Fcy = 16 MHz)<sup>(1)</sup>

|                       |         |        |        |         |          | -       |         |

|-----------------------|---------|--------|--------|---------|----------|---------|---------|

| PWM Frequency         | 30.5 Hz | 244 Hz | 488 Hz | 3.9 kHz | 15.6 kHz | 125 kHz | 500 kHz |

| Timer Prescaler Ratio | 8       | 1      | 1      | 1       | 1        | 1       | 1       |

| Period Register Value | FFFFh   | FFFFh  | 7FFFh  | 0FFFh   | 03FFh    | 007Fh   | 001Fh   |

| Resolution (bits)     | 16      | 16     | 15     | 12      | 10       | 7       | 5       |

**Note 1:** Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

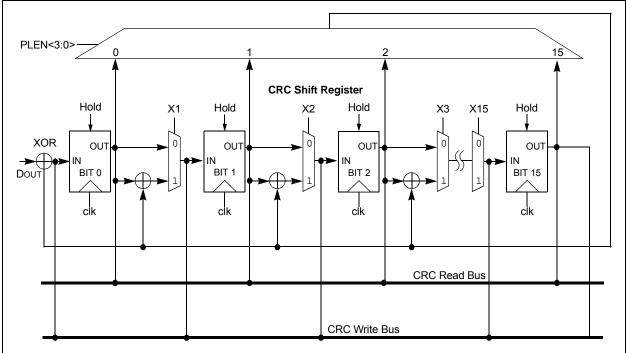

### 20.0 PROGRAMMABLE CYCLIC REDUNDANCY CHECK (CRC) GENERATOR

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Programmable Cyclic Redundancy Check, refer to the "PIC24F Family Reference Manual", Section 30. "Programmable Cyclic Redundancy Check (CRC)" (DS39714).

The programmable Cyclic Redundancy Check (CRC) module in PIC24F devices is a software-configurable CRC checksum generator. The CRC algorithm treats a message as a binary bit stream and divides it by a fixed binary number.

The remainder from this division is considered the checksum. As in division, the CRC calculation is also an iterative process. The only difference is that these operations are done on modulo arithmetic based on mod2. For example, division is replaced with the XOR operation (i.e., subtraction without carry). The CRC algorithm uses the term, polynomial, to perform all of its calculations.

The divisor, dividend and remainder that are represented by numbers are termed as polynomials with binary coefficients.

The programmable CRC generator offers the following features:

- · User-programmable polynomial CRC equation

- Interrupt output

- Data FIFO

The module implements a software-configurable CRC generator. The terms of the polynomial and its length can be programmed using the CRCXOR (X<15:1>) bits and the CRCCON (PLEN<3:0>) bits, respectively. Consider the CRC equation:

#### EQUATION 20-1: CRC

$$x^{16} + x^{12} + x^5 + 1 \\$$

To program this polynomial into the CRC generator, the CRC register bits should be set as provided in Table 20-1.

#### TABLE 20-1: EXAMPLE CRC SETUP

| Bit Name  | Bit Value      |

|-----------|----------------|

| PLEN<3:0> | 1111           |

| X<15:1>   | 00010000010000 |

The value of X<15:1>, the  $12^{th}$  bit and the  $5^{th}$  bit are set to '1', as required by the equation. The 0 bit required by the equation is always XORed. For a 16-bit polynomial, the  $16^{th}$  bit is also always assumed to be XORed; therefore, the X<15:1> bits do not have the 0 bit or the  $16^{th}$  bit.

The topology of a standard CRC generator is displayed in Figure 20-2.

#### FIGURE 20-1: CRC SHIFTER DETAILS

© 2008-2011 Microchip Technology Inc.

| REGISTER 22-1: AD1CON1: A/D CONTROL REGISTER |

|----------------------------------------------|

|----------------------------------------------|

| R/W-0               | U-0 | R/W-0  | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|---------------------|-----|--------|-----|-----|-----|-------|-------|

| ADON <sup>(1)</sup> | —   | ADSIDL | —   | —   | —   | FORM1 | FORM0 |

| bit 15              |     |        |     |     |     |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0, HSC | R/W-0, HSC |

|-------|-------|-------|-----|-----|-------|------------|------------|

| SSRC2 | SSRC1 | SSRC0 | —   |     | ASAM  | SAMP       | DONE       |

| bit 7 |       |       |     |     |       |            | bit 0      |

| Legend:      |                                                                                    | HSC = Hardware Setta                                                                     | ble/Clearable bit                                                                                                  |                                |

|--------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------|

| R = Readal   | ble bit                                                                            | W = Writable bit                                                                         | U = Unimplemented bit,                                                                                             | read as '0'                    |

| -n = Value a | at POR                                                                             | '1' = Bit is set                                                                         | '0' = Bit is cleared                                                                                               | x = Bit is unknown             |

| bit 15       |                                                                                    | /D Operating Mode bit <sup>(1)</sup>                                                     |                                                                                                                    |                                |

|              |                                                                                    | Converter module is operatin<br>Converter is off                                         | g                                                                                                                  |                                |

| bit 14       | Unimple                                                                            | mented: Read as '0'                                                                      |                                                                                                                    |                                |

| bit 13       | ADSIDL:                                                                            | Stop in Idle Mode bit                                                                    |                                                                                                                    |                                |

|              |                                                                                    | ontinue module operation wh<br>inue module operation in Idle                             |                                                                                                                    |                                |

| bit 12-10    | Unimple                                                                            | mented: Read as '0'                                                                      |                                                                                                                    |                                |

| bit 9-8      | FORM<1                                                                             | :0>: Data Output Format bits                                                             | i                                                                                                                  |                                |

|              | 10 = Frac<br>01 = Sigr                                                             | ned fractional (sddd dddd d<br>stional (dddd dddd dd00 (<br>ned integer (ssss sssd dd    | 0000)<br>dd dddd)                                                                                                  |                                |

| h:+ 7 5      |                                                                                    | ger (0000 00dd dddd ddd                                                                  |                                                                                                                    |                                |

| bit 7-5      | 111 = Int<br>110 = CT<br>101 = Re<br>100 = Re<br>011 = Re<br>010 = Tir<br>001 = Ac | MU event ends sampling an<br>eserved<br>eserved<br>eserved<br>ner3 compare ends sampling | and starts conversion (auto-co<br>d starts conversion<br>g and starts conversion<br>ids sampling and starts conver |                                |

| bit 4-3      | Unimple                                                                            | mented: Read as '0'                                                                      |                                                                                                                    |                                |

| bit 2        | ASAM: A                                                                            | /D Sample Auto-Start bit                                                                 |                                                                                                                    |                                |

|              |                                                                                    | pling begins immediately afte<br>pling begins when SAMP bit                              | er last conversion completes; S<br>is set                                                                          | SAMP bit is auto-set           |

| bit 1        | 1 = A/D s                                                                          | /D Sample Enable bit<br>ample/hold amplifier is samp<br>ample/hold amplifier is holdii   |                                                                                                                    |                                |

| bit 0        | <b>DONE:</b> A<br>1 = A/D c                                                        | /D Conversion Status bit<br>conversion is done<br>conversion is not done                 | -                                                                                                                  |                                |

| Note 1:      |                                                                                    | C1BUEn registers will not ret                                                            | ain their values once the ADO                                                                                      | N hit is cleared. Read out the |

**Note 1:** Values of ADC1BUFn registers will not retain their values once the ADON bit is cleared. Read out the conversion values from the buffer before disabling the module.

#### REGISTER 25-1: CTMUCON: CTMU CONTROL REGISTER (CONTINUED)

bit 3-2

EDG1SEL<1:0>: Edge 1 Source Select bits

11 = CTED1 pin

10 = CTED2 pin

01 = OC1 module

00 = Timer1 module

bit 1

EDG2STAT: Edge 2 Status bit

1 = Edge 2 event has occurred

0 = Edge 2 event has not occurred

bit 0

EDG1STAT: Edge 1 Status bit

1 = Edge 1 event has occurred

0 = Edge 1 event has not occurred

#### **REGISTER 25-2: CTMUICON: CTMU CURRENT CONTROL REGISTER**

| R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

|--------|--------|--------|--------|--------|--------|-------|-------|

| ITRIM5 | ITRIM4 | ITRIM3 | ITRIM2 | ITRIM1 | ITRIM0 | IRNG1 | IRNG0 |

| bit 15 |        |        | •      |        |        |       | bit 8 |

|        |        |        |        |        |        |       |       |

| U-0    | U-0    | U-0    | U-0    | U-0    | U-0    | U-0   | U-0   |

| —      | —      | —      | —      |        |        | —     | —     |

| bit 7  |        |        |        |        |        |       | bit 0 |

|        |        |        |        |        |        |       |       |

| Logond |        |        |        |        |        |       |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-10 | ITRIM<5:0>: Current Source Trim bits                   |

|-----------|--------------------------------------------------------|

|           | 011111 = Maximum positive change from nominal current  |

|           | 011110                                                 |

|           |                                                        |

|           |                                                        |

|           | •                                                      |

|           | 000001 = Minimum positive change from nominal current  |

|           | 000000 = Nominal current output specified by IRNG<1:0> |

|           | 111111 = Minimum negative change from nominal current  |

|           | •                                                      |

|           |                                                        |

|           | •                                                      |

|           | 100010                                                 |

|           | 100000 = Maximum negative change from nominal current  |

| bit 9-8   | IRNG<1:0>: Current Source Range Select bits            |

|           | 11 = 100 × Base current                                |

|           | 10 = 10 × Base current                                 |

|           | 01 = Base current level (0.55 μA nominal)              |

|           | 00 = Current source is disabled                        |

| bit 7-0   | Unimplemented: Read as '0'                             |

|           |                                                        |

| Assembly<br>Mnemonic |        | Assembly Syntax Description |                              | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |  |  |  |

|----------------------|--------|-----------------------------|------------------------------|---------------|----------------|--------------------------|--|--|--|

| TBLRDL               | TBLRDL | Ws,Wd                       | Read Prog<15:0> to Wd        | 1             | 2              | None                     |  |  |  |

| TBLWTH               | TBLWTH | Ws,Wd                       | Write Ws<7:0> to Prog<23:16> | 1             | 2              | None                     |  |  |  |

| TBLWTL               | TBLWTL | Ws,Wd                       | Write Ws to Prog<15:0>       | 1             | 2              | None                     |  |  |  |

| ULNK                 | ULNK   |                             | Unlink Frame Pointer         | 1             | 1              | None                     |  |  |  |

| XOR                  | XOR    | f                           | f = f .XOR. WREG             | 1             | 1              | N, Z                     |  |  |  |

|                      | XOR    | f,WREG                      | WREG = f .XOR. WREG          | 1             | 1              | N, Z                     |  |  |  |

|                      | XOR    | #lit10,Wn                   | Wd = lit10 .XOR. Wd          | 1             | 1              | N, Z                     |  |  |  |

|                      | XOR    | Wb,Ws,Wd                    | Wd = Wb .XOR. Ws             | 1             | 1              | N, Z                     |  |  |  |

|                      | XOR    | Wb,#lit5,Wd                 | Wd = Wb .XOR. lit5           | 1             | 1              | N, Z                     |  |  |  |

| ZE                   | ZE     | Ws,Wnd                      | Wnd = Zero-Extend Ws         | 1             | 1              | C, Z, N                  |  |  |  |

#### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

### 29.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC24F16KA102 family electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC24F16KA102 family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these, or any other conditions above the parameters indicated in the operation listings of this specification, is not implied.

### Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                      | 40°C to +125°C       |

|---------------------------------------------------------------------|----------------------|

| Storage temperature                                                 | 65°C to +175°C       |

| Voltage on VDD with respect to Vss                                  | 0.3V to +5.0V        |

| Voltage on any combined analog and digital pin, with respect to Vss | 0.3V to (VDD + 0.3V) |

| Voltage on any digital only pin with respect to Vss                 | 0.3V to (VDD + 0.3V) |

| Voltage on MCLR/VPP pin with respect to Vss                         | 0.3V to +9.0V        |

| Maximum current out of Vss pin                                      |                      |

| Maximum current into VDD pin <sup>(1)</sup>                         | 250 mA               |

| Maximum output current sunk by any I/O pin                          | 25 mA                |

| Maximum output current sourced by any I/O pin                       | 25 mA                |

| Maximum current sunk by all ports                                   | 200 mA               |

| Maximum current sourced by all ports <sup>(1)</sup>                 | 200 mA               |

Note 1: Maximum allowable current is a function of device maximum power dissipation (see Table 29-1).

**† NOTICE:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

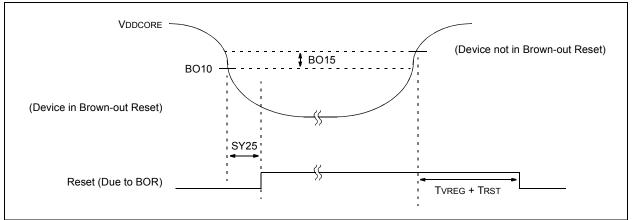

#### FIGURE 29-3: BROWN-OUT RESET CHARACTERISTICS

#### TABLE 29-5:BOR TRIP POINTS

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |       |                               |          |      |      |      |       |                      |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------|----------|------|------|------|-------|----------------------|--|

| Param<br>No.                                                                                                                                                                            | Sym   | Sym Characteristic            |          |      | Тур  | Max  | Units | Conditions           |  |

| DC19                                                                                                                                                                                    | VBOR  | BOR Voltage on VDD Transition | BOR = 00 | _    | _    | —    | _     | LPBOR <sup>(1)</sup> |  |

|                                                                                                                                                                                         |       |                               | BOR = 01 | 2.92 | 3    | 3.08 | V     |                      |  |

|                                                                                                                                                                                         |       |                               | BOR = 10 | 2.63 | 2.7  | 2.77 | V     |                      |  |

|                                                                                                                                                                                         |       |                               | BOR = 11 | 1.75 | 1.82 | 1.85 | V     |                      |  |

| DC14                                                                                                                                                                                    | VBHYS | BOR Hysteresis                |          |      | 5    |      | mV    |                      |  |

**Note 1:** LPBOR re-arms the POR circuit, but does not cause a BOR. LPBOR can be used to ensure a POR after the supply voltage rises to a safe operating level. It does not stop code execution after the supply voltage falls below a chosen trip point.

#### TABLE 29-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARACTEI                             | RISTICS |           | Standard Ope<br>Operating temp |            | <b>.8V to 3.6V (unless</b><br>TA $\leq$ +85°C for Indu<br>TA $\leq$ +125°C for Ext | Istrial       |  |

|------------------------------------------|---------|-----------|--------------------------------|------------|------------------------------------------------------------------------------------|---------------|--|

| Parameter No. Typical <sup>(1)</sup> Max |         |           | Units                          | Conditions |                                                                                    |               |  |

| IDD Current <sup>(2)</sup>               |         |           |                                |            |                                                                                    |               |  |

| DC20                                     |         | 330       |                                | -40°C      |                                                                                    |               |  |

| DS20a                                    |         | 330       |                                | +25°C      |                                                                                    |               |  |

| DC20b                                    | 195     | 330       | μΑ                             | +60°C      | 1.8V                                                                               |               |  |

| DC20c                                    |         | 330       |                                | +85°C      |                                                                                    |               |  |

| DC20d                                    |         | 500       |                                | +125°C     |                                                                                    | 0.5 MIPS,     |  |

| DC20e                                    |         | 590       |                                | -40°C      |                                                                                    | Fosc = 1 MHz  |  |

| DC20f                                    | 1       | 590       |                                | +25°C      |                                                                                    |               |  |

| DC20g                                    | 365     | 645       | μΑ                             | +60°C      | 3.3V                                                                               |               |  |

| DC20h                                    | 1 [     | 720       | 1 F                            | +85°C      |                                                                                    |               |  |

| DC20i                                    | 1       | 800       |                                | +125°C     |                                                                                    |               |  |

| DC22                                     |         | 600       |                                | -40°C      |                                                                                    |               |  |

| DC22a                                    |         | 600       |                                | +25°C      |                                                                                    |               |  |

| DC22b                                    | 363     | 600       | μΑ                             | +60°C      | 1.8V                                                                               |               |  |

| DC22c                                    |         | 600 +85°C |                                |            |                                                                                    |               |  |

| DC22d                                    |         | 800       |                                | +125°C     |                                                                                    | 1 MIPS,       |  |

| DC22e                                    |         | 1100      |                                | -40°C      |                                                                                    | Fosc = 2 MHz  |  |

| DC22f                                    |         | 1100      |                                | +25°C      |                                                                                    |               |  |

| DC22g                                    | 695     | 1100      | μΑ                             | +60°C      | 3.3V                                                                               |               |  |

| DC22h                                    |         | 1100      |                                | +85°C      |                                                                                    |               |  |

| DC22i                                    |         | 1500      |                                | +125°C     |                                                                                    |               |  |

| DC23                                     |         | 18        |                                | -40°C      |                                                                                    |               |  |

| DC23a                                    |         | 18        |                                | +25°C      |                                                                                    |               |  |

| DC23b                                    | 11      | 18        | mA                             | +60°C      | 3.3V                                                                               | 16 MIPS,      |  |

| DC23c                                    |         | 18        |                                | +85°C      |                                                                                    | Fosc = 32 MHz |  |

| DC23d                                    | 1 1     | 18        | 1                              | +125°C     |                                                                                    |               |  |

| DC27                                     |         | 3.40      |                                | -40°C      |                                                                                    |               |  |

| DC27a                                    | 1 [     | 3.40      | 1                              | +25°C      |                                                                                    |               |  |

| DC27b                                    | 2.25    | 3.40      | mA                             | +60°C      | 2.5V                                                                               |               |  |

| DC27c                                    | 1 [     | 3.40      | 7                              | +85°C      |                                                                                    |               |  |

| DC27d                                    | 1 [     | 3.40      | 1 F                            | +125°C     |                                                                                    | FRC (4 MIPS), |  |

| DC27e                                    |         | 4.60      |                                | -40°C      |                                                                                    | Fosc = 8 MHz  |  |

| DC27f                                    | 1 [     | 4.60      | 1 F                            | +25°C      |                                                                                    |               |  |

| DC27g                                    | 3.05    | 4.60      | mA                             | +60°C      | 3.3V                                                                               |               |  |

| DC27h                                    | 1 [     | 4.60      | 1                              | +85°C      |                                                                                    |               |  |

| DC27i                                    | 1 [     | 5.40      | 7                              | +125°C     |                                                                                    |               |  |

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**2:** Operating Parameters:

• EC mode with clock input driven with a square wave rail-to-rail

· I/Os are configured as outputs, driven low

• MCLR – VDD

WDT FSCM is disabled

• SRAM, program and data memory are active

• All PMD bits are set except for modules being measured

| AC CHA       | RACTERIS |                            | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{(Industrial)} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |             |      |       |                                                     |

|--------------|----------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|-------|-----------------------------------------------------|

| Param<br>No. | Symbol   | Charact                    | eristic                                                                                                                                                                                                                                                                              | Min         | Max  | Units | Conditions                                          |

| IS10         | TLO:SCL  | Clock Low Time             | 100 kHz mode                                                                                                                                                                                                                                                                         | 4.7         | —    | μS    | Device must operate at a minimum of 1.5 MHz         |

|              |          |                            | 400 kHz mode                                                                                                                                                                                                                                                                         | 1.3         | _    | μS    | Device must operate at a minimum of 10 MHz          |

|              |          |                            | 1 MHz mode <sup>(1)</sup>                                                                                                                                                                                                                                                            | 0.5         | —    | μS    |                                                     |

| IS11         | THI:SCL  | Clock High Time            | 100 kHz mode                                                                                                                                                                                                                                                                         | 4.0         | —    | μS    | Device must operate at a minimum of 1.5 MHz         |

|              |          |                            | 400 kHz mode                                                                                                                                                                                                                                                                         | 0.6         | —    | μS    | Device must operate at a minimum of 10 MHz          |

|              |          |                            | 1 MHz mode <sup>(1)</sup>                                                                                                                                                                                                                                                            | 0.5         |      | μS    |                                                     |

| IS20         | TF:SCL   | SDAx and SCLx<br>Fall Time | 100 kHz mode                                                                                                                                                                                                                                                                         | —           | 300  | ns    | CB is specified to be from                          |

|              |          |                            | 400 kHz mode                                                                                                                                                                                                                                                                         | 20 + 0.1 Св | 300  | ns    | 10 to 400 pF                                        |

|              |          |                            | 1 MHz mode <sup>(1)</sup>                                                                                                                                                                                                                                                            | —           | 100  | ns    |                                                     |

| IS21         | TR:SCL   | SDAx and SCLx<br>Rise Time | 100 kHz mode                                                                                                                                                                                                                                                                         | —           | 1000 | ns    | CB is specified to be from                          |

|              |          |                            | 400 kHz mode                                                                                                                                                                                                                                                                         | 20 + 0.1 Св | 300  | ns    | 10 to 400 pF                                        |

|              |          |                            | 1 MHz mode <sup>(1)</sup>                                                                                                                                                                                                                                                            | —           | 300  | ns    |                                                     |

| IS25         | TSU:DAT  | Data Input                 | 100 kHz mode                                                                                                                                                                                                                                                                         | 250         | _    | ns    |                                                     |

|              |          | Setup Time                 | 400 kHz mode                                                                                                                                                                                                                                                                         | 100         | —    | ns    |                                                     |

|              |          |                            | 1 MHz mode <sup>(1)</sup>                                                                                                                                                                                                                                                            | 100         | —    | ns    |                                                     |

| IS26         | THD:DAT  | Data Input                 | 100 kHz mode                                                                                                                                                                                                                                                                         | 0           | —    | ns    |                                                     |

|              |          | Hold Time                  | 400 kHz mode                                                                                                                                                                                                                                                                         | 0           | 0.9  | μS    | -                                                   |

|              |          |                            | 1 MHz mode <sup>(1)</sup>                                                                                                                                                                                                                                                            | 0           | 0.3  | μS    |                                                     |

| IS40         | TAA:SCL  | Output Valid From          | 100 kHz mode                                                                                                                                                                                                                                                                         | 0           | 3500 | ns    |                                                     |

|              |          | Clock                      | 400 kHz mode                                                                                                                                                                                                                                                                         | 0           | 1000 | ns    |                                                     |

|              |          |                            | 1 MHz mode <sup>(1)</sup>                                                                                                                                                                                                                                                            | 0           | 350  | ns    |                                                     |

| IS45         | TBF:SDA  | Bus Free Time              | 100 kHz mode                                                                                                                                                                                                                                                                         | 4.7         | _    | μS    | Time the bus must be free before a new transmission |