Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

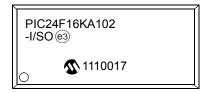

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 18                                                                           |

| Program Memory Size        | 16KB (5.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 1.5K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 9x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 20-VQFN (5x5)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16ka101-i-mq |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| File Name | Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                 | Bit 8                               | Bit 7                 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|---------|--------|---------|--------|--------|--------|-----------------------|-------------------------------------|-----------------------|-------|-------|-------|-------|-------|-------|-------|---------------|

| I2C1RCV   | 0200 | _       | _      | _       | _      | _      |        | _                     | _                                   | I2C1 Receive Register |       |       |       |       |       |       | 0000  |               |

| I2C1TRN   | 0202 | _       | _      | —       | —      | _      | -      | _                     | I2C1 Transmit Register              |                       |       |       |       |       |       | 00FF  |       |               |

| I2C1BRG   | 0204 | _       | _      | _       | _      | _      | _      | _                     | — I2C1 Baud Rate Generator Register |                       |       |       |       |       |       | 0000  |       |               |

| I2C1CON   | 0206 | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                | SMEN                                | GCEN                  | STREN | ACKDT | ACKEN | RCEN  | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT  | 0208 | ACKSTAT | TRSTAT | _       | _      | -      | BCL    | GCSTAT                | ADD10                               | IWCOL                 | I2COV | D/A   | Р     | S     | R/W   | RBF   | TBF   | 0000          |

| I2C1ADD   | 020A | _       | _      | _       | _      | _      | _      | I2C1 Address Register |                                     |                       |       |       |       |       | 0000  |       |       |               |

| I2C1MSK   | 020C |         | _      | _       | _      | -      |        | AMSK9                 | AMSK8                               | AMSK7                 | AMSK6 | AMSK5 | AMSK4 | AMSK3 | AMSK2 | AMSK1 | AMSK0 | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in h.5adecimal.

### TABLE 4-10: UART REGISTER MAP

| File<br>Name | Addr | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8                   | Bit 7                                                     | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|------|----------|--------|----------|--------|--------|--------|--------|-------------------------|-----------------------------------------------------------|----------|-------|-------|-------|--------|--------|-------|---------------|

| U1MODE       | 0220 | UARTEN   | _      | USIDL    | IREN   | RTSMD  | _      | UEN1   | UEN0                    | UEN0 WAKE LPBACK ABAUD RXINV BRGH PDSEL1 PDSEL0 STSEL     |          |       |       |       |        | 0000   |       |               |

| U1STA        | 0222 | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF  | TRMT                    | TRMT URXISEL1 URXISEL0 ADDEN RIDLE PERR FERR OERR URXDA ( |          |       |       |       |        |        | 0110  |               |

| U1TXREG      | 0224 | _        | _      | _        | _      | _      |        | _      | UART1 Transmit Register |                                                           |          |       |       |       |        | 0000   |       |               |

| U1RXREG      | 0226 | _        | _      | _        | _      | _      |        | _      |                         | UART1 Receive Register                                    |          |       |       |       |        |        | 0000  |               |

| U1BRG        | 0228 |          |        |          |        |        |        | Baud R | ate Genera              | ator Prescaler                                            | Register |       |       |       |        |        |       | 0000          |

| U2MODE       | 0230 | UARTEN   | _      | USIDL    | IREN   | RTSMD  |        | UEN1   | UEN0                    | WAKE                                                      | LPBACK   | ABAUD | RXINV | BRGH  | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA        | 0232 | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF  | TRMT                    | URXISEL1                                                  | URXISEL0 | ADDEN | RIDLE | PERR  | FERR   | OERR   | URXDA | 0110          |

| U2TXREG      | 0234 | _        | _      | —        | _      | _      | _      | _      | UART2 Transmit Register |                                                           |          |       |       |       |        | 0000   |       |               |

| U2RXREG      | 0236 | _        | _      | —        | _      | —      | _      | _      | UART2 Receive Register  |                                                           |          |       |       |       |        | 0000   |       |               |

| U2BRG        | 0238 |          |        |          |        |        |        | Bau    | ud Rate Ge              | enerator Prese                                            | caler    |       |       |       |        |        |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-11: SPI REGISTER MAP

| File<br>Name | Addr | Bit 15                       | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10  | Bit 9   | Bit 8   | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|------------------------------|--------|---------|--------|--------|---------|---------|---------|-------|--------|--------|--------|--------|--------|--------|--------|---------------|

| SPI1STAT     | 0240 | SPIEN                        | _      | SPISIDL | _      | _      | SPIBEC2 | SPIBEC1 | SPIBEC0 | SRMPT | SPIROV | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI1CON1     | 0242 |                              | _      | -       | DISSCK | DISSDO | MODE16  | SMP     | CKE     | SSEN  | CKP    | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI1CON2     | 0244 | FRMEN                        | SPIFSD | SPIFPOL | —      | _      | _       | _       | —       | _     | _      | —      | _      | _      | —      | SPIFE  | SPIBEN | 0000          |

| SPI1BUF      | 0248 | SPI1 Transmit/Receive Buffer |        |         |        |        |         |         |         |       |        | 0000   |        |        |        |        |        |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

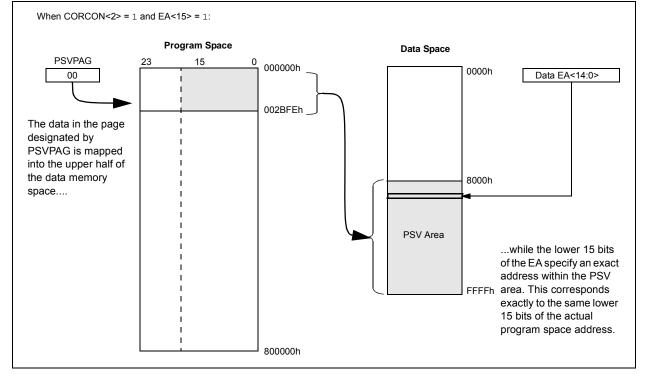

#### 4.3.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into an 8K word page (in PIC24F08KA1XX devices) and a 16K word page (in PIC24F16KA1XX devices) of the program space. This provides transparent access of stored constant data from the data space without the need to use special instructions (i.e., TBLRDL/H).

Program space access through the data space occurs if the MSb of the data space, EA, is '1', and PSV is enabled by setting the PSV bit in the CPU Control (CORCON<2>) register. The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page Address register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits.

By incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads from this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address, 8000h and higher, maps directly into a corresponding program memory address (see Figure 4-7), only the lower 16 bits of the 24-bit program word are used to contain the data. The upper 8 bits of any program space locations used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

| Note: | PSV access is temporarily disabled during |

|-------|-------------------------------------------|

|       | table reads/writes.                       |

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV.D instructions will require one instruction cycle in addition to the specified execution time. All other instructions will require two instruction cycles in addition to the specified execution time.

For operations that use PSV, which are executed inside a REPEAT loop, there will be some instances that require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction accessing data, using PSV, to execute in a single cycle.

### FIGURE 4-7: PROGRAM SPACE VISIBILITY OPERATION

### 6.4.1 ERASE DATA EEPROM

The data EEPROM can be fully erased, or can be partially erased, at three different sizes: one word, four words or eight words. The bits, NVMOP<1:0> (NVMCON<1:0>), decide the number of words to be erased. To erase partially from the data EEPROM, the following sequence must be followed:

- 1. Configure NVMCON to erase the required number of words: one, four or eight.

- 2. Load TBLPAG and WREG with the EEPROM address to be erased.

- 3. Clear NVMIF status bit and enable NVM interrupt (optional).

- 4. Write the key sequence to NVMKEY.

- 5. Set the WR bit to begin erase cycle.

- 6. Either poll the WR bit or wait for the NVM interrupt (NVMIF set).

### EXAMPLE 6-2: SINGLE-WORD ERASE

A typical erase sequence is provided in Example 6-2. This example shows how to do a one-word erase. Similarly, a four-word erase and an eight-word erase can be done. This example uses 'C' library procedures to manage the Table Pointer (builtin\_tblpage and builtin\_tbloffset) and the Erase Page Pointer (builtin\_tblwt1). The memory unlock sequence (builtin\_write\_NVM) also sets the WR bit to initiate the operation and returns control when complete.

```

int __attribute__ ((space(eedata))) eeData = 0x1234; // Variable located in EEPROM

unsigned int offset;

// Set up NVMCON to erase one word of data EEPROM

NVMCON = 0x4058;

// Set up a pointer to the EEPROM location to be erased

TBLPAG = __builtin_tblpage(&eeData); // Initialize EE Data page pointer

offset = __builtin_tbloffset(&eeData); // Initialize lower word of address

__builtin_tblwtl(offset, 0); // Write EEPROM data to write latch

asm volatile ("disi #5"); // Disable Interrupts For 5 Instructions

__builtin_write_NVM(); // Issue Unlock Sequence & Start Write Cycle

```

### REGISTER 8-1: SR: ALU STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-0, HSC          |

|--------|-----|-----|-----|-----|-----|-----|-------------------|

| —      | —   | —   | —   | —   | —   | —   | DC <sup>(1)</sup> |

| bit 15 |     |     |     |     |     |     | bit 8             |

| R/W-0, HSC            | R/W-0, HSC            | R/W-0, HSC            | R-0, HSC          | R/W-0, HSC       | R/W-0, HSC        | R/W-0, HSC       | R/W-0, HSC       |

|-----------------------|-----------------------|-----------------------|-------------------|------------------|-------------------|------------------|------------------|

| IPL2 <sup>(2,3)</sup> | IPL1 <sup>(2,3)</sup> | IPL0 <sup>(2,3)</sup> | RA <sup>(1)</sup> | N <sup>(1)</sup> | OV <sup>(1)</sup> | Z <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7                 |                       |                       |                   |                  |                   |                  | bit 0            |

| Legend:           | HSC = Hardware Settable/0 | HSC = Hardware Settable/Clearable bit |                    |  |  |  |  |

|-------------------|---------------------------|---------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit          | U = Unimplemented bit, read as '0'    |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared                  | x = Bit is unknown |  |  |  |  |

#### bit 15-9 Unimplemented: Read as '0'

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>                                                                                                                                                                                          |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>111 = CPU interrupt priority level is 7 (15); user interrupts disabled</li> <li>110 = CPU interrupt priority level is 6 (14)</li> <li>101 = CPU interrupt priority level is 5 (13)</li> <li>100 = CPU interrupt priority level is 4 (12)</li> </ul> |

|         | 011 = CPU interrupt priority level is 3 (11)                                                                                                                                                                                                                 |

|         | 010 = CPU interrupt priority level is 2 (10)                                                                                                                                                                                                                 |

|         | 001 = CPU interrupt priority level is 1 (9)                                                                                                                                                                                                                  |

|         | 000 = CPU interrupt priority level is 0 (8)                                                                                                                                                                                                                  |

|         |                                                                                                                                                                                                                                                              |

Note 1: See Register 3-1 for the description of these bits, which are not dedicated to interrupt control functions.

- **2:** The IPL bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU interrupt priority level. The value in parentheses indicates the interrupt priority level if IPL3 = 1.

- **3:** The IPL Status bits are read-only when NSTDIS (INTCON1<15>) = 1.

Note: Bit 8 and Bits 4 through 0 are described in Section 3.0 "CPU".

| R/W-0         | U-0                                                                                                               | R/W-0                                                                                              | R/W-0            | R/W-0             | R/W-0           | R/W-0           | R/W-0         |  |  |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------|-------------------|-----------------|-----------------|---------------|--|--|--|--|--|--|

| NVMIE         | 0-0                                                                                                               | AD1IE                                                                                              | U1TXIE           | U1RXIE            | SPI1IE          | SPF1IE          | T3IE          |  |  |  |  |  |  |

| bit 15        |                                                                                                                   | ADTIL                                                                                              | UTTAL            | UIIXIL            | SITTL           | SITTL           | bit           |  |  |  |  |  |  |

|               |                                                                                                                   |                                                                                                    |                  |                   |                 |                 | bit           |  |  |  |  |  |  |

| R/W-0         | U-0                                                                                                               | U-0                                                                                                | U-0              | R/W-0             | R/W-0           | R/W-0           | R/W-0         |  |  |  |  |  |  |

| T2IE          | —                                                                                                                 | —                                                                                                  | _                | T1IE              | OC1IE           | IC1IE           | <b>INTOIE</b> |  |  |  |  |  |  |

| bit 7         |                                                                                                                   |                                                                                                    |                  |                   |                 |                 | bit           |  |  |  |  |  |  |

| Legend:       |                                                                                                                   |                                                                                                    |                  |                   |                 |                 |               |  |  |  |  |  |  |

| R = Readabl   | e bit                                                                                                             | W = Writable                                                                                       | bit              | U = Unimplem      | ented bit, read | d as '0'        |               |  |  |  |  |  |  |

| -n = Value at | POR                                                                                                               | '1' = Bit is set                                                                                   |                  | '0' = Bit is clea | ared            | x = Bit is unkn | own           |  |  |  |  |  |  |

| bit 15        |                                                                                                                   | Interrunt Enab                                                                                     | le hit           |                   |                 |                 |               |  |  |  |  |  |  |

|               | <b>NVMIE:</b> NVM Interrupt Enable bit<br>1 = Interrupt request is enabled                                        |                                                                                                    |                  |                   |                 |                 |               |  |  |  |  |  |  |

|               |                                                                                                                   | equest is not e                                                                                    |                  |                   |                 |                 |               |  |  |  |  |  |  |

| bit 14        | Unimplemen                                                                                                        | ted: Read as '                                                                                     | )'               |                   |                 |                 |               |  |  |  |  |  |  |

| bit 13        | AD1IE: A/D C                                                                                                      | Conversion Con                                                                                     | nplete Interrupt | Enable bit        |                 |                 |               |  |  |  |  |  |  |

|               |                                                                                                                   | equest is enab<br>equest is not e                                                                  |                  |                   |                 |                 |               |  |  |  |  |  |  |

| bit 12        | -                                                                                                                 | RT1 Transmitter                                                                                    |                  | ole bit           |                 |                 |               |  |  |  |  |  |  |

|               |                                                                                                                   | equest is enab                                                                                     | -                |                   |                 |                 |               |  |  |  |  |  |  |

|               | 0 = Interrupt r                                                                                                   | equest is not e                                                                                    | nabled           |                   |                 |                 |               |  |  |  |  |  |  |

| bit 11        | U1RXIE: UART1 Receiver Interrupt Enable bit                                                                       |                                                                                                    |                  |                   |                 |                 |               |  |  |  |  |  |  |

|               | 1 = Interrupt request is enabled                                                                                  |                                                                                                    |                  |                   |                 |                 |               |  |  |  |  |  |  |

|               | <ul> <li>Interrupt request is not enabled</li> <li>SPI1IE: SPI1 Transfer Complete Interrupt Enable bit</li> </ul> |                                                                                                    |                  |                   |                 |                 |               |  |  |  |  |  |  |

| bit 10        |                                                                                                                   | •                                                                                                  | •                | -nable bit        |                 |                 |               |  |  |  |  |  |  |

|               |                                                                                                                   | equest is enab<br>equest is not e                                                                  |                  |                   |                 |                 |               |  |  |  |  |  |  |

| bit 9         | -                                                                                                                 | Fault Interrupt                                                                                    |                  |                   |                 |                 |               |  |  |  |  |  |  |

|               |                                                                                                                   | equest is enab                                                                                     |                  |                   |                 |                 |               |  |  |  |  |  |  |

|               |                                                                                                                   | equest is not e                                                                                    |                  |                   |                 |                 |               |  |  |  |  |  |  |

| bit 8         | T3IE: Timer3                                                                                                      | Interrupt Enabl                                                                                    | e bit            |                   |                 |                 |               |  |  |  |  |  |  |

|               |                                                                                                                   | equest is enab                                                                                     |                  |                   |                 |                 |               |  |  |  |  |  |  |

|               |                                                                                                                   | equest is not e                                                                                    |                  |                   |                 |                 |               |  |  |  |  |  |  |

| bit 7         |                                                                                                                   | Interrupt Enabl                                                                                    |                  |                   |                 |                 |               |  |  |  |  |  |  |

|               |                                                                                                                   | equest is enab<br>equest not is e                                                                  |                  |                   |                 |                 |               |  |  |  |  |  |  |

| bit 6-4       | Unimplemen                                                                                                        | ted: Read as '                                                                                     | )'               |                   |                 |                 |               |  |  |  |  |  |  |

| bit 3         | T1IE: Timer1                                                                                                      | Interrupt Enabl                                                                                    | e bit            |                   |                 |                 |               |  |  |  |  |  |  |

|               |                                                                                                                   | equest is enab<br>equest is not e                                                                  |                  |                   |                 |                 |               |  |  |  |  |  |  |

| bit 2         |                                                                                                                   | ut Compare Ch                                                                                      |                  | pt Enable bit     |                 |                 |               |  |  |  |  |  |  |

|               | •                                                                                                                 | equest is enab                                                                                     |                  | •                 |                 |                 |               |  |  |  |  |  |  |

|               |                                                                                                                   | equest is not e                                                                                    |                  |                   |                 |                 |               |  |  |  |  |  |  |

| bit 1         | IC1IE: Input C                                                                                                    | Capture Channe                                                                                     | el 1 Interrupt E | nable bit         |                 |                 |               |  |  |  |  |  |  |

|               |                                                                                                                   | equest is enab<br>equest is not e                                                                  |                  |                   |                 |                 |               |  |  |  |  |  |  |

| bit 0         | •                                                                                                                 | nal Interrupt 0                                                                                    |                  |                   |                 |                 |               |  |  |  |  |  |  |

|               |                                                                                                                   | -                                                                                                  |                  |                   |                 |                 |               |  |  |  |  |  |  |

|               | ±                                                                                                                 | <ul> <li>1 = Interrupt request is enabled</li> <li>0 = Interrupt request is not enabled</li> </ul> |                  |                   |                 |                 |               |  |  |  |  |  |  |

### REGISTER 10-4: PMD2: PERIPHERAL MODULE DISABLE REGISTER 2

| · · · · · · · · · · · · · · · · · · · |     |     |     |     |     |     |        |

|---------------------------------------|-----|-----|-----|-----|-----|-----|--------|

| U-0                                   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

| _                                     | —   | —   | —   | —   | —   | —   | I2C1MD |

| bit 15                                |     |     |     |     |     |     | bit 8  |

|                                       |     |     |     |     |     |     |        |

| U-0                                   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

|                                       |     |     |     |     |     |     |        |

| —     | — | _ | — | — | — | — | OC1MD |

|-------|---|---|---|---|---|---|-------|

| bit 7 |   |   |   |   |   |   | bit 0 |

|       |   |   |   |   |   |   |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-9 Unimplemented: Read as '0'

bit 8 I2C1MD: Input Capture 1 Module Disable bit 1 = Input Capture 1 module is disabled. All Input Capture registers are held in Reset and are not writable. 0 = Input Capture 1 module is writable

#### bit 7-1 Unimplemented: Read as '0'

#### bit 0 OC1MD: Input Compare 1 Module Disable bit

- 1 = Output Compare 1 module is disabled. All Output Compare registers are held in Reset and are not writable.

- 0 = Output Compare 1 module is writable

| REGISTER 10-6: PMD4: PERIPHERAL MODULE DISABLE REGISTER 4 |                                                                                                                                                 |                                 |                           |                  |                 |                  |             |  |  |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------|------------------|-----------------|------------------|-------------|--|--|

| U-0                                                       | U-0                                                                                                                                             | U-0                             | U-0                       | U-0              | U-0             | U-0              | U-0         |  |  |

| —                                                         | —                                                                                                                                               | —                               |                           | —                | —               | —                | —           |  |  |

| bit 15                                                    |                                                                                                                                                 |                                 |                           |                  |                 |                  | bit 8       |  |  |

| r                                                         |                                                                                                                                                 |                                 |                           |                  |                 |                  |             |  |  |

| U-0                                                       | U-0                                                                                                                                             | U-0                             | R/W-0                     | R/W-0            | R/W-0           | R/W-0            | U-0         |  |  |

| —                                                         | —                                                                                                                                               | —                               | EEMD                      | REFOMD           | CTMUMD          | HLVDMD           | —           |  |  |

| bit 7                                                     |                                                                                                                                                 |                                 |                           |                  |                 |                  | bit 0       |  |  |

|                                                           |                                                                                                                                                 |                                 |                           |                  |                 |                  |             |  |  |

| Legend:                                                   |                                                                                                                                                 |                                 |                           |                  |                 |                  |             |  |  |

| R = Readab                                                | le bit                                                                                                                                          | W = Writable b                  | bit                       | U = Unimpler     | nented bit, rea | d as '0'         |             |  |  |

| -n = Value at                                             | t POR                                                                                                                                           | '1' = Bit is set                |                           | '0' = Bit is cle | ared            | x = Bit is unkn  | iown        |  |  |

|                                                           |                                                                                                                                                 |                                 |                           |                  |                 |                  |             |  |  |

| bit 15-5                                                  | Unimplemer                                                                                                                                      | nted: Read as '                 | כ'                        |                  |                 |                  |             |  |  |

| bit 4                                                     | EEMD: EEPI                                                                                                                                      | ROM Memory M                    | lodule Disable b          | bit              |                 |                  |             |  |  |

|                                                           |                                                                                                                                                 | EEPROM memo<br>I memory is dis  | ory Flash panel,<br>abled | minimizing cur   | rent consumpti  | ion              |             |  |  |

| bit 3                                                     | REFOMD: R                                                                                                                                       | eference Oscilla                | ator Module Disa          | able bit         |                 |                  |             |  |  |

|                                                           | 1 = Reference<br>are not v                                                                                                                      |                                 | dule is disabled.         | All Reference    | Oscillator regi | sters are held i | n Reset and |  |  |

|                                                           | 0 = Referen                                                                                                                                     | ce Oscillator mo                | odule is enabled          |                  |                 |                  |             |  |  |

| bit 2                                                     | CTMUMD: C                                                                                                                                       | CTMUMD: CTMU Module Disable bit |                           |                  |                 |                  |             |  |  |

|                                                           | <ul> <li>1 = CTMU module is disabled. All CTMU registers are held in Reset and are not writable.</li> <li>0 = CTMU module is enabled</li> </ul> |                                 |                           |                  |                 |                  |             |  |  |

| bit 1                                                     | HLVDMD: HI                                                                                                                                      | HLVDMD: HLVD Module Disable bit |                           |                  |                 |                  |             |  |  |

|                                                           | <ul> <li>1 = HLVD module is disabled. All HLVD registers are held in Reset and are not writable.</li> <li>0 = HLVD module is enabled</li> </ul> |                                 |                           |                  |                 |                  |             |  |  |

| bit 0                                                     | Unimplemer                                                                                                                                      | nted: Read as 'o                | כי                        |                  |                 |                  |             |  |  |

|                                                           |                                                                                                                                                 |                                 |                           |                  |                 |                  |             |  |  |

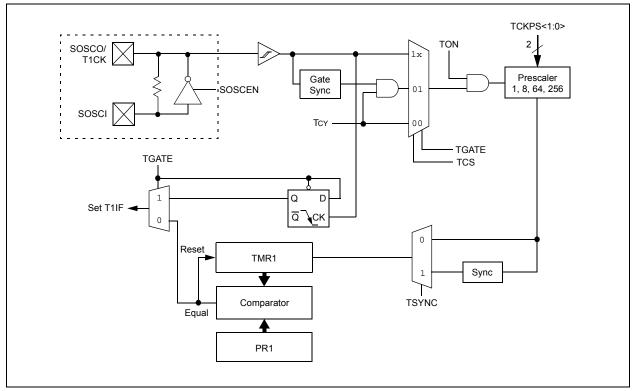

## 12.0 TIMER1

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Timers, refer to the "PIC24F Family Reference Manual", Section 14. "Timers" (DS39704).

The Timer1 module is a 16-bit timer which can serve as the time counter for the Real-Time Clock (RTC), or operate as a free-running, interval timer/counter. Timer1 can operate in three modes:

- 16-Bit Timer

- 16-Bit Synchronous Counter

- 16-Bit Asynchronous Counter

Timer1 also supports these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation During CPU Idle and Sleep modes

- Interrupt on 16-Bit Period Register Match or Falling Edge of External Gate Signal

Figure 12-1 presents a block diagram of the 16-bit Timer1 module.

To configure Timer1 for operation:

- 1. Set the TON bit (= 1).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Set or clear the TSYNC bit to configure synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the interrupt enable bit, T1IE. Use the priority bits, T1IP<2:0>, to set the interrupt priority.

## FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

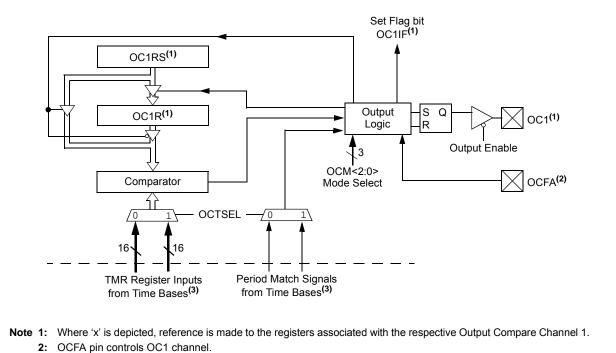

NOTES:

Control princontrols our channel.

Each output compare channel can use one of two selectable time bases. Refer to the device data sheet for the time bases associated with the module.

### REGISTER 15-2: PADCFG1: PAD CONFIGURATION CONTROL REGISTER

| U-0     | U-0 | U-0 | U-0                     | U-0                    | U-0                        | U-0                        | U-0   |

|---------|-----|-----|-------------------------|------------------------|----------------------------|----------------------------|-------|

| _       | _   | _   | —                       | —                      | —                          | -                          | _     |

| bit 15  |     |     |                         |                        |                            |                            | bit 8 |

|         |     |     |                         |                        |                            |                            |       |

| U-0     | U-0 | U-0 | R/W-0                   | R/W-0                  | R/W-0                      | R/W-0                      | R/W-0 |

|         | _   | _   | SMBUSDEL <sup>(3)</sup> | OC1TRIS <sup>(2)</sup> | RTSECSEL1 <sup>(1,4)</sup> | RTSECSEL0 <sup>(1,4)</sup> | _     |

| bit 7   |     |     |                         |                        |                            |                            | bit 0 |

|         |     |     |                         |                        |                            |                            |       |

| Logondy |     |     |                         |                        |                            |                            |       |

#### Legend:

| Legena.           |                  |                               |                    |

|-------------------|------------------|-------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read a | is 'O'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared          | x = Bit is unknown |

#### bit 15-5 Unimplemented: Read as '0'

- bit 3 OC1TRIS: OC1 Output Tri-State Select bit<sup>(2)</sup>

- 1 = OC1 output will not be active on the pin; OCPWM1 can still be used for internal triggers

- 0 = OC1 output will be active on the pin based on the OCPWM1 module settings

### bit 0 Unimplemented: Read as '0'

### Note 1: To enable the actual RTCC output, the RTCOE (RCFGCAL) bit needs to be set.

- 2: To enable the actual OC1 output, the OCPWM1 module has to be enabled.

- 3: Bit 4 is described in Section 17.0 "Inter-Integrated Circuit (I2C<sup>™</sup>)".

- 4: Bits 2 and 1 are described in Section 19.0 Real-Time Clock and Calendar (RTCC).

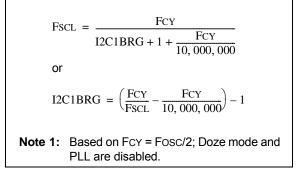

### 17.3 Setting Baud Rate When Operating as a Bus Master

To compute the Baud Rate Generator (BRG) reload value, use Equation 17-1.

# EQUATION 17-1: COMPUTING BAUD RATE RELOAD VALUE<sup>(1)</sup>

### TABLE 17-1: I<sup>2</sup>C<sup>™</sup> CLOCK RATES<sup>(1)</sup>

### 17.4 Slave Address Masking

The I2C1MSK register (Register 17-3) designates address bit positions as "don't care" for both 7-Bit and 10-Bit Addressing modes. Setting a particular bit location (= 1) in the I2C1MSK register causes the slave module to respond whether the corresponding address bit value is '0' or '1'. For example, when I2C1MSK is set to '00100000', the slave module will detect both addresses: '0000000' and '00100000'.

To enable address masking, the Intelligent Peripheral Management Interface (IPMI) must be disabled by clearing the IPMIEN bit (I2C1CON<11>).

**Note:** As a result of changes in the I<sup>2</sup>C protocol, the addresses in Table 17-2 are reserved and will not be Acknowledged in Slave mode. This includes any address mask settings that include any of these addresses.

| Required       |        | I2C1B     | RG Value      | Actual    |

|----------------|--------|-----------|---------------|-----------|

| System<br>FscL | FCY    | (Decimal) | (Hexadecimal) | FSCL      |

| 100 kHz        | 16 MHz | 157       | 9D            | 100 kHz   |

| 100 kHz        | 8 MHz  | 78        | 4E            | 100 kHz   |

| 100 kHz        | 4 MHz  | 39        | 27            | 99 kHz    |

| 400 kHz        | 16 MHz | 37        | 25            | 404 kHz   |

| 400 kHz        | 8 MHz  | 18        | 12            | 404 kHz   |

| 400 kHz        | 4 MHz  | 9         | 9             | 385 kHz   |

| 400 kHz        | 2 MHz  | 4         | 4             | 385 kHz   |

| 1 MHz          | 16 MHz | 13        | D             | 1.026 MHz |

| 1 MHz          | 8 MHz  | 6         | 6             | 1.026 MHz |

| 1 MHz          | 4 MHz  | 3         | 3             | 0.909 MHz |

Note 1: Based on Fcy = Fosc/2; Doze mode and PLL are disabled;

### TABLE 17-2: I<sup>2</sup>C<sup>™</sup> RESERVED ADDRESSES<sup>(1)</sup>

| Slave<br>Address | R/W<br>Bit | Description                            |  |  |  |  |

|------------------|------------|----------------------------------------|--|--|--|--|

| 0000 000         | 0          | General Call Address <sup>(2)</sup>    |  |  |  |  |

| 0000 000         | 1          | Start Byte                             |  |  |  |  |

| 0000 001         | x          | Cbus Address                           |  |  |  |  |

| 0000 010         | x          | Reserved                               |  |  |  |  |

| 0000 011         | x          | Reserved                               |  |  |  |  |

| 0000 1xx         | x          | HS Mode Master Code                    |  |  |  |  |

| 1111 1xx         | x          | Reserved                               |  |  |  |  |

| 1111 0xx         | x          | 10-Bit Slave Upper Byte <sup>(3)</sup> |  |  |  |  |

Note 1: The address bits listed here will never cause an address match, independent of the address mask settings.

- 2: The address will be Acknowledged only if GCEN = 1.

- 3: A match on this address can only occur on the upper byte in 10-Bit Addressing mode.

#### 19.2.5 RTCVAL REGISTER MAPPINGS

### REGISTER 19-4: YEAR: YEAR VALUE REGISTER<sup>(1)</sup>

| U-0          | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |  |  |

|--------------|-----|-----|-----|-----|-----|-----|-----|--|--|

| —            | —   | —   | —   | —   | —   | —   | —   |  |  |

| bit 15 bit 8 |     |     |     |     |     |     |     |  |  |

| R/W-x  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| YRTEN3 | YRTEN2 | YRTEN2 | YRTEN1 | YRONE3 | YRONE2 | YRONE1 | YRONE0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

### Legend:

| Ecgenia.          |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-8 Unimplemented: Read as '0'

- bit 7-4 **YRTEN<3:0>:** Binary Coded Decimal Value of Year's Tens Digit bits Contains a value from 0 to 9.

- bit 3-0 **YRONE<3:0>:** Binary Coded Decimal Value of Year's Ones Digit bits Contains a value from 0 to 9.

**Note 1:** A write to the YEAR register is only allowed when RTCWREN = 1.

### **REGISTER 19-5: MTHDY: MONTH AND DAY VALUE REGISTER<sup>(1)</sup>**

| U-0    | U-0 | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|--------|-----|-----|---------|---------|---------|---------|---------|

| _      | —   | —   | MTHTEN0 | MTHONE3 | MTHONE2 | MTHONE1 | MTHONE0 |

| bit 15 |     |     |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | —   | DAYTEN1 | DAYTEN0 | DAYONE3 | DAYONE2 | DAYONE1 | DAYONE0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                    |

|-----------|---------------------------------------------------------------|

| bit 12    | MTHTEN0: Binary Coded Decimal Value of Month's Tens Digit bit |

|           | Contains a value of '0' or '1'.                               |

| bit 11-8  | MTHONE<3:0>: Binary Coded Decimal Value of Month's Ones Digit |

bit 11-8 MTHONE<3:0>: Binary Coded Decimal Value of Month's Ones Digit bits Contains a value from 0 to 9.

bit 7-6 Unimplemented: Read as '0'

- bit 5-4 **DAYTEN<1:0>:** Binary Coded Decimal Value of Day's Tens Digit bits Contains a value from 0 to 3.

- bit 3-0 DAYONE<3:0>: Binary Coded Decimal Value of Day's Ones Digit bits Contains a value from 0 to 9.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

| REGISTER     | 26-5: FWDT                                                           | T: WATCHDO       | OG TIMER CO    | ONFIGURATI        | ON REGISTE       | ER              |        |  |  |  |

|--------------|----------------------------------------------------------------------|------------------|----------------|-------------------|------------------|-----------------|--------|--|--|--|

| R/P-1        | R/P-1                                                                | U-0              | R/P-1          | R/P-1             | R/P-1            | R/P-1           | R/P-1  |  |  |  |

| FWDTEN       | WINDIS                                                               | —                | FWPSA          | WDTPS3            | WDTPS2           | WDTPS1          | WDTPS0 |  |  |  |

| bit 7        |                                                                      |                  |                |                   |                  |                 | bit    |  |  |  |

| Legend:      |                                                                      |                  |                |                   |                  |                 |        |  |  |  |

| R = Readab   | ole bit                                                              | P = Program      | mable bit      | U = Unimplen      | nented bit, read | d as '0'        |        |  |  |  |

| -n = Value a | at POR                                                               | '1' = Bit is set |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown   |  |  |  |

| bit 7        | FWDTEN: Wat                                                          | chdog Timer E    | Enable bit     |                   |                  |                 |        |  |  |  |

|              | 1 = WDT is ena<br>0 = WDT is dis                                     | abled            |                | e SWDTEN bit)     | )                |                 |        |  |  |  |

| bit 6        | WINDIS: Winde                                                        | owed Watchdo     | og Timer Disab | le bit            |                  |                 |        |  |  |  |

|              | 1 = Standard W<br>0 = Windowed                                       |                  |                | /DT disabled      |                  |                 |        |  |  |  |

| bit 5        | Unimplemented: Read as '0'                                           |                  |                |                   |                  |                 |        |  |  |  |

| bit 4        | FWPSA: WDT Prescaler bit                                             |                  |                |                   |                  |                 |        |  |  |  |

|              | 1 = WDT prescaler ratio of 1:128<br>0 = WDT prescaler ratio of 1:32  |                  |                |                   |                  |                 |        |  |  |  |

| bit 3-0      | WDTPS<3:0>: Watchdog Timer Postscale Select bits                     |                  |                |                   |                  |                 |        |  |  |  |

|              | 1111 = 1:32,76<br>1110 = 1:16,38<br>1101 = 1:8,192<br>1100 = 1:4,096 | 34<br>2<br>3     |                |                   |                  |                 |        |  |  |  |

|              | 1011 = 1:2,048<br>1010 = 1:1,024<br>1001 = 1:512<br>1000 = 1:256     |                  |                |                   |                  |                 |        |  |  |  |

|              | 0111 = 1:128<br>0110 = 1:64<br>0101 = 1:32                           |                  |                |                   |                  |                 |        |  |  |  |

|              | 0100 = 1:16<br>0011 = 1:8<br>0010 = 1:4<br>0001 = 1:2                |                  |                |                   |                  |                 |        |  |  |  |

|              | 0000 = 1:1                                                           |                  |                |                   |                  |                 |        |  |  |  |

|              |                                                                      |                  |                |                   |                  |                 |        |  |  |  |

## REGISTER 26-5: FWDT: WATCHDOG TIMER CONFIGURATION REGISTER

| Assembly<br>Mnemonic |         | Assembly Syntax | Description                                 | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|---------|-----------------|---------------------------------------------|---------------|----------------|--------------------------|

| BTSS                 | BTSS    | f,#bit4         | Bit Test f, Skip if Set                     | 1             | 1<br>(2 or 3)  | None                     |

|                      | BTSS    | Ws,#bit4        | Bit Test Ws, Skip if Set                    | 1             | 1<br>(2 or 3)  | None                     |

| BTST                 | BTST    | f,#bit4         | Bit Test f                                  | 1             | 1              | Z                        |

|                      | BTST.C  | Ws,#bit4        | Bit Test Ws to C                            | 1             | 1              | С                        |

|                      | BTST.Z  | Ws,#bit4        | Bit Test Ws to Z                            | 1             | 1              | Z                        |

|                      | BTST.C  | Ws,Wb           | Bit Test Ws <wb> to C</wb>                  | 1             | 1              | С                        |

|                      | BTST.Z  | Ws,Wb           | Bit Test Ws <wb> to Z</wb>                  | 1             | 1              | Z                        |

| BTSTS                | BTSTS   | f,#bit4         | Bit Test then Set f                         | 1             | 1              | Z                        |

|                      | BTSTS.C | Ws,#bit4        | Bit Test Ws to C, then Set                  | 1             | 1              | С                        |

|                      | BTSTS.Z | Ws,#bit4        | Bit Test Ws to Z, then Set                  | 1             | 1              | Z                        |

| CALL                 | CALL    | lit23           | Call Subroutine                             | 2             | 2              | None                     |

|                      | CALL    | Wn              | Call Indirect Subroutine                    | 1             | 2              | None                     |

| CLR                  | CLR     | f               | f = 0x0000                                  | 1             | 1              | None                     |

|                      | CLR     | WREG            | WREG = 0x0000                               | 1             | 1              | None                     |

|                      | CLR     | Ws              | Ws = 0x0000                                 | 1             | 1              | None                     |

| CLRWDT               | CLRWDT  |                 | Clear Watchdog Timer                        | 1             | 1              | WDTO, Sleep              |

| COM                  | СОМ     | f               | $f = \overline{f}$                          | 1             | 1              | N, Z                     |

|                      | СОМ     | f,WREG          | WREG = $\overline{f}$                       | 1             | 1              | N, Z                     |

|                      | СОМ     | Ws,Wd           | $Wd = \overline{Ws}$                        | 1             | 1              | N, Z                     |

| CP                   | CP      | f               | Compare f with WREG                         | 1             | 1              | C, DC, N, OV, Z          |

| 01                   | CP      | Wb,#lit5        | Compare Wb with lit5                        | 1             | 1              | C, DC, N, OV, Z          |

|                      | CP      | Wb,Ws           | Compare Wb with Ws (Wb – Ws)                | 1             | 1              | C, DC, N, OV, Z          |

| CP0                  | CP0     | f               | Compare f with 0x0000                       | 1             | 1              | C, DC, N, OV, Z          |

| Cro                  | CPO     | Ws              | Compare Ws with 0x0000                      | 1             | 1              | C, DC, N, OV, Z          |

| CPB                  | CPB     | f               | Compare f with WREG, with Borrow            | 1             | 1              | C, DC, N, OV, Z          |

| 012                  | CPB     | Wb,#lit5        | Compare Wb with lit5, with Borrow           | 1             | 1              | C, DC, N, OV, Z          |

|                      | CPB     | Wb,Ws           | Compare Wb with Ws, with Borrow             | 1             | 1              | C, DC, N, OV, Z          |

|                      | 012     |                 | $(Wb - Ws - \overline{C})$                  |               |                |                          |

| CPSEQ                | CPSEQ   | Wb,Wn           | Compare Wb with Wn, Skip if =               | 1             | 1<br>(2 or 3)  | None                     |

| CPSGT                | CPSGT   | Wb,Wn           | Compare Wb with Wn, Skip if >               | 1             | 1<br>(2 or 3)  | None                     |

| CPSLT                | CPSLT   | Wb,Wn           | Compare Wb with Wn, Skip if <               | 1             | 1<br>(2 or 3)  | None                     |

| CPSNE                | CPSNE   | Wb,Wn           | Compare Wb with Wn, Skip if $\neq$          | 1             | 1<br>(2 or 3)  | None                     |

| DAW                  | DAW     | Wn              | Wn = Decimal Adjust Wn                      | 1             | 1              | С                        |

| DEC                  | DEC     | f               | f = f -1                                    | 1             | 1              | C, DC, N, OV, Z          |

|                      | DEC     | f,WREG          | WREG = f –1                                 | 1             | 1              | C, DC, N, OV, Z          |

|                      | DEC     | Ws,Wd           | Wd = Ws - 1                                 | 1             | 1              | C, DC, N, OV, Z          |

| DEC2                 | DEC2    | f               | f = f - 2                                   | 1             | 1              | C, DC, N, OV, Z          |

|                      | DEC2    | f,WREG          | WREG = f – 2                                | 1             | 1              | C, DC, N, OV, Z          |

|                      | DEC2    | Ws,Wd           | Wd = Ws - 2                                 | 1             | 1              | C, DC, N, OV, Z          |

| DISI                 | DISI    | #lit14          | Disable Interrupts for k Instruction Cycles | 1             | 1              | None                     |

| DIV                  | DIV.SW  | Wm,Wn           | Signed 16/16-bit Integer Divide             | 1             | 18             | N, Z, C, OV              |

|                      | DIV.SD  | Wm,Wn           | Signed 32/16-bit Integer Divide             | 1             | 18             | N, Z, C, OV              |

|                      | DIV.UW  | Wm,Wn           | Unsigned 16/16-bit Integer Divide           | 1             | 18             | N, Z, C, OV              |

|                      | DIV.UD  | Wm,Wn           | Unsigned 32/16-bit Integer Divide           | 1             | 18             | N, Z, C, OV              |

| EXCH                 | EXCH    | Wns,Wnd         | Swap Wns with Wnd                           | 1             | 1              | None                     |

| FF1L                 | FF1L    | Ws,Wnd          | Find First One from Left (MSb) Side         | 1             | 1              | С                        |

| FF1R                 | FF1R    | Ws,Wnd          | Find First One from Right (LSb) Side        | 1             | 1              | С                        |

### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Assembly<br>Mnemonic | Assembly Syntax |              | Description                             | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|-----------------|--------------|-----------------------------------------|---------------|----------------|--------------------------|

| PWRSAV               | PWRSAV          | #lit1        | Go into Sleep or Idle mode              | 1             | 1              | WDTO, Sleep              |

| RCALL                | RCALL           | Expr         | Relative Call                           | 1             | 2              | None                     |

|                      | RCALL           | Wn           | Computed Call                           | 1             | 2              | None                     |

| REPEAT               | REPEAT          | #lit14       | Repeat Next Instruction lit14 + 1 times | 1             | 1              | None                     |

|                      | REPEAT          | Wn           | Repeat Next Instruction (Wn) + 1 times  | 1             | 1              | None                     |

| RESET                | RESET           |              | Software Device Reset                   | 1             | 1              | None                     |

| RETFIE               | RETFIE          |              | Return from Interrupt                   | 1             | 3 (2)          | None                     |

| RETLW                | RETLW           | #lit10,Wn    | Return with Literal in Wn               | 1             | 3 (2)          | None                     |

| RETURN               | RETURN          |              | Return from Subroutine                  | 1             | 3 (2)          | None                     |

| RLC                  | RLC             | f            | f = Rotate Left through Carry f         | 1             | 1              | C, N, Z                  |

|                      | RLC             | f,WREG       | WREG = Rotate Left through Carry f      | 1             | 1              | C, N, Z                  |

|                      | RLC             | Ws,Wd        | Wd = Rotate Left through Carry Ws       | 1             | 1              | C, N, Z                  |

| RLNC                 | RLNC            | f            | f = Rotate Left (No Carry) f            | 1             | 1              | N, Z                     |

|                      | RLNC            | f,WREG       | WREG = Rotate Left (No Carry) f         | 1             | 1              | N, Z                     |

|                      | RLNC            | Ws,Wd        | Wd = Rotate Left (No Carry) Ws          | 1             | 1              | N, Z                     |

| RRC                  | RRC             | f            | f = Rotate Right through Carry f        | 1             | 1              | C, N, Z                  |

|                      | RRC             | f,WREG       | WREG = Rotate Right through Carry f     | 1             | 1              | C, N, Z                  |

|                      | RRC             | Ws,Wd        | Wd = Rotate Right through Carry Ws      | 1             | 1              | C, N, Z                  |

| RRNC                 | RRNC            | f            | f = Rotate Right (No Carry) f           | 1             | 1              | N, Z                     |

|                      | RRNC            | f,WREG       | WREG = Rotate Right (No Carry) f        | 1             | 1              | N, Z                     |

|                      | RRNC            | Ws,Wd        | Wd = Rotate Right (No Carry) Ws         | 1             | 1              | N, Z                     |

| SE                   | SE              | Ws,Wnd       | Wnd = Sign-Extended Ws                  | 1             | 1              | C, N, Z                  |

| SETM                 | SETM            | f            | f = FFFFh                               | 1             | 1              | None                     |

|                      | SETM            | WREG         | WREG = FFFFh                            | 1             | 1              | None                     |

|                      | SETM            | Ws           | Ws = FFFFh                              | 1             | 1              | None                     |

| SL                   | SL              | f            | f = Left Shift f                        | 1             | 1              | C, N, OV, Z              |

|                      | SL              | f,WREG       | WREG = Left Shift f                     | 1             | 1              | C, N, OV, Z              |

|                      | SL              | Ws,Wd        | Wd = Left Shift Ws                      | 1             | 1              | C, N, OV, Z              |

|                      | SL              | Wb,Wns,Wnd   | Wnd = Left Shift Wb by Wns              | 1             | 1              | N, Z                     |

|                      | SL              | Wb,#lit5,Wnd | Wnd = Left Shift Wb by lit5             | 1             | 1              | N, Z                     |

| SUB                  | SUB             | f            | f = f – WREG                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUB             | f,WREG       | WREG = f – WREG                         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUB             | #lit10,Wn    | Wn = Wn - lit10                         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUB             | Wb,Ws,Wd     | Wd = Wb – Ws                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUB             | Wb,#lit5,Wd  | Wd = Wb - lit5                          | 1             | 1              | C, DC, N, OV, Z          |

| SUBB                 | SUBB            | f            | $f = f - WREG - (\overline{C})$         | 1             | 1              | C, DC, N, OV, Z          |

| JUDD                 |                 | f,WREG       | $WREG = f - WREG - (\overline{C})$      | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBB            |              |                                         |               |                |                          |

|                      | SUBB            | #lit10,Wn    | $Wn = Wn - lit10 - (\overline{C})$      | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBB            | Wb,Ws,Wd     | $Wd = Wb - Ws - (\overline{C})$         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBB            | Wb,#lit5,Wd  | Wd = Wb - lit5 - (C)                    | 1             | 1              | C, DC, N, OV, Z          |

| SUBR                 | SUBR            | f            | f = WREG – f                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBR            | f,WREG       | WREG = WREG – f                         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBR            | Wb,Ws,Wd     | Wd = Ws – Wb                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBR            | Wb,#lit5,Wd  | Wd = lit5 – Wb                          | 1             | 1              | C, DC, N, OV, Z          |

| SUBBR                | SUBBR           | f            | $f = WREG - f - (\overline{C})$         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBBR           | f,WREG       | WREG = WREG – $f - (\overline{C})$      | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBBR           | Wb,Ws,Wd     | $Wd = Ws - Wb - (\overline{C})$         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBBR           | Wb,#lit5,Wd  | $Wd = lit5 - Wb - (\overline{C})$       | 1             | 1              | C, DC, N, OV, Z          |

| SWAP                 | SWAP.b          | Wn           | Wn = Nibble Swap Wn                     | 1             | 1              | None                     |

|                      | SWAP            | Wn           | Wn = Byte Swap Wn                       | 1             | 1              | None                     |

| TBLRDH               |                 |              | Read Prog<23:16> to Wd<7:0>             |               | 2              |                          |

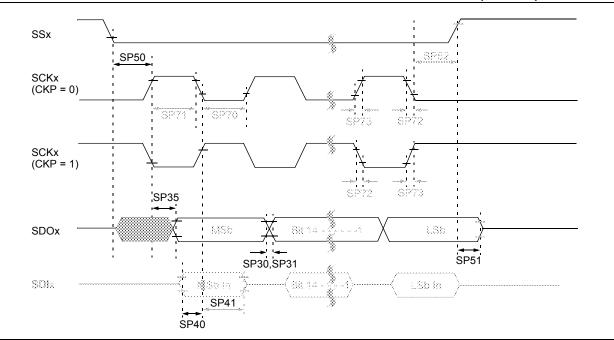

| AC CHARACTERISTICS |                   |                            |                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |       |                        |  |  |

|--------------------|-------------------|----------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------------------|--|--|

| Param<br>No.       | Symbol<br>TLO:SCL | Characteristic             |                           | Min <sup>(1)</sup>                                                                                                                                                                                                                                                                      | Max  | Units | Conditions             |  |  |