Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 18                                                                          |

| Program Memory Size        | 16KB (5.5K x 24)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 512 x 8                                                                     |

| RAM Size                   | 1.5K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 9x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 20-PDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16ka101-i-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

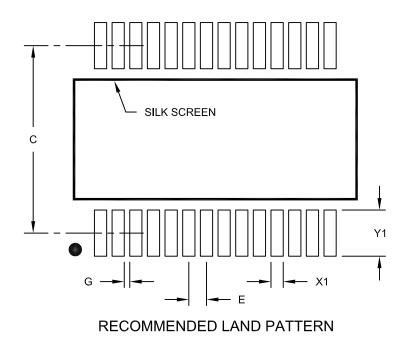

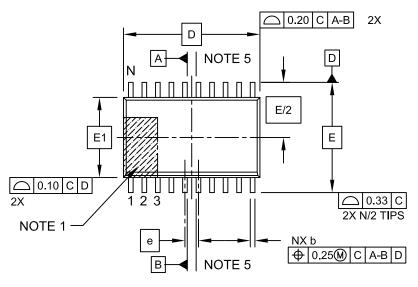

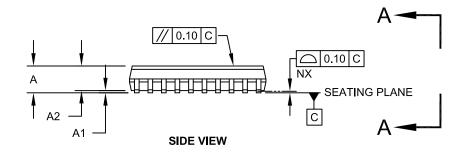

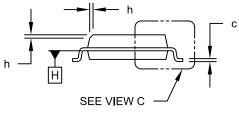

20-Pin PDIP/SSOP/SOIC/QFN 28-Pin SPDIP/SSOP/SOIC/QFN

| TABLE 1-1: DEVICE FEATURES FOR THE PIC24F16KA102 FAMILY                 |                                                                                                                                                     |                     |                           |               |  |  |  |  |

|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------|---------------|--|--|--|--|

| Features                                                                | PIC24F08KA101                                                                                                                                       | PIC24F16KA101       | PIC24F08KA102             | PIC24F16KA102 |  |  |  |  |

| Operating Frequency                                                     |                                                                                                                                                     | DC – 3              | 32 MHz                    |               |  |  |  |  |

| Program Memory (bytes)                                                  | 8K                                                                                                                                                  | 16K                 | 8K                        | 16K           |  |  |  |  |

| Program Memory (instructions)                                           | 2816                                                                                                                                                | 5632                | 2816                      | 5632          |  |  |  |  |

| Data Memory (bytes)                                                     |                                                                                                                                                     | 15                  | 36                        |               |  |  |  |  |

| Data EEPROM Memory (bytes)                                              |                                                                                                                                                     | 5                   | 12                        |               |  |  |  |  |

| Interrupt Sources (soft vectors/NMI traps)                              |                                                                                                                                                     | 30 (2               | 26/4)                     |               |  |  |  |  |

| I/O Ports                                                               | PORT/<br>PORTB<15:1                                                                                                                                 |                     | PORTA<7:0><br>PORTB<15:0> |               |  |  |  |  |

| Total I/O Pins                                                          | 1                                                                                                                                                   | 8                   | 2                         | 4             |  |  |  |  |

| Timers: Total Number (16-bit)<br>32-Bit (from paired 16-bit timers)     |                                                                                                                                                     |                     | 3<br>1                    |               |  |  |  |  |

| Input Capture Channels                                                  |                                                                                                                                                     |                     | 1                         |               |  |  |  |  |

| Output Compare/PWM Channels                                             |                                                                                                                                                     |                     | 1                         |               |  |  |  |  |

| Input Change Notification Interrupt                                     | 1                                                                                                                                                   | 7                   | 2                         | 3             |  |  |  |  |

| Serial Communications: UART<br>SPI (3-wire/4-wire)<br>I <sup>2</sup> C™ |                                                                                                                                                     |                     | 2<br>1<br>1               |               |  |  |  |  |

| 10-Bit Analog-to-Digital Module (input channels)                        |                                                                                                                                                     | (                   | 9                         |               |  |  |  |  |

| Analog Comparators                                                      |                                                                                                                                                     | 2                   | 2                         |               |  |  |  |  |

| Resets (and delays)                                                     | POR, BOR, RESET Instruction, MCLR, WDT, Illegal Opcode,<br>REPEAT Instruction, Hardware Traps, Configuration Word<br>Mismatch (PWRT, OST, PLL Lock) |                     |                           |               |  |  |  |  |

| Instruction Set                                                         | 76 Base Ins                                                                                                                                         | tructions, Multiple | e Addressing Mod          | le Variations |  |  |  |  |

|                                                                         |                                                                                                                                                     |                     |                           |               |  |  |  |  |

Packages

#### EXAMPLE 5-3: LOADING THE WRITE BUFFERS – ASSEMBLY LANGUAGE CODE

| Cot up NTMOON for your more and an and    |                                         |

|-------------------------------------------|-----------------------------------------|

| ; Set up NVMCON for row programming opera |                                         |

| MOV #0x4004, W0                           |                                         |

| MOV W0, NVMCON                            | ; Initialize NVMCON                     |

| ; Set up a pointer to the first program m | -                                       |

| ; program memory selected, and writes ena | bled                                    |

| MOV #0x0000, W0                           | i                                       |

| MOV W0, TBLPAG                            | ; Initialize PM Page Boundary SFR       |

| MOV #0x1500, W0                           | ; An example program memory address     |

| ; Perform the TBLWT instructions to write | the latches                             |

| ; 0th_program_word                        |                                         |

| MOV #LOW_WORD_0, W2                       | ;                                       |

| MOV #HIGH_BYTE_0, W3                      | ;                                       |

| TBLWTL W2, [W0]                           | ; Write PM low word into program latch  |

| TBLWTH W3, [W0++]                         | ; Write PM high byte into program latch |

| ; 1st_program_word                        |                                         |

| MOV #LOW_WORD_1, W2                       | ;                                       |

| MOV #HIGH_BYTE_1, W3                      | ;                                       |

| TBLWTL W2, [W0]                           | ; Write PM low word into program latch  |

| TBLWTH W3, [W0++]                         | ; Write PM high byte into program latch |

| ; 2nd_program_word                        |                                         |

| MOV #LOW_WORD_2, W2                       | ;                                       |

| MOV #HIGH_BYTE_2, W3                      | ;                                       |

| TBLWTL W2, [W0]                           | ; Write PM low word into program latch  |

| TBLWTH W3, [W0++]                         | ; Write PM high byte into program latch |

| •                                         |                                         |

| •                                         |                                         |

| •                                         |                                         |

| ; 32nd_program_word                       |                                         |

| MOV #LOW_WORD_31, W2                      | ;                                       |

| MOV #HIGH_BYTE_31, W3                     | ;                                       |

| TBLWTL W2, [W0]                           | ; Write PM low word into program latch  |

| TBLWTH W3, [W0]                           | ; Write PM high byte into program latch |

|                                           |                                         |

#### EXAMPLE 5-4: LOADING THE WRITE BUFFERS – 'C' LANGUAGE CODE

```

// C example using MPLAB C30

#define NUM_INSTRUCTION_PER_ROW 64

int __attribute__ ((space(auto_psv))) progAddr = 0x1234 // Variable located in Pgm Memory

unsigned int offset;

unsigned int i;

unsigned int progData[2*NUM_INSTRUCTION_PER_ROW];

// Buffer of data to write

//Set up NVMCON for row programming

NVMCON = 0 \times 4004;

// Initialize NVMCON

//Set up pointer to the first memory location to be written

TBLPAG = __builtin_tblpage(&progAddr);

// Initialize PM Page Boundary SFR

// Initialize lower word of address

offset = __builtin_tbloffset(&progAddr);

//Perform TBLWT instructions to write necessary number of latches

for(i=0; i < 2*NUM_INSTRUCTION_PER_ROW; i++)</pre>

{

__builtin_tblwtl(offset, progData[i++]);

// Write to address low word

__builtin_tblwth(offset, progData[i]);

// Write to upper byte

offset = offset + 2;

// Increment address

}

```

| R/W-0, HS       | R/W-0, HS                                                        | R/W-0                                                                 | U-0             | U-0              | R/C-0, HS         | R/W-0, HS         | R/W-0         |  |  |

|-----------------|------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------|------------------|-------------------|-------------------|---------------|--|--|

| TRAPR           | IOPUWR                                                           | SBOREN                                                                | _               | _                | DPSLP             | CM                | PMSLP         |  |  |

| bit 15          |                                                                  |                                                                       |                 |                  |                   | •                 | bit 8         |  |  |

|                 |                                                                  |                                                                       |                 |                  |                   |                   |               |  |  |

| R/W-0, HS       | R/W-0, HS                                                        | R/W-0, HS                                                             | R/W-0, HS       | R/W-0, HS        | R/W-0, HS         | R/W-1, HS         | R/W-1, HS     |  |  |

| EXTR            | SWR                                                              | SWDTEN <sup>(2)</sup>                                                 | WDTO            | SLEEP            | IDLE              | BOR               | POR           |  |  |

| bit 7           |                                                                  |                                                                       |                 |                  |                   |                   | bit 0         |  |  |

|                 |                                                                  |                                                                       |                 |                  |                   |                   |               |  |  |

| Legend:         |                                                                  | C = Clearable                                                         | bit             | HS = Hardwa      | are Settable bit  |                   |               |  |  |

| R = Readable    | Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                                       |                 |                  |                   |                   |               |  |  |

| -n = Value at F | POR                                                              | '1' = Bit is set                                                      |                 | '0' = Bit is cle | ared              | x = Bit is unkr   | Iown          |  |  |

|                 |                                                                  |                                                                       |                 |                  |                   |                   |               |  |  |

| bit 15          |                                                                  | Reset Flag bit                                                        |                 |                  |                   |                   |               |  |  |

|                 | •                                                                | onflict Reset ha<br>onflict Reset ha                                  |                 | d                |                   |                   |               |  |  |

| bit 14          | •                                                                | gal Opcode or                                                         |                 |                  | et Flag bit       |                   |               |  |  |

|                 |                                                                  |                                                                       |                 |                  | ode or uninitial  | ized W registe    | r used as an  |  |  |

|                 |                                                                  | Pointer caused                                                        |                 |                  |                   |                   |               |  |  |

|                 | -                                                                | l opcode or uni                                                       |                 |                  | ccurred           |                   |               |  |  |

| bit 13          |                                                                  | oftware Enable/                                                       |                 | Rbit             |                   |                   |               |  |  |

|                 |                                                                  | 1 = BOR is turned on in software<br>0 = BOR is turned off in software |                 |                  |                   |                   |               |  |  |

| bit 12-11       |                                                                  | ted: Read as '                                                        |                 |                  |                   |                   |               |  |  |

| bit 10          | -                                                                | p Sleep Mode F                                                        |                 |                  |                   |                   |               |  |  |

|                 | -                                                                | ep has occurre                                                        | -               |                  |                   |                   |               |  |  |

|                 | 0 = Deep Sle                                                     | ep has not occ                                                        | urred           |                  |                   |                   |               |  |  |

| bit 9           | -                                                                | ation Word Mis                                                        |                 | -                |                   |                   |               |  |  |

|                 | •                                                                | uration Word Mi                                                       |                 |                  |                   |                   |               |  |  |

| bit 8           | •                                                                | uration Word Mi<br>gram Memory F                                      |                 |                  |                   |                   |               |  |  |

| DILO            |                                                                  | memory bias v                                                         |                 |                  | ing Sleep         |                   |               |  |  |

|                 | •                                                                | memory bias v                                                         | •               | •                | •                 |                   |               |  |  |

| bit 7           |                                                                  | nal Reset (MCL                                                        |                 |                  |                   |                   |               |  |  |

|                 |                                                                  | Clear (pin) Res                                                       |                 |                  |                   |                   |               |  |  |

|                 |                                                                  | Clear (pin) Res                                                       |                 |                  |                   |                   |               |  |  |

| bit 6           |                                                                  | ire Reset (Instru<br>instruction has                                  |                 |                  |                   |                   |               |  |  |

|                 |                                                                  | instruction has                                                       |                 | -                |                   |                   |               |  |  |

| bit 5           |                                                                  | oftware Enable/                                                       |                 |                  |                   |                   |               |  |  |

|                 | 1 = WDT is e                                                     |                                                                       |                 |                  |                   |                   |               |  |  |

|                 | 0 = WDT is di                                                    | isabled                                                               |                 |                  |                   |                   |               |  |  |

| bit 4           |                                                                  | hdog Timer Tin                                                        | -               |                  |                   |                   |               |  |  |

|                 |                                                                  | e-out has occur<br>e-out has not o                                    |                 |                  |                   |                   |               |  |  |

| Note 1: All     |                                                                  |                                                                       |                 | d in software. S | Setting one of th | ese bits in softv | vare does not |  |  |

|                 | ise a device Re                                                  |                                                                       |                 |                  |                   |                   |               |  |  |

|                 | ne FWDTEN Co<br>/DTEN bit settir                                 | -                                                                     | is '1' (unprogr | ammed), the V    | VDT is always e   | nabled, regard    | less of the   |  |  |

### REGISTER 7-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

SWDTEN bit setting.

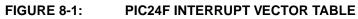

|                                   | Deast game instruction               |          |                                                        |

|-----------------------------------|--------------------------------------|----------|--------------------------------------------------------|

|                                   | Reset – GOTO Instruction             | 000000h  |                                                        |

|                                   | Reset – GOTO Address                 | 000002h  |                                                        |

|                                   | Reserved                             | 000004h  |                                                        |

|                                   | Oscillator Fail Trap Vector          |          |                                                        |

|                                   | Address Error Trap Vector            |          |                                                        |

|                                   | Stack Error Trap Vector              |          |                                                        |

|                                   | Math Error Trap Vector               |          |                                                        |

|                                   | Reserved                             |          |                                                        |

|                                   | Reserved                             |          |                                                        |

|                                   | Reserved                             |          |                                                        |

|                                   | Interrupt Vector 0                   | 000014h  |                                                        |

|                                   | Interrupt Vector 1                   |          |                                                        |

|                                   | —                                    |          |                                                        |

|                                   | —                                    |          |                                                        |

|                                   |                                      |          |                                                        |

| ~                                 | Interrupt Vector 52                  | 00007Ch  | Interrupt Vector Table (IVT) <sup>(1)</sup>            |

| Duit                              | Interrupt Vector 53                  | 00007Eh  |                                                        |

| , Lic                             | Interrupt Vector 54                  | 000080h  |                                                        |

| er                                | —                                    |          |                                                        |

| Drde                              |                                      |          |                                                        |

| 0                                 | —                                    |          |                                                        |

| nra                               | Interrupt Vector 116                 | 0000FCh  |                                                        |

| lati                              | Interrupt Vector 117                 | 0000FEh  |                                                        |

| Decreasing Natural Order Priority | Reserved                             | 000100h  |                                                        |

| sin                               | Reserved                             | 000102h  |                                                        |

| ea                                | Reserved                             |          |                                                        |

| ecr                               | Oscillator Fail Trap Vector          |          |                                                        |

| Ω                                 | Address Error Trap Vector            |          |                                                        |

|                                   | Stack Error Trap Vector              |          |                                                        |

|                                   | Math Error Trap Vector               |          |                                                        |

|                                   | Reserved                             |          |                                                        |

|                                   | Reserved                             |          |                                                        |

|                                   | Reserved                             |          |                                                        |

|                                   | Interrupt Vector 0                   | 000114h  |                                                        |

|                                   | Interrupt Vector 1                   |          |                                                        |

|                                   | —                                    |          |                                                        |

|                                   |                                      |          | (4)                                                    |

|                                   |                                      |          | Alternate Interrupt Vector Table (AIVT) <sup>(1)</sup> |

|                                   | Interrupt Vector 52                  | 00017Ch  |                                                        |

|                                   | Interrupt Vector 53                  | 00017Eh  |                                                        |

|                                   | Interrupt Vector 54                  | 000180h  |                                                        |

|                                   |                                      |          |                                                        |

|                                   |                                      |          |                                                        |

|                                   |                                      | 4 -      | L                                                      |

| Ļ                                 | Interrupt Vector 116                 | -        |                                                        |

| Y                                 | Interrupt Vector 117                 | 0001FEh  |                                                        |

|                                   | Start of Code                        | 000200h  |                                                        |

| Note 1: Se                        | e Table 8-2 for the interrupt vector | or list. |                                                        |

#### 8.3 Interrupt Control and Status Registers

The PIC24F16KA102 family of devices implements a total of 22 registers for the interrupt controller:

- INTCON1

- INTCON2

- IFS0, IFS1, IFS3 and IFS4

- · IEC0, IEC1, IEC3 and IEC4

- IPC0 through IPC5, IPC7 and IPC15 through IPC19

- INTTREG

Global interrupt control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit, as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the AIV table.

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals, or external signal, and is cleared via software.

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

The IPCx registers are used to set the interrupt priority level for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels. The INTTREG register contains the associated interrupt vector number and the new CPU interrupt priority level, which are latched into the Vector Number (VECNUM<6:0>) and the Interrupt Level (ILR<3:0>) bit fields in the INTTREG register. The new interrupt priority level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence listed in Table 8-2. For example, the INT0 (External Interrupt 0) is depicted as having a vector number and a natural order priority of 0. Thus, the INT0IF status bit is found in IFS0<0>, the INT0IE enable bit in IEC0<0> and the INT0IP<2:0> priority bits in the first position of IPC0 (IPC0<2:0>).

Although they are not specifically part of the interrupt control hardware, two of the CPU control registers contain bits that control interrupt functionality. The ALU STATUS register (SR) contains the IPL<2:0> bits (SR<7:5>). These indicate the current CPU interrupt priority level. The user may change the current CPU priority level by writing to the IPL bits.

The CORCON register contains the IPL3 bit, which together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that the trap events cannot be masked by the user's software.

All interrupt registers are described in Register 8-1 through Register 8-21, in the following sections.

| R/W-0         | U-0                                                                                                | R/W-0                                       | R/W-0            | R/W-0             | R/W-0           | R/W-0           | R/W-0         |  |  |

|---------------|----------------------------------------------------------------------------------------------------|---------------------------------------------|------------------|-------------------|-----------------|-----------------|---------------|--|--|

| NVMIE         | 0-0                                                                                                | AD1IE                                       | U1TXIE           | U1RXIE            | SPI1IE          | SPF1IE          | T3IE          |  |  |

| bit 15        |                                                                                                    | ADTIL                                       | UTTAL            | UIIXIL            | SITTL           | SITTL           | bit           |  |  |

|               |                                                                                                    |                                             |                  |                   |                 |                 | bit           |  |  |

| R/W-0         | U-0                                                                                                | U-0                                         | U-0              | R/W-0             | R/W-0           | R/W-0           | R/W-0         |  |  |

| T2IE          | —                                                                                                  | —                                           | _                | T1IE              | OC1IE           | IC1IE           | <b>INTOIE</b> |  |  |

| bit 7         |                                                                                                    |                                             |                  |                   |                 |                 | bit           |  |  |

| Legend:       |                                                                                                    |                                             |                  |                   |                 |                 |               |  |  |

| R = Readabl   | e bit                                                                                              | W = Writable                                | bit              | U = Unimplem      | ented bit, read | d as '0'        |               |  |  |

| -n = Value at | POR                                                                                                | '1' = Bit is set                            |                  | '0' = Bit is clea | ared            | x = Bit is unkn | own           |  |  |

| bit 15        |                                                                                                    | Interrupt Enab                              | le hit           |                   |                 |                 |               |  |  |

|               |                                                                                                    | request is enab                             |                  |                   |                 |                 |               |  |  |

|               |                                                                                                    | equest is not e                             |                  |                   |                 |                 |               |  |  |

| bit 14        | Unimplemen                                                                                         | ted: Read as '                              | )'               |                   |                 |                 |               |  |  |

| bit 13        | AD1IE: A/D C                                                                                       | Conversion Con                              | nplete Interrupt | Enable bit        |                 |                 |               |  |  |

|               |                                                                                                    | equest is enab<br>equest is not e           |                  |                   |                 |                 |               |  |  |

| bit 12        | -                                                                                                  | RT1 Transmitter                             |                  | ole bit           |                 |                 |               |  |  |

|               | 1 = Interrupt request is enabled                                                                   |                                             |                  |                   |                 |                 |               |  |  |

|               | 0 = Interrupt request is not enabled                                                               |                                             |                  |                   |                 |                 |               |  |  |

| bit 11        |                                                                                                    | U1RXIE: UART1 Receiver Interrupt Enable bit |                  |                   |                 |                 |               |  |  |

|               | <ul> <li>1 = Interrupt request is enabled</li> <li>0 = Interrupt request is not enabled</li> </ul> |                                             |                  |                   |                 |                 |               |  |  |

|               | -                                                                                                  | -                                           |                  |                   |                 |                 |               |  |  |

| bit 10        |                                                                                                    | Transfer Comp                               | •                | -nable bit        |                 |                 |               |  |  |

|               |                                                                                                    | equest is enab<br>equest is not e           |                  |                   |                 |                 |               |  |  |

| bit 9         | -                                                                                                  | Fault Interrupt                             |                  |                   |                 |                 |               |  |  |

|               |                                                                                                    | equest is enab                              |                  |                   |                 |                 |               |  |  |

|               |                                                                                                    | equest is not e                             |                  |                   |                 |                 |               |  |  |

| bit 8         | T3IE: Timer3                                                                                       | Interrupt Enabl                             | e bit            |                   |                 |                 |               |  |  |

|               |                                                                                                    | equest is enab                              |                  |                   |                 |                 |               |  |  |

|               |                                                                                                    | equest is not e                             |                  |                   |                 |                 |               |  |  |

| bit 7         |                                                                                                    | Interrupt Enabl                             |                  |                   |                 |                 |               |  |  |

|               |                                                                                                    | equest is enab<br>equest not is e           |                  |                   |                 |                 |               |  |  |

| bit 6-4       | Unimplemen                                                                                         | ted: Read as '                              | )'               |                   |                 |                 |               |  |  |

| bit 3         | T1IE: Timer1                                                                                       | Interrupt Enabl                             | e bit            |                   |                 |                 |               |  |  |

|               |                                                                                                    | equest is enab<br>equest is not e           |                  |                   |                 |                 |               |  |  |

| bit 2         |                                                                                                    | ut Compare Ch                               |                  | pt Enable bit     |                 |                 |               |  |  |

|               | •                                                                                                  | equest is enab                              |                  | •                 |                 |                 |               |  |  |

|               |                                                                                                    | equest is not e                             |                  |                   |                 |                 |               |  |  |

| bit 1         | IC1IE: Input C                                                                                     | Capture Channe                              | el 1 Interrupt E | nable bit         |                 |                 |               |  |  |

|               |                                                                                                    | equest is enab<br>equest is not e           |                  |                   |                 |                 |               |  |  |

| bit 0         | •                                                                                                  | nal Interrupt 0                             |                  |                   |                 |                 |               |  |  |

|               |                                                                                                    | equest is enab                              |                  |                   |                 |                 |               |  |  |

|               | ±                                                                                                  | oquoot io onuo                              | ica              |                   |                 |                 |               |  |  |

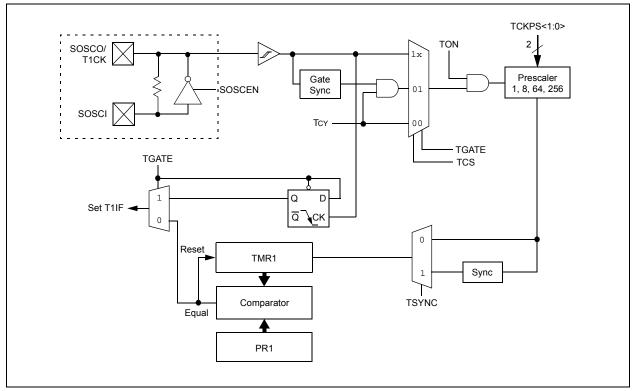

### 12.0 TIMER1

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Timers, refer to the "PIC24F Family Reference Manual", Section 14. "Timers" (DS39704).

The Timer1 module is a 16-bit timer which can serve as the time counter for the Real-Time Clock (RTC), or operate as a free-running, interval timer/counter. Timer1 can operate in three modes:

- 16-Bit Timer

- 16-Bit Synchronous Counter

- 16-Bit Asynchronous Counter

Timer1 also supports these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation During CPU Idle and Sleep modes

- Interrupt on 16-Bit Period Register Match or Falling Edge of External Gate Signal

Figure 12-1 presents a block diagram of the 16-bit Timer1 module.

To configure Timer1 for operation:

- 1. Set the TON bit (= 1).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Set or clear the TSYNC bit to configure synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the interrupt enable bit, T1IE. Use the priority bits, T1IP<2:0>, to set the interrupt priority.

### FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

#### REGISTER 16-1: SPI1STAT: SPI1 STATUS AND CONTROL REGISTER (CONTINUED)

bit 1 SPITBF: SPI1 Transmit Buffer Full Status bit 1 = Transmit has not yet started, SPI1TXB is full 0 = Transmit has started, SPI1TXB is empty In Standard Buffer mode: Automatically set in hardware when the CPU writes to the SPITBF location, loading SPITBF. Automatically cleared in hardware when the SPI1 module transfers data from SPI1TXB to SPIRBF. In Enhanced Buffer mode: Automatically set in hardware when CPU writes to the SPI1BUF location, loading the last available buffer location. Automatically cleared in hardware when a buffer location is available for a CPU write. bit 0 SPIRBF: SPI1 Receive Buffer Full Status bit 1 = Receive is complete; SPI1RXB is full 0 = Receive is not complete; SPI1RXB is empty In Standard Buffer mode: Automatically set in hardware when SPI1 transfers data from SPIRBF to SPIRBF. Automatically cleared in hardware when the core reads the SPI1BUF location, reading SPIRBF. In Enhanced Buffer mode: Automatically set in hardware when SPI1 transfers data from SPI1SR to buffer, filling the last unread buffer location. Automatically cleared in hardware when a buffer location is available for a transfer from SPI1SR.

#### REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

| R/W-0    | R/W-0  | R/W-0    | U-0 | R/W-0, HC | R/W-0 | R-0, HSC | R-1, HSC |

|----------|--------|----------|-----|-----------|-------|----------|----------|

| UTXISEL1 | UTXINV | UTXISEL0 | —   | UTXBRK    | UTXEN | UTXBF    | TRMT     |

| bit 15   |        |          |     |           |       |          | bit 8    |

| R/W-0    | R/W-0    | R/W-0 | R-1, HSC | R-0, HSC | R-0, HSC | R/C-0, HS | R-0, HSC |

|----------|----------|-------|----------|----------|----------|-----------|----------|

| URXISEL1 | URXISEL0 | ADDEN | RIDLE    | PERR     | FERR     | OERR      | URXDA    |

| bit 7    |          |       |          |          |          |           | bit 0    |

| Legend:           | HC = Hardware Clearable bit |                             |                    |  |  |

|-------------------|-----------------------------|-----------------------------|--------------------|--|--|

| C = Clearable bit | HS = Hardware Settable bit  | HSC = Hardware Settable/C   | Clearable bit      |  |  |

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read | d as '0'           |  |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared        | x = Bit is unknown |  |  |

bit 15,13 UTXISEL<1:0>: Transmission Interrupt Mode Selection bits

- 11 = Reserved; do not use

- 10 = Interrupt when a character is transferred to the Transmit Shift Register (TSR), and as a result, the transmit buffer becomes empty

- 01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all transmit operations are completed

- 00 = Interrupt when a character is transferred to the Transmit Shift Register (this implies there is at least one character open in the transmit buffer)

bit 14 UTXINV: IrDA<sup>®</sup> Encoder Transmit Polarity Inversion bit

|         | <b>UTAINV.</b> II DA Encoder Hanshit Folanty Inversion bit                                                                                                                                                                                                                                                                                                 |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <u>If IREN = 0:</u>                                                                                                                                                                                                                                                                                                                                        |

|         | 1 = UxTX Idle '0'                                                                                                                                                                                                                                                                                                                                          |

|         | 0 = UxTX Idle '1'                                                                                                                                                                                                                                                                                                                                          |

|         | If IREN = 1:                                                                                                                                                                                                                                                                                                                                               |

|         | 1 = UxTX Idle '1'                                                                                                                                                                                                                                                                                                                                          |

|         | 0 = UxTX Idle '0'                                                                                                                                                                                                                                                                                                                                          |

| bit 12  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                 |

| bit 11  | UTXBRK: Transmit Break bit                                                                                                                                                                                                                                                                                                                                 |

|         | 1 = Send Sync Break on next transmission – Start bit, followed by twelve '0' bits, followed by Stop bit;<br>cleared by hardware upon completion                                                                                                                                                                                                            |

|         | 0 = Sync Break transmission is disabled or completed                                                                                                                                                                                                                                                                                                       |

| bit 10  | UTXEN: Transmit Enable bit                                                                                                                                                                                                                                                                                                                                 |

|         | 1 = Transmit is enabled, UxTX pin is controlled by UARTx                                                                                                                                                                                                                                                                                                   |

|         | 0 = Transmit is disabled, any pending transmission is aborted and buffer is reset. UxTX pin is controlled<br>by the PORT register.                                                                                                                                                                                                                         |

| bit 9   | UTXBF: Transmit Buffer Full Status bit (read-only)                                                                                                                                                                                                                                                                                                         |

|         | 1 = Transmit buffer is full                                                                                                                                                                                                                                                                                                                                |

|         | 0 = Transmit buffer is not full, at least one more character can be written                                                                                                                                                                                                                                                                                |

| bit 8   | TRMT: Transmit Shift Register Empty bit (read-only)                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = Transmit Shift Register is empty and transmit buffer is empty (the last transmission has completed)</li> <li>0 = Transmit Shift Register is not empty, a transmission is in progress or queued</li> </ul>                                                                                                                                     |

| bit 7-6 | URXISEL<1:0>: Receive Interrupt Mode Selection bits                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>11 = Interrupt is set on RSR transfer, making the receive buffer full (i.e., has 4 data characters)</li> <li>10 = Interrupt is set on RSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)</li> <li>0x = Interrupt is set when any character is received and transferred from the RSR to the receive buffer;</li> </ul> |

|         | reachus huffer has ann ar mars sharestare                                                                                                                                                                                                                                                                                                                  |

#### 19.2.4 RTCC CONTROL REGISTERS

### REGISTER 19-1: RCFGCAL: RTCC CALIBRATION AND CONFIGURATION REGISTER<sup>(1)</sup>

| R/W-0                | U-0 | R/W-0   | R-0, HSC | R-0, HSC               | R/W-0 | R/W-0   | R/W-0   |

|----------------------|-----|---------|----------|------------------------|-------|---------|---------|

| RTCEN <sup>(2)</sup> | —   | RTCWREN | RTCSYNC  | HALFSEC <sup>(3)</sup> | RTCOE | RTCPTR1 | RTCPTR0 |

| bit 15               |     |         |          |                        |       |         | bit 8   |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| CAL7  | CAL6  | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           | HSC = Hardware Settable/Clearable bit |                            |                    |  |  |

|-------------------|---------------------------------------|----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, rea | d as '0'           |  |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared       | x = Bit is unknown |  |  |

| bit 15  | RTCEN: RTCC Enable bit <sup>(2)</sup><br>1 = RTCC module is enabled                                                                                                                                                                |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 0 = RTCC module is disabled                                                                                                                                                                                                        |

| bit 14  | Unimplemented: Read as '0'                                                                                                                                                                                                         |

| bit 13  | RTCWREN: RTCC Value Registers Write Enable bit                                                                                                                                                                                     |

|         | <ul> <li>1 = RTCVALH and RTCVALL registers can be written to by the user</li> <li>0 = RTCVALH and RTCVALL registers are locked out from being written to by the user</li> </ul>                                                    |

| bit 12  | RTCSYNC: RTCC Value Registers Read Synchronization bit                                                                                                                                                                             |

|         | 1 = RTCVALH, RTCVALL and ALCFGRPT registers can change while reading due to a rollover ripple, resulting in an invalid data read. If the register is read twice and results in the same data, the data can be assumed to be valid. |

|         | 0 = RTCVALH, RTCVALL or ALCFGRPT registers can be read without concern over a rollover ripple                                                                                                                                      |

| bit 11  | HALFSEC: Half Second Status bit <sup>(3)</sup>                                                                                                                                                                                     |

|         | <ul> <li>1 = Second half period of a second</li> <li>0 = First half period of a second</li> </ul>                                                                                                                                  |

| bit 10  | RTCOE: RTCC Output Enable bit                                                                                                                                                                                                      |

|         | <ul><li>1 = RTCC output is enabled</li><li>0 = RTCC output is disabled</li></ul>                                                                                                                                                   |

| bit 9-8 | RTCPTR<1:0>: RTCC Value Register Window Pointer bits                                                                                                                                                                               |

|         | Points to the corresponding RTCC Value registers when reading the RTCVALH and RTCVALL registers. The RTCPTR<1:0> value decrements on every read or write of RTCVALH until it reaches '00'.                                         |

|         | <u>RTCVAL&lt;15:8&gt;:</u><br>00 = MINUTES<br>01 = WEEKDAY<br>10 = MONTH                                                                                                                                                           |

|         | 11 = Reserved                                                                                                                                                                                                                      |

|         | <u>RTCVAL&lt;7:0&gt;:</u>                                                                                                                                                                                                          |

|         |                                                                                                                                                                                                                                    |

|         | 01 = HOURS<br>10 = DAY                                                                                                                                                                                                             |

|         | 11 = YEAR                                                                                                                                                                                                                          |

| Note 1: | The RCFGCAL register is only affected by a POR.                                                                                                                                                                                    |

- 2: A write to the RTCEN bit is only allowed when RTCWREN = 1.

- **3:** This bit is read-only; it is cleared to '0' on a write to the lower half of the MINSEC register.

### REGISTER 19-1: RCFGCAL: RTCC CALIBRATION AND CONFIGURATION REGISTER<sup>(1)</sup> (CONTINUED)

| bit 7-0 | CAL<7:0>: RTC Drift Calibration bits                                                                         |

|---------|--------------------------------------------------------------------------------------------------------------|

|         | 01111111 = Maximum positive adjustment; adds 508 RTC clock pulses every one minute                           |

|         |                                                                                                              |

|         | ·                                                                                                            |

|         | •                                                                                                            |

|         | 01111111 = Minimum positive adjustment; adds 4 RTC clock pulses every one minute<br>00000000 = No adjustment |

|         | 11111111 = Minimum negative adjustment; subtracts 4 RTC clock pulses every one minute                        |

|         | •                                                                                                            |

|         | •                                                                                                            |

|         | ·                                                                                                            |

|         | 10000000 = Maximum negative adjustment; subtracts 512 RTC clock pulses every one minute                      |

- **Note 1:** The RCFGCAL register is only affected by a POR.

- 2: A write to the RTCEN bit is only allowed when RTCWREN = 1.

- 3: This bit is read-only; it is cleared to '0' on a write to the lower half of the MINSEC register.

#### REGISTER 19-2: PADCFG1: PAD CONFIGURATION CONTROL REGISTER

| U-0                               | U-0 | U-0 | U-0                                | U-0     | U-0                      | U-0                      | U-0   |

|-----------------------------------|-----|-----|------------------------------------|---------|--------------------------|--------------------------|-------|

| —                                 | —   | —   | —                                  | —       | —                        | —                        | _     |

| bit 15                            |     |     |                                    |         |                          |                          | bit 8 |

|                                   |     |     |                                    |         |                          |                          |       |

| U-0                               | U-0 | U-0 | R/W-0                              | R/W-0   | R/W-0                    | R/W-0                    | U-0   |

|                                   | _   | _   | SMBUSDEL                           | OC1TRIS | RTSECSEL1 <sup>(1)</sup> | RTSECSEL0 <sup>(1)</sup> | _     |

| bit 7                             |     |     |                                    |         |                          |                          | bit 0 |

|                                   |     |     |                                    |         |                          |                          |       |

| Legend:                           |     |     |                                    |         |                          |                          |       |

| R = Readable bit W = Writable bit |     |     | U = Unimplemented bit, read as '0' |         |                          |                          |       |

| bit 15-5 | Unimplemented: Read as '0' |

|----------|----------------------------|

#### bit 4-3 Described in Section 15.0 "Output Compare" and Section 17.0 "Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)".

bit 2-1 RTSECSEL<1:0>: RTCC Seconds Clock Output Select bits<sup>(1)</sup>

'1' = Bit is set

- 11 = Reserved; do not use

- 10 = RTCC source clock is selected for the RTCC pin (can be LPRC or SOSC, depending on the RTCOSC (FDS<5>) bit setting)

'0' = Bit is cleared

- 01 = RTCC seconds clock is selected for the RTCC pin

- 00 = RTCC alarm pulse is selected for the RTCC pin

- bit 0 Unimplemented: Read as '0'

-n = Value at POR

x = Bit is unknown

#### REGISTER 19-10: ALMINSEC: ALARM MINUTES AND SECONDS VALUE REGISTER

| U-0    | R/W-x   |

|--------|---------|---------|---------|---------|---------|---------|---------|

| —      | MINTEN2 | MINTEN1 | MINTEN0 | MINONE3 | MINONE2 | MINONE1 | MINONE0 |

| bit 15 |         |         |         |         |         |         | bit 8   |

| U-0   | R/W-x   |

|-------|---------|---------|---------|---------|---------|---------|---------|

| —     | SECTEN2 | SECTEN1 | SECTEN0 | SECONE3 | SECONE2 | SECONE1 | SECONE0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15    | Unimplemented: Read as '0'                                          |

|-----------|---------------------------------------------------------------------|

| bit 14-12 | MINTEN<2:0>: Binary Coded Decimal Value of Minute's Tens Digit bits |

|           | Contains a value from 0 to 5.                                       |

| bit 11-8  | MINONE<3:0>: Binary Coded Decimal Value of Minute's Ones Digit bits |

|           | Contains a value from 0 to 9.                                       |

| bit 7     | Unimplemented: Read as '0'                                          |

| bit 6-4   | SECTEN<2:0>: Binary Coded Decimal Value of Second's Tens Digit bits |

|           | Contains a value from 0 to 5.                                       |

| bit 3-0   | SECONE<3:0>: Binary Coded Decimal Value of Second's Ones Digit bits |

|           | Contains a value from 0 to 9.                                       |

NOTES:

| R/P-1               | R/P-1                  | R/P-1                                                                                                   | R/P-1                        | R/P-1                          | U-0             | R/P-1           | R/P-1             |  |  |  |  |

|---------------------|------------------------|---------------------------------------------------------------------------------------------------------|------------------------------|--------------------------------|-----------------|-----------------|-------------------|--|--|--|--|

| MCLRE <sup>(2</sup> | ) BORV1 <sup>(3)</sup> | BORV0 <sup>(3)</sup>                                                                                    | I2C1SEL <sup>(1)</sup>       | PWRTEN                         | _               | BOREN1          | BOREN0            |  |  |  |  |

| bit 7               | ·                      |                                                                                                         |                              |                                |                 |                 | bit 0             |  |  |  |  |

|                     |                        |                                                                                                         |                              |                                |                 |                 |                   |  |  |  |  |

| Legend:             |                        |                                                                                                         |                              |                                |                 |                 |                   |  |  |  |  |

| R = Reada           | able bit               | P = Program                                                                                             | nable bit                    | U = Unimplem                   | nented bit, rea | d as '0'        |                   |  |  |  |  |

| -n = Value          | at POR                 | '1' = Bit is set                                                                                        |                              | '0' = Bit is clea              | ared            | x = Bit is unkr | nown              |  |  |  |  |

| bit 7               | MCLRE: MCL             | <br>R Pin Enable b                                                                                      | <sub>it</sub> (2)            |                                |                 |                 |                   |  |  |  |  |

| 2                   |                        | is enabled; RA                                                                                          |                              | isabled                        |                 |                 |                   |  |  |  |  |

|                     |                        | pin is enabled;                                                                                         |                              |                                |                 |                 |                   |  |  |  |  |

| bit 6-5             | BORV<1:0>:             | Brown-out Rese                                                                                          | et Enable bits <sup>(3</sup> | )                              |                 |                 |                   |  |  |  |  |

|                     |                        | ut Reset is set t                                                                                       | o the lowest vo              | oltage                         |                 |                 |                   |  |  |  |  |

|                     |                        | 10 = Brown-out Reset                                                                                    |                              |                                |                 |                 |                   |  |  |  |  |

|                     |                        | 01 = Brown-out Reset is set to the highest voltage<br>00 = Low-Power Brown-out Reset occurs around 2.0V |                              |                                |                 |                 |                   |  |  |  |  |

| bit 4               |                        | ernate I2C1 Pin                                                                                         |                              | 00110 2.0 V                    |                 |                 |                   |  |  |  |  |

| DIL 4               |                        | ocation for SCL                                                                                         |                              |                                |                 |                 |                   |  |  |  |  |

|                     |                        | cation for SCL1                                                                                         |                              |                                |                 |                 |                   |  |  |  |  |

| bit 3               | PWRTEN: Po             | wer-up Timer E                                                                                          | nable bit                    |                                |                 |                 |                   |  |  |  |  |