Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 18                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1.5K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 9x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 20-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16ka101t-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### REGISTER 3-2: CORCON: CPU CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      |     |     |     | —   |     | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/C-0, HSC          | R/W-0 | U-0 | U-0   |

|-------|-----|-----|-----|---------------------|-------|-----|-------|

| _     | —   |     | —   | IPL3 <sup>(1)</sup> | PSV   | —   | —     |

| bit 7 |     |     |     |                     |       |     | bit 0 |

| Legend:           | HSC = Hardware Settable/Clearable bit |                                    |                    |  |  |

|-------------------|---------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 15-4 | Unimplemented: Read as '0'                                                                                                    |

|----------|-------------------------------------------------------------------------------------------------------------------------------|

| bit 3    | IPL3: CPU Interrupt Priority Level Status bit <sup>(1)</sup>                                                                  |

|          | <ul> <li>1 = CPU interrupt priority level is greater than 7</li> <li>0 = CPU interrupt priority level is 7 or less</li> </ul> |

| bit 2    | <b>PSV:</b> Program Space Visibility in Data Space Enable bit                                                                 |

|          | 1 = Program space is visible in data space                                                                                    |

|          | 0 = Program space is not visible in data space                                                                                |

| bit 1-0  | Unimplemented: Read as '0'                                                                                                    |

**Note 1:** User interrupts are disabled when IPL3 = 1.

#### 3.3 Arithmetic Logic Unit (ALU)

The PIC24F ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

The PIC24F CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware division for 16-bit divisor.

#### 3.3.1 MULTIPLIER

The ALU contains a high-speed, 17-bit x 17-bit multiplier. It supports unsigned, signed or mixed sign operation in several multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

| REGISTER 8-12: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4 |                                                                                                |                                                                                                            |               |                   |                 |                 |        |  |  |  |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|---------------|-------------------|-----------------|-----------------|--------|--|--|--|

| U-0                                                      | U-0                                                                                            | R/W-0                                                                                                      | U-0           | U-0               | U-0             | U-0             | R/W-0  |  |  |  |

| _                                                        | —                                                                                              | CTMUIE                                                                                                     | _             | —                 | —               | _               | HLVDIE |  |  |  |

| bit 15                                                   | ·                                                                                              |                                                                                                            |               |                   |                 |                 | bit 8  |  |  |  |

|                                                          |                                                                                                |                                                                                                            |               |                   |                 |                 |        |  |  |  |

| U-0                                                      | U-0                                                                                            | U-0                                                                                                        | U-0           | R/W-0             | R/W-0           | R/W-0           | U-0    |  |  |  |

| _                                                        | _                                                                                              | —                                                                                                          | _             | CRCIE             | U2ERIE          | U1ERIE          | —      |  |  |  |

| bit 7                                                    |                                                                                                |                                                                                                            |               |                   |                 |                 | bit C  |  |  |  |

|                                                          |                                                                                                |                                                                                                            |               |                   |                 |                 |        |  |  |  |

| Legend:                                                  |                                                                                                |                                                                                                            |               |                   |                 |                 |        |  |  |  |

| R = Readab                                               | ole bit                                                                                        | W = Writable b                                                                                             | bit           | U = Unimplen      | nented bit, rea | d as '0'        |        |  |  |  |

| -n = Value a                                             | at POR                                                                                         | '1' = Bit is set                                                                                           |               | '0' = Bit is clea | ared            | x = Bit is unkr | nown   |  |  |  |

|                                                          |                                                                                                |                                                                                                            |               |                   |                 |                 |        |  |  |  |

| bit 15-14                                                | Unimplemer                                                                                     | nted: Read as '0                                                                                           | ,             |                   |                 |                 |        |  |  |  |

| bit 13                                                   |                                                                                                | MU Interrupt En                                                                                            |               |                   |                 |                 |        |  |  |  |

|                                                          |                                                                                                | <ol> <li>I = Interrupt request is enabled</li> <li>Interrupt request is not enabled</li> </ol>             |               |                   |                 |                 |        |  |  |  |

| bit 12-9                                                 |                                                                                                | nted: Read as '0                                                                                           |               |                   |                 |                 |        |  |  |  |

| bit 8                                                    | •                                                                                              | h/Low-Voltage D                                                                                            |               | t Enable bit      |                 |                 |        |  |  |  |

|                                                          | •                                                                                              | •                                                                                                          |               |                   |                 |                 |        |  |  |  |

|                                                          | <ol> <li>I = Interrupt request is enabled</li> <li>Interrupt request is not enabled</li> </ol> |                                                                                                            |               |                   |                 |                 |        |  |  |  |

| bit 7-4                                                  | Unimplemer                                                                                     | ted: Read as '0                                                                                            | ,             |                   |                 |                 |        |  |  |  |

| bit 3                                                    | CRCIE: CRC                                                                                     | Generator Inter                                                                                            | rupt Enable b | pit               |                 |                 |        |  |  |  |

|                                                          |                                                                                                | = Interrupt request is enabled                                                                             |               |                   |                 |                 |        |  |  |  |

|                                                          | 0 = Interrupt                                                                                  | request is not er                                                                                          | nabled        |                   |                 |                 |        |  |  |  |

| bit 2                                                    |                                                                                                | U2ERIE: UART2 Error Interrupt Enable bit                                                                   |               |                   |                 |                 |        |  |  |  |

|                                                          |                                                                                                | 1 = Interrupt request is enabled                                                                           |               |                   |                 |                 |        |  |  |  |

| bit 1                                                    | •                                                                                              | <ul> <li>0 = Interrupt request is not enabled</li> <li>U1ERIE: UART1 Error Interrupt Enable bit</li> </ul> |               |                   |                 |                 |        |  |  |  |

| DILI                                                     |                                                                                                | request is enable                                                                                          | •             |                   |                 |                 |        |  |  |  |

|                                                          |                                                                                                | request is not er                                                                                          |               |                   |                 |                 |        |  |  |  |

| bit 0                                                    | -                                                                                              | ted: Read as '0                                                                                            |               |                   |                 |                 |        |  |  |  |

|                                                          | •                                                                                              |                                                                                                            |               |                   |                 |                 |        |  |  |  |

#### REGISTER 8-22: IPC18: INTERRUPT PRIORITY CONTROL REGISTER 18

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0     | U-0     | U-0     |

|--------|-----|-----|-----|-----|---------|---------|---------|

| —      | _   | —   | —   | _   |         | —       | —       |

| bit 15 |     |     |     |     |         |         | bit 8   |

|        |     |     |     |     |         |         |         |

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-1   | R/W-0   | R/W-0   |

| —      | —   | —   | —   | —   | HLVDIP2 | HLVDIP1 | HLVDIP0 |

| bit 7  |     |     |     |     |         |         | bit 0   |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 2-0 HLVDIP<2:0>: High/Low-Voltage Detect Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

•

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

#### REGISTER 8-23: IPC19: INTERRUPT PRIORITY CONTROL REGISTER 19

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-1   | R/W-0   | R/W-0   | U-0 | U-0 | U-0 | U-0   |

|-------|---------|---------|---------|-----|-----|-----|-------|

| _     | CTMUIP2 | CTMUIP1 | CTMUIP0 | —   |     |     | _     |

| bit 7 |         |         |         |     |     |     | bit 0 |

| Legend:                                                              |                  |                      |                    |

|----------------------------------------------------------------------|------------------|----------------------|--------------------|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                      |                    |

| -n = Value at POR                                                    | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 15-7 Unimplemented: Read as '0'

#### 9.4 Clock Switching Operation

With few limitations, applications are free to switch between any of the four clock sources (POSC, SOSC, FRC and LPRC) under software control and at any time. To limit the possible side effects that could result from this flexibility, PIC24F devices have a safeguard lock built into the switching process.

**Note:** The Primary Oscillator mode has three different submodes (XT, HS and EC), which are determined by the POSCMDx Configuration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch between the different primary submodes without reprogramming the device.

#### 9.4.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the FOSC Configuration register must be programmed to '0'. (Refer to **Section 26.1 "Configuration Bits"** for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and FSCM function are disabled; this is the default setting.

The NOSCx control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSCx bits (OSCCON<14:12>) will reflect the clock source selected by the FNOSCx Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled; it is held at '0' at all times.

#### 9.4.2 OSCILLATOR SWITCHING SEQUENCE

At a minimum, performing a clock switch requires this basic sequence:

- 1. If desired, read the COSCx bits (OSCCON<14:12>), to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- 3. Write the appropriate value to the NOSCx bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically as follows:

- 1. The clock switching hardware compares the COSCx bits with the new value of the NOSCx bits. If they are the same, then the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the LOCK (OSCCON<5>) and CF (OSCCON<3>) bits are cleared.

- The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware will wait until the OST expires. If the new source is using the PLL, then the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- 5. The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSCx bits value is transferred to the COSCx bits.

- The old clock source is turned off at this time, with the exception of LPRC (if WDT, FSCM or RTCC with LPRC as clock source are enabled) or SOSC (if SOSCEN remains enabled).

Note 1: The processor will continue to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

#### 10.2.2 IDLE MODE

Idle mode has these features:

- The CPU will stop executing instructions.

- · The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Selective Peripheral Module Control").

- If the WDT or FSCM is enabled, the LPRC will also remain active.

The device will wake from Idle mode on any of these events:

- Any interrupt that is individually enabled

- · Any device Reset

- · A WDT time-out

On wake-up from Idle, the clock is re-applied to the CPU and instruction execution begins immediately, starting with the instruction following the PWRSAV instruction or the first instruction in the ISR.

#### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction will be held off until entry into Sleep or Idle mode has completed. The device will then wake-up from Sleep or Idle mode.

#### 10.2.4 DEEP SLEEP MODE

In PIC24F16KA102 family devices, Deep Sleep mode is intended to provide the lowest levels of power consumption available without requiring the use of external switches to completely remove all power from the device. Entry into Deep Sleep mode is completely under software control. Exit from Deep Sleep mode can be triggered from any of the following events:

- POR event

- MCLR event

- RTCC alarm (If the RTCC is present)

- External Interrupt 0

- Deep Sleep Watchdog Timer (DSWDT) time-out

In Deep Sleep mode, it is possible to keep the device Real-Time Clock and Calendar (RTCC) running without the loss of clock cycles.

The device has a dedicated Deep Sleep Brown-out Reset (DSBOR) and a Deep Sleep Watchdog Timer Reset (DSWDT) for monitoring voltage and time-out events. The DSBOR and DSWDT are independent of the standard BOR and WDT used with other power-managed modes (Sleep, Idle and Doze).

#### 10.2.4.1 Entering Deep Sleep Mode

Deep Sleep mode is entered by setting the DSEN bit in the DSCON register, and then executing a Sleep command (PWRSAV #SLEEP\_MODE), within one instruction cycle, to minimize the chance that Deep Sleep will be spuriously entered.

If the PWRSAV command is not given within one instruction cycle, the DSEN bit will be cleared by the hardware and must be set again by the software before entering Deep Sleep mode. The DSEN bit is also automatically cleared when exiting the Deep Sleep mode.

| Note: | To re-enter Deep Sleep after a Deep Sleep |

|-------|-------------------------------------------|

|       | wake-up, allow a delay of at least 3 TCY  |

|       | after clearing the RELEASE bit.           |

The sequence to enter Deep Sleep mode is:

- If the application requires the Deep Sleep WDT, enable it and configure its clock source (see Section 10.2.4.5 "Deep Sleep WDT" for details).

- If the application requires Deep Sleep BOR, enable it by programming the DSBOREN Configuration bit (FDS<6>).

- 3. If the application requires wake-up from Deep Sleep on RTCC alarm, enable and configure the RTCC module (see Section 19.0 "Real-Time Clock and Calendar (RTCC)" for more information).

- 4. If needed, save any critical application context data by writing it to the DSGPR0 and DSGPR1 registers (optional).

- 5. Enable Deep Sleep mode by setting the DSEN bit (DSCON<15>).

- 6. Enter Deep Sleep mode by issuing 3 NOP commands, and then a PWRSAV #0 instruction.

Any time the DSEN bit is set, all bits in the DSWAKE register will be automatically cleared.

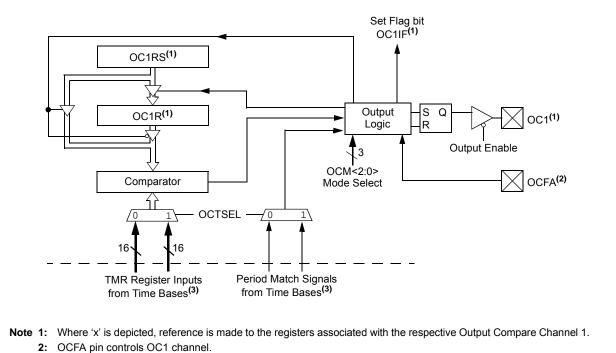

#### 15.3 Pulse-Width Modulation (PWM) Mode

The following steps should be taken when configuring the output compare module for PWM operation:

- 1. Set the PWM period by writing to the selected Timer Period register (PRy).

- 2. Set the PWM duty cycle by writing to the OC1RS register.

- 3. Write the OC1R register with the initial duty cycle.

- 4. Enable interrupts, if required, for the timer and output compare modules. The output compare interrupt is required for PWM Fault pin utilization.

- Configure the output compare module for one of two PWM Operation modes by writing to the Output Compare Mode bits, OCM<2:0> (OC1CON<2:0>).

- 6. Set the TMRy prescale value and enable the time base by setting TON (TxCON<15>) = 1.

- Note: The OC1R register should be initialized before the output compare module is first enabled. The OC1R register becomes a read-only Duty Cycle register when the module is operated in the PWM modes. The value held in OC1R will become the PWM duty cycle for the first PWM period. The contents of the Output Compare 1 Secondary register, OC1RS, will not be transferred into OC1R until a time base period match occurs.

#### 15.3.1 PWM PERIOD

The PWM period is specified by writing to PRy, the Timer Period register. The PWM period can be calculated using Equation 15-1.

### EQUATION 15-1: CALCULATING THE PWM PERIOD<sup>(1)</sup>

PWM Period =  $[(PRy) + 1] \bullet TCY \bullet (Timer Prescale Value)$ where:

PWM Frequency = 1/[PWM Period]

- Note 1: Based on Tcy = 2 \* Tosc; Doze mode and PLL are disabled.

- Note: A PRy value of N will produce a PWM period of N + 1 time base count cycles. For example, a value of 7, written into the PRy register, will yield a period consisting of 8 time base cycles.

#### 15.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the OC1RS register. The OC1RS register can be written to at any time, but the duty cycle value is not latched into OC1R until a match between PRy and TMRy occurs (i.e., the period is complete). This provides a double buffer for the PWM duty cycle and is essential for glitchless PWM operation. In PWM mode, OC1R is a read-only register.

Some important boundary parameters of the PWM duty cycle include:

- If the Output Compare 1 register, OC1R, is loaded with 0000h, the OC1 pin will remain low (0% duty cycle).

- If OC1R is greater than PRy (Timer Period register), the pin will remain high (100% duty cycle).

- If OC1R is equal to PRy, the OC1 pin will be low for one time base count value and high for all other count values.

See Example 15-1 for PWM mode timing details. Table 15-1 provides an example of PWM frequencies and resolutions for a device operating at 10 MIPS.

#### EQUATION 15-2: CALCULATION FOR MAXIMUM PWM RESOLUTION<sup>(1)</sup>

Note 1: Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

Control princontrols our channel.

Each output compare channel can use one of two selectable time bases. Refer to the device data sheet for the time bases associated with the module.

#### REGISTER 16-2: SPI1CON1: SPI1 CONTROL REGISTER 1 (CONTINUED)

bit 1-0 **PPRE<1:0>:** Primary Prescale bits (Master mode)

- 11 = Primary prescale 1:1

- 10 = Primary prescale 4:1

- 01 = Primary prescale 16:1

- 00 = Primary prescale 64:1

- **Note 1:** The CKE bit is not used in the Framed SPI modes. The user should program this bit to '0' for the Framed SPI modes (FRMEN = 1).

#### REGISTER 16-3: SPI1CON2: SPI1 CONTROL REGISTER 2

| R/W-0            | R/W-0                                                                                                                                                                                                                                                                                                                              | R/W-0                                                    | U-0              | U-0               | U-0             | U-0             | U-0    |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------|-------------------|-----------------|-----------------|--------|

| FRMEN            | SPIFSD                                                                                                                                                                                                                                                                                                                             | SPIFPOL                                                  |                  |                   |                 | —               |        |

| bit 15           |                                                                                                                                                                                                                                                                                                                                    |                                                          |                  |                   |                 |                 | bit 8  |

|                  |                                                                                                                                                                                                                                                                                                                                    |                                                          |                  |                   |                 |                 |        |

| U-0              | U-0                                                                                                                                                                                                                                                                                                                                | U-0                                                      | U-0              | U-0               | U-0             | R/W-0           | R/W-0  |

| —                | _                                                                                                                                                                                                                                                                                                                                  | —                                                        | —                | —                 | —               | SPIFE           | SPIBEN |

| bit 7            |                                                                                                                                                                                                                                                                                                                                    |                                                          |                  |                   |                 |                 | bit 0  |

|                  |                                                                                                                                                                                                                                                                                                                                    |                                                          |                  |                   |                 |                 |        |

| Legend:          |                                                                                                                                                                                                                                                                                                                                    |                                                          |                  |                   |                 |                 |        |

| R = Readable     | e bit                                                                                                                                                                                                                                                                                                                              | W = Writable b                                           | bit              | U = Unimplem      | nented bit, rea | d as '0'        |        |

| -n = Value at    | POR                                                                                                                                                                                                                                                                                                                                | '1' = Bit is set                                         |                  | '0' = Bit is clea | ared            | x = Bit is unkr | nown   |

| bit 14<br>bit 13 | <ul> <li>1 = Framed SPI1 support is enabled</li> <li>0 = Framed SPI1 support is disabled</li> <li>SPIFSD: Frame Sync Pulse Direction Control on SS1 Pin bit</li> <li>1 = Frame sync pulse input (slave)</li> <li>0 = Frame sync pulse output (master)</li> <li>SPIFPOL: Frame Sync Pulse Polarity bit (Frame mode only)</li> </ul> |                                                          |                  |                   |                 |                 |        |

|                  | 0 = Frame sy                                                                                                                                                                                                                                                                                                                       | nc pulse is activ<br>nc pulse is activ                   | ve-low           |                   |                 |                 |        |

| bit 12-2         | -                                                                                                                                                                                                                                                                                                                                  | ted: Read as '0                                          |                  |                   |                 |                 |        |

| bit 1            | 1 = Frame sy                                                                                                                                                                                                                                                                                                                       | e Sync Pulse Eo<br>nc pulse coincio<br>nc pulse precec   | les with the fir | st bit clock      |                 |                 |        |

| bit 0            | 1 = Enhanced                                                                                                                                                                                                                                                                                                                       | anced Buffer E<br>d Buffer is enabl<br>d Buffer is disab | ed               | node)             |                 |                 |        |

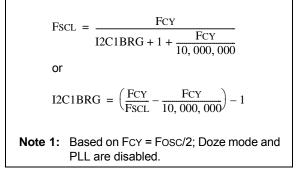

#### 17.3 Setting Baud Rate When Operating as a Bus Master

To compute the Baud Rate Generator (BRG) reload value, use Equation 17-1.

### EQUATION 17-1: COMPUTING BAUD RATE RELOAD VALUE<sup>(1)</sup>

#### TABLE 17-1: I<sup>2</sup>C<sup>™</sup> CLOCK RATES<sup>(1)</sup>

#### 17.4 Slave Address Masking

The I2C1MSK register (Register 17-3) designates address bit positions as "don't care" for both 7-Bit and 10-Bit Addressing modes. Setting a particular bit location (= 1) in the I2C1MSK register causes the slave module to respond whether the corresponding address bit value is '0' or '1'. For example, when I2C1MSK is set to '00100000', the slave module will detect both addresses: '0000000' and '00100000'.

To enable address masking, the Intelligent Peripheral Management Interface (IPMI) must be disabled by clearing the IPMIEN bit (I2C1CON<11>).

**Note:** As a result of changes in the I<sup>2</sup>C protocol, the addresses in Table 17-2 are reserved and will not be Acknowledged in Slave mode. This includes any address mask settings that include any of these addresses.

| Required       |        | I2C1B     | Actual        |           |

|----------------|--------|-----------|---------------|-----------|

| System<br>FscL | Fcy    | (Decimal) | (Hexadecimal) | FSCL      |

| 100 kHz        | 16 MHz | 157       | 9D            | 100 kHz   |

| 100 kHz        | 8 MHz  | 78        | 4E            | 100 kHz   |

| 100 kHz        | 4 MHz  | 39        | 27            | 99 kHz    |

| 400 kHz        | 16 MHz | 37        | 25            | 404 kHz   |

| 400 kHz        | 8 MHz  | 18        | 12            | 404 kHz   |

| 400 kHz        | 4 MHz  | 9         | 9             | 385 kHz   |

| 400 kHz        | 2 MHz  | 4         | 4             | 385 kHz   |

| 1 MHz          | 16 MHz | 13        | D             | 1.026 MHz |

| 1 MHz          | 8 MHz  | 6         | 6             | 1.026 MHz |

| 1 MHz          | 4 MHz  | 3         | 3             | 0.909 MHz |

Note 1: Based on Fcy = Fosc/2; Doze mode and PLL are disabled;

#### TABLE 17-2: I<sup>2</sup>C<sup>™</sup> RESERVED ADDRESSES<sup>(1)</sup>

| Slave<br>Address | R/W<br>Bit | Description                            |

|------------------|------------|----------------------------------------|

| 0000 000         | 0          | General Call Address <sup>(2)</sup>    |

| 0000 000         | 1          | Start Byte                             |

| 0000 001         | x          | Cbus Address                           |

| 0000 010         | x          | Reserved                               |

| 0000 011         | x          | Reserved                               |

| 0000 1xx         | x          | HS Mode Master Code                    |

| 1111 1xx         | x          | Reserved                               |

| 1111 0xx         | x          | 10-Bit Slave Upper Byte <sup>(3)</sup> |

Note 1: The address bits listed here will never cause an address match, independent of the address mask settings.

- 2: The address will be Acknowledged only if GCEN = 1.

- 3: A match on this address can only occur on the upper byte in 10-Bit Addressing mode.

#### 18.1 UART Baud Rate Generator (BRG)

The UART module includes a dedicated 16-bit Baud Rate Generator (BRG). The UxBRG register controls the period of a free-running, 16-bit timer. Equation 18-1 provides the formula for computation of the baud rate with BRGH = 0.

### EQUATION 18-1: UART BAUD RATE WITH BRGH = $0^{(1)}$

Baud Rate =  $\frac{FCY}{16 \cdot (UxBRG + 1)}$ UxBRG =  $\frac{FCY}{16 \cdot Baud Rate} - 1$

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

Example 18-1 provides the calculation of the baud rate error for the following conditions:

- Fcy = 4 MHz

- Desired Baud Rate = 9600

The maximum baud rate (BRGH = 0) possible is Fcy/16 (for UxBRG = 0) and the minimum baud rate possible is Fcy/(16 \* 65536).

Equation 18-2 provides the formula for computation of the baud rate with BRGH = 1.

### EQUATION 18-2: UART BAUD RATE WITH BRGH = $1^{(1)}$

Baud Rate =  $\frac{FCY}{4 \cdot (UxBRG + 1)}$   $UxBRG = \frac{FCY}{4 \cdot Baud Rate} - 1$ Note 1: Based on FCY = FOSC/2; Doze mode and PLL are disabled.

The maximum baud rate (BRGH = 1) possible is FcY/4 (for UxBRG = 0) and the minimum baud rate possible is FcY/(4 \* 65536).

Writing a new value to the UxBRG register causes the BRG timer to be reset (cleared). This ensures the BRG does not wait for a timer overflow before generating the new baud rate.

#### EXAMPLE 18-1: BAUD RATE ERROR CALCULATION (BRGH = 0)<sup>(1)</sup>

```

= FCY/(16 (UxBRG + 1))

Desired Baud Rate

Solving for UxBRG value:

UxBRG

= ((FCY/Desired Baud Rate)/16) - 1

UxBRG

= ((400000/9600)/16) - 1

= 25

UxBRG

Calculated Baud Rate = 400000/(16(25+1))

= 9615

Error

= (Calculated Baud Rate – Desired Baud Rate)

Desired Baud Rate

= (9615 - 9600)/9600

= 0.16\%

Note 1: Based on FCY = FOSC/2; Doze mode and PLL are disabled.

```

#### REGISTER 18-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

- bit 3 BRGH: High Baud Rate Enable bit

- 1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)

0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)

- bit 2-1 **PDSEL<1:0>:** Parity and Data Selection bits

- 11 = 9-bit data, no parity

- 10 = 8-bit data, odd parity

- 01 = 8-bit data, even parity

- 00 = 8-bit data, no parity

- bit 0 STSEL: Stop Bit Selection bit

- 1 = Two Stop bits

- 0 = One Stop bit

- Note 1: This feature is only available for the 16x BRG mode (BRGH = 0).

- 2: Bit availability depends on pin availability.

### 27.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C<sup>®</sup> for Various Device Families

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers

- MPLAB ICD 3

- PICkit™ 3 Debug Express

- Device Programmers

- PICkit<sup>™</sup> 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

#### 27.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- · High-level source code debugging

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- · Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

| Assembly<br>Mnemonic |                  | Assembly Syntax           | Description                                                                              | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|------------------|---------------------------|------------------------------------------------------------------------------------------|---------------|----------------|--------------------------|

| GOTO                 | GOTO             | Expr                      | Go to Address                                                                            | 2             | 2              | None                     |

|                      | GOTO             | Wn                        | Go to Indirect                                                                           | 1             | 2              | None                     |

| INC                  | INC              | f                         | f = f + 1                                                                                | 1             | 1              | C, DC, N, OV, Z          |

|                      | INC              | f,WREG                    | WREG = f + 1                                                                             | 1             | 1              | C, DC, N, OV, Z          |

|                      | INC              | Ws,Wd                     | Wd = Ws + 1                                                                              | 1             | 1              | C, DC, N, OV, Z          |

| INC2                 | INC2             | f                         | f = f + 2                                                                                | 1             | 1              | C, DC, N, OV, Z          |

|                      | INC2             | f,WREG                    | WREG = f + 2                                                                             | 1             | 1              | C, DC, N, OV, Z          |

|                      | INC2             | Ws,Wd                     | Wd = Ws + 2                                                                              | 1             | 1              | C, DC, N, OV, Z          |

| IOR                  | IOR              | f                         | f = f .IOR. WREG                                                                         | 1             | 1              | N, Z                     |

|                      | IOR              | f,WREG                    | WREG = f .IOR. WREG                                                                      | 1             | 1              | N, Z                     |

|                      | IOR              | #lit10,Wn                 | Wd = lit10 .IOR. Wd                                                                      | 1             | 1              | N, Z                     |

|                      | IOR              | Wb,Ws,Wd                  | Wd = Wb .IOR. Ws                                                                         | 1             | 1              | N, Z                     |

|                      | IOR              | Wb,#lit5,Wd               | Wd = Wb .IOR. lit5                                                                       | 1             | 1              | N, Z                     |

| LNK                  | LNK              | #lit14                    | Link Frame Pointer                                                                       | 1             | 1              | None                     |

| LSR                  | LSR              | f                         | f = Logical Right Shift f                                                                | 1             | 1              | C, N, OV, Z              |

|                      | LSR              | f,WREG                    | WREG = Logical Right Shift f                                                             | 1             | 1              | C, N, OV, Z              |

|                      | LSR              | Ws,Wd                     | Wd = Logical Right Shift Ws                                                              | 1             | 1              | C, N, OV, Z              |

|                      | LSR              | Wb,Wns,Wnd                | Wnd = Logical Right Shift Wb by Wns                                                      | 1             | 1              | N, Z                     |

|                      | LSR              | Wb,#lit5,Wnd              | Wnd = Logical Right Shift Wb by lit5                                                     | 1             | 1              | N, Z                     |

| MOV                  | MOV              | f,Wn                      | Move f to Wn                                                                             | 1             | 1              | None                     |

|                      | MOV              | [Wns+Slit10],Wnd          | Move [Wns+Slit10] to Wnd                                                                 | 1             | 1              | None                     |

|                      | MOV              | f                         | Move f to f                                                                              | 1             | 1              | N, Z                     |

|                      | MOV              | f,WREG                    | Move f to WREG                                                                           | 1             | 1              | N, Z                     |

|                      | MOV              | #lit16,Wn                 | Move 16-bit Literal to Wn                                                                | 1             | 1              | None                     |

|                      | MOV.b            | #lit8,Wn                  | Move 8-bit Literal to Wn                                                                 | 1             | 1              | None                     |

|                      | MOV              | Wn,f                      | Move Wn to f                                                                             | 1             | 1              | None                     |

|                      | MOV              | Wns,[Wns+Slit10]          | Move Wns to [Wns+Slit10]                                                                 | 1             | 1              | None                     |

|                      | MOV              | Wso,Wdo                   | Move Ws to Wd                                                                            | 1             | 1              | None                     |

|                      | MOV              | WREG, f                   | Move WREG to f                                                                           | 1             | 1              | N, Z                     |

|                      | MOV.D            | Wns,Wd                    | Move Double from W(ns):W(ns+1) to Wd                                                     | 1             | 2              | None                     |

|                      | MOV.D            | Wills, Wind               | Move Double from Ws to W(nd+1):W(nd)                                                     | 1             | 2              | None                     |

| MUL                  | MUL.SS           | Wb,Ws,Wnd                 | {Wnd+1, Wnd} = Signed(Wb) * Signed(Ws)                                                   | 1             | 1              | None                     |

| NOL                  | MUL.SU           | Wb,Ws,Wnd                 | {Wnd+1, Wnd} = Signed(Wb) * Unsigned(Ws)                                                 | 1             | 1              | None                     |

|                      | MUL.US           | Wb,Ws,Wnd<br>Wb,Ws,Wnd    | {Wnd+1, Wnd} = Unsigned(Wb) * Signed(Ws)<br>{Wnd+1, Wnd} = Unsigned(Wb) * Signed(Ws)     | 1             | 1              | None                     |

|                      |                  |                           | {Wnd+1, Wnd} = Unsigned(Wb) * Unsigned(Ws)<br>{Wnd+1, Wnd} = Unsigned(Wb) * Unsigned(Ws) | 1             | 1              | None                     |

|                      | MUL.UU<br>MUL.SU | Wb,Ws,Wnd<br>Wb,#lit5,Wnd | {Wnd+1, Wnd} = Signed(Wb) * Unsigned(Ws)<br>{Wnd+1, Wnd} = Signed(Wb) * Unsigned(lit5)   | 1             | 1              | None                     |

|                      | MUL.UU           | Wb,#lit5,Wnd              | {Wnd+1, Wnd} = Unsigned(Wb) * Unsigned(lit5)                                             | 1             | 1              | None                     |

|                      | MUL.00           | f                         | W3:W2 = f * WREG                                                                         | 1             | 1              | None                     |

|                      |                  |                           | $f = \overline{f} + 1$                                                                   |               |                |                          |

| NEG                  | NEG              | f                         |                                                                                          | 1             | 1              | C, DC, N, OV, Z          |

|                      | NEG              | f,WREG                    | WREG = <del>1</del> + 1                                                                  | 1             | 1              | C, DC, N, OV, Z          |

|                      | NEG              | Ws,Wd                     | Wd = Ws + 1                                                                              | 1             | 1              | C, DC, N, OV, Z          |

| NOP                  | NOP              |                           | No Operation                                                                             | 1             | 1              | None                     |

|                      | NOPR             |                           | No Operation                                                                             | 1             | 1              | None                     |

| POP                  | POP              | f                         | Pop f from Top-of-Stack (TOS)                                                            | 1             | 1              | None                     |

|                      | POP              | Wdo                       | Pop from Top-of-Stack (TOS) to Wdo                                                       | 1             | 1              | None                     |

|                      | POP.D            | Wnd                       | Pop from Top-of-Stack (TOS) to W(nd):W(nd+1)                                             | 1             | 2              | None                     |

|                      | POP.S            |                           | Pop Shadow Registers                                                                     | 1             | 1              | All                      |

| PUSH                 | PUSH             | f                         | Push f to Top-of-Stack (TOS)                                                             | 1             | 1              | None                     |

|                      | PUSH             | Wso                       | Push Wso to Top-of-Stack (TOS)                                                           | 1             | 1              | None                     |

|                      | PUSH.D           | Wns                       | Push W(ns):W(ns+1) to Top-of-Stack (TOS)                                                 | 1             | 2              | None                     |

|                      | PUSH.S           |                           | Push Shadow Registers                                                                    | 1             | 1              | None                     |

#### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

#### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Assembly<br>Mnemonic |        | Assembly Syntax | Description                             | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|--------|-----------------|-----------------------------------------|---------------|----------------|--------------------------|

| PWRSAV               | PWRSAV | #lit1           | Go into Sleep or Idle mode              | 1             | 1              | WDTO, Sleep              |

| RCALL                | RCALL  | Expr            | Relative Call                           | 1             | 2              | None                     |

|                      | RCALL  | Wn              | Computed Call                           | 1             | 2              | None                     |

| REPEAT               | REPEAT | #lit14          | Repeat Next Instruction lit14 + 1 times | 1             | 1              | None                     |

|                      | REPEAT | Wn              | Repeat Next Instruction (Wn) + 1 times  | 1             | 1              | None                     |

| RESET                | RESET  |                 | Software Device Reset                   | 1             | 1              | None                     |

| RETFIE               | RETFIE |                 | Return from Interrupt                   | 1             | 3 (2)          | None                     |

| RETLW                | RETLW  | #lit10,Wn       | Return with Literal in Wn               | 1             | 3 (2)          | None                     |

| RETURN               | RETURN |                 | Return from Subroutine                  | 1             | 3 (2)          | None                     |

| RLC                  | RLC    | f               | f = Rotate Left through Carry f         | 1             | 1              | C, N, Z                  |

|                      | RLC    | f,WREG          | WREG = Rotate Left through Carry f      | 1             | 1              | C, N, Z                  |

|                      | RLC    | Ws,Wd           | Wd = Rotate Left through Carry Ws       | 1             | 1              | C, N, Z                  |

| RLNC                 | RLNC   | f               | f = Rotate Left (No Carry) f            | 1             | 1              | N, Z                     |

|                      | RLNC   | f,WREG          | WREG = Rotate Left (No Carry) f         | 1             | 1              | N, Z                     |

|                      | RLNC   | Ws,Wd           | Wd = Rotate Left (No Carry) Ws          | 1             | 1              | N, Z                     |

| RRC                  | RRC    | f               | f = Rotate Right through Carry f        | 1             | 1              | C, N, Z                  |

|                      | RRC    | f,WREG          | WREG = Rotate Right through Carry f     | 1             | 1              | C, N, Z                  |

|                      | RRC    | Ws,Wd           | Wd = Rotate Right through Carry Ws      | 1             | 1              | C, N, Z                  |

| RRNC                 | RRNC   | f               | f = Rotate Right (No Carry) f           | 1             | 1              | N, Z                     |

|                      | RRNC   | f,WREG          | WREG = Rotate Right (No Carry) f        | 1             | 1              | N, Z                     |

|                      | RRNC   | Ws,Wd           | Wd = Rotate Right (No Carry) Ws         | 1             | 1              | N, Z                     |

| SE                   | SE     | Ws,Wnd          | Wnd = Sign-Extended Ws                  | 1             | 1              | C, N, Z                  |

| SETM                 | SETM   | f               | f = FFFFh                               | 1             | 1              | None                     |

|                      | SETM   | WREG            | WREG = FFFFh                            | 1             | 1              | None                     |

|                      | SETM   | Ws              | Ws = FFFFh                              | 1             | 1              | None                     |

| SL                   | SL     | f               | f = Left Shift f                        | 1             | 1              | C, N, OV, Z              |

|                      | SL     | f,WREG          | WREG = Left Shift f                     | 1             | 1              | C, N, OV, Z              |

|                      | SL     | Ws,Wd           | Wd = Left Shift Ws                      | 1             | 1              | C, N, OV, Z              |

|                      | SL     | Wb,Wns,Wnd      | Wnd = Left Shift Wb by Wns              | 1             | 1              | N, Z                     |

|                      | SL     | Wb,#lit5,Wnd    | Wnd = Left Shift Wb by lit5             | 1             | 1              | N, Z                     |

| SUB                  | SUB    | f               | f = f – WREG                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUB    | f,WREG          | WREG = f – WREG                         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUB    | #lit10,Wn       | Wn = Wn - lit10                         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUB    | Wb,Ws,Wd        | Wd = Wb – Ws                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUB    | Wb,#lit5,Wd     | Wd = Wb - lit5                          | 1             | 1              | C, DC, N, OV, Z          |

| SUBB                 | SUBB   | f               | $f = f - WREG - (\overline{C})$         | 1             | 1              | C, DC, N, OV, Z          |

| JUDD                 |        | f,WREG          | $WREG = f - WREG - (\overline{C})$      | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBB   |                 |                                         |               |                |                          |

|                      | SUBB   | #lit10,Wn       | $Wn = Wn - lit10 - (\overline{C})$      | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBB   | Wb,Ws,Wd        | $Wd = Wb - Ws - (\overline{C})$         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBB   | Wb,#lit5,Wd     | Wd = Wb - lit5 - (C)                    | 1             | 1              | C, DC, N, OV, Z          |

| SUBR                 | SUBR   | f               | f = WREG – f                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBR   | f,WREG          | WREG = WREG – f                         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBR   | Wb,Ws,Wd        | Wd = Ws – Wb                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBR   | Wb,#lit5,Wd     | Wd = lit5 – Wb                          | 1             | 1              | C, DC, N, OV, Z          |

| SUBBR                | SUBBR  | f               | $f = WREG - f - (\overline{C})$         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBBR  | f,WREG          | WREG = WREG – $f - (\overline{C})$      | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBBR  | Wb,Ws,Wd        | $Wd = Ws - Wb - (\overline{C})$         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBBR  | Wb,#lit5,Wd     | $Wd = lit5 - Wb - (\overline{C})$       | 1             | 1              | C, DC, N, OV, Z          |

| SWAP                 | SWAP.b | Wn              | Wn = Nibble Swap Wn                     | 1             | 1              | None                     |

|                      | SWAP   | Wn              | Wn = Byte Swap Wn                       | 1             | 1              | None                     |

|                      |        |                 | Read Prog<23:16> to Wd<7:0>             |               |                |                          |

NOTES:

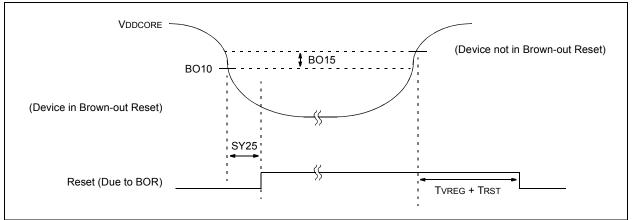

#### FIGURE 29-3: BROWN-OUT RESET CHARACTERISTICS

#### TABLE 29-5:BOR TRIP POINTS

|              | -                  | ting Conditions (unless otherware<br>rature $-40^{\circ}C \le TA \le +85^{\circ}C$ for i<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for | ndustrial | )    |      |      |       |                      |

|--------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------|------|------|------|-------|----------------------|

| Param<br>No. | Sym Characteristic |                                                                                                                                         |           | Min  | Тур  | Max  | Units | Conditions           |

| DC19         | VBOR               | BOR Voltage on VDD Transition                                                                                                           | BOR = 00  | _    | -    | —    | _     | LPBOR <sup>(1)</sup> |

|              |                    |                                                                                                                                         | BOR = 01  | 2.92 | 3    | 3.08 | V     |                      |

|              |                    |                                                                                                                                         | BOR = 10  | 2.63 | 2.7  | 2.77 | V     |                      |

|              |                    |                                                                                                                                         | BOR = 11  | 1.75 | 1.82 | 1.85 | V     |                      |

| DC14         | VBHYS              | BOR Hysteresis                                                                                                                          |           |      | 5    |      | mV    |                      |

**Note 1:** LPBOR re-arms the POR circuit, but does not cause a BOR. LPBOR can be used to ensure a POR after the supply voltage rises to a safe operating level. It does not stop code execution after the supply voltage falls below a chosen trip point.

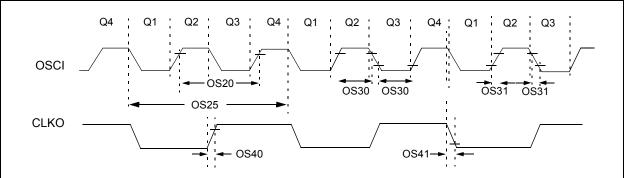

#### FIGURE 29-5: EXTERNAL CLOCK TIMING

#### TABLE 29-19: EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |               |                                                                                        | Standard Operating ten | •                  | e -40°C            | $\leq$ TA $\leq$ +       | <b>3.6V (unless otherwise stated)</b><br>85°C for Industrial<br>125°C for Extended |

|--------------------|---------------|----------------------------------------------------------------------------------------|------------------------|--------------------|--------------------|--------------------------|------------------------------------------------------------------------------------|

| Param<br>No.       | Sym           | Characteristic                                                                         | Min                    | Typ <sup>(1)</sup> | Max                | Units                    | Conditions                                                                         |

| OS10               | Fosc          | External CLKI Frequency<br>(External clocks allowed<br>only in EC mode) <sup>(2)</sup> | DC<br>4                |                    | 32<br>8            | MHz<br>MHz               | EC<br>ECPLL                                                                        |

|                    |               | Oscillator Frequency <sup>(2)</sup>                                                    | 0.2<br>4<br>4<br>31    |                    | 4<br>25<br>8<br>33 | MHz<br>MHz<br>MHz<br>kHz | XT<br>HS<br>HSPLL<br>SOSC                                                          |

| OS20               | Tosc          | Tosc = 1/Fosc                                                                          | —                      | _                  | —                  | —                        | See Parameter OS10 for Fosc value                                                  |

| OS25               | Тсү           | Instruction Cycle Time <sup>(3)</sup>                                                  | 62.5                   | _                  | DC                 | ns                       |                                                                                    |

| OS30               | TosL,<br>TosH | External Clock in (OSCI)<br>High or Low Time                                           | 0.45 x Tosc            | —                  | —                  | ns                       | EC                                                                                 |

| OS31               | TosR,<br>TosF | External Clock in (OSCI)<br>Rise or Fall Time                                          | —                      | _                  | 20                 | ns                       | EC                                                                                 |

| OS40               | TckR          | CLKO Rise Time <sup>(4)</sup>                                                          | —                      | 6                  | 10                 | ns                       |                                                                                    |

| OS41               | TckF          | CLKO Fall Time <sup>(4)</sup>                                                          | —                      | 6                  | 10                 | ns                       |                                                                                    |

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: Refer to Figure 29-1 for the minimum voltage at a given frequency.

- 3: Instruction cycle period (TCY) equals two times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Min." values with an external clock applied to the OSCI/CLKI pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

- 4: Measurements are taken in EC mode. The CLKO signal is measured on the OSCO pin. CLKO is low for the Q1-Q2 period (1/2 TcY) and high for the Q3-Q4 period (1/2 TcY).

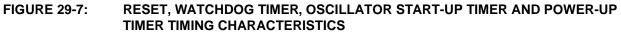

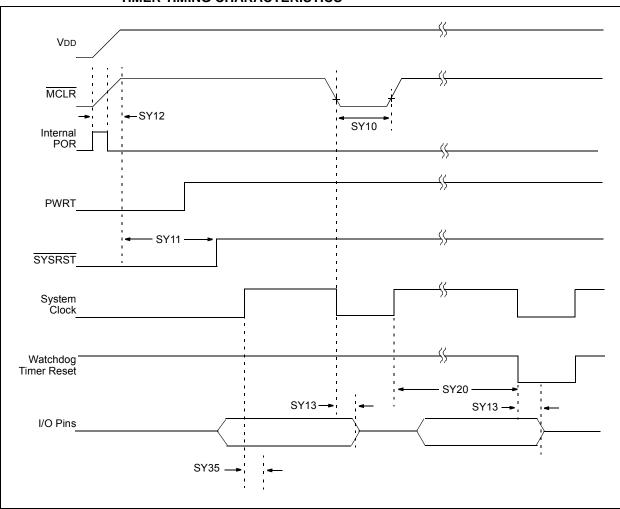

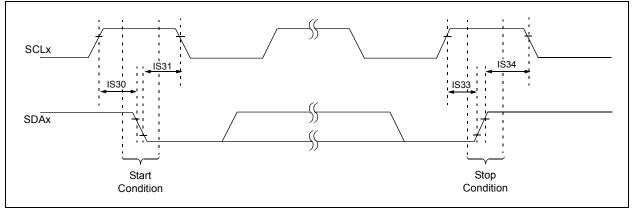

#### FIGURE 29-11: I<sup>2</sup>C<sup>™</sup> BUS START/STOP BITS TIMING CHARACTERISTICS (SLAVE MODE)

| TABLE 29-31: | I <sup>2</sup> C <sup>™</sup> BUS START/STOP BIT TIMING REQUIREMENTS ( | SLAVE MODE) |  |

|--------------|------------------------------------------------------------------------|-------------|--|

|--------------|------------------------------------------------------------------------|-------------|--|

| AC CHARACTERISTICS |         |                 |                           | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |       |                              |                          |

|--------------------|---------|-----------------|---------------------------|-------------------------------------------------------|-----|-------|------------------------------|--------------------------|

| Param<br>No.       | Symbol  | Chara           | cteristic                 | Min                                                   | Max | Units | Conditions                   |                          |

| IS30               | TSU:STA | Start Condition | 100 kHz mode              | 4.7                                                   | _   | μs    | Only relevant for Repeated   |                          |

|                    |         | Setup Time      | Setup Time                | 400 kHz mode                                          | 0.6 | —     | μs                           | Start condition          |

|                    |         |                 | 1 MHz mode <sup>(1)</sup> | 0.25                                                  |     | μs    |                              |                          |

| IS31               | Thd:sta | Start Condition | 100 kHz mode              | 4.0                                                   | —   | μs    | After this period, the first |                          |

|                    |         |                 | Hold Time                 | 400 kHz mode                                          | 0.6 | _     | μs                           | clock pulse is generated |

|                    |         |                 | 1 MHz mode <sup>(1)</sup> | 0.25                                                  | —   | μs    |                              |                          |

| IS33               | Tsu:sto | Stop Condition  | 100 kHz mode              | 4.7                                                   | —   | μs    |                              |                          |

|                    |         | Setup Time      | 400 kHz mode              | 0.6                                                   | —   | μs    |                              |                          |