# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I²C, IrDA, SPI, UART/USART                                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 16KB (5.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 512 x 8                                                                      |

| RAM Size                   | 1.5K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 9x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Through Hole                                                                 |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                      |

| Supplier Device Package    | 28-SPDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16ka102-e-sp |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

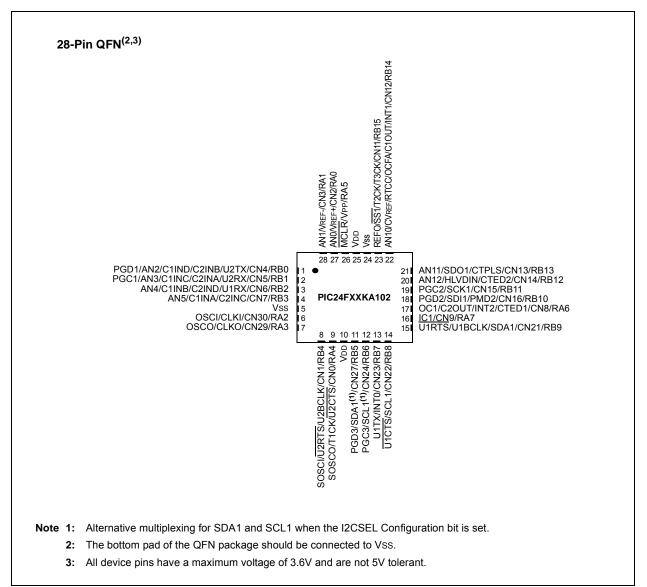

### Pin Diagrams (Continued)

|          |                              | Pin I         | Number                        |                       |     |                  |                                                    |  |  |

|----------|------------------------------|---------------|-------------------------------|-----------------------|-----|------------------|----------------------------------------------------|--|--|

| Function | 20-Pin<br>PDIP/SSOP/<br>SOIC | 20-Pin<br>QFN | 28-Pin<br>SPDIP/<br>SSOP/SOIC | 28-Pin<br>QFN         | I/O | Input<br>Buffer  | Description                                        |  |  |

| PGC1     | 5                            | 2             | 5                             | 2                     | I/O | ST               | In-Circuit Debugger and ICSP™ Programming<br>Clock |  |  |

| PGD1     | 4                            | 1             | 4                             | 1                     | I/O | ST               | In-Circuit Debugger and ICSP Programming Data      |  |  |

| PGC2     | 2                            | 19            | 22                            | 19                    | I/O | ST               | In-Circuit Debugger and ICSP Programming<br>Clock  |  |  |

| PGD2     | 3                            | 20            | 21                            | 18                    | I/O | ST               | In-Circuit Debugger and ICSP Programming Data      |  |  |

| PGC3     | 10                           | 7             | 15                            | 12                    | I/O | ST               | In-Circuit Debugger and ICSP Programming<br>Clock  |  |  |

| PGD3     | 9                            | 6             | 14                            | 11                    | I/O | ST               | In-Circuit Debugger and ICSP Programming Data      |  |  |

| RA0      | 2                            | 19            | 2                             | 27                    | I/O | ST               | PORTA Digital I/O                                  |  |  |

| RA1      | 3                            | 20            | 3                             | 28                    | I/O | ST               | -                                                  |  |  |

| RA2      | 7                            | 4             | 9                             | 6                     | I/O | ST               |                                                    |  |  |

| RA3      | 8                            | 5             | 10                            | 7                     | I/O | ST               |                                                    |  |  |

| RA4      | 10                           | 7             | 12                            | 9                     | I/O | ST               |                                                    |  |  |

| RA5      | 1                            | 18            | 1                             | 26                    | I/O | ST               |                                                    |  |  |

| RA6      | 14                           | 11            | 20                            | 17                    | I/O | ST               |                                                    |  |  |

| RA7      |                              | _             | 19                            | 16                    | I/O | ST               |                                                    |  |  |

| RB0      | 4                            | 1             | 4                             | 1                     | I/O | ST               | PORTB Digital I/O                                  |  |  |

| RB1      | 5                            | 2             | 5                             | 2                     | I/O | ST               |                                                    |  |  |

| RB2      | 6                            | 3             | 6                             | 3                     | I/O | ST               |                                                    |  |  |

| RB3      | _                            | _             | 7                             | 4                     | I/O | ST               |                                                    |  |  |

| RB4      | 9                            | 6             | 11                            | 8                     | I/O | ST               |                                                    |  |  |

| RB5      | _                            | _             | 14                            | 11                    | I/O | ST               |                                                    |  |  |

| RB6      |                              | _             | 15                            | 12                    | I/O | ST               |                                                    |  |  |

| RB7      | 11                           | 8             | 16                            | 13                    | I/O | ST               |                                                    |  |  |

| RB8      | 12                           | 9             | 17                            | 14                    | I/O | ST               |                                                    |  |  |

| RB9      | 13                           | 10            | 18                            | 15                    | I/O | ST               |                                                    |  |  |

| RB10     | _                            | _             | 21                            | 18                    | I/O | ST               | -                                                  |  |  |

| RB11     | _                            | _             | 22                            | 19                    | I/O | ST               | -                                                  |  |  |

| RB12     | 15                           | 12            | 23                            | 20                    | I/O | ST               |                                                    |  |  |

| RB13     | 16                           | 13            | 24                            | 21                    | I/O | ST               | -                                                  |  |  |

| RB14     | 17                           | 14            | 25                            | 22                    | I/O | ST               | -                                                  |  |  |

| RB15     | 18                           | 15            | 26                            | 23                    | I/O | ST               |                                                    |  |  |

| REFO     | 18                           | 15            | 26                            | 23                    | 0   | —                | Reference Clock Output                             |  |  |

| RTCC     | 17                           | 14            | 25                            | 22                    | 0   | —                | Real-Time Clock Alarm Output                       |  |  |

| SCK1     | 15                           | 12            | 22                            | 19                    | I/O | ST               | SPI1 Serial Clock Input/Output                     |  |  |

| SCL1     | 12                           | 9             | 17, 15 <sup>(1)</sup>         | 14, 12 <sup>(1)</sup> | I/O | l <sup>2</sup> C | I2C1 Synchronous Serial Clock Input/Output         |  |  |

| SDA1     | 13                           | 10            | 18, 14 <b>(1)</b>             | 15, 11 <sup>(1)</sup> | I/O | l <sup>2</sup> C | I2C1 Data Input/Output                             |  |  |

| SDI1     | 17                           | 14            | 21                            | 18                    | Ι   | ST               | SPI1 Serial Data Input                             |  |  |

| SDO1     | 16                           | 13            | 24                            | 21                    | 0   | —                | SPI1 Serial Data Output                            |  |  |

| SOSCI    | 9                            | 6             | 11                            | 8                     | Ι   | ANA              | Secondary Oscillator Input                         |  |  |

| SOSCO    | 10                           | 7             | 12                            | 9                     | 0   | ANA              | Secondary Oscillator Output                        |  |  |

| SS1      | 18                           | 15            | 26                            | 23                    | I/O | ST               | Slave Select Input/Frame Select Output (SPI1)      |  |  |

| TABLE 1-2: | PIC24F16KA102 FAMILY PINOUT DESCRIPTIONS (CONTINUED) |

|------------|------------------------------------------------------|

|            |                                                      |

**Legend:** ST = Schmitt Trigger input buffer, ANA = Analog level input/output,  $I^2C^{TM} = I^2C/SMB$ us input buffer

**Note 1:** Alternative multiplexing when the I2C1SEL Configuration bit is cleared.

### REGISTER 3-2: CORCON: CPU CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      |     |     |     | —   |     | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/C-0, HSC          | R/W-0 | U-0 | U-0   |

|-------|-----|-----|-----|---------------------|-------|-----|-------|

| _     | —   |     | —   | IPL3 <sup>(1)</sup> | PSV   | —   | —     |

| bit 7 |     |     |     |                     |       |     | bit 0 |

| Legend:           | HSC = Hardware Settable/Clearable bit |                                    |                    |  |  |  |  |

|-------------------|---------------------------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

| bit 15-4 | Unimplemented: Read as '0'                                                                                                    |

|----------|-------------------------------------------------------------------------------------------------------------------------------|

| bit 3    | IPL3: CPU Interrupt Priority Level Status bit <sup>(1)</sup>                                                                  |

|          | <ul> <li>1 = CPU interrupt priority level is greater than 7</li> <li>0 = CPU interrupt priority level is 7 or less</li> </ul> |

| bit 2    | <b>PSV:</b> Program Space Visibility in Data Space Enable bit                                                                 |

|          | 1 = Program space is visible in data space                                                                                    |

|          | 0 = Program space is not visible in data space                                                                                |

| bit 1-0  | Unimplemented: Read as '0'                                                                                                    |

**Note 1:** User interrupts are disabled when IPL3 = 1.

### 3.3 Arithmetic Logic Unit (ALU)

The PIC24F ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

The PIC24F CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware division for 16-bit divisor.

#### 3.3.1 MULTIPLIER

The ALU contains a high-speed, 17-bit x 17-bit multiplier. It supports unsigned, signed or mixed sign operation in several multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

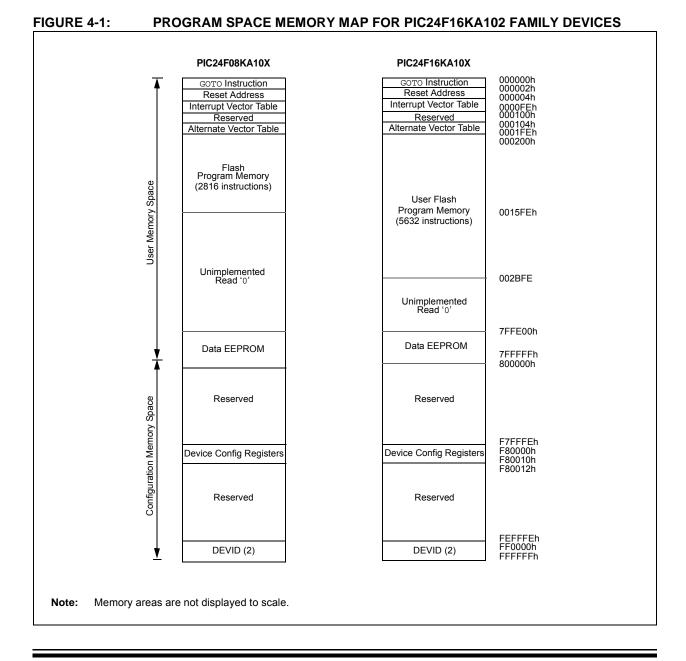

# 4.0 MEMORY ORGANIZATION

As with Harvard architecture devices, the PIC24F microcontrollers feature separate program and data memory space and busing. This architecture also allows the direct access of program memory from the data space during code execution.

### 4.1 **Program Address Space**

The program address memory space of the PIC24F devices is 4M instructions. The space is addressable by a 24-bit value derived from either the 23-bit Program Counter (PC) during program execution, or from a table operation or data space remapping, as described in **Section 4.3 "Interfacing Program and Data Memory Spaces"**.

The user access to the program memory space is restricted to the lower half of the address range (000000h to 7FFFFh). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

Memory maps for the PIC24F16KA102 family of devices are displayed in Figure 4-1.

| IADLL        | <b>-</b> -J. |        |                    |        |        |        |        |        |             |               |           |             |                |              |             |       |       |

|--------------|--------------|--------|--------------------|--------|--------|--------|--------|--------|-------------|---------------|-----------|-------------|----------------|--------------|-------------|-------|-------|

| File<br>Name | Addr         | Bit 15 | Bit 14             | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8       | Bit 7         | Bit 6     | Bit 5       | Bit 4          | Bit 3        | Bit 2       | Bit 1 | Bit 0 |

| WREG0        | 0000         |        | Working Register 0 |        |        |        |        |        |             |               |           |             |                |              |             |       |       |

| WREG1        | 0002         |        | Working Register 1 |        |        |        |        |        |             |               |           |             |                |              |             |       |       |

| WREG2        | 0004         |        | Working Register 2 |        |        |        |        |        |             |               |           |             |                |              |             |       |       |

| WREG3        | 0006         |        | Working Register 3 |        |        |        |        |        |             |               |           |             |                |              |             |       |       |

| WREG4        | 0008         |        |                    |        |        |        |        |        | Working I   | Register 4    |           |             |                |              |             |       |       |

| WREG5        | 000A         |        |                    |        |        |        |        |        | Working I   | Register 5    |           |             |                |              |             |       |       |

| WREG6        | 000C         |        |                    |        |        |        |        |        | Working I   | Register 6    |           |             |                |              |             |       |       |

| WREG7        | 000E         |        |                    |        |        |        |        |        | Working I   | Register 7    |           |             |                |              |             |       |       |

| WREG8        | 0010         |        | Working Register 8 |        |        |        |        |        |             |               |           |             |                |              |             |       |       |

| WREG9        | 0012         |        | Working Register 9 |        |        |        |        |        |             |               |           |             |                |              |             |       |       |

| WREG10       | 0014         |        |                    |        |        |        |        |        | Working F   | Register 10   |           |             |                |              |             |       |       |

| WREG11       | 0016         |        |                    |        |        |        |        |        | Working F   | Register 11   |           |             |                |              |             |       |       |

| WREG12       | 0018         |        |                    |        |        |        |        |        | Working F   | Register 12   |           |             |                |              |             |       |       |

| WREG13       | 001A         |        |                    |        |        |        |        |        | Working F   | Register 13   |           |             |                |              |             |       |       |

| WREG14       | 001C         |        |                    |        |        |        |        |        | Working F   | Register 14   |           |             |                |              |             |       |       |

| WREG15       | 001E         |        |                    |        |        |        |        |        | Working F   | Register 15   |           |             |                |              |             |       |       |

| SPLIM        | 0020         |        |                    |        |        |        |        | Stack  | Pointer Lin | nit Value Re  | egister   |             |                |              |             |       |       |

| PCL          | 002E         |        |                    |        |        |        |        | Progra | m Counter   | Low Byte R    | egister   |             |                |              |             |       |       |

| PCH          | 0030         | _      | _                  | _      | _      | _      | _      | _      | _           |               |           | Progra      | m Counter      | Register Hig | gh Byte     |       |       |

| TBLPAG       | 0032         | _      | _                  | _      | _      | _      | _      | _      | _           |               |           | Table M     | lemory Pag     | e Address F  | Register    |       |       |

| PSVPAG       | 0034         | —      | _                  | _      | _      | —      | —      | _      | —           |               | F         | Program Spa | ace Visibility | Page Addr    | ess Registe | er    |       |

| RCOUNT       | 0036         |        |                    |        |        |        |        | REP    | EAT Loop C  | Counter Reg   | jister    |             |                |              |             |       |       |

| SR           | 0042         | —      | —                  | _      | —      | —      | —      |        | DC          | IPL2          | IPL1      | IPL0        | RA             | N            | OV          | Z     | С     |

| CORCON       | 0044         | _      | _                  | _      | —      | —      | —      | _      | —           | _             | —         | _           | _              | IPL3         | PSV         | —     | —     |

| DISICNT      | 0052         | _      | _                  |        |        |        |        |        | Disab       | le Interrupts | Counter R | egister     |                |              |             |       |       |

|              |              |        |                    |        |        |        |        |        |             |               |           |             |                |              |             |       |       |

#### TABLE 4-3: **CPU CORE REGISTERS MAP**

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All

xxxx

#### 5.5.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of Flash program memory at a time by erasing the programmable row. The general process is:

- 1. Read a row of program memory (32 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase a row (see Example 5-1):

- a) Set the NVMOP bits (NVMCON<5:0>) to '011000' to configure for row erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the block to be erased into the TBLPAG and W registers.

- c) Write 55h to NVMKEY.

- d) Write AAh to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 32 instructions from data RAM into the program memory buffers (see Example 5-1).

- 5. Write the program block to Flash memory:

- a) Set the NVMOP bits to '000100' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 55h to NVMKEY.

- c) Write AAh to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as displayed in Example 5-5.

### EXAMPLE 5-1: ERASING A PROGRAM MEMORY ROW – ASSEMBLY LANGUAGE CODE

| : Sot up NUMCON for row orago operation |                                       |

|-----------------------------------------|---------------------------------------|

| ; Set up NVMCON for row erase operation |                                       |

| MOV #0x4058, W0                         | ;                                     |

| MOV W0, NVMCON                          | ; Initialize NVMCON                   |

| ; Init pointer to row to be ERASED      |                                       |

| MOV #tblpage(PROG_ADDR), W0             | i                                     |

| MOV W0, TBLPAG                          | ; Initialize PM Page Boundary SFR     |

| MOV #tbloffset(PROG_ADDR), W0           | ; Initialize in-page EA[15:0] pointer |

| TBLWTL W0, [W0]                         | ; Set base address of erase block     |

| DISI #5                                 | ; Block all interrupts                |

|                                         | for next 5 instructions               |

| MOV #0x55, W0                           |                                       |

| MOV W0, NVMKEY                          | ; Write the 55 key                    |

| MOV #0xAA, W1                           | ;                                     |

| MOV W1, NVMKEY                          | ; Write the AA key                    |

| BSET NVMCON, #WR                        | ; Start the erase sequence            |

| NOP                                     | ; Insert two NOPs after the erase     |

| NOP                                     | ; command is asserted                 |

|                                         |                                       |

### EXAMPLE 5-2: ERASING A PROGRAM MEMORY ROW – 'C' LANGUAGE CODE

| // C example using MPLAB C30                                   |                                                                        |

|----------------------------------------------------------------|------------------------------------------------------------------------|

| <pre>intattribute ((space(auto_psv))) progAddr = 0x1234;</pre> | // Variable located in Pgm Memory, declared as a<br>// global variable |

| unsigned int offset;                                           | ,, giobal variable                                                     |

| //Set up pointer to the first memory location to be written    |                                                                        |

| <pre>TBLPAG =builtin_tblpage(&amp;progAddr);</pre>             | // Initialize PM Page Boundary SFR                                     |

| <pre>offset =builtin_tbloffset(&amp;progAddr);</pre>           | // Initialize lower word of address                                    |

| <pre>builtin_tblwtl(offset, 0x0000);</pre>                     | // Set base address of erase block                                     |

|                                                                | // with dummy latch write                                              |

| NVMCON = $0 \times 4058;$                                      | // Initialize NVMCON                                                   |

| asm("DISI #5");                                                | // Block all interrupts for next 5 instructions                        |

| builtin_write_NVM();                                           | <pre>// C30 function to perform unlock // sequence and set WR</pre>    |

# 14.1 Input Capture Registers

### REGISTER 14-1: IC1CON: INPUT CAPTURE 1 CONTROL REGISTER

| R/W-0  | U-0     | U-0     | U-0   | U-0   | U-0   |

|--------|---------|---------|-------|-------|-------|

|        |         |         |       |       | -     |

| ICSIDE | —       | —       | —     | —     | —     |

|        |         |         |       |       | bit 8 |

|        |         |         |       |       |       |

| R/W-0  | R-0, HC | R-0, HC | R/W-0 | R/W-0 | R/W-0 |

| ICI0   | ICOV    | ICBNE   | ICM2  | ICM1  | ICM0  |

|        |         |         |       |       | bit C |

|        | -       |         |       |       |       |

| Legend:           | HC = Hardware Clearable bit |                                    |                    |  |  |  |  |

|-------------------|-----------------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                                                                                   |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | ICSIDL: Input Capture 1 Module Stop in Idle Control bit                                                                                                                                                                      |

|           | <ul> <li>1 = Input capture module will halt in CPU Idle mode</li> <li>0 = Input capture module will continue to operate in CPU Idle mode</li> </ul>                                                                          |

| bit 12-8  | Unimplemented: Read as '0'                                                                                                                                                                                                   |

| bit 7     | ICTMR: Input Capture 1 Timer Select bit                                                                                                                                                                                      |

|           | <ul> <li>1 = TMR2 contents are captured on capture event</li> <li>0 = TMR3 contents are captured on capture event</li> </ul>                                                                                                 |

| bit 6-5   | ICI<1:0>: Select Number of Captures per Interrupt bits                                                                                                                                                                       |

|           | 11 = Interrupt on every fourth capture event                                                                                                                                                                                 |

|           | 10 = Interrupt on every third capture event<br>01 = Interrupt on every second capture event                                                                                                                                  |

|           | 00 = Interrupt on every capture event                                                                                                                                                                                        |

| bit 4     | ICOV: Input Capture 1 Overflow Status Flag bit (read-only)                                                                                                                                                                   |

|           | 1 = Input capture overflow occurred                                                                                                                                                                                          |

|           | 0 = No input capture overflow occurred                                                                                                                                                                                       |

| bit 3     | ICBNE: Input Capture 1 Buffer Empty Status bit (read-only)                                                                                                                                                                   |

|           | <ul> <li>1 = Input capture buffer is not empty, at least one more capture value can be read</li> <li>0 = Input capture buffer is empty</li> </ul>                                                                            |

| bit 2-0   | ICM<2:0>: Input Capture 1 Mode Select bits                                                                                                                                                                                   |

|           | <ul> <li>111 = Input capture functions as interrupt pin only when device is in Sleep or Idle mode (rising edge detect only, all other control bits are not applicable)</li> <li>110 = Upward (module is disabled)</li> </ul> |

|           | <ul> <li>110 = Unused (module is disabled)</li> <li>101 = Capture mode, every 16th rising edge</li> </ul>                                                                                                                    |

|           | 100 = Capture mode, every 4th rising edge                                                                                                                                                                                    |

|           | 011 = Capture mode, every rising edge                                                                                                                                                                                        |

|           | 010 = Capture mode, every falling edge                                                                                                                                                                                       |

|           | 001 = Capture mode, every edge (rising and falling) – ICI<1:0> bits do not control interrupt generation<br>for this mode                                                                                                     |

|           | 000 = Input capture module is turned off                                                                                                                                                                                     |

|           |                                                                                                                                                                                                                              |

# 15.4 Output Compare Register

## REGISTER 15-1: OC1CON: OUTPUT COMPARE 1 CONTROL REGISTER

| U-0    | U-0 | R/W-0  | U-0     | U-0    | U-0   | U-0   | U-0   |

|--------|-----|--------|---------|--------|-------|-------|-------|

| —      | —   | OCSIDL | —       | —      | _     |       | —     |

| bit 15 |     |        |         |        |       |       | bit 8 |

|        |     |        |         |        |       |       |       |

| U-0    | U-0 | U-0    | R-0, HC | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

| —      | —   | —      | OCFLT   | OCTSEL | OCM2  | OCM1  | OCM0  |

| bit 7  |     |        |         |        |       |       | bit 0 |

| Legend:           | HC = Hardware Clearable bit |                            |                    |  |  |

|-------------------|-----------------------------|----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, rea | d as '0'           |  |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared       | x = Bit is unknown |  |  |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | OCSIDL: Stop Output Compare 1 in Idle Mode Control bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|           | <ul> <li>1 = Output Compare 1 will halt in CPU Idle mode</li> <li>0 = Output Compare 1 will continue to operate in CPU Idle mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 12-5  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| bit 4     | OCFLT: PWM Fault Condition Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|           | <ul> <li>1 = PWM Fault condition has occurred (cleared in HW only)</li> <li>0 = No PWM Fault condition has occurred (this bit is only used when OCM&lt;2:0&gt; = 111)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                               |

| bit 3     | OCTSEL: Output Compare 1 Timer Select bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|           | <ul> <li>1 = Timer3 is the clock source for Output Compare 1</li> <li>0 = Timer2 is the clock source for Output Compare 1</li> <li>Refer to the device data sheet for specific time bases available to the output compare module.</li> </ul>                                                                                                                                                                                                                                                                                                                   |

| bit 2-0   | OCM<2:0>: Output Compare 1 Mode Select bits<br>111 = PWM mode on OC1, Fault pin; OCF1 enabled <sup>(1)</sup><br>110 = PWM mode on OC1, Fault pin; OCF1 disabled <sup>(1)</sup><br>101 = Initialize OC1 pin low, generate continuous output pulses on OC1 pin<br>100 = Initialize OC1 pin low, generate single output pulse on OC1 pin<br>011 = Compare event toggles OC1 pin<br>010 = Initialize OC1 pin high, compare event forces OC1 pin low<br>001 = Initialize OC1 pin low, compare event forces OC1 pin high<br>000 = Output compare channel is disabled |

Note 1: The OCFA pin controls the OC1 channel.

# 18.2 Transmitting in 8-Bit Data Mode

- 1. Set up the UART:

- a) Write appropriate values for data, parity and Stop bits.

- b) Write appropriate baud rate value to the UxBRG register.

- c) Set up transmit and receive interrupt enable and priority bits.

- 2. Enable the UART.

- 3. Set the UTXEN bit (causes a transmit interrupt two cycles after being set).

- 4. Write data byte to lower byte of UxTXREG word. The value will be immediately transferred to the Transmit Shift Register (TSR) and the serial bit stream will start shifting out with the next rising edge of the baud clock.

- Alternately, the data byte may be transferred while UTXEN = 0, and then, the user may set UTXEN. This will cause the serial bit stream to begin immediately because the baud clock will start from a cleared state.

- 6. A transmit interrupt will be generated as per interrupt control bit, UTXISELx.

### 18.3 Transmitting in 9-Bit Data Mode

- 1. Set up the UART (as described in **Section 18.2** "**Transmitting in 8-Bit Data Mode**").

- 2. Enable the UART.

- 3. Set the UTXEN bit (causes a transmit interrupt two cycles after being set).

- 4. Write UxTXREG as a 16-bit value only.

- 5. A word write to UxTXREG triggers the transfer of the 9-bit data to the TSR. The serial bit stream will start shifting out with the first rising edge of the baud clock.

- 6. A transmit interrupt will be generated as per the setting of control bit, UTXISELx.

# 18.4 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an auto-baud Sync byte.

- 1. Configure the UART for the desired mode.

- 2. Set UTXEN and UTXBRK sets up the Break character.

- 3. Load the UxTXREG with a dummy character to initiate transmission (value is ignored).

- 4. Write '55h' to UxTXREG loads the Sync character into the transmit FIFO.

- 5. After the Break has been sent, the UTXBRK bit is reset by hardware. The Sync character now transmits.

### 18.5 Receiving in 8-Bit or 9-Bit Data Mode

- 1. Set up the UART (as described in Section 18.2 "Transmitting in 8-Bit Data Mode").

- 2. Enable the UART.

- 3. A receive interrupt will be generated when one or more data characters have been received, as per interrupt control bit, URXISELx.

- 4. Read the OERR bit to determine if an overrun error has occurred. The OERR bit must be reset in software.

- 5. Read UxRXREG.

The act of reading the UxRXREG character will move the next character to the top of the receive FIFO, including a new set of PERR and FERR values.

## 18.6 Operation of UxCTS and UxRTS Control Pins

UARTx Clear to Send (UxCTS) and Request to Send (UxRTS) are the two hardware-controlled pins that are associated with the UART module. These two pins allow the UART to operate in Simplex and Flow Control modes. They are implemented to control the transmission and reception between the Data Terminal Equipment (DTE). The UEN<1:0> bits in the UxMODE register configure these pins.

# 18.7 Infrared Support

The UART module provides two types of infrared UART support: one is the IrDA clock output to support an external IrDA encoder and decoder device (legacy module support), and the other is the full implementation of the IrDA encoder and decoder.

As the IrDA modes require a 16x baud clock, they will only work when the BRGH bit (UxMODE<3>) is '0'.

#### 18.7.1 EXTERNAL IrDA SUPPORT – IrDA CLOCK OUTPUT

To support external IrDA encoder and decoder devices, the UxBCLK pin (same as the UxRTS pin) can be configured to generate the 16x baud clock. When UEN<1:0> = 11, the UxBCLK pin will output the 16x baud clock if the UART module is enabled; it can be used to support the IrDA codec chip.

# 18.7.2 BUILT-IN IrDA ENCODER AND DECODER

The UART has full implementation of the IrDA encoder and decoder as part of the UART module. The built-in IrDA encoder and decoder functionality is enabled using the IREN bit (UxMODE<12>). When enabled (IREN = 1), the receive pin (UxRX) acts as the input from the infrared receiver. The transmit pin (UxTX) acts as the output to the infrared transmitter.

### REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

| R/W-0    | R/W-0  | R/W-0    | U-0 | R/W-0, HC | R/W-0 | R-0, HSC | R-1, HSC |

|----------|--------|----------|-----|-----------|-------|----------|----------|

| UTXISEL1 | UTXINV | UTXISEL0 | —   | UTXBRK    | UTXEN | UTXBF    | TRMT     |

| bit 15   |        |          |     |           |       |          | bit 8    |

| R/W-0    | R/W-0    | R/W-0 | R-1, HSC | R-0, HSC | R-0, HSC | R/C-0, HS | R-0, HSC |

|----------|----------|-------|----------|----------|----------|-----------|----------|

| URXISEL1 | URXISEL0 | ADDEN | RIDLE    | PERR     | FERR     | OERR      | URXDA    |

| bit 7    |          |       |          |          |          |           | bit 0    |

| Legend:           | HC = Hardware Clearable bit |                             |                    |  |  |

|-------------------|-----------------------------|-----------------------------|--------------------|--|--|

| C = Clearable bit | HS = Hardware Settable bit  | HSC = Hardware Settable/C   | Clearable bit      |  |  |

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read | d as '0'           |  |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared        | x = Bit is unknown |  |  |

bit 15,13 UTXISEL<1:0>: Transmission Interrupt Mode Selection bits

- 11 = Reserved; do not use

- 10 = Interrupt when a character is transferred to the Transmit Shift Register (TSR), and as a result, the transmit buffer becomes empty

- 01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all transmit operations are completed

- 00 = Interrupt when a character is transferred to the Transmit Shift Register (this implies there is at least one character open in the transmit buffer)

bit 14 UTXINV: IrDA<sup>®</sup> Encoder Transmit Polarity Inversion bit

|         | <b>UTAINV.</b> II DA Encoder Hanshit Folanty Inversion bit                                                                                                                                                                                                                                                                                                 |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <u>If IREN = 0:</u>                                                                                                                                                                                                                                                                                                                                        |

|         | 1 = UxTX Idle '0'                                                                                                                                                                                                                                                                                                                                          |

|         | 0 = UxTX Idle '1'                                                                                                                                                                                                                                                                                                                                          |

|         | If IREN = 1:                                                                                                                                                                                                                                                                                                                                               |

|         | 1 = UxTX Idle '1'                                                                                                                                                                                                                                                                                                                                          |

|         | 0 = UxTX Idle '0'                                                                                                                                                                                                                                                                                                                                          |

| bit 12  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                 |

| bit 11  | UTXBRK: Transmit Break bit                                                                                                                                                                                                                                                                                                                                 |

|         | 1 = Send Sync Break on next transmission – Start bit, followed by twelve '0' bits, followed by Stop bit;<br>cleared by hardware upon completion                                                                                                                                                                                                            |

|         | 0 = Sync Break transmission is disabled or completed                                                                                                                                                                                                                                                                                                       |

| bit 10  | UTXEN: Transmit Enable bit                                                                                                                                                                                                                                                                                                                                 |

|         | 1 = Transmit is enabled, UxTX pin is controlled by UARTx                                                                                                                                                                                                                                                                                                   |

|         | 0 = Transmit is disabled, any pending transmission is aborted and buffer is reset. UxTX pin is controlled<br>by the PORT register.                                                                                                                                                                                                                         |

| bit 9   | UTXBF: Transmit Buffer Full Status bit (read-only)                                                                                                                                                                                                                                                                                                         |

|         | 1 = Transmit buffer is full                                                                                                                                                                                                                                                                                                                                |

|         | 0 = Transmit buffer is not full, at least one more character can be written                                                                                                                                                                                                                                                                                |

| bit 8   | TRMT: Transmit Shift Register Empty bit (read-only)                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = Transmit Shift Register is empty and transmit buffer is empty (the last transmission has completed)</li> <li>0 = Transmit Shift Register is not empty, a transmission is in progress or queued</li> </ul>                                                                                                                                     |

| bit 7-6 | URXISEL<1:0>: Receive Interrupt Mode Selection bits                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>11 = Interrupt is set on RSR transfer, making the receive buffer full (i.e., has 4 data characters)</li> <li>10 = Interrupt is set on RSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)</li> <li>0x = Interrupt is set when any character is received and transferred from the RSR to the receive buffer;</li> </ul> |

|         | reachus huffer has ann ar mars sharestare                                                                                                                                                                                                                                                                                                                  |

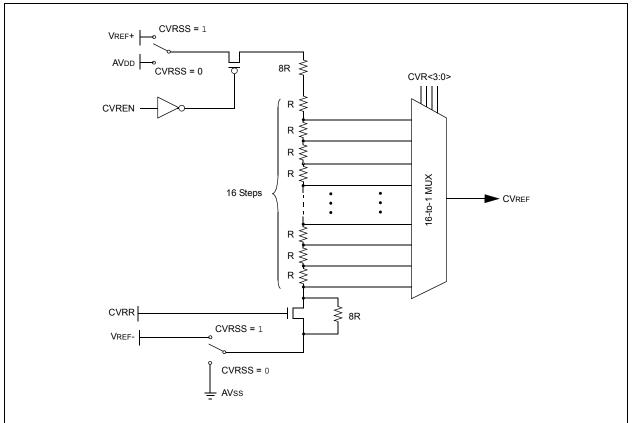

# 24.0 COMPARATOR VOLTAGE REFERENCE

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Comparator Voltage Reference, refer to the "PIC24F Family Reference Manual", Section 20. "Comparator Voltage Reference Module" (DS39709).

## 24.1 Configuring the Comparator Voltage Reference

The comparator voltage reference module is controlled through the CVRCON register (Register 24-1). The comparator voltage reference provides two ranges of output voltage, each with 16 distinct levels. The range to be used is selected by the CVRR bit (CVRCON<5>). The primary difference between the ranges is the size of the steps selected by the CVREF Selection bits (CVR<3:0>), with one range offering finer resolution.

The comparator reference supply voltage can come from either VDD and VSS, or the external VREF+ and VREF-. The voltage source is selected by the CVRSS bit (CVRCON<4>).

The settling time of the comparator voltage reference must be considered when changing the CVREF output.

### FIGURE 24-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

| U-0                            | U-0 | U-0           | U-0 | U-0          | U-0             | R/C-1    | R/C-1 |

|--------------------------------|-----|---------------|-----|--------------|-----------------|----------|-------|

| —                              | —   |               | —   | —            |                 | GSS0     | GWRP  |

| bit 7                          | •   |               | •   |              |                 | •        | bit 0 |

|                                |     |               |     |              |                 |          |       |

|                                |     |               |     |              |                 |          |       |

| Legend:                        |     |               |     |              |                 |          |       |

| <b>Legend:</b><br>R = Readable | bit | C = Clearable | bit | U = Unimplem | ented bit, read | l as '0' |       |

| bit 7-2 | Unimplemented: Read as '0'                                                                          |

|---------|-----------------------------------------------------------------------------------------------------|

| bit 1   | GSS0: General Segment Code Flash Code Protection bit                                                |

|         | <ul><li>1 = No protection</li><li>0 = Standard security is enabled</li></ul>                        |

| bit 0   | GWRP: General Segment Code Flash Write Protection bit                                               |

|         | <ul><li>1 = General segment may be written</li><li>0 = General segment is write-protected</li></ul> |

**REGISTER 26-2: FGS: GENERAL SEGMENT CONFIGURATION REGISTER**

### REGISTER 26-3: FOSCSEL: OSCILLATOR SELECTION CONFIGURATION REGISTER

| R/P-1 | U-0 | U-0 | U-0 | U-0 | R/P-1  | R/P-1  | R/P-1  |

|-------|-----|-----|-----|-----|--------|--------|--------|

| IESO  | —   | —   | —   | —   | FNOSC2 | FNOSC1 | FNOSC0 |

| bit 7 |     |     |     |     |        |        | bit 0  |

| Legend:           |                      |                             |                    |

|-------------------|----------------------|-----------------------------|--------------------|

| R = Readable bit  | P = Programmable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | <b>IESO:</b> Internal External Switchover bit<br>1 = Internal External Switchover mode is enabled (Two-Speed Start-up is enabled)<br>0 = Internal External Switchover mode is disabled (Two-Speed Start-up is disabled)                                                                                                                                                                                                                                                                 |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-3 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| bit 2-0 | FNOSC<2:0>: Oscillator Selection bits                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | <ul> <li>000 = Fast RC Oscillator (FRC)</li> <li>001 = Fast RC Oscillator with divide-by-N with PLL module (FRCDIV+PLL)</li> <li>010 = Primary Oscillator (XT, HS, EC)</li> <li>011 = Primary Oscillator with PLL module (HS+PLL, EC+PLL)</li> <li>100 = Secondary Oscillator (SOSC)</li> <li>101 = Low-Power RC Oscillator (LPRC)</li> <li>110 = 500 kHz Low-Power FRC Oscillator with divide-by-N (LPFRCDIV)</li> <li>111 = 8 MHz FRC Oscillator with divide-by-N (FRCDIV)</li> </ul> |

# 27.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C<sup>®</sup> for Various Device Families

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers

- MPLAB ICD 3

- PICkit™ 3 Debug Express

- Device Programmers

- PICkit<sup>™</sup> 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

### 27.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- · High-level source code debugging

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- · Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

# 28.0 INSTRUCTION SET SUMMARY

| Note: | This chapter is a brief summary of the     |  |  |  |

|-------|--------------------------------------------|--|--|--|

|       | PIC24F instruction set architecture and is |  |  |  |

|       | not intended to be a comprehensive         |  |  |  |

|       | reference source.                          |  |  |  |

The PIC24F instruction set adds many enhancements to the previous PIC<sup>®</sup> MCU instruction sets, while maintaining an easy migration from previous PIC MCU instruction sets. Most instructions are a single program memory word. Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction. The instruction set is highly orthogonal and is grouped into four basic categories:

- Word or byte-oriented operations

- Bit-oriented operations

- · Literal operations

- Control operations

Table 28-1 lists the general symbols used in describing the instructions. The PIC24F instruction set summary in Table 28-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- · The file register, specified by the value, 'f'

- The destination, which could either be the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement may use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by the value of 'k')

- The W register or file register, where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The control instructions may use some of the following operands:

- · A program memory address

- The mode of the table read and table write instructions

All instructions are a single word, except for certain double-word instructions, which were made double-word instructions so that all of the required information is available in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the Program Counter (PC) is changed as a result of the instruction. In these cases, the execution takes two instruction cycles, with the additional instruction cycle(s) executed as a NOP. Notable exceptions are the BRA (unconditional/computed branch), indirect CALL/GOTO, all table reads and writes, and RETURN/RETFIE instructions, which are single-word instructions but take two or three cycles.

Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles. The double-word instructions execute in two instruction cycles.

#### TABLE 29-3: DC CHARACTERISTICS: TEMPERATURE AND VOLTAGE SPECIFICATIONS

| Param<br>No. | Symbol | Characteristic                                                      | Min  | Typ <sup>(1)</sup> | Max | Units | Conditions                        |

|--------------|--------|---------------------------------------------------------------------|------|--------------------|-----|-------|-----------------------------------|

| DC10         | Vdd    | Supply Voltage                                                      | 1.8  | _                  | 3.6 | V     |                                   |

| DC12         | Vdr    | RAM Data Retention<br>Voltage <sup>(2)</sup>                        | 1.5  | _                  | _   | V     |                                   |

| DC16         | Vpor   | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal    | Vss  | —                  | 0.7 | V     |                                   |

| DC17         | Svdd   | <b>VDD Rise Rate</b><br>to Ensure Internal<br>Power-on Reset Signal | 0.05 | _                  |     | V/ms  | 0-3.3V in 0.1s<br>0-2.5V in 60 ms |

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: This is the limit to which VDD can be lowered without losing RAM data.

### TABLE 29-4: HIGH/LOW–VOLTAGE DETECT CHARACTERISTICS

## Standard Operating Conditions (unless otherwise stated)

Operating temperature  $-40^{\circ}C \le TA \le +85^{\circ}C$  for industrial

$-40^{\circ}C \le TA \le +125^{\circ}C$  for Extended

| Param<br>No. | Symbol | Charact             | eristic           | Min  | Тур  | Max  | Units | Conditions |

|--------------|--------|---------------------|-------------------|------|------|------|-------|------------|

| DC18         | Vhlvd  | HLVD Voltage on VDD | HLVDL<3:0> = 0000 | _    | 1.85 | 1.94 | V     |            |

|              |        | Transition          | HLVDL<3:0> = 0001 | 1.81 | 1.90 | 2.00 | V     |            |

|              |        |                     | HLVDL<3:0> = 0010 | 1.85 | 1.95 | 2.05 | V     |            |

|              |        |                     | HLVDL<3:0> = 0011 | 1.90 | 2.00 | 2.10 | V     |            |

|              |        |                     | HLVDL<3:0> = 0100 | 1.95 | 2.05 | 2.15 | V     |            |

|              |        |                     | HLVDL<3:0> = 0101 | 2.06 | 2.17 | 2.28 | V     |            |

|              |        |                     | HLVDL<3:0> = 0110 | 2.12 | 2.23 | 2.34 | V     |            |

|              |        |                     | HLVDL<3:0> = 0111 | 2.24 | 2.36 | 2.48 | V     |            |

|              |        |                     | HLVDL<3:0> = 1000 | 2.31 | 2.43 | 2.55 | V     |            |

|              |        |                     | HLVDL<3:0> = 1001 | 2.47 | 2.60 | 2.73 | V     |            |

|              |        |                     | HLVDL<3:0> = 1010 | 2.64 | 2.78 | 2.92 | V     |            |

|              |        |                     | HLVDL<3:0> = 1011 | 2.74 | 2.88 | 3.02 | V     |            |

|              |        |                     | HLVDL<3:0> = 1100 | 2.85 | 3.00 | 3.15 | V     |            |

|              |        |                     | HLVDL<3:0> = 1101 | 2.96 | 3.12 | 3.28 | V     |            |

|              |        |                     | HLVDL<3:0> = 1110 | 3.22 | 3.39 | 3.56 | V     |            |

### 30.2 Package Details

The following sections give the technical details of the packages.

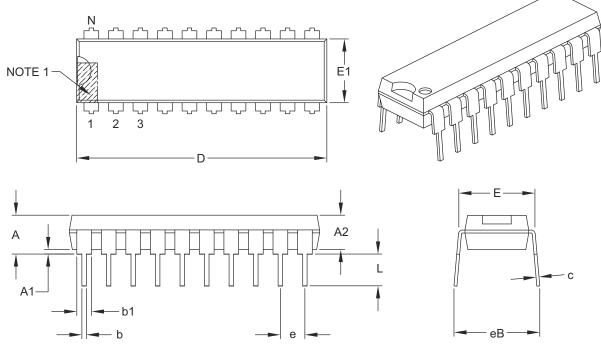

### 20-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units      |          |       | INCHES |  |  |

|----------------------------|------------|----------|-------|--------|--|--|

| Dimens                     | ion Limits | MIN      | NOM   | MAX    |  |  |

| Number of Pins             | Ν          |          | 20    |        |  |  |

| Pitch                      | е          | .100 BSC |       |        |  |  |

| Top to Seating Plane       | Α          | -        | -     | .210   |  |  |

| Molded Package Thickness   | A2         | .115     | .130  | .195   |  |  |

| Base to Seating Plane      | A1         | .015     | -     | -      |  |  |

| Shoulder to Shoulder Width | E          | .300     | .310  | .325   |  |  |

| Molded Package Width       | E1         | .240     | .250  | .280   |  |  |

| Overall Length             | D          | .980     | 1.030 | 1.060  |  |  |

| Tip to Seating Plane       | L          | .115     | .130  | .150   |  |  |

| Lead Thickness             | С          | .008     | .010  | .015   |  |  |

| Upper Lead Width           | b1         | .045     | .060  | .070   |  |  |

| Lower Lead Width           | b          | .014     | .018  | .022   |  |  |

| Overall Row Spacing §      | eB         | _        | -     | .430   |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-019B

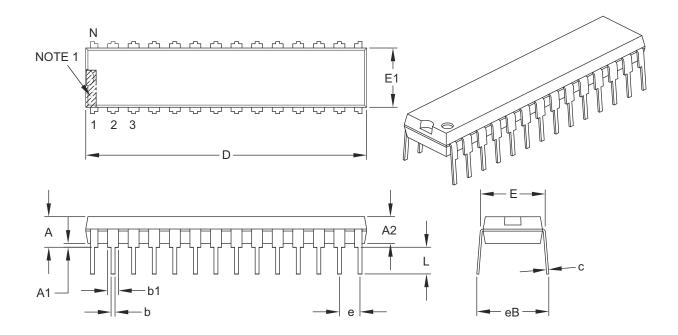

# 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | INCHES   |       |          |       |  |

|----------------------------|----------|-------|----------|-------|--|

| Dimensic                   | n Limits | MIN   | NOM      | MAX   |  |

| Number of Pins             | Ν        |       | 28       |       |  |

| Pitch                      | Pitch e  |       | .100 BSC |       |  |

| Top to Seating Plane       | Α        | -     | -        | .200  |  |

| Molded Package Thickness   | A2       | .120  | .135     | .150  |  |

| Base to Seating Plane      | A1       | .015  | -        | -     |  |

| Shoulder to Shoulder Width | Е        | .290  | .310     | .335  |  |

| Molded Package Width       | E1       | .240  | .285     | .295  |  |

| Overall Length             | D        | 1.345 | 1.365    | 1.400 |  |

| Tip to Seating Plane       | L        | .110  | .130     | .150  |  |

| Lead Thickness             | С        | .008  | .010     | .015  |  |

| Upper Lead Width           | b1       | .040  | .050     | .070  |  |

| Lower Lead Width           | b        | .014  | .018     | .022  |  |

| Overall Row Spacing §      | eB       | _     | -        | .430  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

### Μ

| Microchip Internet Web Site                                                              |     |

|------------------------------------------------------------------------------------------|-----|

| MPLAB ASM30 Assembler, Linker, Librarian                                                 | 204 |

| MPLAB Integrated Development                                                             |     |