Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 24                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1.5K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 9x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 28-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f16ka102t-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.4 Voltage Regulator Pin (VCAP)

| Note: | This section applies only to PIC24F K      |

|-------|--------------------------------------------|

|       | devices with an on-chip voltage regulator. |

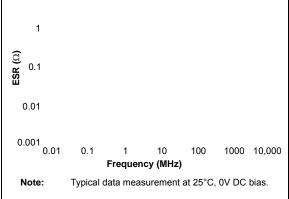

Some of the PIC24F K devices have an internal voltage regulator. These devices have the voltage regulator output brought out on the VCAP pin. On the PIC24F K devices with regulators, a low-ESR (< 5 $\Omega$ ) capacitor is required on the VCAP pin to stabilize the voltage regulator output. The VCAP pin must not be connected to VDD and must use a capacitor of 10  $\mu$ F connected to ground. The type can be ceramic or tantalum. Suitable examples of capacitors are shown in Table 2-1. Capacitors with equivalent specifications can be used.

Designers may use Figure 2-3 to evaluate ESR equivalence of candidate devices.

The placement of this capacitor should be close to VCAP. It is recommended that the trace length not exceed 0.25 inch (6 mm). Refer to **Section 29.0** "**Electrical Characteristics**" for additional information. Refer to **Section 29.0 "Electrical Characteristics"** for information on VDD and VDDCORE.

# FIGURE 2-3: FREQUENCY vs. ESR PERFORMANCE FOR SUGGESTED VCAP

### TABLE 2-1: SUITABLE CAPACITOR EQUIVALENTS

| Make      | Part #             | Nominal<br>Capacitance | Base Tolerance | Rated Voltage | Temp. Range  |

|-----------|--------------------|------------------------|----------------|---------------|--------------|

| TDK       | C3216X7R1C106K     | 10 µF                  | ±10%           | 16V           | -55 to 125°C |

| TDK       | C3216X5R1C106K     | 10 µF                  | ±10%           | 16V           | -55 to 85°C  |

| Panasonic | ECJ-3YX1C106K      | 10 µF                  | ±10%           | 16V           | -55 to 125°C |

| Panasonic | ECJ-4YB1C106K      | 10 µF                  | ±10%           | 16V           | -55 to 85°C  |

| Murata    | GRM32DR71C106KA01L | 10 µF                  | ±10%           | 16V           | -55 to 125°C |

| Murata    | GRM31CR61C106KC31L | 10 µF                  | ±10%           | 16V           | -55 to 85°C  |

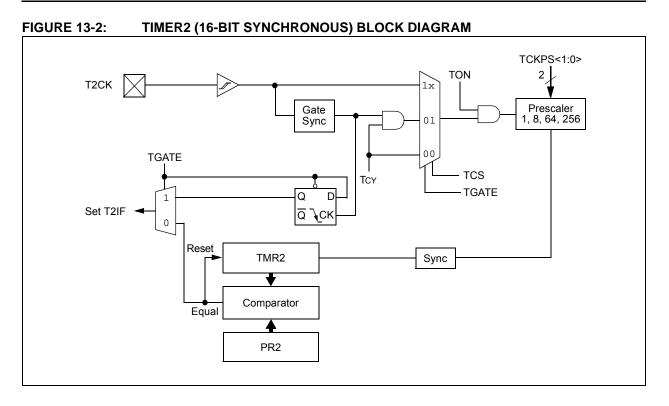

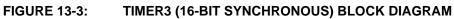

| TABLE 4-6: | TIMER REGISTER MAP |

|------------|--------------------|

|            |                    |

|           | -    |                          |                                                            |        |        |        |        |       |            |             |       |        |        |       |       |       |       |               |

|-----------|------|--------------------------|------------------------------------------------------------|--------|--------|--------|--------|-------|------------|-------------|-------|--------|--------|-------|-------|-------|-------|---------------|

| File Name | Addr | Bit 15                   | Bit 14                                                     | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8      | Bit 7       | Bit 6 | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1      | 0100 |                          |                                                            |        |        |        |        |       | Timer1     | Register    |       |        |        |       |       |       |       | 0000          |

| PR1       | 0102 |                          |                                                            |        |        |        |        |       | Timer1 Per | iod Registe | r     |        |        |       |       |       |       | FFFF          |

| T1CON     | 0104 | TON                      | _                                                          | TSIDL  | _      | _      | _      | _     | _          | _           | TGATE | TCKPS1 | TCKPS0 | _     | TSYNC | TCS   | _     | 0000          |

| TMR2      | 0106 |                          | Timer2 Register                                            |        |        |        |        |       |            |             | 0000  |        |        |       |       |       |       |               |

| TMR3HLD   | 0108 |                          | Timer3 Holding Register (for 32-bit timer operations only) |        |        |        |        |       |            |             | 0000  |        |        |       |       |       |       |               |

| TMR3      | 010A |                          |                                                            |        |        |        |        |       | Timer3     | Register    |       |        |        |       |       |       |       | 0000          |

| PR2       | 010C |                          |                                                            |        |        |        |        |       | Timer2 Per | iod Registe | r     |        |        |       |       |       |       | FFFF          |

| PR3       | 010E | Timer3 Period Register F |                                                            |        |        |        |        |       | FFFF       |             |       |        |        |       |       |       |       |               |

| T2CON     | 0110 | TON                      | _                                                          | TSIDL  | _      | _      | _      | _     | _          |             | TGATE | TCKPS1 | TCKPS0 | T32   | _     | TCS   | _     | 0000          |

| T3CON     | 0112 | TON                      | _                                                          | TSIDL  | _      | —      | —      | _     | _          | _           | TGATE | TCKPS1 | TCKPS0 | —     |       | TCS   | _     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-7: INPUT CAPTURE REGISTER MAP

| File<br>Name | Addr | Bit 15                   | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------------------------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| IC1BUF       | 0140 | Input Capture 1 Register |        |        |        |        |        |       |       | FFFF  |       |       |       |       |       |       |       |               |

| IC1CON       | 0142 |                          | —      | ICSIDL |        |        |        | -     |       | ICTMR | ICI1  | ICI0  | ICOV  | ICBNE | ICM2  | ICM1  | ICM0  | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-8: OUTPUT COMPARE REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14                              | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|-------------------------------------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|--------|-------|-------|-------|---------------|

| OC1RS        | 0180 |        | Output Compare 1 Secondary Register |        |        |        |        |       |       |       |       | FFFF  |       |        |       |       |       |               |

| OC1R         | 0182 |        | Output Compare 1 Register           |        |        |        |        |       |       |       | FFFF  |       |       |        |       |       |       |               |

| OC1CON       | 0184 | _      | _                                   | OCSIDL |        |        | _      |       | _     | —     | —     |       | OCFLT | OCTSEL | OCM2  | OCM1  | OCM0  | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

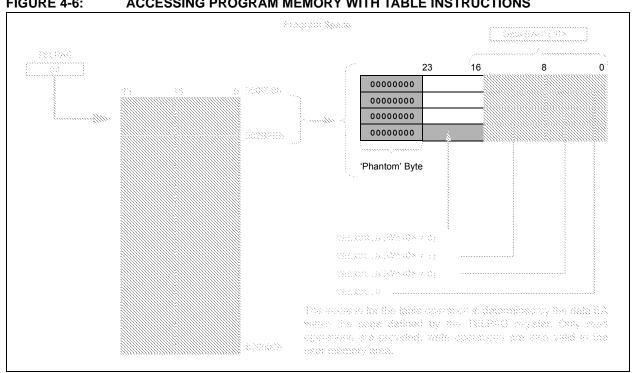

#### DATA ACCESS FROM PROGRAM 4.3.2 MEMORY AND DATA EEPROM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program memory without going through data space. It also offers a direct method of reading or writing a word of any address within data EEPROM memory. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

Note: The TBLRDH and TBLWTH instructions are not used while accessing data EEPROM memory.

The PC is incremented by 2 for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit, word-wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word, and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

1. TBLRDL (Table Read Low): In Word mode, it maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>). In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when byte select is '1'; the lower byte is selected when it is '0'.

2. TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom' byte, will always be '0'.

In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (byte select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in Section 5.0 "Flash Program Memory".

For all table operations, the area of program memory space to be accessed is determined by the Table Memory Page Address register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

Note: Only table read operations will execute in the configuration memory space, and only then, in implemented areas, such as the Device ID. Table write operations are not allowed.

FIGURE 4-6: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

#### 4.3.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

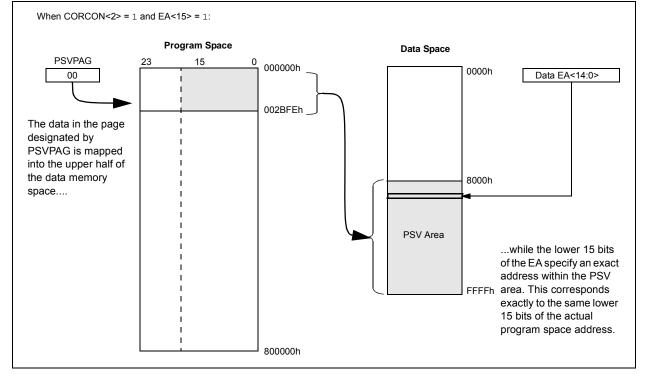

The upper 32 Kbytes of data space may optionally be mapped into an 8K word page (in PIC24F08KA1XX devices) and a 16K word page (in PIC24F16KA1XX devices) of the program space. This provides transparent access of stored constant data from the data space without the need to use special instructions (i.e., TBLRDL/H).

Program space access through the data space occurs if the MSb of the data space, EA, is '1', and PSV is enabled by setting the PSV bit in the CPU Control (CORCON<2>) register. The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page Address register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits.

By incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads from this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address, 8000h and higher, maps directly into a corresponding program memory address (see Figure 4-7), only the lower 16 bits of the 24-bit program word are used to contain the data. The upper 8 bits of any program space locations used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

| Note: | PSV access is temporarily disabled during |

|-------|-------------------------------------------|

|       | table reads/writes.                       |

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV.D instructions will require one instruction cycle in addition to the specified execution time. All other instructions will require two instruction cycles in addition to the specified execution time.

For operations that use PSV, which are executed inside a REPEAT loop, there will be some instances that require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction accessing data, using PSV, to execute in a single cycle.

### FIGURE 4-7: PROGRAM SPACE VISIBILITY OPERATION

#### 5.5.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of Flash program memory at a time by erasing the programmable row. The general process is:

- 1. Read a row of program memory (32 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase a row (see Example 5-1):

- a) Set the NVMOP bits (NVMCON<5:0>) to '011000' to configure for row erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the block to be erased into the TBLPAG and W registers.

- c) Write 55h to NVMKEY.

- d) Write AAh to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 32 instructions from data RAM into the program memory buffers (see Example 5-1).

- 5. Write the program block to Flash memory:

- a) Set the NVMOP bits to '000100' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 55h to NVMKEY.

- c) Write AAh to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as displayed in Example 5-5.

### EXAMPLE 5-1: ERASING A PROGRAM MEMORY ROW – ASSEMBLY LANGUAGE CODE

| : Sot up NUMCON for row orago operation |                                       |

|-----------------------------------------|---------------------------------------|

| ; Set up NVMCON for row erase operation |                                       |

| MOV #0x4058, W0                         | ;                                     |

| MOV W0, NVMCON                          | ; Initialize NVMCON                   |

| ; Init pointer to row to be ERASED      |                                       |

| MOV #tblpage(PROG_ADDR), W0             | i                                     |

| MOV W0, TBLPAG                          | ; Initialize PM Page Boundary SFR     |

| MOV #tbloffset(PROG_ADDR), W0           | ; Initialize in-page EA[15:0] pointer |

| TBLWTL W0, [W0]                         | ; Set base address of erase block     |

| DISI #5                                 | ; Block all interrupts                |

|                                         | for next 5 instructions               |

| MOV #0x55, W0                           |                                       |

| MOV W0, NVMKEY                          | ; Write the 55 key                    |

| MOV #0xAA, W1                           | ;                                     |

| MOV W1, NVMKEY                          | ; Write the AA key                    |

| BSET NVMCON, #WR                        | ; Start the erase sequence            |

| NOP                                     | ; Insert two NOPs after the erase     |

| NOP                                     | ; command is asserted                 |

|                                         |                                       |

### EXAMPLE 5-2: ERASING A PROGRAM MEMORY ROW – 'C' LANGUAGE CODE

| // C example using MPLAB C30                                   |                                                                        |

|----------------------------------------------------------------|------------------------------------------------------------------------|

| <pre>intattribute ((space(auto_psv))) progAddr = 0x1234;</pre> | // Variable located in Pgm Memory, declared as a<br>// global variable |

| unsigned int offset;                                           | ,, giobal variable                                                     |

| //Set up pointer to the first memory location to be written    |                                                                        |

| <pre>TBLPAG =builtin_tblpage(&amp;progAddr);</pre>             | // Initialize PM Page Boundary SFR                                     |

| <pre>offset =builtin_tbloffset(&amp;progAddr);</pre>           | // Initialize lower word of address                                    |

| <pre>builtin_tblwtl(offset, 0x0000);</pre>                     | // Set base address of erase block                                     |

|                                                                | // with dummy latch write                                              |

| NVMCON = $0 \times 4058;$                                      | // Initialize NVMCON                                                   |

| asm("DISI #5");                                                | // Block all interrupts for next 5 instructions                        |

| builtin_write_NVM();                                           | <pre>// C30 function to perform unlock // sequence and set WR</pre>    |

### 7.2.1 POR AND LONG OSCILLATOR START-UP TIMES

The oscillator start-up circuitry and its associated delay timers are not linked to the device Reset delays that occur at power-up. Some crystal circuits (especially low-frequency crystals) will have a relatively long start-up time. Therefore, one or more of the following conditions is possible after SYSRST is released:

- The oscillator circuit has not begun to oscillate.

- The Oscillator Start-up Timer (OST) has not expired (if a crystal oscillator is used).

- The PLL has not achieved a lock (if PLL is used).

The device will not begin to execute code until a valid clock source has been released to the system. Therefore, the oscillator and PLL start-up delays must be considered when the Reset delay time must be known.

### 7.2.2 FAIL-SAFE CLOCK MONITOR (FSCM) AND DEVICE RESETS

If the FSCM is enabled, it will begin to monitor the system clock source when SYSRST is released. If a valid clock source is not available at this time, the device will automatically switch to the FRC oscillator and the user can switch to the desired crystal oscillator in the Trap Service Routine (TSR).

### 7.3 Special Function Register Reset States

Most of the Special Function Registers (SFRs) associated with the PIC24F CPU and peripherals are reset to a particular value at a device Reset. The SFRs are grouped by their peripheral or CPU function and their Reset values are specified in each section of this manual.

The Reset value for each SFR does not depend on the type of Reset with the exception of four registers. The Reset value for the Reset Control register, RCON, will depend on the type of device Reset. The Reset value for the Oscillator Control register, OSCCON, will depend on the type of Reset and the programmed values of the FNOSC bits in the Flash Configuration Word (FOSCSEL); see Table 7-2. The RCFGCAL and NVMCON registers are only affected by a POR.

### 7.4 Deep Sleep BOR (DSBOR)

Deep Sleep BOR is a very low-power BOR circuitry, used when the device is in Deep Sleep mode. Due to low-current consumption, accuracy may vary.

The DSBOR trip point is around 2.0V. DSBOR is enabled by configuring DSBOREN (FDS<6>) = 1. DSBOREN will re-arm the POR to ensure the device will reset if VDD drops below the POR threshold.

### 7.5 Brown-out Reset (BOR)

The PIC24F16KA102 family devices implement a BOR circuit, which provides the user several configuration and power-saving options. The BOR is controlled by the BORV<1:0> and BOREN<1:0> Configuration bits (FPOR<6:5,1:0>). There are a total of four BOR configurations, which are provided in Table 7-3.

The BOR threshold is set by the BORV<1:0> bits. If BOR is enabled (any values of BOREN<1:0>, except '00'), any drop of VDD below the set threshold point will reset the device. The chip will remain in BOR until VDD rises above threshold.

If the Power-up Timer is enabled, it will be invoked after VDD rises above the threshold. Then, it will keep the chip in Reset for an additional time delay, TPWRT, if VDD drops below the threshold while the Power-up Timer is running. The chip goes back into a BOR and the Power-up Timer will be initialized. Once VDD rises above the threshold, the Power-up Timer will execute the additional time delay.

BOR and the Power-up Timer are independently configured. Enabling the BOR Reset does not automatically enable the PWRT.

### 7.5.1 SOFTWARE ENABLED BOR

When BOREN<1:0> = 01, the BOR can be enabled or disabled by the user in software. This is done with the control bit, SBOREN (RCON<13>). Setting SBOREN enables the BOR to function as previously described. Clearing the SBOREN disables the BOR entirely. The SBOREN bit operates only in this mode; otherwise, it is read as '0'.

Placing BOR under software control gives the user the additional flexibility of tailoring the application to its environment without having to reprogram the device to change the BOR configuration. It also allows the user to tailor the incremental current that the BOR consumes. While the BOR current is typically very small, it may have some impact in low-power applications.

Note: Even when the BOR is under software control, the BOR Reset voltage level is still set by the BORV<1:0> Configuration bits; it can not be changed in software.

### 8.3 Interrupt Control and Status Registers

The PIC24F16KA102 family of devices implements a total of 22 registers for the interrupt controller:

- INTCON1

- INTCON2

- IFS0, IFS1, IFS3 and IFS4

- · IEC0, IEC1, IEC3 and IEC4

- IPC0 through IPC5, IPC7 and IPC15 through IPC19

- INTTREG

Global interrupt control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit, as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the AIV table.

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals, or external signal, and is cleared via software.

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

The IPCx registers are used to set the interrupt priority level for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels. The INTTREG register contains the associated interrupt vector number and the new CPU interrupt priority level, which are latched into the Vector Number (VECNUM<6:0>) and the Interrupt Level (ILR<3:0>) bit fields in the INTTREG register. The new interrupt priority level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence listed in Table 8-2. For example, the INT0 (External Interrupt 0) is depicted as having a vector number and a natural order priority of 0. Thus, the INT0IF status bit is found in IFS0<0>, the INT0IE enable bit in IEC0<0> and the INT0IP<2:0> priority bits in the first position of IPC0 (IPC0<2:0>).

Although they are not specifically part of the interrupt control hardware, two of the CPU control registers contain bits that control interrupt functionality. The ALU STATUS register (SR) contains the IPL<2:0> bits (SR<7:5>). These indicate the current CPU interrupt priority level. The user may change the current CPU priority level by writing to the IPL bits.

The CORCON register contains the IPL3 bit, which together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that the trap events cannot be masked by the user's software.

All interrupt registers are described in Register 8-1 through Register 8-21, in the following sections.

| U-0          | U-0                                                        | U-0              | U-0           | U-0                                | R/W-1      | R/W-0              | R/W-0  |  |  |  |  |

|--------------|------------------------------------------------------------|------------------|---------------|------------------------------------|------------|--------------------|--------|--|--|--|--|

| _            | —                                                          | —                | —             | —                                  | RTCIP2     | RTCIP1             | RTCIP0 |  |  |  |  |

| bit 15       |                                                            |                  |               |                                    |            |                    | bit 8  |  |  |  |  |

|              |                                                            |                  |               |                                    |            |                    |        |  |  |  |  |

| U-0          | U-0                                                        | U-0              | U-0           | U-0                                | U-0        | U-0                | U-0    |  |  |  |  |

| _            | _                                                          |                  | _             | —                                  | —          | —                  | _      |  |  |  |  |

| bit 7        |                                                            |                  |               | -                                  |            | •                  | bit 0  |  |  |  |  |

|              |                                                            |                  |               |                                    |            |                    |        |  |  |  |  |

| Legend:      |                                                            |                  |               |                                    |            |                    |        |  |  |  |  |

| R = Readab   | le bit                                                     | W = Writable     | bit           | U = Unimplemented bit, read as '0' |            |                    |        |  |  |  |  |

| -n = Value a | t POR                                                      | '1' = Bit is set |               | '0' = Bit is clea                  | ared       | x = Bit is unknown |        |  |  |  |  |

|              |                                                            |                  |               |                                    |            |                    |        |  |  |  |  |

| bit 15-11    | Unimplemen                                                 | ted: Read as 'd  | )'            |                                    |            |                    |        |  |  |  |  |

| bit 10-8     | RTCIP<2:0>:                                                | Real-Time Clo    | ck and Calend | ar Interrupt Pric                  | ority bits |                    |        |  |  |  |  |

|              | 111 = Interrupt is Priority 7 (highest priority interrupt) |                  |               |                                    |            |                    |        |  |  |  |  |

|              | •                                                          |                  |               |                                    |            |                    |        |  |  |  |  |

|              | •                                                          |                  |               |                                    |            |                    |        |  |  |  |  |

|              | •<br>001 = Interrupt is Priority 1                         |                  |               |                                    |            |                    |        |  |  |  |  |

|              |                                                            | pt source is dis | abled         |                                    |            |                    |        |  |  |  |  |

| bit 7-0      | -                                                          | ted: Read as 'd  |               |                                    |            |                    |        |  |  |  |  |

|              | •                                                          |                  |               |                                    |            |                    |        |  |  |  |  |

### REGISTER 8-20: IPC15: INTERRUPT PRIORITY CONTROL REGISTER 15

### REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

| bit 7 | CLKLOCK: Clock Selection Lock Enabled bit<br><u>If FSCM is enabled (FCKSM1 = 1):</u><br>1 = Clock and PLL selections are locked<br>0 = Clock and PLL selections are not locked and may be modified by setting the OSWEN bit<br><u>If FSCM is disabled (FCKSM1 = 0):</u><br>Clock and PLL selections are never locked and may be modified by setting the OSWEN bit. |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                         |

| bit 5 | LOCK: PLL Lock Status bit <sup>(2)</sup><br>1 = PLL module is in lock or PLL module start-up timer is satisfied<br>0 = PLL module is out of lock, PLL start-up timer is running or PLL is disabled                                                                                                                                                                 |

| bit 4 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                         |

| bit 3 | <b>CF:</b> Clock Fail Detect bit<br>1 = FSCM has detected a clock failure<br>0 = No clock failure has been detected                                                                                                                                                                                                                                                |

| bit 2 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                         |

| bit 1 | <b>SOSCEN:</b> 32 kHz Secondary Oscillator (SOSC) Enable bit<br>1 = Enable secondary oscillator<br>0 = Disable secondary oscillator                                                                                                                                                                                                                                |

| bit 0 | <b>OSWEN:</b> Oscillator Switch Enable bit<br>1 = Initiate an oscillator switch to clock source specified by NOSC<2:0> bits<br>0 = Oscillator switch is complete                                                                                                                                                                                                   |

- Note 1: Reset values for these bits are determined by the FNOSC Configuration bits.

- 2: Also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

#### 19.2.5 RTCVAL REGISTER MAPPINGS

### REGISTER 19-4: YEAR: YEAR VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-x  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| YRTEN3 | YRTEN2 | YRTEN2 | YRTEN1 | YRONE3 | YRONE2 | YRONE1 | YRONE0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

### Legend:

| Ecgenia.          |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

- bit 7-4 **YRTEN<3:0>:** Binary Coded Decimal Value of Year's Tens Digit bits Contains a value from 0 to 9.

- bit 3-0 **YRONE<3:0>:** Binary Coded Decimal Value of Year's Ones Digit bits Contains a value from 0 to 9.

**Note 1:** A write to the YEAR register is only allowed when RTCWREN = 1.

### **REGISTER 19-5: MTHDY: MONTH AND DAY VALUE REGISTER<sup>(1)</sup>**

| U-0    | U-0 | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|--------|-----|-----|---------|---------|---------|---------|---------|

| _      | —   | —   | MTHTEN0 | MTHONE3 | MTHONE2 | MTHONE1 | MTHONE0 |

| bit 15 |     |     |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | —   | DAYTEN1 | DAYTEN0 | DAYONE3 | DAYONE2 | DAYONE1 | DAYONE0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                    |

|-----------|---------------------------------------------------------------|

| bit 12    | MTHTEN0: Binary Coded Decimal Value of Month's Tens Digit bit |

|           | Contains a value of '0' or '1'.                               |

| bit 11-8  | MTHONE<3:0>: Binary Coded Decimal Value of Month's Ones Digit |

bit 11-8 MTHONE<3:0>: Binary Coded Decimal Value of Month's Ones Digit bits Contains a value from 0 to 9.

bit 7-6 Unimplemented: Read as '0'

- bit 5-4 **DAYTEN<1:0>:** Binary Coded Decimal Value of Day's Tens Digit bits Contains a value from 0 to 3.

- bit 3-0 DAYONE<3:0>: Binary Coded Decimal Value of Day's Ones Digit bits Contains a value from 0 to 9.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

### **REGISTER 23-1: CMxCON: COMPARATOR x CONTROL REGISTERS (CONTINUED)**

- bit 5 Unimplemented: Read as '0'

- bit 4 **CREF:** Comparator Reference Select bit (non-inverting input) 1 = Non-inverting input connects to the internal CVREF voltage

- 0 = Non-inverting input connects to the CxINA pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Channel Select bits

- 11 = Inverting input of comparator connects to VBG/2

- 10 = Inverting input of comparator connects to CxIND pin

- 01 = Inverting input of comparator connects to CxINC pin

- 00 = Inverting input of comparator connects to CxINB pin

### REGISTER 23-2: CMSTAT: COMPARATOR MODULE STATUS REGISTER

| R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0 | R-0, HSC | R-0, HSC |

|--------|-----|-----|-----|-----|-----|----------|----------|

| CMIDL  |     | —   | —   | —   | _   | C2EVT    | C1EVT    |

| bit 15 |     |     |     |     |     |          | bit 8    |

|        |     |     |     |     |     |          |          |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R-0, HSC | R-0, HSC |

\_\_\_\_

| bit | 7 |

|-----|---|

| Legend:           | HSC = Hardware Settable/Clearable bit |                                    |                    |  |  |

|-------------------|---------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 15    | CMIDL: Comparator Stop in Idle Mode bit                                                                                                                                                     |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | <ul> <li>1 = Disable comparator interrupts when the device enters Idle mode; the module is still enabled</li> <li>0 = Continue operation of all enabled comparators in Idle mode</li> </ul> |

| bit 14-10 | Unimplemented: Read as '0'                                                                                                                                                                  |

| bit 9     | C2EVT: Comparator 2 Event Status bit (read-only)                                                                                                                                            |

|           | Shows the current event status of Comparator 2 (CM2CON<9>).                                                                                                                                 |

| bit 8     | C1EVT: Comparator 1 Event Status bit (read-only)                                                                                                                                            |

|           | Shows the current event status of Comparator 1 (CM1CON<9>).                                                                                                                                 |

| bit 7-2   | Unimplemented: Read as '0'                                                                                                                                                                  |

| bit 1     | C2OUT: Comparator 2 Output Status bit (read-only)                                                                                                                                           |

|           | Shows the current output of Comparator 2 (CM2CON<8>).                                                                                                                                       |

| bit 0     | C1OUT: Comparator 1 Output Status bit (read-only)                                                                                                                                           |

|           | Shows the current output of Comparator 1 (CM1CON<8>).                                                                                                                                       |

C2OUT

C10UT

bit 0

NOTES:

### TABLE 29-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARACTERISTICS                       |      |      | Standard Ope<br>Operating temp | s <b>otherwise stated)</b><br>strial<br>tended |      |                           |  |

|------------------------------------------|------|------|--------------------------------|------------------------------------------------|------|---------------------------|--|

| Parameter No. Typical <sup>(1)</sup> Max |      |      | Units                          | Conditions                                     |      |                           |  |

| IDD Current <sup>(2)</sup>               |      |      |                                |                                                |      |                           |  |

| DC20                                     |      | 330  |                                | -40°C                                          |      |                           |  |

| DS20a                                    | 1    | 330  |                                | +25°C                                          |      |                           |  |

| DC20b                                    | 195  | 330  | μΑ                             | +60°C                                          | 1.8V |                           |  |

| DC20c                                    |      | 330  |                                | +85°C                                          |      |                           |  |

| DC20d                                    |      | 500  |                                | +125°C                                         |      | 0.5 MIPS,                 |  |

| DC20e                                    |      | 590  |                                | -40°C                                          |      | Fosc = 1 MHz              |  |

| DC20f                                    |      | 590  |                                | +25°C                                          |      |                           |  |

| DC20g                                    | 365  | 645  | μA                             | +60°C                                          | 3.3V |                           |  |

| DC20h                                    | 1    | 720  |                                | +85°C                                          |      |                           |  |

| DC20i                                    |      | 800  |                                | +125°C                                         |      |                           |  |

| DC22                                     |      | 600  |                                | -40°C                                          |      |                           |  |

| DC22a                                    |      | 600  | 1                              | +25°C                                          |      |                           |  |

| DC22b                                    | 363  | 600  | μΑ                             | +60°C                                          | 1.8V |                           |  |

| DC22c                                    |      | 600  | +85°C                          |                                                |      |                           |  |

| DC22d                                    |      | 800  |                                | +125°C                                         |      | 1 MIPS,                   |  |

| DC22e                                    |      | 1100 |                                | -40°C                                          |      | Fosc = 2 MHz              |  |

| DC22f                                    |      | 1100 |                                | +25°C                                          |      |                           |  |

| DC22g                                    | 695  | 1100 | μΑ                             | +60°C                                          | 3.3V |                           |  |

| DC22h                                    | 1 1  | 1100 |                                | +85°C                                          |      |                           |  |

| DC22i                                    |      | 1500 | 1                              | +125°C                                         |      |                           |  |

| DC23                                     |      | 18   |                                | -40°C                                          |      |                           |  |

| DC23a                                    |      | 18   |                                | +25°C                                          |      |                           |  |

| DC23b                                    | 11   | 18   | mA                             | +60°C                                          | 3.3V | 16 MIPS,<br>Fosc = 32 MHz |  |

| DC23c                                    |      | 18   |                                | +85°C                                          |      | FUSC - 32 MITZ            |  |

| DC23d                                    |      | 18   |                                | +125°C                                         |      |                           |  |

| DC27                                     |      | 3.40 | 1                              | -40°C                                          |      |                           |  |

| DC27a                                    | 1 1  | 3.40 | 1                              | +25°C                                          |      |                           |  |

| DC27b                                    | 2.25 | 3.40 | mA                             | +60°C                                          | 2.5V |                           |  |

| DC27c                                    | 1    | 3.40 | 1 F                            | +85°C                                          |      |                           |  |

| DC27d                                    | 1 1  | 3.40 | 1 F                            | +125°C                                         |      | FRC (4 MIPS),             |  |

| DC27e                                    |      | 4.60 |                                | -40°C                                          |      | Fosc = 8 MHz              |  |

| DC27f                                    | 1 1  | 4.60 | 1 F                            | +25°C                                          |      |                           |  |

| DC27g                                    | 3.05 | 4.60 | mA                             | +60°C                                          | 3.3V |                           |  |

| DC27h                                    | 1 1  | 4.60 | 1 F                            | +85°C                                          |      |                           |  |

| DC27i                                    | 1 [  | 5.40 | 1 F                            | +125°C                                         |      |                           |  |

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**2:** Operating Parameters:

• EC mode with clock input driven with a square wave rail-to-rail

· I/Os are configured as outputs, driven low

• MCLR – VDD

WDT FSCM is disabled

• SRAM, program and data memory are active

• All PMD bits are set except for modules being measured

### TABLE 29-7: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

| DC CHARACTERISTICS |                        |              | $ \begin{array}{ll} \mbox{Standard Operating Conditions: 1.8V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array} $ |                      |            |                           |

|--------------------|------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------|---------------------------|

| Param No.          | Typical <sup>(1)</sup> | Max          | Units                                                                                                                                                                                                                                                                          |                      | Conditions |                           |

| Idle Current (     | IIDLE): Core (         | Off, Clock o | on Base Currei                                                                                                                                                                                                                                                                 | nt, PMD Bits are Set | (2)        |                           |

| DC40               |                        | 100          |                                                                                                                                                                                                                                                                                | -40°C                |            |                           |

| DC40a              |                        | 100          |                                                                                                                                                                                                                                                                                | +25°C                |            |                           |

| DC40b              | 48                     | 100          | μA                                                                                                                                                                                                                                                                             | +60°C                | 1.8V       |                           |

| DC40c              |                        | 100          |                                                                                                                                                                                                                                                                                | +85°C                |            |                           |

| DC40d              |                        | 100          |                                                                                                                                                                                                                                                                                | +125°C               |            | 0.5 MIPS,<br>Fosc = 1 MHz |

| DC40e              |                        | 215          |                                                                                                                                                                                                                                                                                | -40°C                |            |                           |

| DC40f              |                        | 215          |                                                                                                                                                                                                                                                                                | +25°C                |            |                           |

| DC40g              | 106                    | 215          | μΑ                                                                                                                                                                                                                                                                             | +60°C                | 3.3V       |                           |

| DC40h              |                        | 215          |                                                                                                                                                                                                                                                                                | +85°C                |            |                           |

| DC40i              |                        | 450          |                                                                                                                                                                                                                                                                                | +125°C               |            |                           |

| DC42               |                        | 200          |                                                                                                                                                                                                                                                                                | -40°C                |            |                           |

| DC42a              |                        | 200          |                                                                                                                                                                                                                                                                                | +25°C                |            |                           |

| DC42b              | 94                     | 200          | μA                                                                                                                                                                                                                                                                             | +60°C                | 1.8V       |                           |

| DC42c              | -                      | 200          | -                                                                                                                                                                                                                                                                              | +85°C                |            |                           |

| DC42d              |                        | 300          |                                                                                                                                                                                                                                                                                | +125°C               |            | 1 MIPS,                   |

| DC42e              |                        | 395          |                                                                                                                                                                                                                                                                                | -40°C                |            | Fosc = 2 MHz              |

| DC42f              |                        | 395          |                                                                                                                                                                                                                                                                                | +25°C                |            |                           |

| DC42g              | 160                    | 395          | μΑ                                                                                                                                                                                                                                                                             | +60°C                | 3.3V       |                           |

| DC42h              |                        | 395          | 1 1                                                                                                                                                                                                                                                                            | +85°C                |            |                           |

| DC42i              | 1                      | 600          |                                                                                                                                                                                                                                                                                | +125°C               |            |                           |

| DC43               |                        | 6.0          |                                                                                                                                                                                                                                                                                | -40°C                |            |                           |

| DC43a              | 1                      | 6.0          |                                                                                                                                                                                                                                                                                | +25°C                |            |                           |

| DC43b              | 3.1                    | 6.0          | mA                                                                                                                                                                                                                                                                             | +60°C                | 3.3V       | 16 MIPS,                  |

| DC43c              |                        | 6.0          | 1                                                                                                                                                                                                                                                                              | +85°C                |            | Fosc = 32 MHz             |

| DC43d              | 1                      | 6.0          |                                                                                                                                                                                                                                                                                | +125°C               |            |                           |

| DC44               |                        | 0.74         |                                                                                                                                                                                                                                                                                | -40°C                |            |                           |

| DC44a              | 1                      | 0.74         | 1                                                                                                                                                                                                                                                                              | +25°C                |            |                           |

| DC44b              | 0.56                   | 0.74         | mA                                                                                                                                                                                                                                                                             | +60°C                | 1.8V       |                           |

| DC44c              |                        | 0.74         | 1                                                                                                                                                                                                                                                                              | +85°C                |            |                           |

| DC44d              | 1                      | 0.74         | 1                                                                                                                                                                                                                                                                              | +125°C               |            | FRC (4 MIPS),             |

| DC44e              |                        | 1.50         |                                                                                                                                                                                                                                                                                | -40°C                |            | Fosc = 8 MHz              |

| DC44f              | 1                      | 1.50         | 1                                                                                                                                                                                                                                                                              | +25°C                |            |                           |

| DC44g              | 0.95                   | 1.50         | mA                                                                                                                                                                                                                                                                             | +60°C                | 3.3V       |                           |

| DC44h              | 1                      | 1.50         | 1                                                                                                                                                                                                                                                                              | +85°C                |            |                           |

| DC44i              | 1                      | 1.50         | 1                                                                                                                                                                                                                                                                              | +125°C               |            |                           |

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: Operating Parameters:

Core is off

• EC mode with the clock input driven with a square wave rail-to-rail

• I/Os are configured as outputs, driven low

• MCLR - VDD

• WDT FSCM are disabled

• SRAM, program and data memory are active

• All PMD bits are set except for the modules being measured

| DC CHARACTERISTICS |                        |              | $ \begin{array}{llllllllllllllllllllllllllllllllllll$ |                           |      |                                       |  |

|--------------------|------------------------|--------------|-------------------------------------------------------|---------------------------|------|---------------------------------------|--|

| Parameter<br>No.   | Typical <sup>(1)</sup> | Max          | Units                                                 | Conditions                |      |                                       |  |

| Power-Down (       | Current (IPD): F       | PMD Bits are | Set, PMSLP                                            | Bit is '0' <sup>(2)</sup> |      |                                       |  |

| DC70               |                        | 0.200        |                                                       | -40°C                     |      |                                       |  |

| DC70a              |                        | 0.200        |                                                       | +25°C                     |      |                                       |  |

| DC70b              | 0.045                  | 0.200        | μΑ                                                    | +60°C                     | 1.8V |                                       |  |

| DC70c              |                        | 0.200        |                                                       | +85°C                     |      |                                       |  |

| DC70d              |                        | 1.45         |                                                       | +125°C                    |      | LPBOR <sup>(3,4)</sup>                |  |

| DC70e              |                        | 0.200        |                                                       | -40°C                     |      |                                       |  |

| DC70f              |                        | 0.200        |                                                       | +25°C                     |      |                                       |  |

| DC70g              | 0.095                  | 0.200        | μΑ                                                    | +60°C                     | 3.3V |                                       |  |

| DC70h              |                        | 0.200        |                                                       | +85°C                     |      |                                       |  |

| DC70i              |                        | 1.55         |                                                       | +125°C                    |      |                                       |  |

| DC71               |                        | 0.55         |                                                       | -40°C                     |      |                                       |  |

| DC71a              |                        | 0.55         |                                                       | +25°C                     |      |                                       |  |

| DC71b              | 0.35                   | 0.55         | μΑ                                                    | +60°C                     | 1.8V |                                       |  |

| DC71c              |                        | 0.55         |                                                       | +85°C                     |      | Deep Sleep Watchdog Timer:            |  |

| DC71d              |                        | 1.70         |                                                       | +125°C                    |      |                                       |  |

| DC71e              |                        | 0.75         |                                                       | -40°C                     |      | DSWDT (SOSC – LP) <sup>(6)</sup>      |  |

| DC71f              |                        | 0.75         |                                                       | +25°C                     |      |                                       |  |

| DC71g              | 0.55                   | 0.75         | μΑ                                                    | +60°C                     | 3.3V |                                       |  |

| DC71h              |                        | 0.75         |                                                       | +85°C                     |      |                                       |  |

| DC71i              |                        | 2.10         |                                                       | +125°C                    |      |                                       |  |

| DC72               |                        | 0.200        | μΑ                                                    | -40°C                     |      |                                       |  |

| DC72a              |                        | 0.200        |                                                       | +25°C                     | 1.8V |                                       |  |

| DC72b              | 0.005                  | 0.200        |                                                       | +60°C                     |      |                                       |  |

| DC72c              |                        | 0.200        |                                                       | +85°C                     |      |                                       |  |

| DC72d              |                        | 0.200        |                                                       | +125°C                    |      | Deep Sleep BOR (DSBOR) <sup>(6)</sup> |  |

| DC72e              |                        | 0.200        |                                                       | -40°C                     |      |                                       |  |

| DC72f              |                        | 0.200        |                                                       | +25°C                     |      |                                       |  |

| DC72g              | 0.010                  | 0.200        | μΑ                                                    | +60°C                     | 3.3V |                                       |  |

| DC72h              |                        | 0.200        |                                                       | +85°C                     |      |                                       |  |

|                    |                        |              |                                                       |                           | 7    | 1                                     |  |

Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only Note 1: and are not tested.

Base IPD is measured with all peripherals and clocks shut down. All I/Os are configured as outputs and set low. 2: WDT, etc., are all switched off.

+125°C

3: The  $\Delta$  current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- 4: Current applies to Sleep only.

- 5: Current applies to Sleep and Deep Sleep.

0.200

6: Current applies to Deep Sleep only.

DC72i

### http://www.microchip.com/packaging EXPOSED D2 D PAD е E2 2 2 1 1 Ν Ν NOTE 1 TOP VIEW BOTTOM VIEW А AAAAA 99

### 20-Lead Plastic Quad Flat, No Lead Package (MQ) – 5x5x0.9 mm Body [QFN]

For the most current package drawings, please see the Microchip Packaging Specification located at

|                        | MILLIMETERS |      |          |      |

|------------------------|-------------|------|----------|------|

| Dimens                 | sion Limits | MIN  | NOM      | MAX  |

| Number of Pins         | N           |      | 20       |      |

| Pitch                  | е           |      | 0.65 BSC |      |

| Overall Height         | Α           | 0.80 | 0.90     | 1.00 |

| Standoff               | A1          | 0.00 | 0.02     | 0.05 |

| Contact Thickness      | A3          |      | 0.20 REF |      |

| Overall Width          | E           |      | 5.00 BSC |      |

| Exposed Pad Width      | E2          | 3.15 | 3.25     | 3.35 |

| Overall Length         | D           |      | 5.00 BSC |      |

| Exposed Pad Length     | D2          | 3.15 | 3.25     | 3.35 |

| Contact Width          | b           | 0.25 | 0.30     | 0.35 |

| Contact Length         | L           | 0.35 | 0.40     | 0.45 |

| Contact-to-Exposed Pad | K           | 0.20 | -        | -    |

Notes:

A3

Note:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

A1

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-139B

### APPENDIX A: REVISION HISTORY

### **Revision A (November 2008)**

Original data sheet for the PIC24F16KA102 family of devices.

### Revision B (March 2009)

Section 29.0 "Electrical Characteristics" was revised and minor text edits were made throughout the document.

### **Revision C (October 2011)**

- · Changed all instances of DSWSRC to DSWAKE.

- Corrected Example 5-2.

- Corrected Example 5-4.

- Corrected Example 6-1.

- Corrected Example 6-3.

- Added a comment to Example 6-5.

- Corrected Figure 9-1 to connect the SOSCI and SOSCO pins to the Schmitt trigger correctly.

- Added register descriptions for PMD1, PMD2, PMD3 and PMD4.

- Added note that RTCC will run in Reset.

- Corrected time values of ADCS (AD1CON3<5:0>).

- Corrected CH0SB and CH0SA (AD1CHS<11:8> and AD1CHS<3:0>) to correctly reference AVDD and AN3.

- Added description of PGCF15 and PGCF14 (AD1PCFG<15:14>).

- Edited Figure 22-2 to correctly reference RIC and the A/D capacitance.