Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                  |

|--------------------------------|------------------------------------------------------------------|

| Product Status                 | Obsolete                                                         |

| Number of LABs/CLBs            | -                                                                |

| Number of Logic Elements/Cells | 75264                                                            |

| Total RAM Bits                 | 516096                                                           |

| Number of I/O                  | 620                                                              |

| Number of Gates                | 300000                                                           |

| Voltage - Supply               | 1.14V ~ 1.575V                                                   |

| Mounting Type                  | Surface Mount                                                    |

| Operating Temperature          | -40°C ~ 85°C (TA)                                                |

| Package / Case                 | 896-BGA                                                          |

| Supplier Device Package        | 896-FBGA (31x31)                                                 |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/agle3000v2-fg896i |

|                                |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

IGLOOe Device Family Overview

# SRAM and FIFO

IGLOOe devices have embedded SRAM blocks along their north and south sides. Each variable-aspectratio SRAM block is 4,608 bits in size. Available memory configurations are 256×18, 512×9, 1k×4, 2k×2, and 4k×1 bits. The individual blocks have independent read and write ports that can be configured with different bit widths on each port. For example, data can be sent through a 4-bit port and read as a single bitstream. The embedded SRAM blocks can be initialized via the device JTAG port (ROM emulation mode) using the UJTAG macro.

In addition, every SRAM block has an embedded FIFO control unit. The control unit allows the SRAM block to be configured as a synchronous FIFO without using additional core VersaTiles. The FIFO width and depth are programmable. The FIFO also features programmable Almost Empty (AEMPTY) and Almost Full (AFULL) flags in addition to the normal Empty and Full flags. The embedded FIFO control unit contains the counters necessary for generation of the read and write address pointers. The embedded SRAM/FIFO blocks can be cascaded to create larger configurations.

# PLL and CCC

IGLOOe devices provide designers with very flexible clock conditioning capabilities. Each member of the IGLOOe family contains six CCCs, each with an integrated PLL.

The six CCC blocks are located at the four corners and the centers of the east and west sides. One CCC (center west side) has a PLL.

The inputs of the six CCC blocks are accessible from the FPGA core or from one of several inputs located near the CCC that have dedicated connections to the CCC block.

The CCC block has these key features:

- Wide input frequency range ( $f_{IN CCC}$ ) = 1.5 MHz up to 250 MHz

- Output frequency range (f<sub>OUT CCC</sub>) = 0.75 MHz up to 250 MHz

- 2 programmable delay types for clock skew minimization

- Clock frequency synthesis

Additional CCC specifications:

- Internal phase shift = 0°, 90°, 180°, and 270°. Output phase shift depends on the output divider configuration.

- Output duty cycle = 50% ± 1.5% or better

- Low output jitter: worst case < 2.5% × clock period peak-to-peak period jitter when single global network used

- Maximum acquisition time is 300 µs

- Exceptional tolerance to input period jitter—allowable input jitter is up to 1.5 ns

- Four precise phases; maximum misalignment between adjacent phases of 40 ps × 250 MHz / fout\_ccc

#### **Global Clocking**

IGLOOe devices have extensive support for multiple clocking domains. In addition to the CCC and PLL support described above, there is a comprehensive global clock distribution network.

Each VersaTile input and output port has access to nine VersaNets: six chip (main) and three quadrant global networks. The VersaNets can be driven by the CCC or directly accessed from the core via multiplexers (MUXes). The VersaNets can be used to distribute low-skew clock signals or for rapid distribution of high-fanout nets.

IGLOOe Device Family Overview

| m file Save to file | <u></u>               |            | Show BSR [              |

|---------------------|-----------------------|------------|-------------------------|

| Port Name           | Macro Cell            | Pin Number | 1/O State (Output Only) |

| BIST                | ADLIB:INBUF           | T2         | 1                       |

| SYPASS_IO           | ADLIB:INBUF           | K1         | 1                       |

| CLK                 | ADLIB:INBUF           | B1         | 1                       |

| ENOUT               | ADLIB:INBUF           | J16        | 1                       |

| _ED                 | ADLIB:OUTBUF          | M3         | 0                       |

| MONITOR[0]          | ADLIB:OUTBUF          | B5         | 0                       |

| MONITOR[1]          | ADLIB:OUTBUF          | C7         | Z                       |

| MONITOR[2]          | ADLIB:OUTBUF          | D9         | Z                       |

| MONITOR[3]          | ADLIB:OUTBUF          | D7         | Z                       |

| MONITOR[4]          | ADLIB:OUTBUF          | A11        | Z                       |

| DEa                 | ADLIB:INBUF           | E4         | Z                       |

| ЭЕЬ                 | ADLIB:INBUF           | F1         | Z                       |

| DSC_EN              | ADLIB:INBUF           | К3         | Z                       |

| PAD[10]             | ADLIB:BIBUF_LVCMOS33U | M8         | Z                       |

| PAD[11]             | ADLIB:BIBUF_LVCMOS33D | R7         | Z                       |

| PAD[12]             | ADLIB:BIBUF_LVCMOS33U | D11        | Z                       |

| PAD[13]             | ADLIB:BIBUF_LVCMOS33D | C12        | Z                       |

| PAD[14]             | ADLIB:BIBUF_LVCMOS33U | R6         | Z                       |

### Figure 1-4 • I/O States During Programming Window

- 6. Click OK to return to the FlashPoint Programming File Generator window.

- Note: I/O States During programming are saved to the ADB and resulting programming files after completing programming file generation.

| Product Grade | Programming<br>Cycles | Program Retention<br>(biased/unbiased) | Maximum Storage<br>Temperature T <sub>STG</sub> (°C) <sup>2</sup> | Maximum Operating Junction Temperature $T_J$ (°C) <sup>2</sup> |

|---------------|-----------------------|----------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------|

| Commercial    | 500                   | 20 years                               | 110                                                               | 100                                                            |

| Industrial    | 500                   | 20 years                               | 110                                                               | 100                                                            |

| <i>Table 2-3</i> • Flash Programming Limits – Retention, Storage, and Operating Temperature | Table 2-3 • | Flash Programming Limits – Retention, Storage, and Operating Temperature <sup>1</sup> |

|---------------------------------------------------------------------------------------------|-------------|---------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------------|-------------|---------------------------------------------------------------------------------------|

Notes:

1. This is a stress rating only; functional operation at any condition other than those indicated is not implied.

2. These limits apply for program/data retention only. Refer to Table 2-1 on page 2-1 and Table 2-2 for device operating conditions and absolute limits.

| Table 2-4 • | Overshoot and Undershoot Limits <sup>1, 3</sup> |

|-------------|-------------------------------------------------|

|             |                                                 |

| VCCI          | Average VCCI–GND Overshoot or Undershoot Duration<br>as a Percentage of Clock Cycle <sup>2</sup> | Maximum Overshoot/<br>Undershoot <sup>2</sup> |

|---------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 2.7 V or less | 10%                                                                                              | 1.4 V                                         |

|               | 5%                                                                                               | 1.49 V                                        |

| 3 V           | 10%                                                                                              | 1.1 V                                         |

|               | 5%                                                                                               | 1.19 V                                        |

| 3.3 V         | 10%                                                                                              | 0.79 V                                        |

|               | 5%                                                                                               | 0.88 V                                        |

| 3.6 V         | 10%                                                                                              | 0.45 V                                        |

|               | 5%                                                                                               | 0.54 V                                        |

Notes:

1. Based on reliability requirements at junction temperature at 85°C.

2. The duration is allowed at one out of six clock cycles. If the overshoot/undershoot occurs at one out of two cycles, the maximum overshoot/undershoot has to be reduced by 0.15 V.

3. This table does not provide PCI overshoot/undershoot limits.

# I/O Power-Up and Supply Voltage Thresholds for Power-On Reset (Commercial and Industrial)

Sophisticated power-up management circuitry is designed into every IGLOOe device. These circuits ensure easy transition from the powered-off state to the powered-up state of the device. The many different supplies can power up in any sequence with minimized current spikes or surges. In addition, the I/O will be in a known state through the power-up sequence. The basic principle is shown in Figure 2-1 on page 2-4 and Figure 2-2 on page 2-5.

There are five regions to consider during power-up.

IGLOOe I/Os are activated only if ALL of the following three conditions are met:

- 1. VCC and VCCI are above the minimum specified trip points (Figure 2-1 on page 2-4 and Figure 2-2 on page 2-5).

- 2. VCCI > VCC 0.75 V (typical)

- 3. Chip is in the operating mode.

#### VCCI Trip Point:

Ramping up: 0.6 V < trip\_point\_up < 1.2 V Ramping down: 0.5 V < trip\_point\_down < 1.1 V

#### VCC Trip Point:

Ramping up: 0.6 V < trip\_point\_up < 1.1 V Ramping down: 0.5 V < trip\_point\_down < 1 V

VCC and VCCI ramp-up trip points are about 100 mV higher than ramp-down trip points. This specifically built-in hysteresis prevents undesirable power-up oscillations and current surges. Note the following:

• During programming, I/Os become tristated and weakly pulled up to VCCI.

# **Calculating Power Dissipation**

# **Quiescent Supply Current**

Quiescent supply current (IDD) calculation depends on multiple factors, including operating voltages (VCC, VCCI, and VJTAG), operating temperature, system clock frequency, and power modes usage. Microsemi recommends using the PowerCalculator and SmartPower software estimation tools to evaluate the projected static and active power based on the user design, power mode usage, operating voltage, and temperature.

#### Table 2-8 • Power Supply State per Mode

|                      | Power Supply Configurations |        |      |       |                 |  |  |

|----------------------|-----------------------------|--------|------|-------|-----------------|--|--|

| Modes/power supplies | VCC                         | VCCPLL | VCCI | VJTAG | VPUMP           |  |  |

| Flash*Freeze         | On                          | On     | On   | On    | On/off/floating |  |  |

| Sleep                | Off                         | Off    | On   | Off   | Off             |  |  |

| Shutdown             | Off                         | Off    | Off  | Off   | Off             |  |  |

| No Flash*Freeze      | On                          | On     | On   | On    | On/off/floating |  |  |

*Note:* Off: Power supply level = 0 V

#### Table 2-9 • Quiescent Supply Current (IDD), IGLOOe Flash\*Freeze Mode\*

|                | Core Voltage | AGLE600 | AGLE3000 | Units |

|----------------|--------------|---------|----------|-------|

| Typical (25°C) | 1.2 V        | 34      | 95       | μΑ    |

|                | 1.5 V        | 72      | 310      | μA    |

Note: \*IDD includes VCC, VPUMP, VCCI, VCCPLL, and VMV currents. Values do not include I/O static contribution, which is shown in Table 2-13 on page 2-9 and Table 2-14 on page 2-10 (PDC6 and PDC7).

#### Table 2-10 • Quiescent Supply Current (IDD) Characteristics, IGLOOe Sleep Mode\*

|                                                 | Core Voltage  | AGLE600 | AGLE3000 | Units |

|-------------------------------------------------|---------------|---------|----------|-------|

| VCCI/VJTAG = 1.2 V (per bank)<br>Typical (25°C) | 1.2 V         | 1.7     | 1.7      | μA    |

| VCCI/VJTAG = 1.5 V (per bank)<br>Typical (25°C) | 1.2 V / 1.5 V | 1.8     | 1.8      | μA    |

| VCCI/VJTAG = 1.8 V (per bank)<br>Typical (25°C) | 1.2 V / 1.5 V | 1.9     | 1.9      | μA    |

| VCCI/VJTAG = 2.5 V (per bank)<br>Typical (25°C) | 1.2 V / 1.5 V | 2.2     | 2.2      | μA    |

| VCCI/VJTAG= 3.3 V (per bank)<br>Typical (25°C)  | 1.2 V / 1.5 V | 2.5     | 2.5      | μA    |

Note:  $*IDD = N_{BANKS} \times ICCI$ . Values do not include I/O static contribution, which is shown in Table 2-13 on page 2-9 and Table 2-14 on page 2-10 (PDC6 and PDC7).

#### Table 2-11 • Quiescent Supply Current (IDD) Characteristics, IGLOOe Shutdown Mode\*

|                | Core Voltage  | AGLE600 | AGLE3000 | Units |

|----------------|---------------|---------|----------|-------|

| Typical (25°C) | 1.2 V / 1.5 V | 0       | 0        | μA    |

# 🌜 Microsemi.

IGLOOe DC and Switching Characteristics

# **User I/O Characteristics**

# **Timing Model**

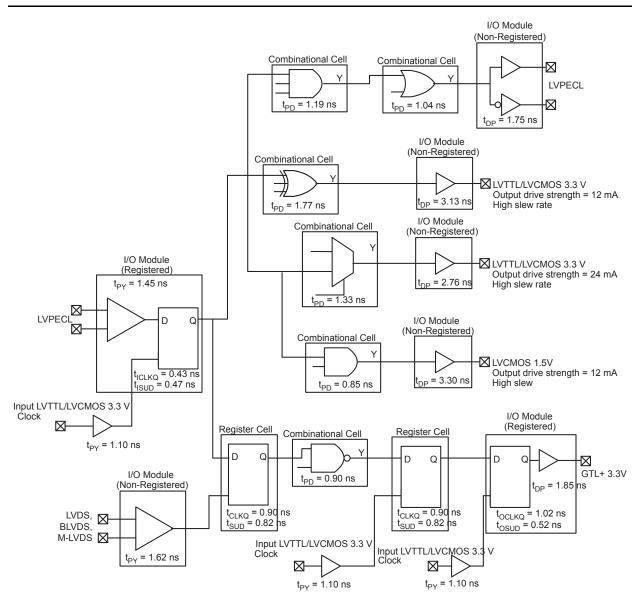

*Figure 2-3* • Timing Model Operating Conditions: Std. Speed, Commercial Temperature Range (T<sub>J</sub> = 70°C), Worst-Case VCC = 1.425 V, Applicable to 1.5 V DC Core Voltage, V2 and V5 devices

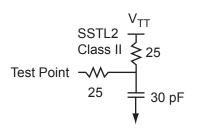

## SSTL2 Class II

Stub-Speed Terminated Logic for 2.5 V memory bus standard (JESD8-9). IGLOOe devices support Class II. This provides a differential amplifier input buffer and a push-pull output buffer.

| SSTL2<br>Class II |           | VIL        | VIH        |           | VOL       | VOH         | IOL | юн | IOSH                    | IOSL                    | IIL¹            | IIH <sup>2</sup> |

|-------------------|-----------|------------|------------|-----------|-----------|-------------|-----|----|-------------------------|-------------------------|-----------------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V   | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup> | μA⁴              |

| 18 mA             | -0.3      | VREF – 0.2 | VREF + 0.2 | 3.6       | 0.35      | VCCI - 0.43 | 18  | 18 | 169                     | 124                     | 10              | 10               |

Table 2-101 • Minimum and Maximum DC Input and Output Levels

Notes:

1. IIL is the input leakage current per I/O pin over recommended operating conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

#### Figure 2-20 • AC Loading

#### Table 2-102 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input HIGH (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------------------|

| VREF – 0.2    | VREF + 0.2     | 1.25                 | 1.25            | 1.25           | 30                     |

Note: \*Measuring point = Vtrip. See Table 2-23 on page 2-23 for a complete table of trip points.

#### Timing Characteristics

1.5 V DC Core Voltage

#### Table 2-103 • SSTL 2 Class II – Applies to 1.5 V DC Core Voltage

```

Commercial-Case Conditions: T_J = 70^{\circ}C, Worst-Case VCC = 1.425 V,

```

Worst-Case VCCI = 2.3 V VREF = 1.25 V

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.        | 0.98              | 1.94            | 0.19             | 1.15            | 0.67              | 1.97            | 1.66            |                 |                 | 5.60             | 5.29             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### 1.2 V DC Core Voltage

#### Table 2-104 • SSTL 2 Class II – Applies to 1.2 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 2.3 V VREF = 1.25 V

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.        | 1.55              | 2.20            | 0.26             | 1.39            | 1.10              | 2.24            | 1.97            |                 |                 | 8.05             | 7.78             | ns    |

# **Differential I/O Characteristics**

### Physical Implementation

Configuration of the I/O modules as a differential pair is handled by the Microsemi Designer software when the user instantiates a differential I/O macro in the design.

Differential I/Os can also be used in conjunction with the embedded Input Register (InReg), Output Register (OutReg), Enable Register (EnReg), and DDR. However, there is no support for bidirectional I/Os or tristates with the LVPECL standards.

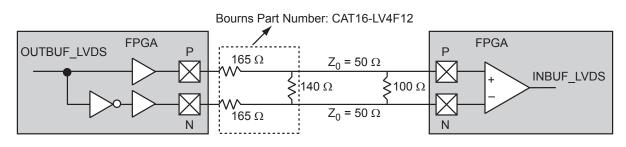

### LVDS

Low-Voltage Differential Signaling (ANSI/TIA/EIA-644) is a high-speed, differential I/O standard. It requires that one data bit be carried through two signal lines, so two pins are needed. It also requires external resistor termination.

The full implementation of the LVDS transmitter and receiver is shown in an example in Figure 2-23. The building blocks of the LVDS transmitter-receiver are one transmitter macro, one receiver macro, three board resistors at the transmitter end, and one resistor at the receiver end. The values for the three driver resistors are different from those used in the LVPECL implementation because the output standard specifications are different.

Along with LVDS I/O, IGLOOe also supports Bus LVDS structure and Multipoint LVDS (M-LVDS) configuration (up to 40 nodes).

Figure 2-23 • LVDS Circuit Diagram and Board-Level Implementation

#### 1.2 V DC Core Voltage

# Table 2-124 • Input Data Register Propagation DelaysCommercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.14 V

| Parameter            | Description                                                         | Std. | Units |

|----------------------|---------------------------------------------------------------------|------|-------|

| t <sub>ICLKQ</sub>   | Clock-to-Q of the Input Data Register                               | 0.68 | ns    |

| t <sub>ISUD</sub>    | Data Setup Time for the Input Data Register                         | 0.97 | ns    |

| t <sub>IHD</sub>     | Data Hold Time for the Input Data Register                          | 0.00 | ns    |

| t <sub>ISUE</sub>    | Enable Setup Time for the Input Data Register                       | 1.02 | ns    |

| t <sub>IHE</sub>     | Enable Hold Time for the Input Data Register                        | 0.00 | ns    |

| t <sub>ICLR2Q</sub>  | Asynchronous Clear-to-Q of the Input Data Register                  | 1.19 | ns    |

| t <sub>IPRE2Q</sub>  | Asynchronous Preset-to-Q of the Input Data Register                 | 1.19 | ns    |

| t <sub>IREMCLR</sub> | Asynchronous Clear Removal Time for the Input Data Register         | 0.00 | ns    |

| t <sub>IRECCLR</sub> | Asynchronous Clear Recovery Time for the Input Data Register        | 0.24 | ns    |

| t <sub>IREMPRE</sub> | Asynchronous Preset Removal Time for the Input Data Register        | 0.00 | ns    |

| t <sub>IRECPRE</sub> | Asynchronous Preset Recovery Time for the Input Data Register       | 0.24 | ns    |

| t <sub>IWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Input Data Register  | 0.19 | ns    |

| t <sub>IWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Input Data Register | 0.19 | ns    |

| t <sub>ICKMPWH</sub> | Clock Minimum Pulse Width HIGH for the Input Data Register          | 0.31 | ns    |

| t <sub>ICKMPWL</sub> | Clock Minimum Pulse Width LOW for the Input Data Register           | 0.28 | ns    |

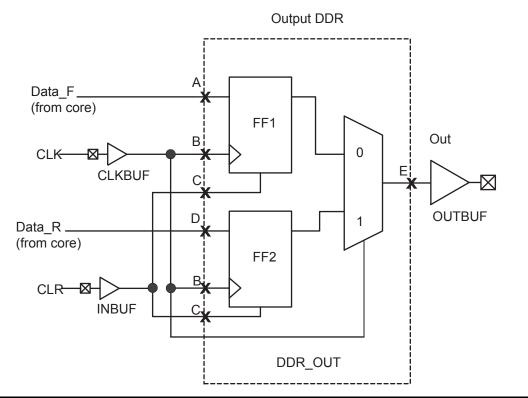

# **Output DDR Module**

# Figure 2-33 • Output DDR Timing Model

### Table 2-132 • Parameter Definitions

| Parameter Name          | Parameter Definition      | Measuring Nodes (from, to) |

|-------------------------|---------------------------|----------------------------|

| t <sub>DDROCLKQ</sub>   | Clock-to-Out              | B, E                       |

| t <sub>DDROCLR2Q</sub>  | Asynchronous Clear-to-Out | C, E                       |

| t <sub>DDROREMCLR</sub> | Clear Removal             | С, В                       |

| t <sub>DDRORECCLR</sub> | Clear Recovery            | С, В                       |

| t <sub>DDROSUD1</sub>   | Data Setup Data_F         | A, B                       |

| t <sub>DDROSUD2</sub>   | Data Setup Data_R         | D, B                       |

| t <sub>DDROHD1</sub>    | Data Hold Data_F          | A, B                       |

| t <sub>DDROHD2</sub>    | Data Hold Data_R          | D, B                       |

**Microsemi**.

IGLOOe DC and Switching Characteristics

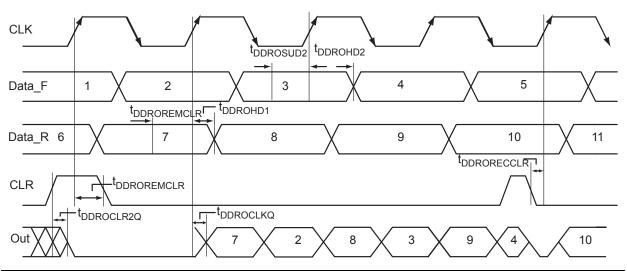

Figure 2-34 • Output DDR Timing Diagram

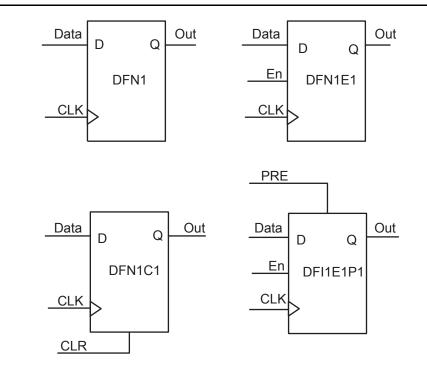

# VersaTile Specifications as a Sequential Module

The IGLOOe library offers a wide variety of sequential cells, including flip-flops and latches. Each has a data input and optional enable, clear, or preset. In this section, timing characteristics are presented for a representative sample from the library. For more details, refer to the *IGLOO*, *Fusion*, *and ProASIC3 Macro Library Guide*.

Figure 2-37 • Sample of Sequential Cells

### 1.2 V DC Core Voltage

#### Table 2-138 • Register Delays

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V

| Parameter           | Description                                                   | Std. | Units |

|---------------------|---------------------------------------------------------------|------|-------|

| t <sub>CLKQ</sub>   | Clock-to-Q of the Core Register                               | 1.61 | ns    |

| t <sub>SUD</sub>    | Data Setup Time for the Core Register                         | 1.17 | ns    |

| t <sub>HD</sub>     | Data Hold Time for the Core Register                          | 0.00 | ns    |

| t <sub>SUE</sub>    | Enable Setup Time for the Core Register                       | 1.29 | ns    |

| t <sub>HE</sub>     | Enable Hold Time for the Core Register                        | 0.00 | ns    |

| t <sub>CLR2Q</sub>  | Asynchronous Clear-to-Q of the Core Register                  | 0.87 | ns    |

| t <sub>PRE2Q</sub>  | Asynchronous Preset-to-Q of the Core Register                 | 0.89 | ns    |

| t <sub>REMCLR</sub> | Asynchronous Clear Removal Time for the Core Register         | 0.00 | ns    |

| t <sub>RECCLR</sub> | Asynchronous Clear Recovery Time for the Core Register        | 0.24 | ns    |

| t <sub>REMPRE</sub> | Asynchronous Preset Removal Time for the Core Register        | 0.00 | ns    |

| t <sub>RECPRE</sub> | Asynchronous Preset Recovery Time for the Core Register       | 0.24 | ns    |

| t <sub>WCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Core Register  | 0.46 | ns    |

| t <sub>WPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Core Register | 0.46 | ns    |

| t <sub>CKMPWH</sub> | Clock Minimum Pulse Width HIGH for the Core Register          | 0.95 | ns    |

| t <sub>CKMPWL</sub> | Clock Minimum Pulse Width LOW for the Core Register           | 0.95 | ns    |

# static Microsemi.

IGLOOe DC and Switching Characteristics

# **Timing Characteristics**

### Applies to 1.5 V DC Core Voltage

#### Table 2-145 • RAM4K9

### Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter                                                              | Description                                                                                                         | Std. | Units |

|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------|-------|

| t <sub>AS</sub>                                                        | Address Setup Time                                                                                                  | 0.83 | ns    |

| t <sub>AH</sub>                                                        | Address Hold Time                                                                                                   | 0.16 | ns    |

| t <sub>ENS</sub>                                                       | REN, WEN Setup Time                                                                                                 | 0.81 | ns    |

| t <sub>ENH</sub>                                                       | REN, WEN Hold Time                                                                                                  | 0.16 | ns    |

| t <sub>BKS</sub>                                                       | BLK Setup Time                                                                                                      | 1.65 | ns    |

| t <sub>вкн</sub>                                                       | BLK Hold Time                                                                                                       | 0.16 | ns    |

| t <sub>DS</sub>                                                        | Input Data (DIN) Setup Time                                                                                         | 0.71 | ns    |

| t <sub>DH</sub>                                                        | Input Data (DIN) Hold Time                                                                                          | 0.36 | ns    |

| CKQ1 Clock HIGH to New Data Valid on DOUT (output retained, WMODE = 0) |                                                                                                                     | 3.53 | ns    |

|                                                                        | Clock HIGH to New Data Valid on DOUT (flow-through, WMODE = 1)                                                      | 3.06 | ns    |

| t <sub>CKQ2</sub>                                                      | Clock HIGH to New Data Valid on DOUT (pipelined)                                                                    | 1.81 | ns    |

| t <sub>C2CWWL</sub> 1                                                  | Address collision clk-to-clk delay for reliable write after write on same address; applicable to closing edge       |      | ns    |

| t <sub>C2CRWH</sub> 1                                                  | Address collision clk-to-clk delay for reliable read access after write on same address; applicable to opening edge |      | ns    |

| t <sub>C2CWRH</sub> 1                                                  | Address collision clk-to-clk delay for reliable write access after read on same address; applicable to opening edge | 0.41 | ns    |

| t <sub>RSTBQ</sub>                                                     | RESET Low to Data Out Low on DOUT (flow-through)                                                                    | 2.06 | ns    |

|                                                                        | RESET Low to Data Out Low on DOUT (pipelined)                                                                       | 2.06 | ns    |

| t <sub>REMRSTB</sub>                                                   | RESET Removal                                                                                                       | 0.61 | ns    |

| t <sub>RECRSTB</sub>                                                   | RESET Recovery                                                                                                      | 3.21 | ns    |

| t <sub>MPWRSTB</sub>                                                   | RESET Minimum Pulse Width                                                                                           | 0.68 | ns    |

| t <sub>CYC</sub>                                                       | Clock Cycle Time                                                                                                    | 6.24 | ns    |

| F <sub>MAX</sub>                                                       | Maximum Frequency                                                                                                   | 160  | MHz   |

Notes:

1. For more information, refer to the application note Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs.

| Table 2-146 • RAM512X18                                                     |  |

|-----------------------------------------------------------------------------|--|

| Commercial-Case Conditions: T <sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V |  |

| Parameter             | Description                                                                                                         | Std. | Units |

|-----------------------|---------------------------------------------------------------------------------------------------------------------|------|-------|

| t <sub>AS</sub>       | Address Setup Time                                                                                                  | 0.83 | ns    |

| t <sub>AH</sub>       | Address Hold Time                                                                                                   | 0.16 | ns    |

| t <sub>ENS</sub>      | REN, WEN Setup Time                                                                                                 | 0.73 | ns    |

| t <sub>ENH</sub>      | REN, WEN Hold Time                                                                                                  | 0.08 | ns    |

| t <sub>DS</sub>       | Input Data (WD) Setup Time                                                                                          | 0.71 | ns    |

| t <sub>DH</sub>       | Input Data (WD) Hold Time                                                                                           | 0.36 | ns    |

| t <sub>CKQ1</sub>     | Clock HIGH to New Data Valid on RD (output retained, WMODE = 0)                                                     |      | ns    |

| t <sub>CKQ2</sub>     | Clock HIGH to New Data Valid on RD (pipelined)                                                                      |      | ns    |

| t <sub>C2CRWH</sub> 1 | Address collision clk-to-clk delay for reliable read access after write on same address; applicable to opening edge |      | ns    |

| t <sub>C2CWRH</sub> 1 | Address collision clk-to-clk delay for reliable write access after read on same address; applicable to opening edge |      | ns    |

| t <sub>RSTBQ</sub>    | RESET Low to Data Out Low on RD (flow-through)                                                                      | 2.06 | ns    |

|                       | RESET Low to Data Out Low on RD (pipelined)                                                                         | 2.06 | ns    |

| t <sub>REMRSTB</sub>  | RESET Removal                                                                                                       | 0.61 | ns    |

| t <sub>RECRSTB</sub>  | RESET Recovery                                                                                                      |      | ns    |

| t <sub>MPWRSTB</sub>  | RESET Minimum Pulse Width                                                                                           | 0.68 | ns    |

| t <sub>CYC</sub>      | Clock Cycle Time                                                                                                    | 6.24 | ns    |

| F <sub>MAX</sub>      | Maximum Frequency                                                                                                   | 160  | MHz   |

Notes:

1. For more information, refer to the application note Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs.

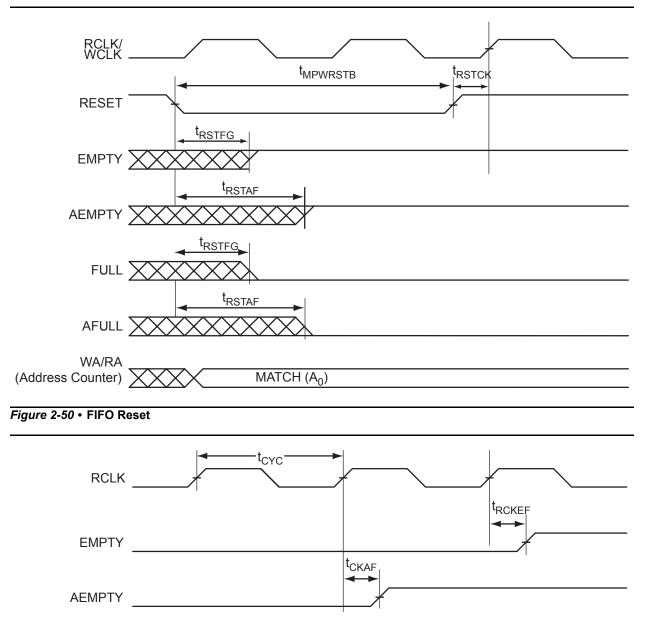

Figure 2-51 • FIFO EMPTY Flag and AEMPTY Flag Assertion

### Applies to 1.2 V DC Core Voltage

#### Table 2-150 • FIFO

Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.14 V

| Parameter            | Description                                       | Std.  | Units |

|----------------------|---------------------------------------------------|-------|-------|

| t <sub>ENS</sub>     | REN, WEN Setup Time                               | 4.13  | ns    |

| t <sub>ENH</sub>     | REN, WEN Hold Time                                | 0.31  | ns    |

| t <sub>BKS</sub>     | BLK Setup Time                                    | 0.47  | ns    |

| t <sub>BKH</sub>     | BLK Hold Time                                     | 0.00  | ns    |

| t <sub>DS</sub>      | Input Data (WD) Setup Time                        | 1.56  | ns    |

| t <sub>DH</sub>      | Input Data (WD) Hold Time                         | 0.49  | ns    |

| t <sub>CKQ1</sub>    | Clock HIGH to New Data Valid on RD (pass-through) | 6.80  | ns    |

| t <sub>CKQ2</sub>    | Clock HIGH to New Data Valid on RD (pipelined)    | 3.62  | ns    |

| t <sub>RCKEF</sub>   | RCLK HIGH to Empty Flag Valid                     | 7.23  | ns    |

| t <sub>WCKFF</sub>   | WCLK HIGH to Full Flag Valid                      | 6.85  | ns    |

| t <sub>CKAF</sub>    | Clock HIGH to Almost Empty/Full Flag Valid        | 26.61 | ns    |

| t <sub>RSTFG</sub>   | RESET LOW to Empty/Full Flag Valid                | 7.12  | ns    |

| t <sub>RSTAF</sub>   | RESET LOW to Almost Empty/Full Flag Valid         | 26.33 | ns    |

| t <sub>RSTBQ</sub>   | RESET LOW to Data Out LOW on RD (pass-through)    | 4.09  | ns    |

|                      | RESET LOW to Data Out LOW on RD (pipelined)       | 4.09  | ns    |

| t <sub>REMRSTB</sub> | RESET Removal                                     | 1.23  | ns    |

| t <sub>RECRSTB</sub> | RESET Recovery                                    | 6.58  | ns    |

| t <sub>MPWRSTB</sub> | RESET Minimum Pulse Width                         | 1.18  | ns    |

| t <sub>CYC</sub>     | Clock Cycle Time                                  | 10.90 | ns    |

| F <sub>MAX</sub>     | Maximum Frequency                                 | 92    | MHz   |

Pin Descriptions and Packaging

Table 3-1 shows the Flash\*Freeze pin location on the available packages. The Flash\*Freeze pin location is independent of device (except for a PQ208 package), allowing migration to larger or smaller IGLOO devices while maintaining the same pin location on the board. Refer to the "Flash\*Freeze Technology and Low Power Modes" chapter of the *IGLOOe FPGA Fabric User's Guide* for more information on I/O states during Flash\*Freeze mode.

| Table 3-1 | • Flash*Freeze | <b>Pin Locations</b> | for IGI OOe | Devices |

|-----------|----------------|----------------------|-------------|---------|

|           |                |                      |             |         |

| Package | Flash*Freeze Pin |

|---------|------------------|

| FG256   | Т3               |

| FG484   | W6               |

| FG896   | AH4              |

# **JTAG Pins**

Low power flash devices have a separate bank for the dedicated JTAG pins. The JTAG pins can be run at any voltage from 1.5 V to 3.3 V (nominal). VCC must also be powered for the JTAG state machine to operate, even if the device is in bypass mode; VJTAG alone is insufficient. Both VJTAG and VCC to the part must be supplied to allow JTAG signals to transition the device. Isolating the JTAG power supply in a separate I/O bank gives greater flexibility in supply selection and simplifies power supply and PCB design. If the JTAG interface is neither used nor planned for use, the VJTAG pin together with the TRST pin could be tied to GND.

#### тск

#### **Test Clock**

Test clock input for JTAG boundary scan, ISP, and UJTAG. The TCK pin does not have an internal pullup/-down resistor. If JTAG is not used, Microsemi recommends tying off TCK to GND through a resistor placed close to the FPGA pin. This prevents JTAG operation in case TMS enters an undesired state.

Note that to operate at all VJTAG voltages, 500  $\Omega$  to 1 k $\Omega$  will satisfy the requirements. Refer to Table 3-2 for more information.

| VJTAG          | Tie-Off Resistance <sup>1,2</sup> |

|----------------|-----------------------------------|

| VJTAG at 3.3 V | 200 $\Omega$ to 1 k $\Omega$      |

| VJTAG at 2.5 V | 200 $\Omega$ to 1 k $\Omega$      |

| VJTAG at 1.8 V | 500 $\Omega$ to 1 k $\Omega$      |

| VJTAG at 1.5 V | 500 Ω to 1 kΩ                     |

Table 3-2 • Recommended Tie-Off Values for the TCK and TRST Pins

Notes:

1. The TCK pin can be pulled-up or pulled-down.

2. The TRST pin is pulled-down.

3. Equivalent parallel resistance if more than one device is on the JTAG chain

|               | FG484             | FG484         |                   |  |

|---------------|-------------------|---------------|-------------------|--|

| Pin<br>Number | AGLE3000 Function | Pin<br>Number | AGLE3000 Function |  |

| V3            | GND               | W15           | GDC2/IO156PDB4V   |  |

| V4            | GEA1/IO234PDB6V0  | W16           | IO154NDB4V0       |  |

| V5            | GEA0/IO234NDB6V0  | W17           | GDA2/IO154PDB4V   |  |

| V6            | GNDQ              | W18           | TMS               |  |

| V7            | GEC2/IO231PDB5V4  | W19           | GND               |  |

| V8            | IO222NPB5V3       | W20           | IO150NDB3V4       |  |

| V9            | IO204NDB5V1       | W21           | IO146NDB3V4       |  |

| V10           | IO204PDB5V1       | W22           | IO148PPB3V4       |  |

| V11           | IO195NDB5V0       | Y1            | VCCIB6            |  |

| V12           | IO195PDB5V0       | Y2            | IO237NDB6V0       |  |

| V13           | IO178NDB4V3       | Y3            | IO228NDB5V4       |  |

| V14           | IO178PDB4V3       | Y4            | IO224NDB5V3       |  |

| V15           | IO155NDB4V0       | Y5            | GND               |  |

| V16           | GDB2/IO155PDB4V0  | Y6            | IO220NDB5V3       |  |

| V17           | TDI               | Y7            | IO220PDB5V3       |  |

| V18           | GNDQ              | Y8            | VCC               |  |

| V19           | TDO               | Y9            | VCC               |  |

| V20           | GND               | Y10           | IO200PDB5V0       |  |

| V21           | IO146PDB3V4       | Y11           | IO192PDB4V4       |  |

| V22           | IO142NDB3V3       | Y12           | IO188NPB4V4       |  |

| W1            | IO239NDB6V0       | Y13           | IO187PSB4V4       |  |

| W2            | IO237PDB6V0       | Y14           | VCC               |  |

| W3            | IO230PSB5V4       | Y15           | VCC               |  |

| W4            | GND               | Y16           | IO164NDB4V1       |  |

| W5            | IO232NDB5V4       | Y17           | IO164PDB4V1       |  |

| W6            | FF/GEB2/IO232PDB5 | Y18           | GND               |  |

|               | V4                | Y19           | IO158PPB4V0       |  |

| W7            | IO231NDB5V4       | Y20           | IO150PDB3V4       |  |

| W8            | IO214NDB5V2       | Y21           | IO148NPB3V4       |  |

| W9            | IO214PDB5V2       | Y22           | VCCIB3            |  |

| W10           | IO200NDB5V0       | <u> </u>      | 1                 |  |

| W11           | IO192NDB4V4       |               |                   |  |

| W12           | IO184NDB4V3       |               |                   |  |

| W13           | IO184PDB4V3       |               |                   |  |

|               |                   |               |                   |  |

W14

IO156NDB4V0

| FG896      |                      |            | FG896                |            | FG896                |

|------------|----------------------|------------|----------------------|------------|----------------------|

| Pin Number | AGLE3000<br>Function | Pin Number | AGLE3000<br>Function | Pin Number | AGLE3000<br>Function |

| D30        | GBA2/IO82PPB2V0      | F5         | VMV7                 | G7         | VCC                  |

| E1         | GND                  | F5         | VMV7                 | G8         | VMV0                 |

| E2         | IO303NPB7V3          | F6         | GND                  | G9         | VCCIB0               |

| E3         | VCCIB7               | F7         | GNDQ                 | G10        | IO10NDB0V1           |

| E4         | IO305PPB7V3          | F8         | IO12NDB0V1           | G11        | IO16NDB0V1           |

| E5         | VCC                  | F9         | IO12PDB0V1           | G12        | IO22PDB0V2           |

| E6         | GAC0/IO02NDB0V0      | F10        | IO10PDB0V1           | G13        | IO26PPB0V3           |

| E7         | VCCIB0               | F11        | IO16PDB0V1           | G14        | IO38NPB0V4           |

| E8         | IO06PPB0V0           | F12        | IO22NDB0V2           | G15        | IO36NDB0V4           |

| E9         | IO24NDB0V2           | F13        | IO30NDB0V3           | G16        | IO46NDB1V0           |

| E10        | IO24PDB0V2           | F14        | IO30PDB0V3           | G17        | IO46PDB1V0           |

| E11        | IO13NDB0V1           | F15        | IO36PDB0V4           | G18        | IO56NDB1V1           |

| E12        | IO13PDB0V1           | F16        | IO48NDB1V0           | G19        | IO56PDB1V1           |

| E13        | IO34NDB0V4           | F17        | IO48PDB1V0           | G20        | IO66NDB1V3           |

| E14        | IO34PDB0V4           | F18        | IO50NDB1V1           | G21        | IO66PDB1V3           |

| E15        | IO40NDB0V4           | F19        | IO58NDB1V2           | G22        | VCCIB1               |

| E16        | IO49NDB1V1           | F20        | IO60PDB1V2           | G23        | VMV1                 |

| E17        | IO49PDB1V1           | F21        | IO77NDB1V4           | G24        | VCC                  |

| E18        | IO50PDB1V1           | F22        | IO72NDB1V3           | G25        | GNDQ                 |

| E19        | IO58PDB1V2           | F23        | IO72PDB1V3           | G25        | GNDQ                 |

| E20        | IO60NDB1V2           | F24        | GNDQ                 | G26        | VCCIB2               |

| E21        | IO77PDB1V4           | F25        | GND                  | G27        | IO86NDB2V0           |

| E22        | IO68NDB1V3           | F26        | VMV2                 | G28        | IO92NDB2V1           |

| E23        | IO68PDB1V3           | F26        | VMV2                 | G29        | IO100PPB2V2          |

| E24        | VCCIB1               | F27        | IO86PDB2V0           | G30        | GND                  |

| E25        | IO74PDB1V4           | F28        | IO92PDB2V1           | H1         | IO294PDB7V2          |

| E26        | VCC                  | F29        | VCC                  | H2         | IO294NDB7V2          |

| E27        | GBB1/IO80PPB1V4      | F30        | IO100NPB2V2          | H3         | IO300NDB7V3          |

| E28        | VCCIB2               | G1         | GND                  | H4         | IO300PDB7V3          |

| E29        | IO82NPB2V0           | G2         | IO296NPB7V2          | H5         | IO295PDB7V2          |

| E30        | GND                  | G3         | IO306NDB7V4          | H6         | IO299PDB7V3          |

| F1         | IO296PPB7V2          | G4         | IO297NDB7V2          | H7         | VCOMPLA              |

| F2         | VCC                  | G5         | VCCIB7               | H8         | GND                  |

| F3         | IO306PDB7V4          | G6         | GNDQ                 | H9         | IO08NDB0V0           |

| F4         | IO297PDB7V2          | G6         | GNDQ                 | H10        | IO08PDB0V0           |

Datasheet Information

| Revision                                    | Changes                                                                                                                                                                                                                                                                                                        | Page   |  |  |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|--|

| Revision 3 (cont'd)                         | Table 2-14 • Summary of I/O Output Buffer Power (per pin) – Default I/O Software Settings1 was updated to change PDC3 to PDC7. The table notes were updated to reflect that power was measured on VCCI. Table note 4 is new.                                                                                   |        |  |  |

|                                             | Table 2-16 • Different Components Contributing to the Static Power Consumption<br>in IGLOO Devices and Table 2-18 • Different Components Contributing to the<br>Static Power Consumption in IGLOO Devices were updated to add PDC6 and<br>PDC7, and to change the definition for PDC5 to bank quiescent power. |        |  |  |

|                                             | A table subtitle was added for Table 2-18 • Different Components Contributing to the Static Power Consumption in IGLOO Devices.                                                                                                                                                                                |        |  |  |

|                                             | The "Total Static Power Consumption—PSTAT" section was updated to revise the calculation of P <sub>STAT</sub> , including PDC6 and PDC7.                                                                                                                                                                       |        |  |  |

|                                             | Footnote 1 was updated to include information about $P_{AC13}$ . The PLL Contribution equation was changed from: $P_{PLL} = P_{AC13} + P_{AC14} * FCLKOUT$ to PPLL = $P_{DC4} + P_{AC13} * F_{CLKOUT}$ .                                                                                                       | 2-14   |  |  |

|                                             | The "Timing Model" was updated to be consistent with the revised timing numbers.                                                                                                                                                                                                                               | 2-16   |  |  |

|                                             | In Table 2-22 $\bullet$ Summary of Maximum and Minimum DC Input Levels, $T_J$ was changed to $T_A$ in notes 1 and 2.                                                                                                                                                                                           | 2-22   |  |  |

|                                             | Table 2-22 • Summary of Maximum and Minimum DC Input Levels was updated to included a hysteresis value for 1.2 V LVCMOS (Schmitt trigger mode).                                                                                                                                                                | 2-22   |  |  |

|                                             | All AC Loading figures for single-ended I/O standards were changed from Datapaths at 35 pF to 5 pF.                                                                                                                                                                                                            | N/A    |  |  |

|                                             | The "1.2 V LVCMOS (JESD8-12A)" section is new.                                                                                                                                                                                                                                                                 | 2-47   |  |  |

| Revision 2 (Jun 2008)<br>Product Brief v1.0 | The product brief section of the datasheet was divided into two sections and given a version number, starting at v1.0. The first section of the document includes features, benefits, ordering information, and temperature and speed grade offerings. The second section is a device family overview.         |        |  |  |

| Revision 2 (cont'd)<br>Packaging v1.1       | The naming conventions changed for the following pins in the "FG484" for the<br>A3GLE600:Pin NumberNew Function NameJ19IO45PPB2V1K20IO45NPB2V1M2IO114NPB6V1N1IO114PPB6V1N4GFC2/IO115PPB6V1P3IO115NPB6V1                                                                                                        | 4-6    |  |  |

| Revision 1 (Mar 2008)                       | The "Low Power" section was updated to change "1.2 V and 1.5 V Core Voltage"                                                                                                                                                                                                                                   |        |  |  |

| Product Brief rev. 1                        | to "1.2 V and 1.5 V Core and I/O Voltage." The text "(from 25 $\mu$ W)" was removed from "Low Power Active FPGA Operation."                                                                                                                                                                                    |        |  |  |

|                                             | 1.2_V was added to the list of core and I/O voltages in the "Pro (Professional) I/O" and "Pro I/Os with Advanced I/O Standards" section sections.                                                                                                                                                              | I, 1-7 |  |  |

| Revision 0 (Jan 2008)                       | This document was previously in datasheet Advance v0.4. As a result of moving to the handbook format, Actel has restarted the version numbers. The new version number is 51700096-001-0.                                                                                                                       | N/A    |  |  |