Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                   |

|--------------------------------|-------------------------------------------------------------------|

| Product Status                 | Obsolete                                                          |

| Number of LABs/CLBs            | -                                                                 |

| Number of Logic Elements/Cells | 75264                                                             |

| Total RAM Bits                 | 516096                                                            |

| Number of I/O                  | 620                                                               |

| Number of Gates                | 3000000                                                           |

| Voltage - Supply               | 1.14V ~ 1.575V                                                    |

| Mounting Type                  | Surface Mount                                                     |

| Operating Temperature          | -40°C ~ 85°C (TA)                                                 |

| Package / Case                 | 896-BGA                                                           |

| Supplier Device Package        | 896-FBGA (31x31)                                                  |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/agle3000v2-fgg896i |

|                                |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Temperature Grade Offerings**

|         | AGLE600 | AGLE3000    |

|---------|---------|-------------|

| Package |         | M1AGLPE3000 |

| FG256   | C, I    | -           |

| FG484   | C, I    | C, I        |

| FG896   | _       | C, I        |

*Note:* C = Commercial temperature range: 0°C to 70°C ambient temperature.<math>I = Industrial temperature range: -40°C to 85°C ambient temperature.

References made to IGLOOe devices also apply to ARM-enabled IGLOOe devices. The ARM-enabled part numbers start with M1 (Cortex-M1).

Contact your local Microsemi SoC Products Group representative for device availability:

http://www.microsemi.com/soc/contact/default.aspx.

# **Calculating Power Dissipation**

## **Quiescent Supply Current**

Quiescent supply current (IDD) calculation depends on multiple factors, including operating voltages (VCC, VCCI, and VJTAG), operating temperature, system clock frequency, and power modes usage. Microsemi recommends using the PowerCalculator and SmartPower software estimation tools to evaluate the projected static and active power based on the user design, power mode usage, operating voltage, and temperature.

#### Table 2-8 • Power Supply State per Mode

|                      | Power Supply Configurations |        |      |       |                 |  |  |  |  |  |  |

|----------------------|-----------------------------|--------|------|-------|-----------------|--|--|--|--|--|--|

| Modes/power supplies | VCC                         | VCCPLL | VCCI | VJTAG | VPUMP           |  |  |  |  |  |  |

| Flash*Freeze         | On                          | On     | On   | On    | On/off/floating |  |  |  |  |  |  |

| Sleep                | Off                         | Off    | On   | Off   | Off             |  |  |  |  |  |  |

| Shutdown             | Off                         | Off    | Off  | Off   | Off             |  |  |  |  |  |  |

| No Flash*Freeze      | On                          | On     | On   | On    | On/off/floating |  |  |  |  |  |  |

*Note:* Off: Power supply level = 0 V

#### Table 2-9 • Quiescent Supply Current (IDD), IGLOOe Flash\*Freeze Mode\*

|                | Core Voltage | AGLE600 | AGLE3000 | Units |

|----------------|--------------|---------|----------|-------|

| Typical (25°C) | 1.2 V        | 34      | 95       | μΑ    |

|                | 1.5 V        | 72      | 310      | μA    |

Note: \*IDD includes VCC, VPUMP, VCCI, VCCPLL, and VMV currents. Values do not include I/O static contribution, which is shown in Table 2-13 on page 2-9 and Table 2-14 on page 2-10 (PDC6 and PDC7).

#### Table 2-10 • Quiescent Supply Current (IDD) Characteristics, IGLOOe Sleep Mode\*

|                                                 | Core Voltage  | AGLE600 | AGLE3000 | Units |

|-------------------------------------------------|---------------|---------|----------|-------|

| VCCI/VJTAG = 1.2 V (per bank)<br>Typical (25°C) | 1.2 V         | 1.7     | 1.7      | μA    |

| VCCI/VJTAG = 1.5 V (per bank)<br>Typical (25°C) | 1.2 V / 1.5 V | 1.8     | 1.8      | μA    |

| VCCI/VJTAG = 1.8 V (per bank)<br>Typical (25°C) | 1.2 V / 1.5 V | 1.9     | 1.9      | μA    |

| VCCI/VJTAG = 2.5 V (per bank)<br>Typical (25°C) | 1.2 V / 1.5 V | 2.2     | 2.2      | μA    |

| VCCI/VJTAG= 3.3 V (per bank)<br>Typical (25°C)  | 1.2 V / 1.5 V | 2.5     | 2.5      | μA    |

Note:  $*IDD = N_{BANKS} \times ICCI$ . Values do not include I/O static contribution, which is shown in Table 2-13 on page 2-9 and Table 2-14 on page 2-10 (PDC6 and PDC7).

#### Table 2-11 • Quiescent Supply Current (IDD) Characteristics, IGLOOe Shutdown Mode\*

|                | Core Voltage  | AGLE600 | AGLE3000 | Units |

|----------------|---------------|---------|----------|-------|

| Typical (25°C) | 1.2 V / 1.5 V | 0       | 0        | μA    |

IGLOOe DC and Switching Characteristics

#### Combinatorial Cells Contribution—P<sub>C-CELL</sub>

$P_{C-CELL} = N_{C-CELL} * \alpha_1 / 2 * PAC7 * F_{CLK}$

N<sub>C-CELL</sub> is the number of VersaTiles used as combinatorial modules in the design.

$\alpha_{1}$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 2-19 on page 2-15.

$\mathsf{F}_{\mathsf{CLK}}$  is the global clock signal frequency.

### Routing Net Contribution—P<sub>NET</sub>

$\mathsf{P}_{\mathsf{NET}} = (\mathsf{N}_{\mathsf{S}\text{-}\mathsf{CELL}} + \mathsf{N}_{\mathsf{C}\text{-}\mathsf{CELL}}) * \alpha_1 / 2 * \mathsf{PAC8} * \mathsf{F}_{\mathsf{CLK}}$

N<sub>S-CELL</sub> is the number of VersaTiles used as sequential modules in the design.

$N_{C\text{-}CELL}$  is the number of VersaTiles used as combinatorial modules in the design.

$\alpha_1$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 2-19 on page 2-15.

F<sub>CLK</sub> is the global clock signal frequency.

#### I/O Input Buffer Contribution—PINPUTS

$P_{INPUTS}$  =  $N_{INPUTS}$  \*  $\alpha_2$  / 2 \* PAC9 \*  $F_{CLK}$

N<sub>INPUTS</sub> is the number of I/O input buffers used in the design.

$\alpha_2$  is the I/O buffer toggle rate—guidelines are provided in Table 2-19 on page 2-15.

F<sub>CLK</sub> is the global clock signal frequency.

#### I/O Output Buffer Contribution—POUTPUTS

$P_{OUTPUTS} = N_{OUTPUTS} * \alpha_2 / 2 * \beta_1 * PAC10 * F_{CLK}$

$N_{\mbox{OUTPUTS}}$  is the number of I/O output buffers used in the design.

$\alpha_2$  is the I/O buffer toggle rate—guidelines are provided in Table 2-19 on page 2-15.

$\beta_1$  is the I/O buffer enable rate—guidelines are provided in Table 2-20 on page 2-15.

F<sub>CLK</sub> is the global clock signal frequency.

#### RAM Contribution—P<sub>MEMORY</sub>

$\mathsf{P}_{\mathsf{MEMORY}} = \mathsf{PAC11} * \mathsf{N}_{\mathsf{BLOCKS}} * \mathsf{F}_{\mathsf{READ-CLOCK}} * \beta_2 + \mathsf{PAC12} * \mathsf{N}_{\mathsf{BLOCK}} * \mathsf{F}_{\mathsf{WRITE-CLOCK}} * \beta_3$

$N_{\mbox{\scriptsize BLOCKS}}$  is the number of RAM blocks used in the design.

F<sub>READ-CLOCK</sub> is the memory read clock frequency.

$\beta_2$  is the RAM enable rate for read operations—guidelines are provided in Table 2-20 on page 2-15.

F<sub>WRITE-CLOCK</sub> is the memory write clock frequency.

$\beta_3$  is the RAM enable rate for write operations—guidelines are provided in Table 2-20 on page 2-15.

## PLL Contribution—P<sub>PLL</sub>

P<sub>PLL</sub> = PDC4 + PAC13 \* F<sub>CLKOUT</sub>

F<sub>CLKOUT</sub> is the output clock frequency.<sup>1</sup>

If a PLL is used to generate more than one output clock, include each output clock in the formula by adding its corresponding contribution (P<sub>AC13</sub>\* F<sub>CLKOUT</sub> product) to the total PLL contribution.

# 🌜 Microsemi.

IGLOOe DC and Switching Characteristics

# Table 2-26 • Summary of I/O Timing Characteristics—Software Default SettingsStd. Speed Grade, Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V,Worst-Case VCCI (per standard)

| I/O Standard                              | Drive Strength (mA)  | Equivalent Software Default<br>Drive Strength Option <sup>1</sup> (mA) | Slew Rate | Capacitive Load (pF) | External Resistor ( $\Omega$ ) | t <sub>bout</sub> (ns) | t <sub>DP</sub> (ns) | t <sub>DIN</sub> (ns) | t <sub>pY</sub> (ns) | t <sub>PYS</sub> (ns) | t <sub>Eour</sub> (ns) | t <sub>ZL</sub> (ns) | t <sub>ZH</sub> (ns) | t <sub>LZ</sub> (ns) | t <sub>HZ</sub> (ns) | t <sub>ZLS</sub> (ns) | t <sub>ZHS</sub> (ns) | Units |

|-------------------------------------------|----------------------|------------------------------------------------------------------------|-----------|----------------------|--------------------------------|------------------------|----------------------|-----------------------|----------------------|-----------------------|------------------------|----------------------|----------------------|----------------------|----------------------|-----------------------|-----------------------|-------|

| 3.3 V LVTTL /<br>3.3 V LVCMOS             | 12                   | 12                                                                     | High      | 5                    | -                              | 1.55                   | 2.47                 | 0.26                  | 1.31                 | 1.58                  | 1.10                   | 2.51                 | 2.04                 | 3.28                 | 3.97                 | 8.29                  | 7.82                  | ns    |

| 3.3 V LVCMOS<br>Wide Range <sup>1,2</sup> | 100 µA               | 12                                                                     | High      | 35                   | -                              | 1.55                   | 3.40                 | 0.26                  | 1.66                 | 2.14                  | 1.10                   | 3.40                 | 2.68                 | 4.55                 | 5.49                 | 9.19                  | 8.46                  | ns    |

| 2.5 V LVCMOS                              | 12                   | 12                                                                     | High      | 5                    | -                              | 1.55                   | 2.51                 | 0.26                  | 1.55                 | 1.77                  | 1.10                   | 2.54                 | 2.22                 | 3.36                 | 3.85                 | 8.33                  | 8.00                  | ns    |

| 1.8 V LVCMOS                              | 12                   | 12                                                                     | High      | 5                    | -                              | 1.55                   | 2.75                 | 0.26                  | 1.53                 | 1.96                  | 1.10                   | 2.78                 | 2.40                 | 3.68                 | 4.56                 | 8.57                  | 8.19                  | ns    |

| 1.5 V LVCMOS                              | 12                   | 12                                                                     | High      | 5                    | -                              | 1.55                   | 3.10                 | 0.26                  | 1.72                 | 2.16                  | 1.10                   | 3.15                 | 2.70                 | 3.86                 | 4.68                 | 8.93                  | 8.49                  | ns    |

| 1.2 V LVCMOS                              | 2                    | 2                                                                      | High      | 5                    | -                              | 1.55                   | 4.06                 | 0.26                  | 2.09                 | 2.95                  | 1.10                   | 3.92                 | 3.46                 | 4.01                 | 3.79                 | 9.71                  | 9.24                  | ns    |

| 1.2 V LVCMOS<br>Wide Range <sup>1,3</sup> | 100 µA               | 2                                                                      | High      | 5                    | Ι                              | 1.55                   | 4.06                 | 0.26                  | 2.09                 | 2.95                  | 1.10                   | 3.92                 | 3.46                 | 4.01                 | 3.79                 | 9.71                  | 9.24                  | ns    |

| 3.3 V PCI                                 | Per PCI<br>spec      | -                                                                      | High      | 10                   | 25 <sup>4</sup>                | 1.55                   | 2.76                 | 0.26                  | 1.19                 | 1.63                  | 1.10                   | 2.79                 | 2.16                 | 3.29                 | 3.97                 | 8.58                  | 7.94                  | ns    |

| 3.3 V PCI-X                               | Per<br>PCI-X<br>spec | -                                                                      | High      | 10                   | 25 <sup>4</sup>                | 1.55                   | 2.76                 | 0.25                  | 1.22                 | 1.58                  | 1.10                   | 2.79                 | 2.16                 | 3.29                 | 3.97                 | 8.58                  | 7.94                  | ns    |

| 3.3 V GTL                                 | 20 <sup>5</sup>      | -                                                                      | High      | 10                   | 25                             | 1.55                   | 2.08                 | 0.25                  | 2.76                 | -                     | 1.10                   | 2.09                 | 2.08                 | -                    | _                    | 7.88                  | 7.87                  | ns    |

| 2.5 V GTL                                 | 20 <sup>5</sup>      | -                                                                      | High      | 10                   | 25                             | 1.55                   | 2.17                 | 0.25                  | 2.35                 | -                     | 1.10                   | 2.20                 | 2.13                 | -                    | -                    | 7.99                  | 7.91                  | ns    |

| 3.3 V GTL+                                | 35                   | —                                                                      | High      | 10                   | 25                             | 1.55                   | 2.12                 | 0.25                  | 1.62                 | -                     | 1.10                   | 2.14                 | 2.07                 | _                    | -                    | 7.93                  | 7.85                  | ns    |

| 2.5 V GTL+                                | 33                   | -                                                                      | High      | 10                   | 25                             | 1.55                   | 2.25                 | 0.25                  | 1.55                 | -                     | 1.10                   | 2.27                 | 2.10                 | _                    | 1                    | 8.06                  | 7.89                  | ns    |

| HSTL (I)                                  | 8                    | -                                                                      | High      | 20                   | 50                             | 1.55                   | 3.09                 | 0.25                  | 1.95                 | -                     | 1.10                   | 3.11                 | 3.09                 | -                    | I                    | 8.90                  | 8.88                  | ns    |

| HSTL (II)                                 | 15                   | —                                                                      | High      | 20                   | 25                             | 1.55                   | 2.94                 | 0.25                  | 1.95                 | -                     |                        | 2.98                 |                      | -                    | -                    | 8.77                  | 8.53                  | ns    |

| SSTL2 (I)                                 | 15                   | _                                                                      | High      | 30                   | 50                             | 1.55                   | 2.18                 | 0.25                  | 1.40                 | -                     | 1.10                   | 2.21                 | 2.03                 | -                    | Ι                    | 7.99                  | 7.82                  | ns    |

| SSTL2 (II)                                | 18                   | -                                                                      | High      | 30                   | 25                             | 1.55                   | 2.21                 | 0.25                  | 1.40                 | -                     | 1.10                   | 2.24                 | 1.97                 | -                    | 1                    | 8.03                  | 7.76                  | ns    |

| SSTL3 (I)                                 | 14                   | —                                                                      | High      | 30                   | 50                             |                        | 2.33                 |                       | 1.33                 | -                     |                        | 2.36                 |                      | -                    | Ι                    | 8.15                  |                       | ns    |

| SSTL3 (II)                                | 21                   | _                                                                      | High      | 30                   | 25                             | 1.55                   | 2.13                 | 0.25                  | 1.33                 | _                     | 1.10                   | 2.16                 | 1.89                 | _                    | I                    | 7.94                  | 7.67                  | ns    |

Notes:

The minimum drive strength for any LVCMOS 1.2 V or LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

2. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8-B specification.

3. All LVCMOS 1.2 V software macros support LVCMOS 1.2 V wide range as specified in the JESD8-12 specification.

4. Resistance is used to measure I/O propagation delays as defined in PCI specifications. See Figure 2-12 on page 2-49 for connectivity. This resistor is not required during normal operation.

5. Output drive strength is below JEDEC specification.

# Table 2-26 • Summary of I/O Timing Characteristics—Software Default Settings (continued)Std. Speed Grade, Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V,Worst-Case VCCI (per standard)

| I/O Standard | Drive Strength (mA) | Equivalent Software Default<br>Drive Strength Option <sup>1</sup> (mA) | w Rate | Capacitive Load (pF) | External Resistor (Ω) | t <sub>DOUT</sub> (ns) | t <sub>DP</sub> (ns) | t <sub>DIN</sub> (ns) | t <sub>PΥ</sub> (ns) | t <sub>PYS</sub> (ns) | t <sub>EOUT</sub> (ns) | t <sub>ZL</sub> (ns) | t <sub>zH</sub> (ns) | t <sub>LZ</sub> (ns) | t <sub>HZ</sub> (ns) | t <sub>ZLS</sub> (ns) | t <sub>ZHS</sub> (ns) | Units |

|--------------|---------------------|------------------------------------------------------------------------|--------|----------------------|-----------------------|------------------------|----------------------|-----------------------|----------------------|-----------------------|------------------------|----------------------|----------------------|----------------------|----------------------|-----------------------|-----------------------|-------|

| LVDS         | 24                  | -                                                                      | High   | -                    | _                     | 1.55                   | 2.26                 | 0.25                  | 1.95                 | -                     | —                      | —                    | _                    | —                    | —                    | _                     | -                     | ns    |

| LVPECL       | 24                  | -                                                                      | High   | _                    | -                     | 1.55                   | 2.17                 | 0.25                  | 1.70                 | -                     | _                      | -                    | _                    | _                    | _                    | _                     | -                     | ns    |

Notes:

The minimum drive strength for any LVCMOS 1.2 V or LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

2. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8-B specification.

3. All LVCMOS 1.2 V software macros support LVCMOS 1.2 V wide range as specified in the JESD8-12 specification.

4. Resistance is used to measure I/O propagation delays as defined in PCI specifications. See Figure 2-12 on page 2-49 for connectivity. This resistor is not required during normal operation.

5. Output drive strength is below JEDEC specification.

#### Timing Characteristics

#### 1.5 V DC Core Voltage

Table 2-36 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew – Applies to 1.5 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

| Drive Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Unit<br>s |

|----------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-----------|

| 4 mA           | Std.           | 0.97              | 4.90            | 0.18             | 1.08            | 1.34             | 0.66              | 5.00            | 3.99            | 2.27            | 2.16            | 8.60             | 7.59             | ns        |

| 8 mA           | Std.           | 0.97              | 4.05            | 0.18             | 1.08            | 1.34             | 0.66              | 4.13            | 3.45            | 2.53            | 2.65            | 7.73             | 7.05             | ns        |

| 12 mA          | Std.           | 0.97              | 3.44            | 0.18             | 1.08            | 1.34             | 0.66              | 3.51            | 3.05            | 2.71            | 2.95            | 7.11             | 6.64             | ns        |

| 16 mA          | Std.           | 0.97              | 3.27            | 0.18             | 1.08            | 1.34             | 0.66              | 3.34            | 2.96            | 2.74            | 3.04            | 6.93             | 6.55             | ns        |

| 24 mA          | Std.           | 0.97              | 3.18            | 0.18             | 1.08            | 1.34             | 0.66              | 3.24            | 2.97            | 2.79            | 3.36            | 6.84             | 6.56             | ns        |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

## Table 2-37 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 4 mA           | Std.        | 0.97              | 2.85            | 0.18             | 1.08            | 1.34             | 0.66              | 2.92            | 2.27            | 2.27            | 2.27            | 6.51             | 5.87             | ns    |

| 8 mA           | Std.        | 0.97              | 2.39            | 0.18             | 1.08            | 1.34             | 0.66              | 2.44            | 1.88            | 2.53            | 2.76            | 6.03             | 5.47             | ns    |

| 12 mA          | Std.        | 0.97              | 2.12            | 0.18             | 1.08            | 1.34             | 0.66              | 2.17            | 1.69            | 2.71            | 3.08            | 5.76             | 5.28             | ns    |

| 16 mA          | Std.        | 0.97              | 2.08            | 0.18             | 1.08            | 1.34             | 0.66              | 2.12            | 1.65            | 2.75            | 3.17            | 5.72             | 5.25             | ns    |

| 24 mA          | Std.        | 0.97              | 2.10            | 0.18             | 1.08            | 1.34             | 0.66              | 2.14            | 1.60            | 2.80            | 3.49            | 5.74             | 5.20             | ns    |

Notes:

1. Software default selection highlighted in gray.

## 2.5 V GTL

Gunning Transceiver Logic is a high-speed bus standard (JESD8-3). It provides a differential amplifier input buffer and an open-drain output buffer. The VCCI pin should be connected to 2.5 V.

| Table 2-77 • | Minimum and Maximum DC Input and Output Levels |

|--------------|------------------------------------------------|

|--------------|------------------------------------------------|

| 2.5 GTL            |           | VIL         | VIH              |     | VOL       | VOH       | IOL | IOH | IOSH                    | IOSL                    | IIL¹            | IIH <sup>2</sup> |

|--------------------|-----------|-------------|------------------|-----|-----------|-----------|-----|-----|-------------------------|-------------------------|-----------------|------------------|

| Drive<br>Strength  | Min.<br>V | Max.<br>V   | Min. Max.<br>V V |     | Max.<br>V | Min.<br>V | mA  | mA  | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup> | μA <sup>4</sup>  |

| 20 mA <sup>5</sup> | -0.3      | VREF – 0.05 | VREF + 0.05      | 3.6 | 0.4       | _         | 20  | 20  | 169                     | 124                     | 10              | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operating conditions where -0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

5. Output drive strength is below JEDEC specification.

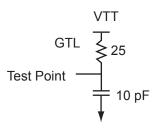

#### Figure 2-14 • AC Loading

#### Table 2-78 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------------------|

| VREF – 0.05   | VREF + 0.05    | 0.8                  | 0.8             | 1.2            | 10                     |

Note: \*Measuring point = Vtrip. See Table 2-23 on page 2-23 for a complete table of trip points.

#### Timing Characteristics

#### 1.5 V DC Core Voltage

#### Table 2-79 • 2.5 V GTL – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V VREF = 0.8 V

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.        | 0.98              | 1.90            | 0.19             | 2.04            | 0.67              | 1.94            | 1.87            |                 |                 | 5.57             | 5.50             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### 1.2 V DC Core Voltage

#### Table 2-80 • 2.5 V GTL – Applies to 1.2 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 3.0 V VREF = 0.8 V

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.        | 1.55              | 2.16            | 0.26             | 2.35            | 1.10              | 2.20            | 2.13            |                 |                 | 8.01             | 7.94             | ns    |

# 🌜 Microsemi.

IGLOOe DC and Switching Characteristics

## HSTL Class I

High-Speed Transceiver Logic is a general-purpose high-speed 1.5 V bus standard (EIA/JESD8-6). IGLOOe devices support Class I. This provides a differential amplifier input buffer and a push-pull output buffer.

| Table 2-89 • | Minimum and Maximum DC Input and Output Levels |

|--------------|------------------------------------------------|

|--------------|------------------------------------------------|

| HSTL Class        |           | VIL        | VIH        |           | VOL       | VOH      |    | ЮН | IOSH                    | IOSL | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-------------------|-----------|------------|------------|-----------|-----------|----------|----|----|-------------------------|------|------------------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.     | mA |    | Max.<br>mA <sup>3</sup> | Max. |                  | μA <sup>4</sup>  |

| 8 mA              | -0.3      | VREF – 0.1 | VREF + 0.1 | 3.6       | 0.4       | VCCI-0.4 | 8  | 8  | 32                      | 39   | 10               | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operating conditions where -0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

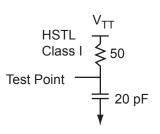

#### Figure 2-17 • AC Loading

#### Table 2-90 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------------------|

| VREF – 0.1    | VREF + 0.1     | 0.75                 | 0.75            | 0.75           | 20                     |

Note: \*Measuring point = Vtrip. See Table 2-23 on page 2-23 for a complete table of trip points.

#### Timing Characteristics

#### 1.5 V DC Core Voltage

Table 2-91 •HSTL Class I – Applies to 1.5 V DC Core Voltage<br/>Commercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V,<br/>Worst-Case VCCI = 1.4 V VREF = 0.75 V

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.        | 0.98              | 2.74            | 0.19             | 1.77            | 0.67              | 2.79            | 2.73            |                 |                 | 6.42             | 6.36             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### 1.2 V DC Core Voltage

# Table 2-92 • HSTL Class I – Applies to 1.2 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 1.4 V VREF = 0.75 V

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.        | 1.55              | 3.10            | 0.26             | 1.94            | 1.10              | 3.12            | 3.10            |                 |                 | 8.93             | 8.91             | ns    |

## SSTL2 Class II

Stub-Speed Terminated Logic for 2.5 V memory bus standard (JESD8-9). IGLOOe devices support Class II. This provides a differential amplifier input buffer and a push-pull output buffer.

| SSTL2<br>Class II |           | VIL        | VIH        |           | VOL       | VOH         | IOL | юн | IOSH                    | IOSL                    | IIL¹            | IIH <sup>2</sup> |

|-------------------|-----------|------------|------------|-----------|-----------|-------------|-----|----|-------------------------|-------------------------|-----------------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V   | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup> | μA⁴              |

| 18 mA             | -0.3      | VREF – 0.2 | VREF + 0.2 | 3.6       | 0.35      | VCCI - 0.43 | 18  | 18 | 169                     | 124                     | 10              | 10               |

Table 2-101 • Minimum and Maximum DC Input and Output Levels

Notes:

1. IIL is the input leakage current per I/O pin over recommended operating conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

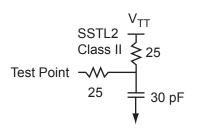

#### Figure 2-20 • AC Loading

#### Table 2-102 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input HIGH (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------------------|

| VREF – 0.2    | VREF + 0.2     | 1.25                 | 1.25            | 1.25           | 30                     |

Note: \*Measuring point = Vtrip. See Table 2-23 on page 2-23 for a complete table of trip points.

#### Timing Characteristics

1.5 V DC Core Voltage

#### Table 2-103 • SSTL 2 Class II – Applies to 1.5 V DC Core Voltage

```

Commercial-Case Conditions: T_J = 70^{\circ}C, Worst-Case VCC = 1.425 V,

```

Worst-Case VCCI = 2.3 V VREF = 1.25 V

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.        | 0.98              | 1.94            | 0.19             | 1.15            | 0.67              | 1.97            | 1.66            |                 |                 | 5.60             | 5.29             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### 1.2 V DC Core Voltage

#### Table 2-104 • SSTL 2 Class II – Applies to 1.2 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 2.3 V VREF = 1.25 V

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.        | 1.55              | 2.20            | 0.26             | 1.39            | 1.10              | 2.24            | 1.97            |                 |                 | 8.05             | 7.78             | ns    |

# **Microsemi**.

IGLOOe DC and Switching Characteristics

## B-LVDS/M-LVDS

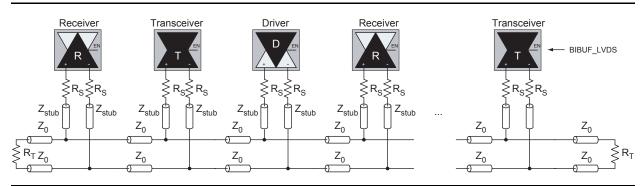

Bus LVDS (B-LVDS) and Multipoint LVDS (M-LVDS) specifications extend the existing LVDS standard to high-performance multipoint bus applications. Multidrop and multipoint bus configurations may contain any combination of drivers, receivers, and transceivers. Microsemi LVDS drivers provide the higher drive current required by B-LVDS and M-LVDS to accommodate the loading. The drivers require series terminations for better signal quality and to control voltage swing. Termination is also required at both ends of the bus since the driver can be located anywhere on the bus. These configurations can be implemented using the TRIBUF\_LVDS and BIBUF\_LVDS macros along with appropriate terminations. Multipoint designs using Microsemi LVDS macros can achieve up to 200 MHz with a maximum of 20 loads. A sample application is given in Figure 2-24. The input and output buffer delays are available in the LVDS section in Table 2-115 on page 2-63 and Table 2-116 on page 2-63.

Example: For a bus consisting of 20 equidistant loads, the following terminations provide the required differential voltage, in worst-case Industrial operating conditions, at the farthest receiver:  $R_S = 60 \Omega$  and  $R_T = 70 \Omega$ , given  $Z_0 = 50 \Omega$  (2") and  $Z_{stub} = 50 \Omega$  (~1.5").

Figure 2-24 • B-LVDS/M-LVDS Multipoint Application Using LVDS I/O Buffers

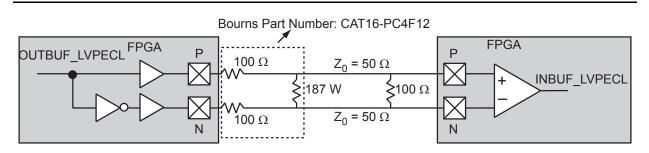

## LVPECL

Low-Voltage Positive Emitter-Coupled Logic (LVPECL) is another differential I/O standard. It requires that one data bit be carried through two signal lines. Like LVDS, two pins are needed. It also requires external resistor termination.

The full implementation of the LVDS transmitter and receiver is shown in an example in Figure 2-25. The building blocks of the LVPECL transmitter-receiver are one transmitter macro, one receiver macro, three board resistors at the transmitter end, and one resistor at the receiver end. The values for the three driver resistors are different from those used in the LVDS implementation because the output standard specifications are different.

| DC Parameter | Description                    | Min.  | Max. | Min.  | Max.   | Min.  | Max. | Units |  |   |

|--------------|--------------------------------|-------|------|-------|--------|-------|------|-------|--|---|

| VCCI         | Supply Voltage                 | 3     | 3.0  |       | .0 3.3 |       | .3   | 3.6   |  | V |

| VOL          | Output Low Voltage             | 0.96  | 1.27 | 1.06  | 1.43   | 1.30  | 1.57 | V     |  |   |

| VOH          | Output High Voltage            | 1.8   | 2.11 | 1.92  | 2.28   | 2.13  | 2.41 | V     |  |   |

| VIL, VIH     | Input Low, Input High Voltages | 0     | 3.6  | 0     | 3.6    | 0     | 3.6  | V     |  |   |

| VODIFF       | Differential Output Voltage    | 0.625 | 0.97 | 0.625 | 0.97   | 0.625 | 0.97 | V     |  |   |

| VOCM         | Output Common Mode Voltage     | 1.762 | 1.98 | 1.762 | 1.98   | 1.762 | 1.98 | V     |  |   |

| VICM         | Input Common Mode Voltage      | 1.01  | 2.57 | 1.01  | 2.57   | 1.01  | 2.57 | V     |  |   |

| VIDIFF       | Input Differential Voltage     | 300   |      | 300   |        | 300   |      | mV    |  |   |

#### Table 2-117 • Minimum and Maximum DC Input and Output Levels

Table 2-118 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input LOW (V) | Input HIGH (V) | Measuring Point* (V) | VREF (typ.) (V) |

|---------------|----------------|----------------------|-----------------|

| 1.64          | 1.94           | Cross point          | -               |

Note: \*Measuring point = Vtrip. See Table 2-23 on page 2-23 for a complete table of trip points.

#### Timing Characteristics

#### 1.5 V DC Core Voltage

#### Table 2-119 • LVPECL – Applies to 1.5 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------|

| Std.        | 0.98              | 1.75            | 0.19             | 1.45            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### 1.2 V DC Core Voltage

#### Table 2-120 • LVPECL – Applies to 1.2 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 3.0 V

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------|

| Std.        | 1.55              | 2.16            | 0.26             | 1.70            | ns    |

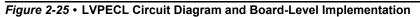

| Parameter Name        | Parameter Definition                                            | Measuring Nodes<br>(from, to)* |

|-----------------------|-----------------------------------------------------------------|--------------------------------|

| t <sub>oclkq</sub>    | Clock-to-Q of the Output Data Register                          | HH, DOUT                       |

| t <sub>OSUD</sub>     | Data Setup Time for the Output Data Register                    | FF, HH                         |

| t <sub>OHD</sub>      | Data Hold Time for the Output Data Register                     | FF, HH                         |

| t <sub>OSUE</sub>     | Enable Setup Time for the Output Data Register                  | GG, HH                         |

| t <sub>OHE</sub>      | Enable Hold Time for the Output Data Register                   | GG, HH                         |

| t <sub>OCLR2Q</sub>   | Asynchronous Clear-to-Q of the Output Data Register             | LL, DOUT                       |

| t <sub>OREMCLR</sub>  | Asynchronous Clear Removal Time for the Output Data Register    | LL, HH                         |

| t <sub>ORECCLR</sub>  | Asynchronous Clear Recovery Time for the Output Data Register   | LL, HH                         |

| t <sub>OECLKQ</sub>   | Clock-to-Q of the Output Enable Register                        | HH, EOUT                       |

| t <sub>OESUD</sub>    | Data Setup Time for the Output Enable Register                  | JJ, HH                         |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                   | JJ, HH                         |

| t <sub>OESUE</sub>    | Enable Setup Time for the Output Enable Register                | KK, HH                         |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                 | KK, HH                         |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register           | II, EOUT                       |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register  | II, HH                         |

| t <sub>OERECCLR</sub> | Asynchronous Clear Recovery Time for the Output Enable Register | II, HH                         |

| t <sub>ICLKQ</sub>    | Clock-to-Q of the Input Data Register                           | AA, EE                         |

| t <sub>ISUD</sub>     | Data Setup Time for the Input Data Register                     | CC, AA                         |

| t <sub>IHD</sub>      | Data Hold Time for the Input Data Register                      | CC, AA                         |

| t <sub>ISUE</sub>     | Enable Setup Time for the Input Data Register                   | BB, AA                         |

| t <sub>IHE</sub>      | Enable Hold Time for the Input Data Register                    | BB, AA                         |

| t <sub>ICLR2Q</sub>   | Asynchronous Clear-to-Q of the Input Data Register              | DD, EE                         |

| t <sub>IREMCLR</sub>  | Asynchronous Clear Removal Time for the Input Data Register     | DD, AA                         |

| t <sub>IRECCLR</sub>  | Asynchronous Clear Recovery Time for the Input Data Register    | DD, AA                         |

#### Table 2-122 • Parameter Definition and Measuring Nodes

Note: \*See Figure 2-27 on page 2-68 for more information.

## 🌜 Microsemi.

IGLOOe DC and Switching Characteristics

#### Figure 2-30 • Output Enable Register Timing Diagram

#### **Timing Characteristics**

#### 1.5 V DC Core Voltage

# Table 2-127 • Output Enable Register Propagation DelaysCommercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V

| Parameter             | Description                                                            | Std. | Units |

|-----------------------|------------------------------------------------------------------------|------|-------|

| t <sub>OECLKQ</sub>   | Clock-to-Q of the Output Enable Register                               | 0.75 | ns    |

| t <sub>OESUD</sub>    | Data Setup Time for the Output Enable Register                         | 0.51 | ns    |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                          | 0.00 | ns    |

| t <sub>OESUE</sub>    | Enable Setup Time for the Output Enable Register                       | 0.73 | ns    |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                        | 0.00 | ns    |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register                  | 1.13 | ns    |

| t <sub>OEPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Enable Register                 | 1.13 | ns    |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register         | 0.00 | ns    |

| t <sub>OERECCLR</sub> | Asynchronous Clear Recovery Time for the Output Enable Register        | 0.24 | ns    |

| t <sub>OEREMPRE</sub> | Asynchronous Preset Removal Time for the Output Enable Register        | 0.00 | ns    |

| t <sub>OERECPRE</sub> | Asynchronous Preset Recovery Time for the Output Enable Register       | 0.24 | ns    |

| t <sub>OEWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Output Enable Register  | 0.19 | ns    |

| t <sub>OEWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Output Enable Register | 0.19 | ns    |

| t <sub>OECKMPWH</sub> | Clock Minimum Pulse Width HIGH for the Output Enable Register          | 0.31 | ns    |

| t <sub>OECKMPWL</sub> | Clock Minimum Pulse Width LOW for the Output Enable Register           | 0.28 | ns    |

# **User Pins**

#### I/O

GL

FF

#### **User Input/Output**

The I/O pin functions as an input, output, tristate, or bidirectional buffer. Input and output signal levels are compatible with the I/O standard selected.

During programming, I/Os become tristated and weakly pulled up to VCCI. With VCCI, VMV, and VCC supplies continuously powered up, when the device transitions from programming to operating mode, the I/Os are instantly configured to the desired user configuration.

Unused I/Os are configured as follows:

- Output buffer is disabled (with tristate value of high impedance)

- Input buffer is disabled (with tristate value of high impedance)

- Weak pull-up is programmed

#### Globals

GL I/Os have access to certain clock conditioning circuitry (and the PLL) and/or have direct access to the global network (spines). Additionally, the global I/Os can be used as regular I/Os, since they have identical capabilities. Unused GL pins are configured as inputs with pull-up resistors.

See more detailed descriptions of global I/O connectivity in the "Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs" chapter of the *IGLOOe FPGA Fabric User's Guide*. All inputs labeled GC/GF are direct inputs into the quadrant clocks. For example, if GAA0 is used for an input, GAA1 and GAA2 are no longer available for input to the quadrant globals. All inputs labeled GC/GF are direct inputs into the chip-level globals, and the rest are connected to the quadrant globals. The inputs to the global network are multiplexed, and only one input can be used as a global input.

Refer to the I/O Structure section of the IGLOOe FPGA Fabric User's Guide for an explanation of the naming of global pins.

#### Flash\*Freeze Mode Activation Pin

Flash\*Freeze mode is available on IGLOOe devices. The FF pin is a dedicated input pin used to enter and exit Flash\*Freeze mode. The FF pin is active low, has the same characteristics as a single-ended I/O, and must meet the maximum rise and fall times. When Flash\*Freeze mode is not used in the design, the FF pin is available as a regular I/O. The FF pin can be configured as a Schmitt trigger input.

When Flash\*Freeze mode is used, the FF pin must not be left floating to avoid accidentally entering Flash\*Freeze mode. While in Flash\*Freeze mode, the Flash\*Freeze pin should be constantly asserted.

The Flash\*Freeze pin can be used with any single-ended I/O standard supported by the I/O bank in which the pin is located, and input signal levels compatible with the I/O standard selected. The FF pin should be treated as a sensitive asynchronous signal. When defining pin placement and board layout, simultaneously switching outputs (SSOs) and their effects on sensitive asynchronous pins must be considered.

Unused FF or I/O pins are tristated with weak pull-up. This default configuration applies to both Flash\*Freeze mode and normal operation mode. No user intervention is required.

Package Pin Assignments

| FG484         |                   |               | FG484             |               | FG484             |

|---------------|-------------------|---------------|-------------------|---------------|-------------------|

| Pin<br>Number | AGLE3000 Function | Pin<br>Number | AGLE3000 Function | Pin<br>Number | AGLE3000 Function |

| N8            | VCCIB6            | P21           | IO130PDB3V2       | T12           | IO194NDB5V0       |

| N9            | VCC               | P22           | IO128NDB3V1       | T13           | IO186NDB4V4       |

| N10           | GND               | R1            | IO247NDB6V1       | T14           | IO186PDB4V4       |

| N11           | GND               | R2            | IO245PDB6V1       | T15           | GNDQ              |

| N12           | GND               | R3            | VCC               | T16           | VCOMPLD           |

| N13           | GND               | R4            | IO249NPB6V1       | T17           | VJTAG             |

| N14           | VCC               | R5            | IO251NDB6V2       | T18           | GDC0/IO151NDB3V4  |

| N15           | VCCIB3            | R6            | IO251PDB6V2       | T19           | GDA1/IO153PDB3V4  |

| N16           | IO116NPB3V0       | R7            | GEC0/IO236NPB6V0  | T20           | IO144PDB3V3       |

| N17           | IO132NPB3V2       | R8            | VMV5              | T21           | IO140PDB3V3       |

| N18           | IO117NPB3V0       | R9            | VCCIB5            | T22           | IO134NDB3V2       |

| N19           | IO132PPB3V2       | R10           | VCCIB5            | U1            | IO240PPB6V0       |

| N20           | GNDQ              | R11           | IO196NDB5V0       | U2            | IO238PDB6V0       |

| N21           | IO126NDB3V1       | R12           | IO196PDB5V0       | U3            | IO238NDB6V0       |

| N22           | IO128PDB3V1       | R13           | VCCIB4            | U4            | GEB1/IO235PDB6V0  |

| P1            | IO247PDB6V1       | R14           | VCCIB4            | U5            | GEB0/IO235NDB6V0  |

| P2            | IO253PDB6V2       | R15           | VMV3              | U6            | VMV6              |

| P3            | IO270NPB6V4       | R16           | VCCPLD            | U7            | VCCPLE            |

| P4            | IO261NPB6V3       | R17           | GDB1/IO152PPB3V4  | U8            | IO233NPB5V4       |

| P5            | IO249PPB6V1       | R18           | GDC1/IO151PDB3V4  | U9            | IO222PPB5V3       |

| P6            | IO259PDB6V3       | R19           | IO138NDB3V3       | U10           | IO206PDB5V1       |

| P7            | IO259NDB6V3       | R20           | VCC               | U11           | IO202PDB5V1       |

| P8            | VCCIB6            | R21           | IO130NDB3V2       | U12           | IO194PDB5V0       |

| P9            | GND               | R22           | IO134PDB3V2       | U13           | IO176NDB4V2       |

| P10           | VCC               | T1            | IO243PPB6V1       | U14           | IO176PDB4V2       |

| P11           | VCC               | T2            | IO245NDB6V1       | U15           | VMV4              |

| P12           | VCC               | Т3            | IO243NPB6V1       | U16           | ТСК               |

| P13           | VCC               | T4            | IO241PDB6V0       | U17           | VPUMP             |

| P14           | GND               | T5            | IO241NDB6V0       | U18           | TRST              |

| P15           | VCCIB3            | Т6            | GEC1/IO236PPB6V0  | U19           | GDA0/IO153NDB3V4  |

| P16           | GDB0/IO152NPB3V4  | T7            | VCOMPLE           | U20           | IO144NDB3V3       |

| P17           | IO136NDB3V2       | Т8            | GNDQ              | U21           | IO140NDB3V3       |

| P18           | IO136PDB3V2       | Т9            | GEA2/IO233PPB5V4  | U22           | IO142PDB3V3       |

| P19           | IO138PDB3V3       | T10           | IO206NDB5V1       | V1            | IO239PDB6V0       |

| P20           | VMV3              | T11           | IO202NDB5V1       | V2            | IO240NPB6V0       |

| FG896      |                      |            | FG896                |            | FG896                |  |  |

|------------|----------------------|------------|----------------------|------------|----------------------|--|--|

| Pin Number | AGLE3000<br>Function | Pin Number | AGLE3000<br>Function | Pin Number | AGLE3000<br>Function |  |  |

| D30        | GBA2/IO82PPB2V0      | F5         | VMV7                 | G7         | VCC                  |  |  |

| E1         | GND                  | F5         | VMV7                 | G8         | VMV0                 |  |  |

| E2         | IO303NPB7V3          | F6         | GND                  | G9         | VCCIB0               |  |  |

| E3         | VCCIB7               | F7         | GNDQ                 | G10        | IO10NDB0V1           |  |  |

| E4         | IO305PPB7V3          | F8         | IO12NDB0V1           | G11        | IO16NDB0V1           |  |  |

| E5         | VCC                  | F9         | IO12PDB0V1           | G12        | IO22PDB0V2           |  |  |

| E6         | GAC0/IO02NDB0V0      | F10        | IO10PDB0V1           | G13        | IO26PPB0V3           |  |  |

| E7         | VCCIB0               | F11        | IO16PDB0V1           | G14        | IO38NPB0V4           |  |  |

| E8         | IO06PPB0V0           | F12        | IO22NDB0V2           | G15        | IO36NDB0V4           |  |  |

| E9         | IO24NDB0V2           | F13        | IO30NDB0V3           | G16        | IO46NDB1V0           |  |  |

| E10        | IO24PDB0V2           | F14        | IO30PDB0V3           | G17        | IO46PDB1V0           |  |  |

| E11        | IO13NDB0V1           | F15        | IO36PDB0V4           | G18        | IO56NDB1V1           |  |  |

| E12        | IO13PDB0V1           | F16        | IO48NDB1V0           | G19        | IO56PDB1V1           |  |  |

| E13        | IO34NDB0V4           | F17        | IO48PDB1V0           | G20        | IO66NDB1V3           |  |  |

| E14        | IO34PDB0V4           | F18        | IO50NDB1V1           | G21        | IO66PDB1V3           |  |  |

| E15        | IO40NDB0V4           | F19        | IO58NDB1V2           | G22        | VCCIB1               |  |  |

| E16        | IO49NDB1V1           | F20        | IO60PDB1V2           | G23        | VMV1                 |  |  |

| E17        | IO49PDB1V1           | F21        | IO77NDB1V4           | G24        | VCC                  |  |  |

| E18        | IO50PDB1V1           | F22        | IO72NDB1V3           | G25        | GNDQ                 |  |  |

| E19        | IO58PDB1V2           | F23        | IO72PDB1V3           | G25        | GNDQ                 |  |  |

| E20        | IO60NDB1V2           | F24        | GNDQ                 | G26        | VCCIB2               |  |  |

| E21        | IO77PDB1V4           | F25        | GND                  | G27        | IO86NDB2V0           |  |  |

| E22        | IO68NDB1V3           | F26        | VMV2                 | G28        | IO92NDB2V1           |  |  |

| E23        | IO68PDB1V3           | F26        | VMV2                 | G29        | IO100PPB2V2          |  |  |

| E24        | VCCIB1               | F27        | IO86PDB2V0           | G30        | GND                  |  |  |

| E25        | IO74PDB1V4           | F28        | IO92PDB2V1           | H1         | IO294PDB7V2          |  |  |

| E26        | VCC                  | F29        | VCC                  | H2         | IO294NDB7V2          |  |  |

| E27        | GBB1/IO80PPB1V4      | F30        | IO100NPB2V2          | H3         | IO300NDB7V3          |  |  |

| E28        | VCCIB2               | G1         | GND                  | H4         | IO300PDB7V3          |  |  |

| E29        | IO82NPB2V0           | G2         | IO296NPB7V2          | H5         | IO295PDB7V2          |  |  |

| E30        | GND                  | G3         | IO306NDB7V4          | H6         | IO299PDB7V3          |  |  |

| F1         | IO296PPB7V2          | G4         | IO297NDB7V2          | H7         | VCOMPLA              |  |  |

| F2         | VCC                  | G5         | VCCIB7               | H8         | GND                  |  |  |

| F3         | IO306PDB7V4          | G6         | GNDQ                 | H9         | IO08NDB0V0           |  |  |

| F4         | IO297PDB7V2          | G6         | GNDQ                 | H10        | IO08PDB0V0           |  |  |

|            | FG896                |            | FG896                |            | FG896                |

|------------|----------------------|------------|----------------------|------------|----------------------|

| Pin Number | AGLE3000<br>Function | Pin Number | AGLE3000<br>Function | Pin Number | AGLE3000<br>Function |

| L26        | IO87NDB2V0           | N1         | IO276PDB7V0          | P6         | GFC1/IO275PDB7V0     |

| L27        | IO97PDB2V1           | N2         | IO278PDB7V0          | P7         | GFC0/IO275NDB7V0     |

| L28        | IO101PDB2V2          | N3         | IO280PDB7V0          | P8         | IO277PDB7V0          |

| L29        | IO103PDB2V2          | N4         | IO284PDB7V1          | P9         | IO277NDB7V0          |

| L30        | IO119NDB3V0          | N5         | IO279PDB7V0          | P10        | VCCIB7               |

| M1         | IO282NDB7V1          | N6         | IO285NDB7V1          | P11        | VCC                  |

| M2         | IO282PDB7V1          | N7         | IO287NDB7V1          | P12        | GND                  |

| M3         | IO292NDB7V2          | N8         | IO281NDB7V0          | P13        | GND                  |

| M4         | IO292PDB7V2          | N9         | IO281PDB7V0          | P14        | GND                  |

| M5         | IO283NDB7V1          | N10        | VCCIB7               | P15        | GND                  |

| M6         | IO285PDB7V1          | N11        | VCC                  | P16        | GND                  |

| M7         | IO287PDB7V1          | N12        | GND                  | P17        | GND                  |

| M8         | IO289PDB7V1          | N13        | GND                  | P18        | GND                  |

| M9         | IO289NDB7V1          | N14        | GND                  | P19        | GND                  |

| M10        | VCCIB7               | N15        | GND                  | P20        | VCC                  |

| M11        | VCC                  | N16        | GND                  | P21        | VCCIB2               |

| M12        | GND                  | N17        | GND                  | P22        | GCC1/IO112PDB2V3     |

| M13        | GND                  | N18        | GND                  | P23        | IO110PDB2V3          |

| M14        | GND                  | N19        | GND                  | P24        | IO110NDB2V3          |

| M15        | GND                  | N20        | VCC                  | P25        | IO109PPB2V3          |

| M16        | GND                  | N21        | VCCIB2               | P26        | IO111NPB2V3          |

| M17        | GND                  | N22        | IO106NDB2V3          | P27        | IO105PDB2V2          |

| M18        | GND                  | N23        | IO106PDB2V3          | P28        | IO105NDB2V2          |

| M19        | GND                  | N24        | IO108PDB2V3          | P29        | GCC2/IO117PDB3V0     |

| M20        | VCC                  | N25        | IO108NDB2V3          | P30        | IO117NDB3V0          |

| M21        | VCCIB2               | N26        | IO95NDB2V1           | R1         | GFC2/IO270PDB6V4     |

| M22        | NC                   | N27        | IO99NDB2V2           | R2         | GFB1/IO274PPB7V0     |

| M23        | IO104PPB2V2          | N28        | IO99PDB2V2           | R3         | VCOMPLF              |

| M24        | IO102PDB2V2          | N29        | IO107PDB2V3          | R4         | GFA0/IO273NDB6V4     |

| M25        | IO102NDB2V2          | N30        | IO107NDB2V3          | R5         | GFB0/IO274NPB7V0     |

| M26        | IO95PDB2V1           | P1         | IO276NDB7V0          | R6         | IO271NDB6V4          |

| M27        | IO97NDB2V1           | P2         | IO278NDB7V0          | R7         | GFB2/IO271PDB6V4     |

| M28        | IO101NDB2V2          | P3         | IO280NDB7V0          | R8         | IO269PDB6V4          |

| M29        | IO103NDB2V2          | P4         | IO284NDB7V1          | R9         | IO269NDB6V4          |

| M30        | IO119PDB3V0          | P5         | IO279NDB7V0          | R10        | VCCIB7               |

# 5 – Datasheet Information

# **List of Changes**

The following table lists critical changes that were made in each revision of the IGLOOe datasheet.

| Revision                        | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page          |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Revision 13<br>(December 2012)  | The "IGLOOe Ordering Information" section has been updated to mention "Y" as "Blank" mentioning "Device Does Not Include License to Implement IP Based on the Cryptography Research, Inc. (CRI) Patent Portfolio" (SAR 43176).                                                                                                                                                                                                                                                                                      | 111           |

|                                 | Also added the missing heading 'Supply Voltage' under V2.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |

|                                 | The note in Table 2-143 • IGLOOe CCC/PLL Specification and Table 2-144 • IGLOOe CCC/PLL Specification referring the reader to SmartGen was revised to refer instead to the online help associated with the core (SAR 42568).                                                                                                                                                                                                                                                                                        | 2-91,<br>2-92 |

|                                 | Live at Power-Up (LAPU) has been replaced with 'Instant On'.                                                                                                                                                                                                                                                                                                                                                                                                                                                        | NA            |

| Revision 12<br>(September 2012) | The "Security" section was modified to clarify that Microsemi does not support read-back of programmed data.                                                                                                                                                                                                                                                                                                                                                                                                        | 1-2           |

|                                 | Libero Integrated Design Environment (IDE) was changed to Libero System-on-Chip (SoC) throughout the document (SAR 40272).                                                                                                                                                                                                                                                                                                                                                                                          | N/A           |

| Revision 11<br>(August 2012)    | The drive strength, IOL, and IOH value for 3.3 V GTL and 2.5 V GTL was changed from 25 mA to 20 mA in the following tables (SAR 37180):                                                                                                                                                                                                                                                                                                                                                                             |               |

|                                 | Table 2-21 • Summary of Maximum and Minimum DC Input and Output Levels,                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-20          |

|                                 | Table 2-25 • Summary of I/O Timing Characteristics—Software Default Settings                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-25          |

|                                 | Table 2-26 • Summary of I/O Timing Characteristics—Software Default Settings                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-26          |

|                                 | Table 2-28 • I/O Output Buffer Maximum Resistances1                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-28          |

|                                 | Table 2-73 • Minimum and Maximum DC Input and Output Levels                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-51          |

|                                 | Table 2-77 • Minimum and Maximum DC Input and Output Levels                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-53          |

|                                 | Also added note stating " <i>Output drive strength is below JEDEC specification</i> ." for Tables 2-25, 2-26, and 2-28.                                                                                                                                                                                                                                                                                                                                                                                             |               |

|                                 | Additionally, the IOL and IOH values for 3.3 V GTL+ and 2.5 V GTL+ were corrected from 51 to 35 (for 3.3 V GTL+) and from 40 to 33 (for 2.5 V GTL+) in table Table 2-21 (SAR 39713).                                                                                                                                                                                                                                                                                                                                |               |

|                                 | In Table 2-117 • Minimum and Maximum DC Input and Output Levels, VIL and VIH were revised so that the maximum is 3.6 V for all listed values of VCCI (SAR 37183).                                                                                                                                                                                                                                                                                                                                                   | 2-65          |

|                                 | The following sentence was removed from the "VMVx I/O Supply Voltage (quiet)" section in the "Pin Descriptions and Packaging" section: "Within the package, the VMV plane is decoupled from the simultaneous switching noise originating from the output buffer VCCI domain" and replaced with "Within the package, the VMV plane biases the input stage of the I/Os in the I/O banks" (SAR 38318). The datasheet mentions that "VMV pins must be connected to the corresponding VCCI pins" for an ESD enhancement. | 3-1           |

# **Datasheet Categories**

### Categories