Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                 |

|--------------------------------|-----------------------------------------------------------------|

| Product Status                 | Obsolete                                                        |

| Number of LABs/CLBs            | -                                                               |

| Number of Logic Elements/Cells | 13824                                                           |

| Total RAM Bits                 | 110592                                                          |

| Number of I/O                  | 270                                                             |

| Number of Gates                | 600000                                                          |

| Voltage - Supply               | 1.425V ~ 1.575V                                                 |

| Mounting Type                  | Surface Mount                                                   |

| Operating Temperature          | -40°C ~ 85°C (TA)                                               |

| Package / Case                 | 484-BGA                                                         |

| Supplier Device Package        | 484-FPBGA (23x23)                                               |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/agle600v5-fg484i |

|                                |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

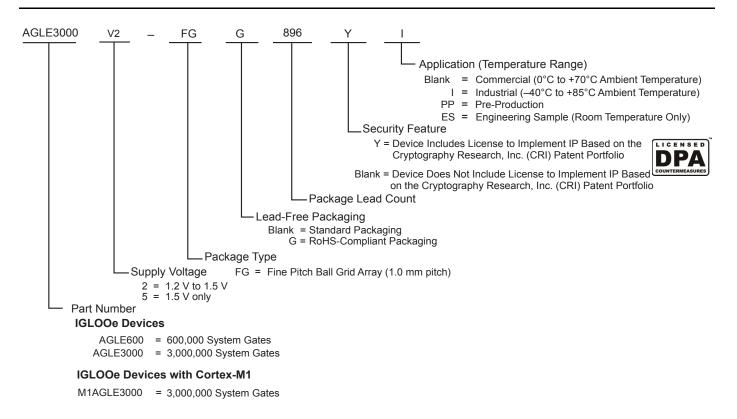

# **IGLOOe Ordering Information**

Note: Marking Information: IGLOO V2 devices do not have V2 marking, but IGLOO V5 devices are marked accordingly.

# **Calculating Power Dissipation**

# **Quiescent Supply Current**

Quiescent supply current (IDD) calculation depends on multiple factors, including operating voltages (VCC, VCCI, and VJTAG), operating temperature, system clock frequency, and power modes usage. Microsemi recommends using the PowerCalculator and SmartPower software estimation tools to evaluate the projected static and active power based on the user design, power mode usage, operating voltage, and temperature.

#### Table 2-8 • Power Supply State per Mode

|                      | Power Supply Configurations |        |      |       |                 |  |  |  |  |  |

|----------------------|-----------------------------|--------|------|-------|-----------------|--|--|--|--|--|

| Modes/power supplies | VCC                         | VCCPLL | VCCI | VJTAG | VPUMP           |  |  |  |  |  |

| Flash*Freeze         | On                          | On     | On   | On    | On/off/floating |  |  |  |  |  |

| Sleep                | Off                         | Off    | On   | Off   | Off             |  |  |  |  |  |

| Shutdown             | Off                         | Off    | Off  | Off   | Off             |  |  |  |  |  |

| No Flash*Freeze      | On                          | On     | On   | On    | On/off/floating |  |  |  |  |  |

*Note:* Off: Power supply level = 0 V

#### Table 2-9 • Quiescent Supply Current (IDD), IGLOOe Flash\*Freeze Mode\*

|                | Core Voltage | AGLE600 | AGLE3000 | Units |

|----------------|--------------|---------|----------|-------|

| Typical (25°C) | 1.2 V        | 34      | 95       | μΑ    |

|                | 1.5 V        | 72      | 310      | μΑ    |

Note: \*IDD includes VCC, VPUMP, VCCI, VCCPLL, and VMV currents. Values do not include I/O static contribution, which is shown in Table 2-13 on page 2-9 and Table 2-14 on page 2-10 (PDC6 and PDC7).

#### Table 2-10 • Quiescent Supply Current (IDD) Characteristics, IGLOOe Sleep Mode\*

|                                                 | Core Voltage  | AGLE600 | AGLE3000 | Units |

|-------------------------------------------------|---------------|---------|----------|-------|

| VCCI/VJTAG = 1.2 V (per bank)<br>Typical (25°C) | 1.2 V         | 1.7     | 1.7      | μA    |

| VCCI/VJTAG = 1.5 V (per bank)<br>Typical (25°C) | 1.2 V / 1.5 V | 1.8     | 1.8      | μA    |

| VCCI/VJTAG = 1.8 V (per bank)<br>Typical (25°C) | 1.2 V / 1.5 V | 1.9     | 1.9      | μA    |

| VCCI/VJTAG = 2.5 V (per bank)<br>Typical (25°C) | 1.2 V / 1.5 V | 2.2     | 2.2      | μA    |

| VCCI/VJTAG= 3.3 V (per bank)<br>Typical (25°C)  | 1.2 V / 1.5 V | 2.5     | 2.5      | μA    |

Note:  $*IDD = N_{BANKS} \times ICCI$ . Values do not include I/O static contribution, which is shown in Table 2-13 on page 2-9 and Table 2-14 on page 2-10 (PDC6 and PDC7).

#### Table 2-11 • Quiescent Supply Current (IDD) Characteristics, IGLOOe Shutdown Mode\*

|                | Core Voltage  | AGLE600 | AGLE3000 | Units |

|----------------|---------------|---------|----------|-------|

| Typical (25°C) | 1.2 V / 1.5 V | 0       | 0        | μA    |

## Guidelines

#### Toggle Rate Definition

A toggle rate defines the frequency of a net or logic element relative to a clock. It is a percentage. If the toggle rate of a net is 100%, this means that this net switches at half the clock frequency. Below are some examples:

- The average toggle rate of a shift register is 100% as all flip-flop outputs toggle at half of the clock frequency.

- The average toggle rate of an 8-bit counter is 25%:

- Bit 0 (LSB) = 100%

- Bit 1 = 50%

- Bit 2 = 25%

- ...

- Bit 7 (MSB) = 0.78125%

- Average toggle rate = (100% + 50% + 25% + 12.5% + . . . + 0.78125%) / 8

#### Enable Rate Definition

Output enable rate is the average percentage of time during which tristate outputs are enabled. When nontristate output buffers are used, the enable rate should be 100%.

#### Table 2-19 • Toggle Rate Guidelines Recommended for Power Calculation

| Component      | Component Definition   |     |  |  |  |  |  |  |

|----------------|------------------------|-----|--|--|--|--|--|--|

| $\alpha_1$     | 10%                    |     |  |  |  |  |  |  |

| α <sub>2</sub> | I/O buffer toggle rate | 10% |  |  |  |  |  |  |

#### Table 2-20 • Enable Rate Guidelines Recommended for Power Calculation

| Component      | Definition                           | Guideline |

|----------------|--------------------------------------|-----------|

| β <sub>1</sub> | I/O output buffer enable rate        | 100%      |

| β <sub>2</sub> | RAM enable rate for read operations  | 12.5%     |

| $\beta_3$      | RAM enable rate for write operations | 12.5%     |

# static Microsemi.

IGLOOe DC and Switching Characteristics

| Parameter         | Definition                                                                  |

|-------------------|-----------------------------------------------------------------------------|

| t <sub>DP</sub>   | Data to Pad delay through the Output Buffer                                 |

| t <sub>PY</sub>   | Pad to Data delay through the Input Buffer with Schmitt trigger disabled    |

| t <sub>DOUT</sub> | Data to Output Buffer delay through the I/O interface                       |

| t <sub>EOUT</sub> | Enable to Output Buffer Tristate Control delay through the I/O interface    |

| t <sub>DIN</sub>  | Input Buffer to Data delay through the I/O interface                        |

| t <sub>PYS</sub>  | Pad to Data delay through the Input Buffer with Schmitt trigger enabled     |

| t <sub>HZ</sub>   | Enable to Pad delay through the Output Buffer—HIGH to Z                     |

| t <sub>zH</sub>   | Enable to Pad delay through the Output Buffer—Z to HIGH                     |

| t <sub>LZ</sub>   | Enable to Pad delay through the Output Buffer—LOW to Z                      |

| t <sub>ZL</sub>   | Enable to Pad delay through the Output Buffer—Z to LOW                      |

| t <sub>zHS</sub>  | Enable to Pad delay through the Output Buffer with delayed enable—Z to HIGH |

| t <sub>ZLS</sub>  | Enable to Pad delay through the Output Buffer with delayed enable—Z to LOW  |

#### Table 2-24 • I/O AC Parameter Definitions

# 🌜 Microsemi.

IGLOOe DC and Switching Characteristics

#### 1.2 V DC Core Voltage

# Table 2-38 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew – Applies to 1.2 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 3.0 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 4 mA           | Std.        | 1.55              | 5.54            | 0.26             | 1.31            | 1.58             | 1.10              | 5.63            | 4.53            | 2.79            | 2.87            | 11.42            | 10.32            | ns    |

| 8 mA           | Std.        | 1.55              | 4.60            | 0.26             | 1.31            | 1.58             | 1.10              | 4.67            | 3.94            | 3.09            | 3.45            | 10.45            | 9.73             | ns    |

| 12 mA          | Std.        | 1.55              | 3.93            | 0.26             | 1.31            | 1.58             | 1.10              | 3.99            | 3.51            | 3.28            | 3.82            | 9.77             | 9.29             | ns    |

| 16 mA          | Std.        | 1.55              | 3.74            | 0.26             | 1.31            | 1.58             | 1.10              | 3.79            | 3.41            | 3.32            | 3.92            | 9.58             | 9.20             | ns    |

| 24 mA          | Std.        | 1.55              | 3.64            | 0.26             | 1.31            | 1.58             | 1.10              | 3.69            | 3.42            | 3.38            | 4.30            | 9.48             | 9.21             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-6 for derating values.

# Table 2-39 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew – Applies to 1.2 V DC Core Voltage Commercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 3.0 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 4 mA           | Std.        | 1.55              | 3.26            | 0.26             | 1.31            | 1.58             | 1.10              | 3.33            | 2.67            | 2.79            | 3.01            | 9.12             | 8.46             | ns    |

| 8 mA           | Std.        | 1.55              | 2.77            | 0.26             | 1.31            | 1.58             | 1.10              | 2.80            | 2.24            | 3.09            | 3.59            | 8.59             | 8.03             | ns    |

| 12 mA          | Std.        | 1.55              | 2.47            | 0.26             | 1.31            | 1.58             | 1.10              | 2.51            | 2.04            | 3.28            | 3.97            | 8.29             | 7.82             | ns    |

| 16 mA          | Std.        | 1.55              | 2.42            | 0.26             | 1.31            | 1.58             | 1.10              | 2.46            | 2.00            | 3.33            | 4.08            | 8.24             | 7.79             | ns    |

| 24 mA          | Std.        | 1.55              | 2.45            | 0.26             | 1.31            | 1.58             | 1.10              | 2.48            | 1.95            | 3.38            | 4.46            | 8.26             | 7.73             | ns    |

Notes:

1. Software default selection highlighted in gray.

# static Microsemi.

IGLOOe DC and Switching Characteristics

## 1.5 V LVCMOS (JESD8-11)

Low-Voltage CMOS for 1.5 V is an extension of the LVCMOS standard (JESD8-5) used for generalpurpose 1.5 V applications. It uses a 1.5 V input buffer and a push-pull output buffer.

| 1.5 V<br>LVCMOS   |           | VIL         | VIH         |           | VOL         | VOH         | IOL | ЮН | IOSH                    | IOSL                    | IIL¹            | IIH <sup>2</sup> |

|-------------------|-----------|-------------|-------------|-----------|-------------|-------------|-----|----|-------------------------|-------------------------|-----------------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V   | Min.<br>V   | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup> | μA <sup>4</sup>  |

| 2 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 2   | 2  | 13                      | 16                      | 10              | 10               |

| 4 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 4   | 4  | 25                      | 33                      | 10              | 10               |

| 6 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 6   | 6  | 32                      | 39                      | 10              | 10               |

| 8 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 8   | 8  | 66                      | 55                      | 10              | 10               |

| 12 mA             | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 12  | 12 | 66                      | 55                      | 10              | 10               |

#### Table 2-58 • Minimum and Maximum DC Input and Output Levels

#### Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

5. Software default selection highlighted in gray.

Test Point

Datapath

$$\downarrow$$

35 pF  $R = 1 k$

Enable Path  $\downarrow$   $R$  to VCCI for  $t_{LZ} / t_{ZL} / t_{ZLS}$

$R$  to GND for  $t_{HZ} / t_{ZH} / t_{ZHS}$

$5 pF for t_{ZH} / t_{ZHS} / t_{ZL} / t_{ZLS}$

$5 pF for t_{HZ} / t_{ZH} / t_{ZLS}$

#### Figure 2-10 • AC Loading

#### Table 2-59 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|------------------------|

| 0             | 1.5            | 0.75                 | _               | 5                      |

Note: \*Measuring point = Vtrip. See Table 2-23 on page 2-23 for a complete table of trip points.

## Voltage-Referenced I/O Characteristics

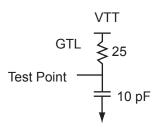

## 3.3 V GTL

Gunning Transceiver Logic is a high-speed bus standard (JESD8-3). It provides a differential amplifier input buffer and an open-drain output buffer. The VCCI pin should be connected to 3.3 V.

Table 2-73 • Minimum and Maximum DC Input and Output Levels

| 3.3 V GTL          |           | VIL         | VIH<br>Min Max |           | VOL      | VOH       | IOL | ЮН | IOSL                    | IOSH                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|--------------------|-----------|-------------|----------------|-----------|----------|-----------|-----|----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength  | Min.<br>V | Max.<br>V   | Min.<br>V      | Max.<br>V | Max<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 20 mA <sup>5</sup> | -0.3      | VREF – 0.05 | VREF + 0.05    | 3.6       | 0.4      | -         | 20  | 20 | 268                     | 181                     | 10               | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operating conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Output drive strength is below JEDEC specification.

#### Figure 2-13 • AC Loading

| Table 2-74 • | AC Waveforms. | Measuring Points   | , and Capacitive Loads     |

|--------------|---------------|--------------------|----------------------------|

|              |               | inououring i onito | , and capacitie is a cauce |

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------------------|

| VREF – 0.05   | VREF + 0.05    | 0.8                  | 0.8             | 1.2            | 10                     |

*Note:* \*Measuring point = Vtrip. See Table 2-23 on page 2-23 for a complete table of trip points.

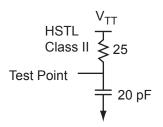

## HSTL Class II

High-Speed Transceiver Logic is a general-purpose high-speed 1.5 V bus standard (EIA/JESD8-6). IGLOOe devices support Class II. This provides a differential amplifier input buffer and a push-pull output buffer.

| HSTL<br>Class II   |           | VIL        | VIH        |           | VOL       | VOH        | IOL | юн | IOSH                    | IOSL                    | IIL¹            | IIH <sup>2</sup> |

|--------------------|-----------|------------|------------|-----------|-----------|------------|-----|----|-------------------------|-------------------------|-----------------|------------------|

| Drive<br>Strength  | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V  | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup> | μA <sup>4</sup>  |

| 15 mA <sup>5</sup> | -0.3      | VREF – 0.1 | VREF + 0.1 | 3.6       | 0.4       | VCCI – 0.4 | 15  | 15 | 66                      | 55                      | 10              | 10               |

Table 2-93 • Minimum and Maximum DC Input and Output Levels

Notes:

1. IIL is the input leakage current per I/O pin over recommended operating conditions where -0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

5. Output drive strength is below JEDEC specification.

#### Figure 2-18 • AC Loading

#### Table 2-94 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------------------|

| VREF – 0.1    | VREF + 0.1     | 0.75                 | 0.75            | 0.75           | 20                     |

Note: \*Measuring point = Vtrip. See Table 2-23 on page 2-23 for a complete table of trip points.

#### Timing Characteristics

#### 1.5 V DC Core Voltage

Table 2-95 •HSTL Class II – Applies to 1.5 V DC Core Voltage<br/>Commercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V,<br/>Worst-Case VCCI = 1.4 V VREF = 0.75 V

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.        | 0.98              | 2.62            | 0.19             | 1.77            | 0.67              | 2.66            | 2.40            |                 |                 | 6.29             | 6.03             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### 1.2 V DC Core Voltage

# Table 2-96 •HSTL Class II – Applies to 1.2 V DC Core Voltage<br/>Commercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.14 V,<br/>Worst-Case VCCI = 1.4 V VREF = 0.75 V

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.        | 1.55              | 2.93            | 0.26             | 1.94            | 1.10              | 2.98            | 2.75            |                 |                 | 8.79             | 8.55             | ns    |

# 🌜 Microsemi.

IGLOOe DC and Switching Characteristics

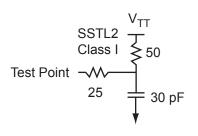

## SSTL2 Class I

Stub-Speed Terminated Logic for 2.5 V memory bus standard (JESD8-9). IGLOOe devices support Class I. This provides a differential amplifier input buffer and a push-pull output buffer.

| Table 2-97 • | Minimum and Maximum | DC Input and | Output Levels |

|--------------|---------------------|--------------|---------------|

|--------------|---------------------|--------------|---------------|

| SSTL2<br>Class I  |           | VIL        | VIH        |           | VOL       | VOH         | IOL | юн | IOSH                    | IOSL                    | IIL¹            | IIH <sup>2</sup> |

|-------------------|-----------|------------|------------|-----------|-----------|-------------|-----|----|-------------------------|-------------------------|-----------------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V   | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup> | μA <sup>4</sup>  |

| 15 mA             | -0.3      | VREF – 0.2 | VREF + 0.2 | 3.6       | 0.54      | VCCI - 0.62 | 15  | 15 | 83                      | 87                      | 10              | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operating conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

#### Figure 2-19 • AC Loading

Table 2-98 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------------------|

| VREF – 0.2    | VREF + 0.2     | 1.25                 | 1.25            | 1.25           | 30                     |

Note: \*Measuring point = Vtrip. See Table 2-23 on page 2-23 for a complete table of trip points.

#### Timing Characteristics

1.5 V DC Core Voltage

Table 2-99 • SSTL 2 Class I – Applies to 1.5 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V,

Worst-Case VCCI = 2.3 V VREF = 1.25 V

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.        | 0.98              | 1.91            | 0.19             | 1.15            | 0.67              | 1.94            | 1.72            |                 |                 | 5.57             | 5.35             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### 1.2 V DC Core Voltage

#### Table 2-100 • SSTL 2 Class I – Applies to 1.2 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 2.3 V VREF = 1.25 V

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.        | 1.55              | 2.17            | 0.26             | 1.39            | 1.10              | 2.21            | 2.04            |                 |                 | 8.02             | 7.84             | ns    |

## **Microsemi**. IGLOOE DC and Switching Characteristics

## **Timing Characteristics**

1.5 V DC Core Voltage

#### Table 2-135 • Combinatorial Cell Propagation Delays

#### Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Combinatorial Cell | Equation                  | Parameter       | Std. | Units |

|--------------------|---------------------------|-----------------|------|-------|

| INV                | Y = !A                    | t <sub>PD</sub> | 0.80 | ns    |

| AND2               | $Y = A \cdot B$           | t <sub>PD</sub> | 0.84 | ns    |

| NAND2              | Y = !(A · B)              | t <sub>PD</sub> | 0.90 | ns    |

| OR2                | Y = A + B                 | t <sub>PD</sub> | 1.19 | ns    |

| NOR2               | Y = !(A + B)              | t <sub>PD</sub> | 1.10 | ns    |

| XOR2               | Y = A 🕀 B                 | t <sub>PD</sub> | 1.37 | ns    |

| MAJ3               | Y = MAJ(A, B, C)          | t <sub>PD</sub> | 1.33 | ns    |

| XOR3               | $Y = A \oplus B \oplus C$ | t <sub>PD</sub> | 1.79 | ns    |

| MUX2               | Y = A !S + B S            | t <sub>PD</sub> | 1.48 | ns    |

| AND3               | $Y = A \cdot B \cdot C$   | t <sub>PD</sub> | 1.21 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### 1.2 V DC Core Voltage

# Table 2-136 • Combinatorial Cell Propagation DelaysCommercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V

| Combinatorial Cell | Equation                  | Parameter       | Std. | Units |

|--------------------|---------------------------|-----------------|------|-------|

| INV                | Y = !A                    | t <sub>PD</sub> | 1.35 | ns    |

| AND2               | $Y = A \cdot B$           | t <sub>PD</sub> | 1.42 | ns    |

| NAND2              | Y = !(A ⋅ B)              | t <sub>PD</sub> | 1.58 | ns    |

| OR2                | Y = A + B                 | t <sub>PD</sub> | 2.10 | ns    |

| NOR2               | Y = !(A + B)              | t <sub>PD</sub> | 1.94 | ns    |

| XOR2               | Y = A 🕀 B                 | t <sub>PD</sub> | 2.33 | ns    |

| MAJ3               | Y = MAJ(A, B, C)          | t <sub>PD</sub> | 2.34 | ns    |

| XOR3               | $Y = A \oplus B \oplus C$ | t <sub>PD</sub> | 3.05 | ns    |

| MUX2               | Y = A !S + B S            | t <sub>PD</sub> | 2.64 | ns    |

| AND3               | $Y = A \cdot B \cdot C$   | t <sub>PD</sub> | 2.10 | ns    |

## **Global Tree Timing Characteristics**

Global clock delays include the central rib delay, the spine delay, and the row delay. Delays do not include I/O input buffer clock delays, as these are I/O standard–dependent, and the clock may be driven and conditioned internally by the CCC module. For more details on clock conditioning capabilities, refer to the "Clock Conditioning Circuits" section on page 2-91. Table 2-139 and Table 2-141 present minimum and maximum global clock delays within the device. Minimum and maximum delays are measured with minimum and maximum loading.

#### Timing Characteristics

#### 1.5 V DC Core Voltage

#### Table 2-139 • AGLE600 Global Resource Commercial-Case Conditions: T<sub>.1</sub> = 70°C, VCC = 1.425 V

|                      |                                           |      | Std.                                |    |

|----------------------|-------------------------------------------|------|-------------------------------------|----|

| Parameter            | Description                               | Min. | Min. <sup>1</sup> Max. <sup>2</sup> |    |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.48 | 1.82                                | ns |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.52 | 1.94                                | ns |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.18 |                                     | ns |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.15 |                                     | ns |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |      | 0.42                                | ns |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

## Table 2-140 • AGLE3000 Global Resource

|                      |                                           | S                 | Std.                                |    |

|----------------------|-------------------------------------------|-------------------|-------------------------------------|----|

| Parameter            | Description                               | Min. <sup>1</sup> | Min. <sup>1</sup> Max. <sup>2</sup> |    |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 2.00              | 2.34                                | ns |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 2.09              | 2.51                                | ns |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.18              |                                     | ns |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.15              |                                     | ns |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.42                                | ns |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

# 🌜 Microsemi.

IGLOOe DC and Switching Characteristics

#### 1.2 V DC Core Voltage

#### Table 2-141 • AGLE600 Global Resource

#### Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.14 V

|                      |                                           | Std.                                |      |       |

|----------------------|-------------------------------------------|-------------------------------------|------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> Max. <sup>2</sup> |      | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 2.22                                | 2.67 | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 2.32                                | 2.93 | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width HIGH for Global Clock | 1.40                                |      | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width LOW for Global Clock  | 1.65                                |      | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                                     | 0.61 | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-6 for derating values.

#### Table 2-142 • AGLE3000 Global Resource Commercial-Case Conditions:

|                      |                                           | Std.                                |      |       |

|----------------------|-------------------------------------------|-------------------------------------|------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> Max. <sup>2</sup> |      | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 2.83                                | 3.27 | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 3.00                                | 3.61 | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width HIGH for Global Clock | 1.40                                |      | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width LOW for Global Clock  | 1.65                                |      | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                                     | 0.61 | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

## Timing Waveforms

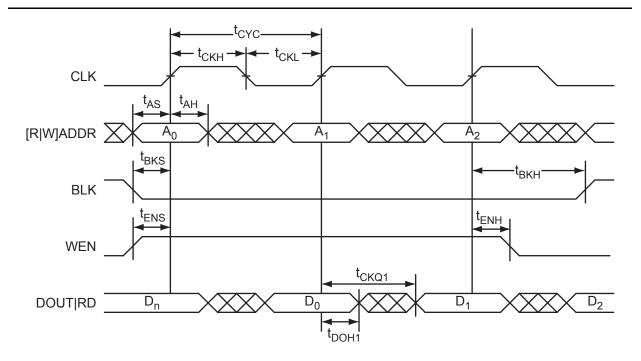

Figure 2-42 • RAM Read for Pass-Through Output. Applicable to Both RAM4K9 and RAM512X18.

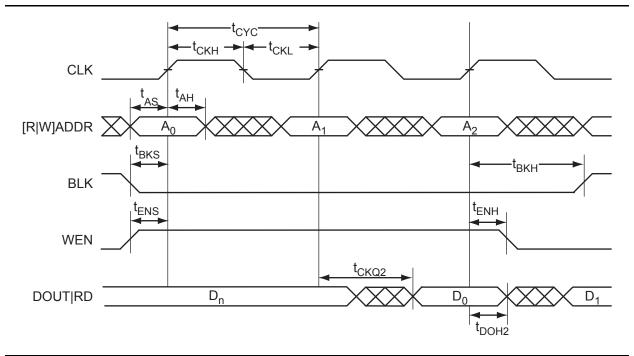

*Figure 2-43* • RAM Read for Pipelined Output. Applicable to Both RAM4K9 and RAM512X18.

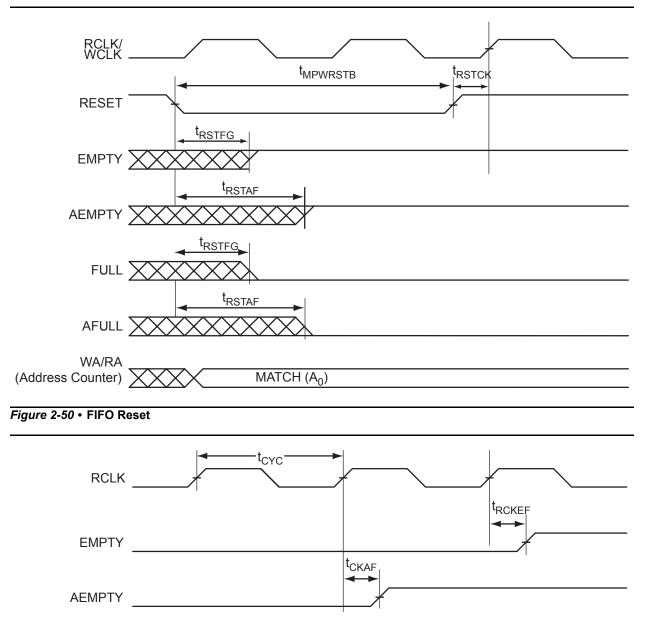

Figure 2-51 • FIFO EMPTY Flag and AEMPTY Flag Assertion

## Applies to 1.2 V DC Core Voltage

#### Table 2-150 • FIFO

Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.14 V

| Parameter            | Description                                       | Std.  | Units |

|----------------------|---------------------------------------------------|-------|-------|

| t <sub>ENS</sub>     | REN, WEN Setup Time                               | 4.13  | ns    |

| t <sub>ENH</sub>     | REN, WEN Hold Time                                | 0.31  | ns    |

| t <sub>BKS</sub>     | BLK Setup Time                                    | 0.47  | ns    |

| t <sub>BKH</sub>     | BLK Hold Time                                     | 0.00  | ns    |

| t <sub>DS</sub>      | Input Data (WD) Setup Time                        | 1.56  | ns    |

| t <sub>DH</sub>      | Input Data (WD) Hold Time                         | 0.49  | ns    |

| t <sub>CKQ1</sub>    | Clock HIGH to New Data Valid on RD (pass-through) | 6.80  | ns    |

| t <sub>CKQ2</sub>    | Clock HIGH to New Data Valid on RD (pipelined)    | 3.62  | ns    |

| t <sub>RCKEF</sub>   | RCLK HIGH to Empty Flag Valid                     |       | ns    |

| t <sub>WCKFF</sub>   | WCLK HIGH to Full Flag Valid                      | 6.85  | ns    |

| t <sub>CKAF</sub>    | Clock HIGH to Almost Empty/Full Flag Valid        | 26.61 | ns    |

| t <sub>RSTFG</sub>   | RESET LOW to Empty/Full Flag Valid                | 7.12  | ns    |

| t <sub>RSTAF</sub>   | RESET LOW to Almost Empty/Full Flag Valid         | 26.33 | ns    |

| t <sub>RSTBQ</sub>   | RESET LOW to Data Out LOW on RD (pass-through)    | 4.09  | ns    |

|                      | RESET LOW to Data Out LOW on RD (pipelined)       | 4.09  | ns    |

| t <sub>REMRSTB</sub> | RESET Removal                                     | 1.23  | ns    |

| t <sub>RECRSTB</sub> | RESET Recovery                                    | 6.58  | ns    |

| t <sub>MPWRSTB</sub> | RESET Minimum Pulse Width                         | 1.18  | ns    |

| t <sub>CYC</sub>     | Clock Cycle Time                                  | 10.90 | ns    |

| F <sub>MAX</sub>     | Maximum Frequency                                 | 92    | MHz   |

#### Table 3-3 • TRST and TCK Pull-Down Recommendations

| VJTAG          | Tie-Off Resistance* |

|----------------|---------------------|

| VJTAG at 3.3 V | 200 Ω to 1 kΩ       |

| VJTAG at 2.5 V | 200 Ω to 1 kΩ       |

| VJTAG at 1.8 V | 500 Ω to 1 kΩ       |

| VJTAG at 1.5 V | 500 Ω to 1 kΩ       |

*Note:* Equivalent parallel resistance if more than one device is on the JTAG chain

#### TDI

#### Test Data Input

Serial input for JTAG boundary scan, ISP, and UJTAG usage. There is an internal weak pull-up resistor on the TDI pin.

#### TDO Test Data Output

Serial output for JTAG boundary scan, ISP, and UJTAG usage.

#### TMS Test Mode Select

The TMS pin controls the use of the IEEE 1532 boundary scan pins (TCK, TDI, TDO, TRST). There is an internal weak pull-up resistor on the TMS pin.

#### TRST Boundary Scan Reset Pin

The TRST pin functions as an active-low input to asynchronously initialize (or reset) the boundary scan circuitry. There is an internal weak pull-up resistor on the TRST pin. If JTAG is not used, an external pull-down resistor could be included to ensure the test access port (TAP) is held in reset mode. The resistor values must be chosen from Table 3-2 and must satisfy the parallel resistance value requirement. The values in Table 3-2 correspond to the resistor recommended when a single device is used, and the equivalent parallel resistor when multiple devices are connected via a JTAG chain.

In critical applications, an upset in the JTAG circuit could allow entrance to an undesired JTAG state. In such cases, Microsemi recommends tying off TRST to GND through a resistor placed close to the FPGA pin.

Note that to operate at all VJTAG voltages, 500  $\Omega$  to 1 k $\Omega$  will satisfy the requirements.

# **Special Function Pins**

#### NC

#### No Connect

This pin is not connected to circuitry within the device. These pins can be driven to any voltage or can be left floating with no effect on the operation of the device.

#### DC

#### Do Not Connect

This pin should not be connected to any signals on the PCB. These pins should be left unconnected.

# Packaging

Semiconductor technology is constantly shrinking in size while growing in capability and functional integration. To enable next-generation silicon technologies, semiconductor packages have also evolved to provide improved performance and flexibility.

Microsemi consistently delivers packages that provide the necessary mechanical and environmental protection to ensure consistent reliability and performance. Microsemi IC packaging technology efficiently supports high-density FPGAs with large-pin-count Ball Grid Arrays (BGAs), but is also flexible enough to accommodate stringent form factor requirements for Chip Scale Packaging (CSP). In addition, Microsemi offers a variety of packages designed to meet your most demanding application and economic requirements for today's embedded and mobile systems.

Package Pin Assignments

|            | FG256            |            | FG256            | FG256      |                  |

|------------|------------------|------------|------------------|------------|------------------|

| Pin Number | AGLE600 Function | Pin Number | AGLE600 Function | Pin Number | AGLE600 Function |

| A1         | GND              | C5         | GAC0/IO02NDB0V0  | E9         | IO21NDB1V0       |

| A2         | GAA0/IO00NDB0V0  | C6         | GAC1/IO02PDB0V0  | E10        | VCCIB1           |

| A3         | GAA1/IO00PDB0V0  | C7         | IO15NDB0V2       | E11        | VCCIB1           |

| A4         | GAB0/IO01NDB0V0  | C8         | IO15PDB0V2       | E12        | VMV1             |

| A5         | IO05PDB0V0       | C9         | IO20PDB1V0       | E13        | GBC2/IO38PDB2V0  |

| A6         | IO10PDB0V1       | C10        | IO25NDB1V0       | E14        | IO37NDB2V0       |

| A7         | IO12PDB0V2       | C11        | IO27PDB1V0       | E15        | IO41NDB2V0       |

| A8         | IO16NDB0V2       | C12        | GBC0/IO33NDB1V1  | E16        | IO41PDB2V0       |

| A9         | IO23NDB1V0       | C13        | VCCPLB           | F1         | IO124PDB7V0      |

| A10        | IO23PDB1V0       | C14        | VMV2             | F2         | IO125PDB7V0      |

| A11        | IO28NDB1V1       | C15        | IO36NDB2V0       | F3         | IO126PDB7V0      |

| A12        | IO28PDB1V1       | C16        | IO42PDB2V0       | F4         | IO130NDB7V1      |

| A13        | GBB1/IO34PDB1V1  | D1         | IO128PDB7V1      | F5         | VCCIB7           |

| A14        | GBA0/IO35NDB1V1  | D2         | IO129PDB7V1      | F6         | GND              |

| A15        | GBA1/IO35PDB1V1  | D3         | GAC2/IO132PDB7V1 | F7         | VCC              |

| A16        | GND              | D4         | VCOMPLA          | F8         | VCC              |

| B1         | GAB2/IO133PDB7V1 | D5         | GNDQ             | F9         | VCC              |

| B2         | GAA2/IO134PDB7V1 | D6         | IO09NDB0V1       | F10        | VCC              |

| B3         | GNDQ             | D7         | IO09PDB0V1       | F11        | GND              |

| B4         | GAB1/IO01PDB0V0  | D8         | IO13PDB0V2       | F12        | VCCIB2           |

| B5         | IO05NDB0V0       | D9         | IO21PDB1V0       | F13        | IO38NDB2V0       |

| B6         | IO10NDB0V1       | D10        | IO25PDB1V0       | F14        | IO40NDB2V0       |

| B7         | IO12NDB0V2       | D11        | IO27NDB1V0       | F15        | IO40PDB2V0       |

| B8         | IO16PDB0V2       | D12        | GNDQ             | F16        | IO45PSB2V1       |

| B9         | IO20NDB1V0       | D13        | VCOMPLB          | G1         | IO124NDB7V0      |

| B10        | IO24NDB1V0       | D14        | GBB2/IO37PDB2V0  | G2         | IO125NDB7V0      |

| B11        | IO24PDB1V0       | D15        | IO39PDB2V0       | G3         | IO126NDB7V0      |

| B12        | GBC1/IO33PDB1V1  | D16        | IO39NDB2V0       | G4         | GFC1/IO120PPB7V0 |

| B13        | GBB0/IO34NDB1V1  | E1         | IO128NDB7V1      | G5         | VCCIB7           |

| B14        | GNDQ             | E2         | IO129NDB7V1      | G6         | VCC              |

| B15        | GBA2/IO36PDB2V0  | E3         | IO132NDB7V1      | G7         | GND              |

| B16        | IO42NDB2V0       | E4         | IO130PDB7V1      | G8         | GND              |

| C1         | IO133NDB7V1      | E5         | VMV0             | G9         | GND              |

| C2         | IO134NDB7V1      | E6         | VCCIB0           | G10        | GND              |

| C3         | VMV7             | E7         | VCCIB0           | G11        | VCC              |

| C4         | VCCPLA           | E8         | IO13NDB0V2       | G12        | VCCIB2           |

Microsemi. IGLOOe Low Power Flash FPGAs

|               | FG484            |               | FG484            | FG484         |                  |

|---------------|------------------|---------------|------------------|---------------|------------------|

| Pin<br>Number | AGLE600 Function | Pin<br>Number | AGLE600 Function | Pin<br>Number | AGLE600 Function |

| C18           | GND              | E9            | IO10NDB0V1       | F22           | NC               |

| C19           | NC               | E10           | IO12NDB0V2       | G1            | IO127NDB7V1      |

| C20           | NC               | E11           | IO16PDB0V2       | G2            | IO127PDB7V1      |

| C21           | NC               | E12           | IO20NDB1V0       | G3            | NC               |

| C22           | VCCIB2           | E13           | IO24NDB1V0       | G4            | IO128PDB7V1      |

| D1            | NC               | E14           | IO24PDB1V0       | G5            | IO129PDB7V1      |

| D2            | NC               | E15           | GBC1/IO33PDB1V1  | G6            | GAC2/IO132PDB7V1 |

| D3            | NC               | E16           | GBB0/IO34NDB1V1  | G7            | VCOMPLA          |

| D4            | GND              | E17           | GNDQ             | G8            | GNDQ             |

| D5            | GAA0/IO00NDB0V0  | E18           | GBA2/IO36PDB2V0  | G9            | IO09NDB0V1       |

| D6            | GAA1/IO00PDB0V0  | E19           | IO42NDB2V0       | G10           | IO09PDB0V1       |

| D7            | GAB0/IO01NDB0V0  | E20           | GND              | G11           | IO13PDB0V2       |

| D8            | IO05PDB0V0       | E21           | NC               | G12           | IO21PDB1V0       |

| D9            | IO10PDB0V1       | E22           | NC               | G13           | IO25PDB1V0       |

| D10           | IO12PDB0V2       | F1            | NC               | G14           | IO27NDB1V0       |

| D11           | IO16NDB0V2       | F2            | IO131NDB7V1      | G15           | GNDQ             |

| D12           | IO23NDB1V0       | F3            | IO131PDB7V1      | G16           | VCOMPLB          |

| D13           | IO23PDB1V0       | F4            | IO133NDB7V1      | G17           | GBB2/IO37PDB2V0  |

| D14           | IO28NDB1V1       | F5            | IO134NDB7V1      | G18           | IO39PDB2V0       |

| D15           | IO28PDB1V1       | F6            | VMV7             | G19           | IO39NDB2V0       |

| D16           | GBB1/IO34PDB1V1  | F7            | VCCPLA           | G20           | IO43PDB2V0       |

| D17           | GBA0/IO35NDB1V1  | F8            | GAC0/IO02NDB0V0  | G21           | IO43NDB2V0       |

| D18           | GBA1/IO35PDB1V1  | F9            | GAC1/IO02PDB0V0  | G22           | NC               |

| D19           | GND              | F10           | IO15NDB0V2       | H1            | NC               |

| D20           | NC               | F11           | IO15PDB0V2       | H2            | NC               |

| D21           | NC               | F12           | IO20PDB1V0       | H3            | VCC              |

| D22           | NC               | F13           | IO25NDB1V0       | H4            | IO128NDB7V1      |

| E1            | NC               | F14           | IO27PDB1V0       | H5            | IO129NDB7V1      |

| E2            | NC               | F15           | GBC0/IO33NDB1V1  | H6            | IO132NDB7V1      |

| E3            | GND              | F16           | VCCPLB           | H7            | IO130PDB7V1      |

| E4            | GAB2/IO133PDB7V1 | F17           | VMV2             | H8            | VMV0             |

| E5            | GAA2/IO134PDB7V1 | F18           | IO36NDB2V0       | H9            | VCCIB0           |

| E6            | GNDQ             | F19           | IO42PDB2V0       | H10           | VCCIB0           |

| E7            | GAB1/IO01PDB0V0  | F20           | NC               | H11           | IO13NDB0V2       |

| E8            | IO05NDB0V0       | F21           | NC               | H12           | IO21NDB1V0       |

Microsemi. IGLOOe Low Power Flash FPGAs

| FG484         |                  | FG484         |                  | FG484         |                  |  |

|---------------|------------------|---------------|------------------|---------------|------------------|--|

| Pin<br>Number | AGLE600 Function | Pin<br>Number | AGLE600 Function | Pin<br>Number | AGLE600 Function |  |

| N8            | VCCIB6           | P21           | IO59PDB3V0       | T12           | IO82NDB5V0       |  |

| N9            | VCC              | P22           | IO58NDB3V0       | T13           | IO74NDB4V1       |  |

| N10           | GND              | R1            | NC               | T14           | IO74PDB4V1       |  |

| N11           | GND              | R2            | IO110PDB6V0      | T15           | GNDQ             |  |

| N12           | GND              | R3            | VCC              | T16           | VCOMPLD          |  |

| N13           | GND              | R4            | IO109NPB6V0      | T17           | VJTAG            |  |

| N14           | VCC              | R5            | IO106NDB6V0      | T18           | GDC0/IO65NDB3V1  |  |

| N15           | VCCIB3           | R6            | IO106PDB6V0      | T19           | GDA1/IO67PDB3V1  |  |

| N16           | IO54NPB3V0       | R7            | GEC0/IO104NPB6V0 | T20           | NC               |  |

| N17           | IO57NPB3V0       | R8            | VMV5             | T21           | IO64PDB3V1       |  |

| N18           | IO55NPB3V0       | R9            | VCCIB5           | T22           | IO62NDB3V1       |  |

| N19           | IO57PPB3V0       | R10           | VCCIB5           | U1            | NC               |  |

| N20           | NC               | R11           | IO84NDB5V0       | U2            | IO107PDB6V0      |  |

| N21           | IO56NDB3V0       | R12           | IO84PDB5V0       | U3            | IO107NDB6V0      |  |

| N22           | IO58PDB3V0       | R13           | VCCIB4           | U4            | GEB1/IO103PDB6V0 |  |

| P1            | NC               | R14           | VCCIB4           | U5            | GEB0/IO103NDB6V0 |  |

| P2            | IO111PDB6V1      | R15           | VMV3             | U6            | VMV6             |  |

| P3            | IO115NPB6V1      | R16           | VCCPLD           | U7            | VCCPLE           |  |

| P4            | IO113NPB6V1      | R17           | GDB1/IO66PPB3V1  | U8            | IO101NPB5V2      |  |

| P5            | IO109PPB6V0      | R18           | GDC1/IO65PDB3V1  | U9            | IO95PPB5V1       |  |

| P6            | IO108PDB6V0      | R19           | IO61NDB3V1       | U10           | IO92PDB5V1       |  |

| P7            | IO108NDB6V0      | R20           | VCC              | U11           | IO90PDB5V1       |  |

| P8            | VCCIB6           | R21           | IO59NDB3V0       | U12           | IO82PDB5V0       |  |

| P9            | GND              | R22           | IO62PDB3V1       | U13           | IO76NDB4V1       |  |

| P10           | VCC              | T1            | NC               | U14           | IO76PDB4V1       |  |

| P11           | VCC              | T2            | IO110NDB6V0      | U15           | VMV4             |  |

| P12           | VCC              | Т3            | NC               | U16           | ТСК              |  |

| P13           | VCC              | T4            | IO105PDB6V0      | U17           | VPUMP            |  |

| P14           | GND              | T5            | IO105NDB6V0      | U18           | TRST             |  |

| P15           | VCCIB3           | Т6            | GEC1/IO104PPB6V0 | U19           | GDA0/IO67NDB3V1  |  |

| P16           | GDB0/IO66NPB3V1  | T7            | VCOMPLE          | U20           | NC               |  |

| P17           | IO60NDB3V1       | Т8            | GNDQ             | U21           | IO64NDB3V1       |  |

| P18           | IO60PDB3V1       | Т9            | GEA2/IO101PPB5V2 | U22           | IO63PDB3V1       |  |

| P19           | IO61PDB3V1       | T10           | IO92NDB5V1       | V1            | NC               |  |

| P20           | NC               | T11           | IO90NDB5V1       | V2            | NC               |  |

Datasheet Information

| Revision                                                                                                  | Changes                                                                                                                                                                                                                                                                                             | Page                |  |  |

|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--|--|

| Revision 8 (Nov 2009)                                                                                     | The version changed to v2.0 for IGLOOe datasheet chapters, indicating the datasheet contains information based on final characterization.                                                                                                                                                           |                     |  |  |

| Product Brief v2.0                                                                                        | The "Pro (Professional) I/O" section was revised to add "Hot-swappable and cold-sparing I/Os."                                                                                                                                                                                                      |                     |  |  |

|                                                                                                           | The "Reprogrammable Flash Technology" section was revised to add "250 MHz (1.5 V systems) and 160 MHz (1.2 V systems) System Performance."                                                                                                                                                          |                     |  |  |

|                                                                                                           | Definitions of hot-swap and cold-sparing were added to the "Pro I/Os with Advanced I/O Standards" section.                                                                                                                                                                                          |                     |  |  |

| DC and Switching<br>Characteristics v2.0                                                                  | $3.3~\rm V$ LVCMOS and $1.2~\rm V$ LVCMOS Wide Range support was added to the datasheet. This affects all tables that contained $3.3~\rm V$ LVCMOS and $1.2~\rm V$ LVCMOS data.                                                                                                                     |                     |  |  |

|                                                                                                           | IIL and IIH input leakage current information was added to all "Minimum and Maximum DC Input and Output Levels" tables.                                                                                                                                                                             | N/A                 |  |  |

|                                                                                                           | Values for 1.2 V wide range DC core supply voltage were added to Table 2-2 • Recommended Operating Conditions 1. Table notes regarding 3.3 V wide range and the core voltage required for programming were added to the table.                                                                      | 2-2                 |  |  |

|                                                                                                           | The data in Table 2-6 • Temperature and Voltage Derating Factors for Timing Delays (1.5 V DC core supply voltage) and Table 2-7 • Temperature and Voltage Derating Factors for Timing Delays (1.2 V DC core supply voltage) was revised.                                                            | 2-6                 |  |  |

|                                                                                                           | 3.3 V LVCMOS wide range data was included in Table 2-13 • Summary of I/O<br>Input Buffer Power (per pin) – Default I/O Software Settings and Table 2-14 •<br>Summary of I/O Output Buffer Power (per pin) – Default I/O Software Settings1.<br>Table notes were added in connection with this data. | 2-9, 2-10           |  |  |

|                                                                                                           | The temperature was revised from 110°C to 100°C in Table 2-31 • Duration of Short Circuit Event before Failure and Table 2-33 • I/O Input Rise Time, Fall Time, and Related I/O Reliability*.                                                                                                       | 2-31, 2-31          |  |  |

|                                                                                                           | The tables in the "Overview of I/O Performance" section and "Detailed I/O DC Characteristics" sectionwere revised to include $3.3$ V LVCMOS and $1.2$ V LVCMOS wide range.                                                                                                                          | 2-20, 2-28          |  |  |

|                                                                                                           | Most tables were updated in the following sections, revising existing values and<br>adding information for 3.3 V and 1.2 V wide range:<br>"Single-Ended I/O Characteristics"<br>"Voltage-Referenced I/O Characteristics"<br>"Differential I/O Characteristics"                                      | 2-32,<br>2-51, 2-62 |  |  |

|                                                                                                           | The value for "Delay range in block: fixed delay" was revised in Table 2-143 • IGLOOe CCC/PLL Specification and Table 2-144 • IGLOOe CCC/PLL Specification.                                                                                                                                         | 2-91, 2-92          |  |  |

|                                                                                                           | The timing characteristics tables for RAM4K9 and RAM512X18 were updated, including renaming of the address collision parameters.                                                                                                                                                                    | 2-98 –<br>2-101     |  |  |

| <b>Revision 7 (Apr 2009)</b><br>Product Brief v1.4<br>DC and Switching<br>Characteristics<br>Advance v0.4 | The –F speed grade is no longer offered for IGLOOe devices and was removed from the documentation. The speed grade column and note regarding –F speed grade were removed from "IGLOOe Ordering Information". The "Speed Grade and Temperature Grade Matrix" section was removed.                    | III, IV             |  |  |