Welcome to **E-XFL.COM**

### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                            |

|---------------------------------|------------------------------------------------------------|

| Product Status                  | Active                                                     |

| Core Processor                  | PowerPC G2_LE                                              |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                             |

| Speed                           | 400MHz                                                     |

| Co-Processors/DSP               | Communications; RISC CPM                                   |

| RAM Controllers                 | DRAM, SDRAM                                                |

| Graphics Acceleration           | No                                                         |

| Display & Interface Controllers | -                                                          |

| Ethernet                        | 10/100Mbps (2)                                             |

| SATA                            | -                                                          |

| USB                             | USB 2.0 (1)                                                |

| Voltage - I/O                   | 3.3V                                                       |

| Operating Temperature           | 0°C ~ 105°C (TA)                                           |

| Security Features               | -                                                          |

| Package / Case                  | 516-BBGA                                                   |

| Supplier Device Package         | 516-FPBGA (27x27)                                          |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8247vrtiea |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Overview

- Floating-point unit (FPU) supports floating-point arithmetic

- Support for cache locking

- Low-power consumption

- Separate power supply for internal logic (1.5 V) and for I/O (3.3 V)

- Separate PLLs for G2\_LE core and for the communications processor module (CPM)

- G2\_LE core and CPM can run at different frequencies for power/performance optimization

- Internal core/bus clock multiplier that provides ratios 2:1, 2.5:1, 3:1, 3.5:1, 4:1, 4.5:1, 5:1, 5:5:1, 6:1, 7:1, 8:1

- Internal CPM/bus clock multiplier that provides ratios 2:1, 2.5:1, 3:1, 3.5:1, 4:1, 5:1, 6:1, 8:1 ratios

- 64-bit data and 32-bit address 60x bus

- Bus supports multiple master designs—up to two external masters

- Supports single transfers and burst transfers

- 64-, 32-, 16-, and 8-bit port sizes controlled by on-chip memory controller

- 60x-to-PCI bridge

- Programmable host bridge and agent

- 32-bit data bus, 66 MHz, 3.3 V

- Synchronous and asynchronous 60x and PCI clock modes

- All internal address space available to external PCI host

- DMA for memory block transfers

- PCI-to-60x address remapping

- System interface unit (SIU)

- Clock synthesizer

- Reset controller

- Real-time clock (RTC) register

- Periodic interrupt timer

- Hardware bus monitor and software watchdog timer

- IEEE 1149.1 JTAG test access port

- Eight bank memory controller

- Glueless interface to SRAM, page mode SDRAM, DRAM, EPROM, Flash, and other user-definable peripherals

- Byte write enables

- 32-bit address decodes with programmable bank size

- Three user-programmable machines, general-purpose chip-select machine, and page mode pipeline SDRAM machine

- Byte selects for 64-bit bus width (60x)

- Dedicated interface logic for SDRAM

- Disable CPU mode

#### Overview

- One of the FCCs supports ATM (MPC8272 and MPC8271 only)—full-duplex SAR at 155 Mbps, 8-bit UTOPIA interface 31 Mphys, AAL5, AAL1, AAL2, AAL0 protocols, TM 4.0 CBR, VBR, UBR, ABR traffic types, up to 64-K external connections

- Three serial communications controllers (SCCs) identical to those on the MPC860 supporting the digital portions of the following protocols:

- Ethernet/IEEE 802.3 CDMA/CS

- HDLC/SDLC and HDLC bus

- Universal asynchronous receiver transmitter (UART)

- Synchronous UART

- Binary synchronous (BiSync) communications

- Transparent

- QUICC multichannel controller (QMC) up to 64 channels

- Independent transmit and receive routing, frame synchronization.

- Serial-multiplexed (full-duplex) input/output 2048, 1544, and 1536 Kbps PCM highways

- Compatible with T1/DS1 24-channel and CEPT E1 32-channel PCM highway, ISDN basic rate, ISDN primary rate, and user defined.

- Subchanneling on each time slot.

- Independent transmit and receive routing, frame synchronization and clocking

- Concatenation of any not necessarily consecutive time slots to channels independently for receiver/transmitter

- Supports H1,H11, and H12 channels

- Allows dynamic allocation of channels

- SCC3 in NMSI mode is not usable when USB is enabled.

- Two serial management controllers (SMCs), identical to those of the MPC860

- Provides management for BRI devices as general-circuit interface (GCI) controllers in time-division-multiplexed (TDM) channels

- Transparent

- UART (low-speed operation)

- One serial peripheral interface identical to the MPC860 SPI

- One I<sup>2</sup>C controller (identical to the MPC860 I<sup>2</sup>C controller)

- Microwire compatible

- Multiple-master, single-master, and slave modes

- Up to two TDM interfaces

- Supports one groups of two TDM channels

- 1024 bytes of SI RAM

- Eight independent baud rate generators and 14 input clock pins for supplying clocks to FCC, SCC, SMC, and USB serial channels

- Four independent 16-bit timers that can be interconnected as two 32-bit timers

- PCI bridge

- PCI Specification revision 2.2-compliant and supports frequencies up to 66 MHz

- On-chip arbitration

- Support for PCI to 60x memory and 60x memory to PCI streaming

- PCI host bridge or peripheral capabilities

- Includes four DMA channels for the following transfers:

- PCI-to-60x to 60x-to-PCI

- 60x-to-PCI to PCI-to-60x

- PCI-to-60x to PCI-to-60x

- 60x-to-PCI to 60x-to-PCI

- Includes the configuration registers required by the PCI standard (which are automatically loaded from the EPROM to configure the MPC8272) and message and doorbell registers

- Supports the I<sub>2</sub>O standard

- Hot-Swap friendly (supports the Hot Swap Specification as defined by PICMG 2.1 R1.0 August 3, 1998)

- Support for 66 MHz, 3.3 V specification

- 60x-PCI bus core logic, which uses a buffer pool to allocate buffers for each port

### **Operating Conditions** 2

This table shows the maximum electrical ratings.

Table 3. Absolute Maximum Ratings<sup>1</sup>

| Rating                           | Symbol           | Value           | Unit |

|----------------------------------|------------------|-----------------|------|

| Core supply voltage <sup>2</sup> | VDD              | -0.3 - 2.25     | ٧    |

| PLL supply voltage <sup>2</sup>  | VCCSYN           | -0.3 - 2.25     | ٧    |

| I/O supply voltage <sup>3</sup>  | VDDH             | -0.3 - 4.0      | ٧    |

| Input voltage <sup>4</sup>       | VIN              | GND(-0.3) - 3.6 | ٧    |

| Junction temperature             | Тј               | 120             | °C   |

| Storage temperature range        | T <sub>STG</sub> | (-55) - (+150)  | °C   |

<sup>1</sup> Absolute maximum ratings are stress ratings only; functional operation (see Table 4) at the maximums is not guaranteed. Stress beyond those listed may affect device reliability or cause permanent damage.

MPC8272 PowerQUICC II Family Hardware Specifications, Rev. 3 Freescale Semiconductor

<sup>&</sup>lt;sup>2</sup> Caution: VDD/VCCSYN must not exceed VDDH by more than 0.4 V during normal operation. It is recommended that VDD/VCCSYN should be raised before or simultaneous with VDDH during power-on reset. VDD/VCCSYN may exceed VDDH by more than 0.4 V during power-on reset for no more than 100 ms.

<sup>&</sup>lt;sup>3</sup> Caution: VDDH can exceed VDD/VCCSYN by 3.3 V during power on reset by no more than 100 mSec. VDDH should not exceed VDD/VCCSYN by more than 2.5 V during normal operation.

<sup>&</sup>lt;sup>4</sup> Caution: VIN must not exceed VDDH by more than 2.5 V at any time, including during power-on reset.

#### **Operating Conditions**

This table lists recommended operational voltage conditions.

Table 4. Recommended Operating Conditions<sup>1</sup>

| Rating                         | Symbol         | Value              | Unit |

|--------------------------------|----------------|--------------------|------|

| Core supply voltage            | VDD            | 1.425 – 575        | V    |

| PLL supply voltage             | VCCSYN         | 1.425 – 575        | V    |

| I/O supply voltage             | VDDH           | 3.135 – 3.465      | V    |

| Input voltage                  | VIN            | GND (-0.3) - 3.465 | V    |

| Junction temperature (maximum) | Tj             | 105 <sup>2</sup>   | °C   |

| Ambient temperature            | T <sub>A</sub> | 0-70 <sup>2</sup>  | °C   |

Caution: These are the recommended and tested operating conditions. Proper operation outside of these conditions is not guaranteed.

This SoC contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (either GND or V<sub>CC</sub>).

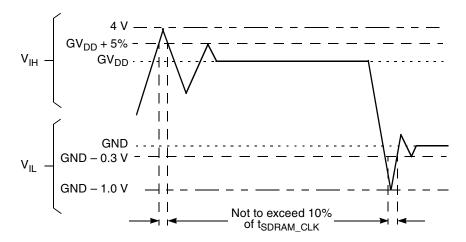

This figure shows the undershoot and overshoot voltage of the 60x bus memory interface of the SoC. Note that in PCI mode the I/O interface is different.

Figure 2. Overshoot/Undershoot Voltage

<sup>&</sup>lt;sup>2</sup> Note that for extended temperature parts the range is  $(-40)_{T_A}$  –  $105_{T_j}$ .

# 3 DC Electrical Characteristics

This table shows DC electrical characteristics.

Table 5. DC Electrical Characteristics<sup>1</sup>

| Characteristic                                                                                                                                                                                                                  | Symbol           | Min | Max   | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|-------|------|

| Input high voltage—all inputs except TCK, TRST and PORESET <sup>2</sup>                                                                                                                                                         | V <sub>IH</sub>  | 2.0 | 3.465 | V    |

| Input low voltage <sup>3</sup>                                                                                                                                                                                                  | V <sub>IL</sub>  | GND | 0.8   | V    |

| CLKIN input high voltage                                                                                                                                                                                                        | V <sub>IHC</sub> | 2.4 | 3.465 | V    |

| CLKIN input low voltage                                                                                                                                                                                                         | V <sub>ILC</sub> | GND | 0.4   | V    |

| Input leakage current, V <sub>IN</sub> = VDDH <sup>4</sup>                                                                                                                                                                      | I <sub>IN</sub>  | _   | 10    | μA   |

| Hi-Z (off state) leakage current, V <sub>IN</sub> = VDDH <sup>2</sup>                                                                                                                                                           | I <sub>OZ</sub>  | _   | 10    | μΑ   |

| Signal low input current, V <sub>IL</sub> = 0.8 V                                                                                                                                                                               | ΙL               | _   | 1     | μΑ   |

| Signal high input current, V <sub>IH</sub> = 2.0 V                                                                                                                                                                              | I <sub>H</sub>   | _   | 1     | μΑ   |

| Output high voltage, I <sub>OH</sub> = -2 mA<br>except UTOPIA mode, and open drain pins<br>In UTOPIA mode <sup>5</sup> (UTOPIA pins only): I <sub>OH</sub> = -8.0mA<br>PA[8-31]<br>PB[18-31]<br>PC[0-1,4-29]<br>PD[7-25, 29-31] | V <sub>ОН</sub>  | 2.4 | _     | V    |

| In UTOPIA mode <sup>5</sup> (UTOPIA pins only): I <sub>OL</sub> = 8.0mA<br>PA[8–31]<br>PB[18–31]<br>PC[0–1,4–29]<br>PD[7–25, 29–31]                                                                                             | V <sub>OL</sub>  | _   | 0.5   | V    |

#### **Thermal Characteristics**

<sup>4</sup> MPC8280, MPC8275VR, MPC8275ZQ only.

## 4 Thermal Characteristics

This table describes thermal characteristics. See Table 2 for information on a given SoC's package. Discussions of each characteristic are provided in Section 4.1, "Estimation with Junction-to-Ambient Thermal Resistance," through Section 4.7, "References." For the these discussions,  $P_D = (V_{DD} \times I_{DD}) + PI/O$ , where PI/O is the power dissipation of the I/O drivers.

**Table 7. Thermal Characteristics**

| Characteristic                       | Symbol          | Value | Unit | Air Flow           |

|--------------------------------------|-----------------|-------|------|--------------------|

| Junction-to-ambient—                 | _               | 27    | 2011 | Natural convection |

| single-layer board <sup>1</sup>      | $R_{	hetaJA}$   | 21    | °C/W | 1 m/s              |

| Junction-to-ambient—                 | $R_{	hetaJA}$   | 19    | 2011 | Natural convection |

| four-layer board                     |                 | 16    | °C/W | 1 m/s              |

| Junction-to-board <sup>2</sup>       | $R_{\theta JB}$ | 11    | °C/W | _                  |

| Junction-to-case <sup>3</sup>        | $R_{	heta JC}$  | 8     | °C/W | _                  |

| Junction-to-package top <sup>4</sup> | $R_{\theta JT}$ | 2     | °C/W | _                  |

Assumes no thermal vias

### 4.1 Estimation with Junction-to-Ambient Thermal Resistance

An estimation of the chip junction temperature, T<sub>I</sub>, in C can be obtained from the following equation:

$$T_{J} = T_{A} + (R_{\theta JA} \times P_{D})$$

where:

$T_A$  = ambient temperature (°C)

$R_{\theta JA}$  = package junction-to-ambient thermal resistance (°C/W)

$P_D$  = power dissipation in package

The junction-to-ambient thermal resistance is an industry standard value that provides a quick and easy estimation of thermal performance. However, the answer is only an estimate; test cases have demonstrated that errors of a factor of two (in the quantity  $T_I - T_A$ ) are possible.

Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

### 4.2 Estimation with Junction-to-Case Thermal Resistance

Historically, the thermal resistance has frequently been expressed as the sum of a junction-to-case thermal resistance and a case-to-ambient thermal resistance:

$$R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$$

where:

$R_{\theta JA}$  = junction-to-ambient thermal resistance (°C/W)

$R_{\theta IC}$  = junction-to-case thermal resistance (°C/W)

$R_{\theta CA}$  = case-to-ambient thermal resistance (°C/W)

$R_{\theta JC}$  is device related and cannot be influenced by the user. The user adjusts the thermal environment to affect the case-to-ambient thermal resistance,  $R_{\theta CA}$ . For instance, the user can change the air flow around the device, add a heat sink, change the mounting arrangement on the printed circuit board, or change the thermal dissipation on the printed circuit board surrounding the device. This thermal model is most useful for ceramic packages with heat sinks where some 90% of the heat flows through the case and the heat sink to the ambient environment. For most packages, a better model is required.

### 4.3 Estimation with Junction-to-Board Thermal Resistance

A simple package thermal model which has demonstrated reasonable accuracy (about 20%) is a two-resistor model consisting of a junction-to-board and a junction-to-case thermal resistance. The junction-to-case thermal resistance covers the situation where a heat sink is used or where a substantial amount of heat is dissipated from the top of the package. The junction-to-board thermal resistance describes the thermal performance when most of the heat is conducted to the printed circuit board. It has been observed that the thermal performance of most plastic packages, especially PBGA packages, is strongly dependent on the board temperature.

If the board temperature is known, an estimate of the junction temperature in the environment can be made using the following equation:

$$T_{J} = T_{B} + (R_{\theta JB} \times P_{D})$$

where:

$R_{\theta JB}$  = junction-to-board thermal resistance (°C/W)

$T_B$  = board temperature (°C)

$P_D$  = power dissipation in package

If the board temperature is known and the heat loss from the package case to the air can be ignored, acceptable predictions of junction temperature can be made. For this method to work, the board and board mounting must be similar to the test board used to determine the junction-to-board thermal resistance, namely a 2s2p (board with a power and a ground plane) and by attaching the thermal balls to the ground plane.

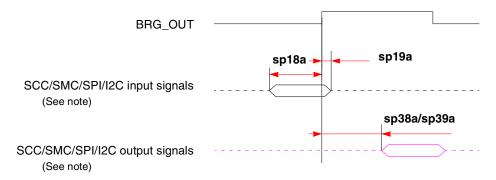

This figure shows the SCC/SMC/SPI/I<sup>2</sup>C internal clock.

Note: There are four possible timing conditions for SCC and SPI:

- 1. Input sampled on the rising edge and output driven on the rising edge (shown).

- 2. Input sampled on the rising edge and output driven on the falling edge.

- 3. Input sampled on the falling edge and output driven on the falling edge.

- 4. Input sampled on the falling edge and output driven on the rising edge.

Figure 6. SCC/SMC/SPI/I<sup>2</sup>C Internal Clock Diagram

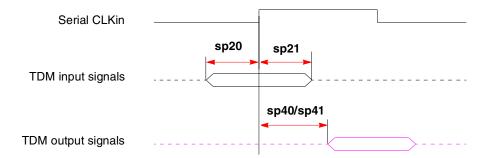

This figure shows TDM input and output signals.

Note: There are four possible TDM timing conditions:

- 1. Input sampled on the rising edge and output driven on the rising edge (shown).

- 2. Input sampled on the rising edge and output driven on the falling edge.

- 3. Input sampled on the falling edge and output driven on the falling edge.

- 4. Input sampled on the falling edge and output driven on the rising edge.

Figure 7. TDM Signal Diagram

#### **AC Electrical Characteristics**

#### NOTE

The UPM machine outputs change on the internal tick determined by the memory controller programming; the AC specifications are relative to the internal tick. Note that SDRAM and GPCM machine outputs change on CLKin's rising edge.

## 6.3 JTAG Timings

This table lists the JTAG timings.

Table 15. JTAG Timings<sup>1</sup>

| Parameter                                                                 | Symbol <sup>2</sup>                        | Min      | Max      | Unit     | Notes        |

|---------------------------------------------------------------------------|--------------------------------------------|----------|----------|----------|--------------|

| JTAG external clock frequency of operation                                | f <sub>JTG</sub>                           | 0        | 33.3     | MHz      | _            |

| JTAG external clock cycle time                                            | t <sub>JTG</sub>                           | 30       | _        | ns       | _            |

| JTAG external clock pulse width measured at 1.4V                          | t <sub>JTKHKL</sub>                        | 15       | _        | ns       | _            |

| JTAG external clock rise and fall times                                   | t <sub>JTGR</sub> and t <sub>JTGF</sub>    | 0        | 5        | ns       | 6            |

| TRST assert time                                                          | t <sub>TRST</sub>                          | 25       | _        | ns       | 3, 6         |

| Input setup times  Boundary-scan data  TMS, TDI                           | t <sub>JTDVKH</sub><br>t <sub>JTIVKH</sub> | 4<br>4   | _<br>_   | ns<br>ns | 4, 7<br>4, 7 |

| Input hold times  Boundary-scan data  TMS, TDI                            | t <sub>JTDXKH</sub><br>t <sub>JTIXKH</sub> | 10<br>10 |          | ns<br>ns | 4, 7<br>4, 7 |

| Output valid times  Boundary-scan data TDO                                | t <sub>JTKLDV</sub><br>t <sub>JTKLOV</sub> | _<br>_   | 10<br>10 | ns<br>ns | 5, 7<br>5, 7 |

| Output hold times  Boundary-scan data TDO                                 | t <sub>JTKLDX</sub><br>t <sub>JTKLOX</sub> | 1<br>1   |          | ns<br>ns | 5, 7<br>5, 7 |

| JTAG external clock to output high impedance<br>Boundary-scan data<br>TDO | t <sub>JTKLDZ</sub><br>t <sub>JTKLOZ</sub> | 1        | 10<br>10 | ns<br>ns | 5, 6<br>5, 6 |

All outputs are measured from the midpoint voltage of the falling/rising edge of t<sub>TCLK</sub> to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50-Ω load. Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

<sup>&</sup>lt;sup>3</sup> TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

<sup>&</sup>lt;sup>4</sup> Non-JTAG signal input timing with respect to t<sub>TCLK</sub>.

<sup>&</sup>lt;sup>5</sup> Non-JTAG signal output timing with respect to t<sub>TCLK</sub>.

<sup>&</sup>lt;sup>6</sup> Guaranteed by design.

<sup>&</sup>lt;sup>7</sup> Guaranteed by design and device characterization.

Table 17. Clock Configurations for PCI Host Mode (PCI\_MODCK=0)<sup>1,2</sup> (continued)

| Mode <sup>3</sup>      | Bus (    |          | CPM<br>Multiplication |       | Clock<br>Hz) | CPU<br>Multiplication |       | Clock<br>Hz) | PCI<br>Division     |      | Clock<br>Hz) |

|------------------------|----------|----------|-----------------------|-------|--------------|-----------------------|-------|--------------|---------------------|------|--------------|

| MODCK_H-<br>MODCK[1-3] | Low      | High     | Factor <sup>4</sup>   | Low   | High         | Factor <sup>5</sup>   | Low   | High         | Factor <sup>6</sup> | Low  | High         |

| 1011_100               | 80.0     | 106.7    | 2.5                   | 200.0 | 266.6        | 4                     | 320.0 | 426.6        | 4                   | 50.0 | 66.7         |

| 1011_101               | 80.0     | 106.7    | 2.5                   | 200.0 | 266.6        | 4.5                   | 360.0 | 480.0        | 4                   | 50.0 | 66.7         |

|                        |          |          |                       |       |              |                       |       |              |                     |      |              |

| 1101_000               | 100.0    | 133.3    | 2.5                   | 250.0 | 333.3        | 3                     | 300.0 | 400.0        | 5                   | 50.0 | 66.7         |

| 1101_001               | 100.0    | 133.3    | 2.5                   | 250.0 | 333.3        | 3.5                   | 350.0 | 466.6        | 5                   | 50.0 | 66.7         |

| 1101_010               | 100.0    | 133.3    | 2.5                   | 250.0 | 333.3        | 4                     | 400.0 | 533.3        | 5                   | 50.0 | 66.7         |

| 1101_011               | 100.0    | 133.3    | 2.5                   | 250.0 | 333.3        | 4.5                   | 450.0 | 599.9        | 5                   | 50.0 | 66.7         |

| 1101_100               | 100.0    | 133.3    | 2.5                   | 250.0 | 333.3        | 5                     | 500.0 | 666.6        | 5                   | 50.0 | 66.7         |

|                        |          |          |                       |       |              |                       |       |              |                     |      |              |

| 1101_101               | 125.0    | 166.7    | 2                     | 250.0 | 333.3        | 3                     | 375.0 | 500.0        | 5                   | 50.0 | 66.7         |

| 1101_110               | 125.0    | 166.7    | 2                     | 250.0 | 333.3        | 4                     | 500.0 | 666.6        | 5                   | 50.0 | 66.7         |

|                        |          |          |                       |       |              |                       |       |              |                     |      |              |

| 1110_000               | 100.0    | 133.3    | 3                     | 300.0 | 400.0        | 3.5                   | 350.0 | 466.6        | 6                   | 50.0 | 66.7         |

| 1110_001               | 100.0    | 133.3    | 3                     | 300.0 | 400.0        | 4                     | 400.0 | 533.3        | 6                   | 50.0 | 66.7         |

| 1110_010               | 100.0    | 133.3    | 3                     | 300.0 | 400.0        | 4.5                   | 450.0 | 599.9        | 6                   | 50.0 | 66.7         |

| 1110_011               | 100.0    | 133.3    | 3                     | 300.0 | 400.0        | 5                     | 500.0 | 666.6        | 6                   | 50.0 | 66.7         |

| 1110_100               | 100.0    | 133.3    | 3                     | 300.0 | 400.0        | 5.5                   | 550.0 | 733.3        | 6                   | 50.0 | 66.7         |

|                        |          |          |                       |       |              |                       |       |              |                     |      |              |

| 1100_000               | Reserved |          |                       |       |              |                       |       |              |                     |      |              |

| 1100_001               |          | Reserved |                       |       |              |                       |       |              |                     |      |              |

| 1100_010               |          | Reserved |                       |       |              |                       |       |              |                     |      |              |

The "low" values are the minimum allowable frequencies for a given clock mode. The minimum bus frequency in a table entry guarantees only the required minimum CPU operating frequency. The "high" values are for the purpose of illustration only. Users must select a mode and input bus frequency so that the resulting configuration does not exceed the frequency rating of the user's device. The minimum CPU frequency is 150 MHz for commercial temperature devices and 175 MHz for extended temperature devices. The minimum CPM frequency is 120 MHz.

$CPM\_CLK/PCI\_CLK = (PCIDF + 1) / 2.$

<sup>&</sup>lt;sup>2</sup> PCI\_MODCK determines the PCI clock frequency range. SeeTable 18 for lower range configurations.

<sup>&</sup>lt;sup>3</sup> MODCK\_H = hard reset configuration word [28–31] (see Section 5.4 in the SoC reference manual). MODCK[1-3] = three hardware configuration pins.

<sup>&</sup>lt;sup>4</sup> CPM multiplication factor = CPM clock/bus clock

<sup>&</sup>lt;sup>5</sup> CPU multiplication factor = Core PLL multiplication factor

<sup>&</sup>lt;sup>6</sup> CPM\_CLK/PCI\_CLK ratio. When PCI\_MODCK = 0, the ratio of CPM\_CLK/PCI\_CLK should be calculated from SCCR[PCIDF] as follows:

### **Clock Configuration Modes**

<sup>6</sup> CPM\_CLK/PCI\_CLK ratio. When PCI\_MODCK = 1, the ratio of CPM\_CLK/PCI\_CLK should be calculated from PCIDF as follows:

PCIDF = 3 > CPM\_CLK/PCI\_CLK = 4

PCIDF = 5 > CPM\_CLK/PCI\_CLK = 6

PCIDF = 7 > CPM\_CLK/PCI\_CLK = 8

PCIDF = 9 > CPM\_CLK/PCI\_CLK = 5

PCIDF = B > CPM\_CLK/PCI\_CLK = 6

## 7.2 PCI Agent Mode

These tables show configurations for PCI agent mode. The frequency values listed are for the purpose of illustration only. Users must select a mode and input bus frequency so that the resulting configuration does not exceed the frequency rating of the user's device. Note that in PCI agent mode the input clock is PCI clock.

Table 19. Clock Configurations for PCI Agent Mode (PCI\_MODCK=0)<sup>1,2</sup>

| Mode <sup>3</sup>      | PCI Clock<br>(MHz) |      | CPM<br>Multiplication |         | Clock<br>Hz) | CPU<br>- Multiplication - |       | Clock<br>Hz) | Bus<br>Division |      | Clock<br>Hz) |

|------------------------|--------------------|------|-----------------------|---------|--------------|---------------------------|-------|--------------|-----------------|------|--------------|

| MODCK_H-<br>MODCK[1-3] | Low                | High | Factor <sup>4</sup>   | Low     | High         | Factor <sup>5</sup>       | Low   | High         | Factor          | Low  | High         |

|                        |                    |      | Defau                 | ılt Mod | es (MO       | DCK_H=0000)               |       |              |                 |      |              |

| 0000_000               | 60.0               | 66.7 | 2                     | 120.0   | 133.3        | 2.5                       | 150.0 | 166.7        | 2               | 60.0 | 66.7         |

| 0000_001               | 50.0               | 66.7 | 2                     | 100.0   | 133.3        | 3                         | 150.0 | 200.0        | 2               | 50.0 | 66.7         |

| 0000_010               | 50.0               | 66.7 | 3                     | 150.0   | 200.0        | 3                         | 150.0 | 200.0        | 3               | 50.0 | 66.7         |

| 0000_011               | 50.0               | 66.7 | 3                     | 150.0   | 200.0        | 4                         | 200.0 | 266.6        | 3               | 50.0 | 66.7         |

| 0000_100               | 50.0               | 66.7 | 3                     | 150.0   | 200.0        | 3                         | 180.0 | 240.0        | 2.5             | 60.0 | 80.0         |

| 0000_101               | 50.0               | 66.7 | 3                     | 150.0   | 200.0        | 3.5                       | 210.0 | 280.0        | 2.5             | 60.0 | 80.0         |

| 0000_110               | 50.0               | 66.7 | 4                     | 200.0   | 266.6        | 3.5                       | 233.3 | 311.1        | 3               | 66.7 | 88.9         |

| 0000_111               | 50.0               | 66.7 | 4                     | 200.0   | 266.6        | 3                         | 240.0 | 320.0        | 2.5             | 80.0 | 106.7        |

|                        |                    |      | F                     | ull Con | figurat      | ion Modes                 |       |              |                 |      |              |

| 0001_001               | 60.0               | 66.7 | 2                     | 120.0   | 133.3        | 5                         | 150.0 | 166.7        | 4               | 30.0 | 33.3         |

| 0001_010               | 50.0               | 66.7 | 2                     | 100.0   | 133.3        | 6                         | 150.0 | 200.0        | 4               | 25.0 | 33.3         |

| 0001_011               | 50.0               | 66.7 | 2                     | 100.0   | 133.3        | 7                         | 175.0 | 233.3        | 4               | 25.0 | 33.3         |

| 0001_100               | 50.0               | 66.7 | 2                     | 100.0   | 133.3        | 8                         | 200.0 | 266.6        | 4               | 25.0 | 33.3         |

|                        |                    |      |                       |         |              |                           |       |              |                 |      |              |

| 0010_001               | 50.0               | 66.7 | 3                     | 150.0   | 200.0        | 3                         | 180.0 | 240.0        | 2.5             | 60.0 | 80.0         |

| 0010_010               | 50.0               | 66.7 | 3                     | 150.0   | 200.0        | 3.5                       | 210.0 | 280.0        | 2.5             | 60.0 | 80.0         |

| 0010_011               | 50.0               | 66.7 | 3                     | 150.0   | 200.0        | 4                         | 240.0 | 320.0        | 2.5             | 60.0 | 80.0         |

| 0010_100               | 50.0               | 66.7 | 3                     | 150.0   | 200.0        | 4.5                       | 270.0 | 360.0        | 2.5             | 60.0 | 80.0         |

|                        |                    |      |                       |         |              |                           |       |              |                 |      |              |

MPC8272 PowerQUICC II Family Hardware Specifications, Rev. 3

Table 19. Clock Configurations for PCI Agent Mode (PCI\_MODCK=0)<sup>1,2</sup> (continued)

| Mode <sup>3</sup>      | PCI (    | Clock<br>Hz) | CPM<br>Multiplication | _     | Clock<br>Hz) | CPU<br>Multiplication |       | Clock<br>Hz) | Bus<br>Division |       | Clock<br>Hz) |

|------------------------|----------|--------------|-----------------------|-------|--------------|-----------------------|-------|--------------|-----------------|-------|--------------|

| MODCK_H-<br>MODCK[1-3] | Low      | High         | Factor <sup>4</sup>   | Low   | High         | Factor <sup>5</sup>   | Low   | High         | Factor          | Low   | High         |

| 1100_101               | 50.0     | 66.7         | 6                     | 300.0 | 400.0        | 4                     | 400.0 | 533.3        | 3               | 100.0 | 133.3        |

| 1100_110               | 50.0     | 66.7         | 6                     | 300.0 | 400.0        | 4.5                   | 450.0 | 599.9        | 3               | 100.0 | 133.3        |

| 1100_111               | 50.0     | 66.7         | 6                     | 300.0 | 400.0        | 5                     | 500.0 | 666.6        | 3               | 100.0 | 133.3        |

| 1101_000               | 50.0     | 66.7         | 6                     | 300.0 | 400.0        | 5.5                   | 550.0 | 733.3        | 3               | 100.0 | 133.3        |

|                        |          |              |                       |       |              |                       |       |              |                 |       |              |

| 1101_001               | 50.0     | 66.7         | 6                     | 300.0 | 400.0        | 3.5                   | 420.0 | 559.9        | 2.5             | 120.0 | 160.0        |

| 1101_010               | 50.0     | 66.7         | 6                     | 300.0 | 400.0        | 4                     | 480.0 | 639.9        | 2.5             | 120.0 | 160.0        |

| 1101_011               | 50.0     | 66.7         | 6                     | 300.0 | 400.0        | 4.5                   | 540.0 | 719.9        | 2.5             | 120.0 | 160.0        |

| 1101_100               | 50.0     | 66.7         | 6                     | 300.0 | 400.0        | 5                     | 600.0 | 799.9        | 2.5             | 120.0 | 160.0        |

|                        |          |              |                       |       |              |                       |       |              |                 |       |              |

| 1110_000               | 50.0     | 66.7         | 5                     | 250.0 | 333.3        | 2.5                   | 312.5 | 416.6        | 2               | 125.0 | 166.7        |

| 1110_001               | 50.0     | 66.7         | 5                     | 250.0 | 333.3        | 3                     | 375.0 | 500.0        | 2               | 125.0 | 166.7        |

| 1110_010               | 50.0     | 66.7         | 5                     | 250.0 | 333.3        | 3.5                   | 437.5 | 583.3        | 2               | 125.0 | 166.7        |

| 1110_011               | 50.0     | 66.7         | 5                     | 250.0 | 333.3        | 4                     | 500.0 | 666.6        | 2               | 125.0 | 166.7        |

|                        |          |              |                       |       |              |                       |       |              |                 |       |              |

| 1110_100               | 50.0     | 66.7         | 5                     | 250.0 | 333.3        | 4                     | 333.3 | 444.4        | 3               | 83.3  | 111.1        |

| 1110_101               | 50.0     | 66.7         | 5                     | 250.0 | 333.3        | 4.5                   | 375.0 | 500.0        | 3               | 83.3  | 111.1        |

| 1110_110               | 50.0     | 66.7         | 5                     | 250.0 | 333.3        | 5                     | 416.7 | 555.5        | 3               | 83.3  | 111.1        |

| 1110_111               | 50.0     | 66.7         | 5                     | 250.0 | 333.3        | 5.5                   | 458.3 | 611.1        | 3               | 83.3  | 111.1        |

|                        |          |              |                       |       |              |                       |       |              |                 |       |              |

| 1100_000               | Reserved |              |                       |       |              |                       |       |              |                 |       |              |

| 1100_001               |          | Reserved     |                       |       |              |                       |       |              |                 |       |              |

| 1100_010               |          | Reserved     |                       |       |              |                       |       |              |                 |       |              |

The "low" values are the minimum allowable frequencies for a given clock mode. The minimum bus frequency in a table entry guarantees only the required minimum CPU operating frequency. The "high" values are for the purpose of illustration only. Users must select a mode and input bus frequency so that the resulting configuration does not exceed the frequency rating of the user's device. The minimum CPU frequency is 150 MHz for commercial temperature devices and 175 MHz for extended temperature devices. The minimum CPM frequency is 120 MHz.

<sup>&</sup>lt;sup>2</sup> PCI\_MODCK determines the PCI clock frequency range. See Table 20 for lower range configurations.

<sup>&</sup>lt;sup>3</sup> MODCK\_H = hard reset configuration word [28–31] (see Section 5.4 in the SoC reference manual). MODCK[1-3] = three hardware configuration pins.

<sup>&</sup>lt;sup>4</sup> CPM multiplication factor = CPM clock/bus clock

<sup>&</sup>lt;sup>5</sup> CPU multiplication factor = Core PLL multiplication factor

Table 20. Clock Configurations for PCI Agent Mode (PCI\_MODCK=1)<sup>1,2</sup> (continued)

| Mode <sup>3</sup>      |      | Clock<br>Hz) | CPM<br>Multiplication |       | Clock<br>Hz) | CPU<br>Multiplication |       | Clock<br>Hz) | Bus<br>Division |      | Clock<br>Hz) |

|------------------------|------|--------------|-----------------------|-------|--------------|-----------------------|-------|--------------|-----------------|------|--------------|

| MODCK_H-<br>MODCK[1-3] | Low  | High         | Factor <sup>4</sup>   | Low   | High         | Factor <sup>5</sup>   | Low   | High         | Factor          | Low  | High         |

| 1110_000               | 25.0 | 50.0         | 5                     | 125.0 | 250.0        | 2.5                   | 156.3 | 312.5        | 2               | 62.5 | 125.0        |

| 1110_001               | 25.0 | 50.0         | 5                     | 125.0 | 250.0        | 3                     | 187.5 | 375.0        | 2               | 62.5 | 125.0        |

| 1110_010               | 28.6 | 50.0         | 5                     | 142.9 | 250.0        | 3.5                   | 250.0 | 437.5        | 2               | 71.4 | 125.0        |

| 1110_011               | 25.0 | 50.0         | 5                     | 125.0 | 250.0        | 4                     | 250.0 | 500.0        | 2               | 62.5 | 125.0        |

|                        |      |              |                       |       |              |                       |       |              |                 |      |              |

| 1110_100               | 25.0 | 50.0         | 5                     | 125.0 | 250.0        | 4                     | 166.7 | 333.3        | 3               | 41.7 | 83.3         |

| 1110_101               | 25.0 | 50.0         | 5                     | 125.0 | 250.0        | 4.5                   | 187.5 | 375.0        | 3               | 41.7 | 83.3         |

| 1110_110               | 25.0 | 50.0         | 5                     | 125.0 | 250.0        | 5                     | 208.3 | 416.7        | 3               | 41.7 | 83.3         |

| 1110_111               | 25.0 | 50.0         | 5                     | 125.0 | 250.0        | 5.5                   | 229.2 | 458.3        | 3               | 41.7 | 83.3         |

|                        |      |              |                       |       |              |                       |       |              |                 |      |              |

| 1100_000               |      | Reserved     |                       |       |              |                       |       |              |                 |      |              |

| 1100_001               |      | Reserved     |                       |       |              |                       |       |              |                 |      |              |

| 1100_010               |      |              |                       |       |              | Reserved              |       |              |                 |      |              |

The "low" values are the minimum allowable frequencies for a given clock mode. The minimum bus frequency in a table entry guarantees only the required minimum CPU operating frequency. The "high" values are for the purpose of illustration only. Users must select a mode and input bus frequency so that the resulting configuration does not exceed the frequency rating of the user's device. The minimum CPU frequency is 150 MHz for commercial temperature devices and 175 MHz for extended temperature devices. The minimum CPM frequency is 120 MHz.

## 8 Pinout

This figure and table show the pin assignments and pinout for the 516 PBGA package.

<sup>&</sup>lt;sup>2</sup> PCI\_MODCK determines the PCI clock frequency range. See Table 19 for higher range configurations.

<sup>&</sup>lt;sup>3</sup> MODCK\_H = hard reset configuration word [28–31] (see Section 5.4 in the SoC reference manual). MODCK[1-3] = three hardware configuration pins.

<sup>&</sup>lt;sup>4</sup> CPM multiplication factor = CPM clock/bus clock

<sup>&</sup>lt;sup>5</sup> CPU multiplication factor = Core PLL multiplication factor

### **Pinout**

Table 21. Pinout (continued)

| Pin Na                                 | Pin Name             |      |  |  |  |  |  |  |

|----------------------------------------|----------------------|------|--|--|--|--|--|--|

| MPC8272/MPC8248 and<br>MPC8271/MPC8247 | MPC8272/MPC8271 Only | Ball |  |  |  |  |  |  |

| D4                                     | D46                  |      |  |  |  |  |  |  |

| D4                                     | 7                    | F2   |  |  |  |  |  |  |

| D4                                     | 8                    | AB1  |  |  |  |  |  |  |

| D4                                     | 9                    | U4   |  |  |  |  |  |  |

| D5                                     | 0                    | U1   |  |  |  |  |  |  |

| D5                                     | 1                    | R3   |  |  |  |  |  |  |

| D5                                     | 2                    | N3   |  |  |  |  |  |  |

| D5                                     | 3                    | K2   |  |  |  |  |  |  |

| D5                                     | 4                    | H5   |  |  |  |  |  |  |

| D5                                     | 5                    | F4   |  |  |  |  |  |  |

| D5                                     | 6                    | AA3  |  |  |  |  |  |  |

| D5                                     | 7                    | U5   |  |  |  |  |  |  |

| D5                                     | 8                    | U2   |  |  |  |  |  |  |

| D5                                     | 9                    | P5   |  |  |  |  |  |  |

| D6                                     | 0                    | M3   |  |  |  |  |  |  |

| D6                                     | 1                    | K4   |  |  |  |  |  |  |

| D6                                     | 2                    | H3   |  |  |  |  |  |  |

| D6                                     | 3                    | E1   |  |  |  |  |  |  |

| ĪRQ3/CKSTP_C                           | OUT/EXT_BR3          | B16  |  |  |  |  |  |  |

| IRQ4/CORE_SRE                          | SET/EXT_BG3          | C15  |  |  |  |  |  |  |

| IRQ5/TBEN/EX                           | T_DBG3/CINT          | Y4   |  |  |  |  |  |  |

| PSDV                                   | /AL                  | C19  |  |  |  |  |  |  |

| TA                                     |                      | AA4  |  |  |  |  |  |  |

| TE.                                    | Ā                    | AB6  |  |  |  |  |  |  |

| GBL/II                                 | RQ1                  | D15  |  |  |  |  |  |  |

| CI/BADDR                               | 29/IRQ2              | D16  |  |  |  |  |  |  |

| WT/BADDF                               | R30/IRQ3             | C16  |  |  |  |  |  |  |

| BADDR31/ĪĪ                             | RQ5/CINT             | E17  |  |  |  |  |  |  |

| CPU_BR/I                               | NT_OUT               | B20  |  |  |  |  |  |  |

| CS                                     | 0                    | AE6  |  |  |  |  |  |  |

| CS                                     | 1                    | AD7  |  |  |  |  |  |  |

MPC8272 PowerQUICC II Family Hardware Specifications, Rev. 3

Table 21. Pinout (continued)

| Pin 1                                  | Name                  |      |  |  |  |  |  |

|----------------------------------------|-----------------------|------|--|--|--|--|--|

| MPC8272/MPC8248 and<br>MPC8271/MPC8247 | MPC8272/MPC8271 Only  | Ball |  |  |  |  |  |

| C                                      | CS2                   |      |  |  |  |  |  |

| C                                      | <del>S</del> 3        | AC8  |  |  |  |  |  |

| C                                      | <del>S4</del>         | AF6  |  |  |  |  |  |

| C                                      | <del>S</del> 5        | AD8  |  |  |  |  |  |

| CS6/BC                                 | TL1/SMI               | AC9  |  |  |  |  |  |

| CS7/TL                                 | BISYNC                | AB9  |  |  |  |  |  |

| BADDR                                  | 27/ <del>IRQ1</del>   | AB8  |  |  |  |  |  |

| BADDR                                  | 28/IRQ2               | AC7  |  |  |  |  |  |

| ALE/                                   | ÎRQ4                  | AF4  |  |  |  |  |  |

| BC                                     | TLO                   | AF3  |  |  |  |  |  |

| PWE0/PSDI                              | DQM0/PBS0             | AD6  |  |  |  |  |  |

| PWE1/PSDI                              | DQM1/PBS1             | AE5  |  |  |  |  |  |

| PWE2/PSDI                              | DQM2/PBS2             | AE3  |  |  |  |  |  |

| PWE3/PSDI                              | DQM3/PBS3             | AF2  |  |  |  |  |  |

| PWE4/PSDI                              | DQM4/PBS4             | AC6  |  |  |  |  |  |

| PWE5/PSDI                              | DQM5/PBS5             | AC5  |  |  |  |  |  |

| PWE6/PSDI                              | DQM6/PBS6             | AD4  |  |  |  |  |  |

| PWE7/PSDI                              | DQM7/PBS7             | AB5  |  |  |  |  |  |

| PSDA10                                 | )/PGPL0               | AE2  |  |  |  |  |  |

| PSDWE                                  | PGPL1                 | AD3  |  |  |  |  |  |

| POE/PSDF                               | RAS/PGPL2             | AB4  |  |  |  |  |  |

| PSDCAS                                 | S/PGPL3               | AC3  |  |  |  |  |  |

| PGTA/PUPM                              | WAIT/PGPL4            | AD2  |  |  |  |  |  |

| PSDAMU                                 | JX/PGPL5              | AC2  |  |  |  |  |  |

| PCI_N                                  | MODE <sup>1</sup>     | AD22 |  |  |  |  |  |

| PCI_CFG0 (Pi                           | CI_HOST_EN)           | AC21 |  |  |  |  |  |

| PCI_CFG1 (F                            | PCI_CFG1 (PCI_ARB_EN) |      |  |  |  |  |  |

| PCI_CFG2 (E                            | DLL_ENABLE)           | AE23 |  |  |  |  |  |

| PCI_                                   | PAR                   | AF12 |  |  |  |  |  |

| PCI_F                                  | RAME                  | AD15 |  |  |  |  |  |

| PCI_                                   | TRDY                  | AF16 |  |  |  |  |  |

### **Pinout**

Table 21. Pinout (continued)

| Pin Name                               |                      |      |

|----------------------------------------|----------------------|------|

| MPC8272/MPC8248 and<br>MPC8271/MPC8247 | MPC8272/MPC8271 Only | Ball |

| PCI_                                   | IRDY                 | AF15 |

| PCI_                                   | STOP                 | AE15 |

| PCI_D                                  | EVSEL                | AE14 |

| PCI_I                                  | DSEL                 | AC17 |

| PCI_I                                  | PERR                 | AD14 |

| PCI_S                                  | SERR                 | AD13 |

| PCI_I                                  | REQ0                 | AE20 |

| PCI_REQ1/0                             | CPCI_HS_ES           | AF14 |

| PCI_                                   | GNT0                 | AD20 |

| PCI_GNT1/C                             | PCI_HS_LED           | AE13 |

| PCI_GNT2/CF                            | PCI_HS_ENUM          | AF21 |

| PCI_                                   | RST                  | AF22 |

| PCI_                                   | INTA                 | AE21 |

| PCI_I                                  | REQ2                 | AB14 |

| DLL                                    | OUT                  | AC22 |

| PCI_                                   | PCI_AD0              |      |

| PCI_                                   | AD1                  | AE10 |

| PCI_                                   | PCI_AD2              |      |

| PCI_AD3                                |                      | AD10 |

| PCI_AD4                                |                      | AE9  |

| PCI_                                   | AD5                  | AF8  |

| PCI_AD6                                |                      | AC10 |

| PCI_AD7                                |                      | AE11 |

| PCI_                                   | _AD8                 | AB11 |

| PCI_AD9                                |                      | AF10 |

| PCI_AD10                               |                      | AF9  |

| PCI_AD11                               |                      | AB12 |

| PCI_                                   | AD12                 | AC12 |

| PCI_                                   | AD13                 | AD12 |

| PCI_AD14                               |                      | AF11 |

| PCI_                                   | PCI_AD15             |      |

MPC8272 PowerQUICC II Family Hardware Specifications, Rev. 3

Table 21. Pinout (continued)

| Pin Name                            |                      |      |  |

|-------------------------------------|----------------------|------|--|

| MPC8272/MPC8248 and MPC8271/MPC8247 | MPC8272/MPC8271 Only | Ball |  |

| PCI_                                | AD16                 | AE16 |  |

| PCI_                                | AD17                 | AF17 |  |

| PCI                                 | AD18                 | AD16 |  |

| PCI                                 | AD19                 | AC16 |  |

| PCI                                 | AD20                 | AF18 |  |

| PCI                                 | AD21                 | AB16 |  |

| PCI                                 | AD22                 | AD17 |  |

| PCI                                 | AD23                 | AF19 |  |

| PCI                                 | AD24                 | AB17 |  |

| PCI                                 | AD25                 | AF20 |  |

| PCI                                 | AD26                 | AE19 |  |

| PCI                                 | AD27                 | AC18 |  |

| PCI_AD28                            |                      | AB18 |  |

| PCI                                 | PCI_AD29             |      |  |

| PCI                                 | AD30                 | AD21 |  |

| PCI_AD31                            |                      | AC20 |  |

| PCI_C                               | 0/BE0                | AE12 |  |

| PCI_C                               | PCI_C1/BE1           |      |  |

| PCI_C                               | PCI_C2/BE2           |      |  |

| PCI_C3/BE3                          |                      | AE18 |  |

| ĪRQ0/NI                             | ĪRQ0/NMI_OUT         |      |  |

| TRST <sup>2</sup>                   |                      | E21  |  |

| тск                                 |                      | B22  |  |

| TMS                                 |                      | C23  |  |

| TDI                                 |                      | B24  |  |

| TDO                                 |                      | A22  |  |

| TF                                  | TRIS                 |      |  |

| PORESET <sup>2</sup> /PCI_RST       |                      | C24  |  |

| HRE                                 | D22                  |      |  |

| SRE                                 | F22                  |      |  |

| RSTCONF                             |                      | A24  |  |

Table 21. Pinout (continued)

| Pin Name                                                 |                      |                   |  |

|----------------------------------------------------------|----------------------|-------------------|--|

| MPC8272/MPC8248 and MPC8271/MPC8247                      | MPC8272/MPC8271 Only | Ball              |  |

| PA31/FCC1_MII_COL                                        | FCC1_UT_TXENB        | G22 <sup>3</sup>  |  |

| PB18/FCC2_M                                              | II_HDLC_RXD3         | T25 <sup>3</sup>  |  |

| PB19/FCC2_M                                              | II_HDLC_RXD2         | P22 <sup>3</sup>  |  |

| PB20/FCC2_MII_HDLC_RMII_RXD1                             |                      | L25 <sup>3</sup>  |  |

| PB21/FCC2_MII_HDLC_RMII_RXD0/FCC2_TRAN_RXD               |                      | J26 <sup>3</sup>  |  |

| PB22/FCC2_MII_HDLC_TXD0/FCC2_TRAN_TXD/<br>FCC2_RMII_TXD0 |                      | U23 <sup>3</sup>  |  |

| PB23/FCC2_MII_HDLC_                                      | TXD1/FCC2_RMII_TXD1  | U26 <sup>3</sup>  |  |

| PB24/FCC2_MII_HDLC_TXD2/L1RSYNCB2                        |                      | M24 <sup>3</sup>  |  |

| PB25/FCC2_MII_HDLC_TXD3/L1TSYNCB2                        |                      | M23 <sup>3</sup>  |  |

| PB26/FCC2_MII                                            | _CRS/L1RXDB2         | H24 <sup>3</sup>  |  |

| PB27/FCC2_MII_COL/L1TXDB2                                |                      | E25 <sup>3</sup>  |  |

| PB28/FCC2_MII_RMII_RX_ER/ <del>FCC2_RTS</del> /TXD1      |                      | D26 <sup>3</sup>  |  |

| PB29/FCC2_MII_RMII_TX_EN                                 |                      | K21 <sup>3</sup>  |  |

| PB30/FCC2_MII_RX_DV/FCC2_RMII_CRS_DV                     |                      | D24 <sup>3</sup>  |  |

| PB31/FCC2_MII_TX_ER                                      |                      | E23 <sup>3</sup>  |  |

| PC0/DREQ3/BRGO7/SMSYN1/L1CLKOA2                          |                      | AF23 <sup>3</sup> |  |

| PC1/BRGO6/L1RQA2                                         |                      | AD23 <sup>3</sup> |  |

| PC4/SMRXD1/SI2_L1ST4/FCC2_CD                             |                      | AB22 <sup>3</sup> |  |

| PC5/SMTXD1/SI2_L1ST3/FCC2_CTS                            |                      | AE24 <sup>3</sup> |  |

| PC6/FCC1_CD/SI2_L1ST2                                    | FCC1_UT_RXADDR2      | AF24 <sup>3</sup> |  |

| PC7/FCC1_CTS                                             | FCC1_UT_TXADDR2      | AE26 <sup>3</sup> |  |

| PC8/CD4/RTS1/SI2_L1ST2/CTS3                              |                      | AC24 <sup>3</sup> |  |

| PC9/CTS4/L1TSYNCA2                                       |                      | AA23 <sup>3</sup> |  |

| PC10/CD3/USB_RN                                          |                      | AB25 <sup>3</sup> |  |

| PC11/CTS3/USB_RP/L1TXD3A2                                |                      | V22 <sup>3</sup>  |  |

| PC12                                                     | FCC1_UT_RXADDR1      | AA26 <sup>3</sup> |  |

| PC13/BRGO5                                               | FCC1_UT_TXADDR1      | V23 <sup>3</sup>  |  |

| PC14/CD1                                                 | FCC1_UT_RXADDR0      | W24 <sup>3</sup>  |  |

| PC15/CTS1                                                | FCC1_UT_TXADDR0      | U24 <sup>3</sup>  |  |

| PC16/                                                    | CLK16                | T23 <sup>3</sup>  |  |

Table 21. Pinout (continued)

| Pin Name                               |                      |                   |  |  |

|----------------------------------------|----------------------|-------------------|--|--|

| MPC8272/MPC8248 and<br>MPC8271/MPC8247 | MPC8272/MPC8271 Only | Ball              |  |  |

| PC17/CLK15/BR                          | GO8/DONE2            | T26 <sup>3</sup>  |  |  |

| PC18/CLK14                             | /TGATE2              | R26 <sup>3</sup>  |  |  |

| PC19/CLK13/BRGO7/TGATE1                |                      | P24 <sup>3</sup>  |  |  |

| PC20/CLK12/ <del>USBOE</del>           |                      | L26 <sup>3</sup>  |  |  |

| PC21/CLK11/BRGO6/CP_INT                |                      | L24 <sup>3</sup>  |  |  |

| PC22/CLK10/DONE3                       | FCC1_UT_TXPRTY       | L23 <sup>3</sup>  |  |  |

| PC23/CLK9/BRGO5/ <del>DACK3/CD1</del>  |                      | K24 <sup>3</sup>  |  |  |

| PC24/CLK8/TIN3/TOU                     | T4/DREQ2/BRGO1       | K23 <sup>3</sup>  |  |  |

| PC25/CLK7/BRGO4                        | /DACK2/SPISEL        | F26 <sup>3</sup>  |  |  |

| PC26/CLK6/TOI                          | JT3/TMCLK            | H23 <sup>3</sup>  |  |  |

| PC27/CLK5/BRGO3/TOUT1                  | FCC1_UT_RXPRTY       | K22 <sup>3</sup>  |  |  |

| PC28/CLK4/TIN1/TOUT2/SPICLK            |                      | D25 <sup>3</sup>  |  |  |

| PC29/CLK3/TIN2/BRGO2/CTS1              |                      | F24 <sup>3</sup>  |  |  |

| PD7/SMSYN2                             | FCC1_UT_TXADDR3      | AB21 <sup>3</sup> |  |  |

| PD14/I20                               | CSCL                 | AC26 <sup>3</sup> |  |  |

| PD15/I20                               | CSDA                 | Y23 <sup>3</sup>  |  |  |

| PD16/SPIMISO                           | FCC1_UT_TXPRTY       | AA25 <sup>3</sup> |  |  |

| PD17/BRGO2/SPIMOSI                     | FCC1_UT_RXPRTY       | Y26 <sup>3</sup>  |  |  |

| PD18/SPICLK                            | FCC1_UT_RXADDR4      | W25 <sup>3</sup>  |  |  |

| PD19/SPISEL/BRGO1                      | FCC1_UT_TXADDR4      | V25 <sup>3</sup>  |  |  |

| PD20/RTS4/L1RSYNCA2                    |                      | R24 <sup>3</sup>  |  |  |

| PD21/TXD4/L1RXD0A2                     |                      | P23 <sup>3</sup>  |  |  |

| PD22/RXD4/L1TXD0A2                     |                      | N25 <sup>3</sup>  |  |  |

| PD23/RTS3/                             | USB_TP               | K26 <sup>3</sup>  |  |  |

| PD24/TXD3/USB_TN                       |                      | K25 <sup>3</sup>  |  |  |

| PD25/RXD3/USB_RXD                      |                      | J25 <sup>3</sup>  |  |  |

| PD29/RTS1                              | FCC1_UT_RXADDR3      | C26 <sup>3</sup>  |  |  |

| PD30/TXD1                              |                      | E24 <sup>3</sup>  |  |  |

| PD31/RXD1                              |                      | B25 <sup>3</sup>  |  |  |

| VCCSYN                                 |                      | C18               |  |  |

| VCCSYN1                                |                      | K6                |  |  |

## **Table 23. Document Revision History (continued)**

| Revision | Date    | Substantive Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1.2      | 09/2005 | <ul> <li>Added 133-MHz to the list of frequencies in the opening sentence of Section 6, "AC Electrical Characteristics".</li> <li>Added 133 MHz columns to Table 9, Table 11, Table 12, and Table 13.</li> <li>Added footnote 2 to Table 13.</li> <li>Added the conditions note directly above Table 12.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 1.1      | 01/2005 | Modification for correct display of assertion level ("overbar") for some signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 1.0      | 12/2004 | <ul> <li>Section 1.1: Added 8:1 ratio to Internal CPM/bus clock multiplier values</li> <li>Section 2: removed voltage tracking note</li> <li>Table 3: Note 2 updated regarding VDD/VCCSYN relationship to VDDH during power-on reset</li> <li>Table 4: Updated VDD and VCCSYN to 1.425 V - 1.575 V</li> <li>Table 8: Note 2 updated to reflect VIH=2.5 for TCK, TRST, PORESET; request for external pull-up removed.</li> <li>Section 4.6: Updated description of layout practices</li> <li>Table 8: Note 3 added regarding IIC compatibility</li> <li>Table 8: Updated nominal and maximum power dissipation values</li> <li>Table 9: updated PCI impedance to 27Ω, updated 60x and MEMC values and added note to reflect configurable impedance</li> <li>Section 6: Added sentence providing derating factor</li> <li>Section 6.1: added Note: Rise/Fall Time on CPM Input Pins</li> <li>Table 9: updated values for following specs: sp36b, sp37a, sp38a, sp39a, sp38b, sp40, sp41, sp42, sp43, sp42a</li> <li>Table 11: updated values for following specs: sp16a, sp16b, sp18a, sp18b, sp20, sp21, sp22</li> <li>Section 6.2: added spread spectrum clocking note</li> <li>Section 6.2: added CLKIN jitter note</li> <li>Table 12: combined specs sp11 and sp11a</li> <li>Table 13: sp30 Data Bus minimum delay values changed to 0.8</li> <li>Section 7: unit of ns added to Tval notes</li> <li>Section 7: Updated all notes to reflect updated CPU Fmin of 150 MHz commercial temp devices, 175 MHz extended temp; CPM Fmin of 120 MHz.</li> <li>Section 7, "Clock Configuration Modes": Updated all table footnotes reflect updated CPU Fmin of 150 MHz commercial temp devices, 175 MHz extended temp; CPM Fmin of 120 MHz.</li> <li>Table 21: remove DONE3 from PC12</li> <li>Table 21: signals referring to TDMs C2 and D2 removed</li> </ul> |  |