Welcome to **E-XFL.COM**

### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

# **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                       |

|---------------------------------|-----------------------------------------------------------------------|

| Product Status                  | Active                                                                |

| Core Processor                  | PowerPC G2_LE                                                         |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 400MHz                                                                |

| Co-Processors/DSP               | Communications; RISC CPM, Security; SEC                               |

| RAM Controllers                 | DRAM, SDRAM                                                           |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10/100Mbps (2)                                                        |

| SATA                            | -                                                                     |

| USB                             | USB 2.0 (1)                                                           |

| Voltage - I/O                   | 3.3V                                                                  |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                      |

| Security Features               | Cryptography, Random Number Generator                                 |

| Package / Case                  | 516-BBGA                                                              |

| Supplier Device Package         | 516-PBGA (27x27)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8248vrtiea |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Overview

# 1 Overview

This table shows the functionality supported by each SoC in the MPC8272 family.

Table 1. MPC8272 PowerQUICC II Family Functionality

|                                            | SoCs                 |          |         |         |         |  |  |  |  |

|--------------------------------------------|----------------------|----------|---------|---------|---------|--|--|--|--|

| Functionality                              |                      | MPC8272  | MPC8248 | MPC8271 | MPC8247 |  |  |  |  |

|                                            | Package <sup>1</sup> | 516 PBGA |         |         |         |  |  |  |  |

| Serial communications controllers (SCC     | s)                   | 3        | 3       | 3       | 3       |  |  |  |  |

| QUICC multi-channel controller (QMC)       |                      | Yes      | Yes     | Yes     | Yes     |  |  |  |  |

| Fast communication controllers (FCCs)      |                      | 2        | 2       | 2       | 2       |  |  |  |  |

| I-Cache (Kbyte)                            |                      | 16       | 16      | 16      | 16      |  |  |  |  |

| D-Cache (Kbyte)                            |                      | 16       | 16      | 16      | 16      |  |  |  |  |

| Ethernet (10/100)                          |                      | 2        | 2       | 2       | 2       |  |  |  |  |

| UTOPIA II Ports                            |                      | 1        | 0       | 1       | 0       |  |  |  |  |

| Multi-channel controllers (MCCs)           |                      | 0        | 0       | 0       | 0       |  |  |  |  |

| PCI bridge                                 |                      | Yes      | Yes     | Yes     | Yes     |  |  |  |  |

| Transmission convergence (TC) layer        |                      | _        | _       | _       | _       |  |  |  |  |

| Inverse multiplexing for ATM (IMA)         |                      | _        | _       | _       | _       |  |  |  |  |

| Universal serial bus (USB) 2.0 full/low ra | ate                  | 1        | 1       | 1       | 1       |  |  |  |  |

| Security engine (SEC)                      |                      | Yes      | Yes     | _       | _       |  |  |  |  |

<sup>1</sup> See Table 2.

Devices in the MPC8272 family are available in two packages—the VR or ZQ package—as shown in . For package ordering information, see Section 10, "Ordering Information."

Table 2. MPC8272 PowerQUICC II Device Packages

| Code<br>(Package) | VR<br>(516 PBGA—Lead free) | ZQ<br>(516 PBGA—Lead spheres) |

|-------------------|----------------------------|-------------------------------|

|                   | MPC8272VR                  | MPC8272ZQ                     |

| Device            | MPC8248VR                  | MPC8248ZQ                     |

| Device            | MPC8271VR                  | MPC8271ZQ                     |

|                   | MPC8247VR                  | MPC8247ZQ                     |

- Integrated security engine (SEC) (MPC8272 and MPC8248 only)

- Supports DES, 3DES, MD-5, SHA-1, AES, PKEU, RNG and RC-4 encryption algorithms in hardware

- Communications processor module (CPM)

- Embedded 32-bit communications processor (CP) uses a RISC architecture for flexible support for communications peripherals

- Interfaces to G2\_LE core through on-chip dual-port RAM and DMA controller. (Dual-port RAM size is 16 KB plus 4 KB dedicated instruction RAM.)

- Microcode tracing capabilities

- Eight CPM trap registers

- Universal serial bus (USB) controller

- Supports USB 2.0 full/low rate compatible

- USB host mode

- Supports control, bulk, interrupt, and isochronous data transfers

- CRC16 generation and checking

- NRZI encoding/decoding with bit stuffing

- Supports both 12- and 1.5-Mbps data rates (automatic generation of preamble token and data rate configuration). Note that low-speed operation requires an external hub.

- Flexible data buffers with multiple buffers per frame

- Supports local loopback mode for diagnostics (12 Mbps only)

- Supports USB slave mode

- Four independent endpoints support control, bulk, interrupt, and isochronous data transfers

- CRC16 generation and checking

- CRC5 checking

- NRZI encoding/decoding with bit stuffing

- 12- or 1.5-Mbps data rate

- Flexible data buffers with multiple buffers per frame

- Automatic retransmission upon transmit error

- Serial DMA channels for receive and transmit on all serial channels

- Parallel I/O registers with open-drain and interrupt capability

- Virtual DMA functionality executing memory-to-memory and memory-to-I/O transfers

- Two fast communication controllers (FCCs) supporting the following protocols:

- 10-/100-Mbit Ethernet/IEEE 802.3 CDMA/CS interface through media independent interface (MII)

- Transparent

- HDLC—up to T3 rates (clear channel)

# 3 DC Electrical Characteristics

This table shows DC electrical characteristics.

Table 5. DC Electrical Characteristics<sup>1</sup>

| Characteristic                                                                                                                                                                                                                  | Symbol           | Min | Max   | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|-------|------|

| Input high voltage—all inputs except TCK, TRST and PORESET <sup>2</sup>                                                                                                                                                         | V <sub>IH</sub>  | 2.0 | 3.465 | V    |

| Input low voltage <sup>3</sup>                                                                                                                                                                                                  | V <sub>IL</sub>  | GND | 0.8   | V    |

| CLKIN input high voltage                                                                                                                                                                                                        | V <sub>IHC</sub> | 2.4 | 3.465 | V    |

| CLKIN input low voltage                                                                                                                                                                                                         | V <sub>ILC</sub> | GND | 0.4   | V    |

| Input leakage current, V <sub>IN</sub> = VDDH <sup>4</sup>                                                                                                                                                                      | I <sub>IN</sub>  | _   | 10    | μA   |

| Hi-Z (off state) leakage current, V <sub>IN</sub> = VDDH <sup>2</sup>                                                                                                                                                           | I <sub>OZ</sub>  | _   | 10    | μΑ   |

| Signal low input current, V <sub>IL</sub> = 0.8 V                                                                                                                                                                               | ΙL               | _   | 1     | μΑ   |

| Signal high input current, V <sub>IH</sub> = 2.0 V                                                                                                                                                                              | I <sub>H</sub>   | _   | 1     | μΑ   |

| Output high voltage, I <sub>OH</sub> = -2 mA<br>except UTOPIA mode, and open drain pins<br>In UTOPIA mode <sup>5</sup> (UTOPIA pins only): I <sub>OH</sub> = -8.0mA<br>PA[8-31]<br>PB[18-31]<br>PC[0-1,4-29]<br>PD[7-25, 29-31] | V <sub>ОН</sub>  | 2.4 | _     | V    |

| In UTOPIA mode <sup>5</sup> (UTOPIA pins only): I <sub>OL</sub> = 8.0mA<br>PA[8–31]<br>PB[18–31]<br>PC[0–1,4–29]<br>PD[7–25, 29–31]                                                                                             | V <sub>OL</sub>  | _   | 0.5   | V    |

### **DC Electrical Characteristics**

# Table 5. DC Electrical Characteristics<sup>1</sup> (continued)

| Characteristic           | Symbol          | Min | Max | Unit |

|--------------------------|-----------------|-----|-----|------|

| I <sub>OL</sub> = 6.0mA  | V <sub>OL</sub> | _   | 0.4 | V    |

| BR                       |                 |     |     |      |

| BG/IRQ6                  |                 |     |     |      |

| ABB/IRQ2                 |                 |     |     |      |

| TS                       |                 |     |     |      |

| A[0-31]                  |                 |     |     |      |

| TT[0-4]                  |                 |     |     |      |

| TBST                     |                 |     |     |      |

| TSIZE[0-3]               |                 |     |     |      |

| AACK                     |                 |     |     |      |

| ARTRY DBG/IRQ7           |                 |     |     |      |

| DBB/IRQ7                 |                 |     |     |      |

| D[0-63]                  |                 |     |     |      |

| IRQ3/CKSTP_OUT/EXT_BR3   |                 |     |     |      |

| IRQ4/CORE_SRESET/EXT_BG3 |                 |     |     |      |

| IRQ5/TBEN/EXT_DBG3/CINT  |                 |     |     |      |

| PSDVAL                   |                 |     |     |      |

| TA                       |                 |     |     |      |

| TEA                      |                 |     |     |      |

| GBL/IRQ1                 |                 |     |     |      |

| CI/BADDR29/IRQ2          |                 |     |     |      |

| WT/BADDR30/IRQ3          |                 |     |     |      |

| BADDR31/IRQ5/CINT        |                 |     |     |      |

| CPU_BR/INT_OUT           |                 |     |     |      |

| IRQ0/NMI_OUT             |                 |     |     |      |

| PORESET/PCI_RST          |                 |     |     |      |

| HRESET                   |                 |     |     |      |

| SRESET                   |                 |     |     |      |

| RSTCONF                  |                 |     |     |      |

# **DC Electrical Characteristics**

<sup>5</sup> MPC8272 and MPC8271 only.

# Table 6.

| Characteristic                                                                                                                                                 | Symbol           | Min | Max   | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|-------|------|

| Input high voltage—all inputs except TCK, TRST and PORESET <sup>1</sup>                                                                                        | V <sub>IH</sub>  | 2.0 | 3.465 | V    |

| Input low voltage                                                                                                                                              | V <sub>IL</sub>  | GND | 0.8   | V    |

| CLKIN input high voltage                                                                                                                                       | V <sub>IHC</sub> | 2.4 | 3.465 | V    |

| CLKIN input low voltage                                                                                                                                        | V <sub>ILC</sub> | GND | 0.4   | V    |

| Input leakage current, V <sub>IN</sub> = VDDH <sup>2</sup>                                                                                                     | I <sub>IN</sub>  |     | 10    | μA   |

| Hi-Z (off state) leakage current, V <sub>IN</sub> = VDDH <sup>2</sup>                                                                                          | l <sub>oz</sub>  | _   | 10    | μA   |

| Signal low input current, $V_{IL} = 0.8 \text{ V}^3$                                                                                                           | IL               |     | 1     | μA   |

| Signal high input current, V <sub>IH</sub> = 2.0 V                                                                                                             | I <sub>H</sub>   |     | 1     | μA   |

| Output high voltage, I <sub>OH</sub> = -2 mA except UTOPIA mode, and open drain pins  In UTOPIA mode <sup>4</sup> (UTOPIA pins only): I <sub>OH</sub> = -8.0mA | V <sub>OH</sub>  | 2.4 | _     | V    |

| In UTOPIA mode <sup>4</sup> (UTOPIA pins only): I <sub>OL</sub> = 8.0mA                                                                                        | V <sub>OL</sub>  | _   | 0.5   | V    |

| G                                                                                                                                                              | Vol              |     | 0.4   | V    |

**Thermal Characteristics**

# 4.4 Estimation Using Simulation

When the board temperature is not known, a thermal simulation of the application is needed. The simple two-resistor model can be used with the thermal simulation of the application, or a more accurate and complex model of the package can be used in the thermal simulation.

# 4.5 Experimental Determination

To determine the junction temperature of the device in the application after prototypes are available, the thermal characterization parameter ( $\Psi_{JT}$ ) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using the following equation:

$$T_J = T_T + (\Psi_{JT} \times P_D)$$

where:

$\Psi_{IT}$  = thermal characterization parameter

$T_T$  = thermocouple temperature on top of package

$P_D$  = power dissipation in package

The thermal characterization parameter is measured per JEDEC JESD51-2 specification using a 40-gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the case to avoid measurement errors caused by cooling effects of the thermocouple wire.

# 4.6 Layout Practices

Each VDD and VDDH pin should be provided with a low-impedance path to the board's power supplies. Each ground pin should likewise be provided with a low-impedance path to ground. The power supply pins drive distinct groups of logic on chip. The VDD and VDDH power supplies should be bypassed to ground using bypass capacitors located as close as possible to the four sides of the package. For filtering high frequency noise, a capacitor of 0.1uF on each VDD and VDDH pin is recommended. Further, for medium frequency noise, a total of 2 capacitors of 47uF for VDD and 2 capacitors of 47uF for VDDH are also recommended. The capacitor leads and associated printed circuit traces connecting to chip VDD, VDDH and ground should be kept to less than half an inch per capacitor lead. Boards should employ separate inner layers for power and GND planes.

All output pins on the SoC have fast rise and fall times. Printed circuit (PC) trace interconnection length should be minimized to minimize overdamped conditions and reflections caused by these fast output switching times. This recommendation particularly applies to the address and data buses. Maximum PC trace lengths of six inches are recommended. Capacitance calculations should consider all device loads as well as parasitic capacitances due to the PC traces. Attention to proper PCB layout and bypassing becomes especially critical in systems with higher capacitive loads because these loads create higher transient currents in the VDD and GND circuits. Pull up all unused inputs or signals that will be inputs during reset. Special care should be taken to minimize the noise levels on the PLL supply pins.

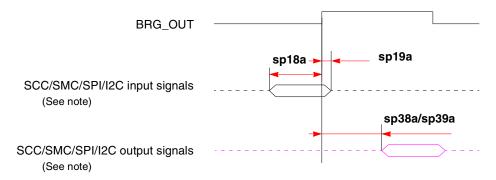

This figure shows the SCC/SMC/SPI/I<sup>2</sup>C internal clock.

Note: There are four possible timing conditions for SCC and SPI:

- 1. Input sampled on the rising edge and output driven on the rising edge (shown).

- 2. Input sampled on the rising edge and output driven on the falling edge.

- 3. Input sampled on the falling edge and output driven on the falling edge.

- 4. Input sampled on the falling edge and output driven on the rising edge.

Figure 6. SCC/SMC/SPI/I<sup>2</sup>C Internal Clock Diagram

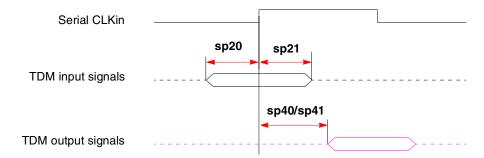

This figure shows TDM input and output signals.

Note: There are four possible TDM timing conditions:

- 1. Input sampled on the rising edge and output driven on the rising edge (shown).

- 2. Input sampled on the rising edge and output driven on the falling edge.

- 3. Input sampled on the falling edge and output driven on the falling edge.

- 4. Input sampled on the falling edge and output driven on the rising edge.

Figure 7. TDM Signal Diagram

#### **AC Electrical Characteristics**

# **NOTE**

Activating data pipelining (setting BRx[DR] in the memory controller) improves the AC timing.

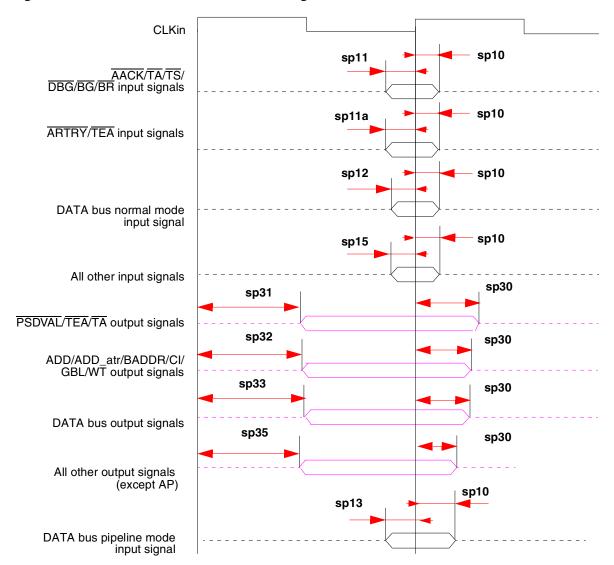

This figure shows the interaction of several bus signals.

Figure 9. Bus Signals

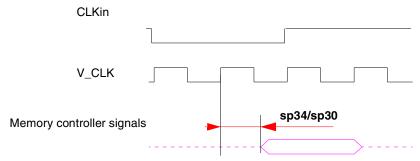

This figure shows signal behavior in MEMC mode.

Figure 10. MEMC Mode Diagram

#### **NOTE**

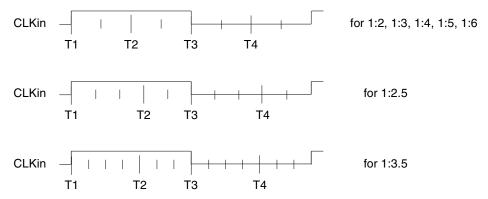

Generally, all SoC bus and system output signals are driven from the rising edge of the input clock (CLKin). Memory controller signals, however, trigger on four points within a CLKin cycle. Each cycle is divided by four internal ticks: T1, T2, T3, and T4. T1 always occurs at the rising edge, and T3 at the falling edge, of CLKin. However, the spacing of T2 and T4 depends on the PLL clock ratio selected, as shown in Table 14.

**Table 14. Tick Spacing for Memory Controller Signals**

| PLL Clock Ratio         | Tick Spacing (T1 Occurs at the Rising Edge of CLKin) |           |             |  |  |  |  |  |

|-------------------------|------------------------------------------------------|-----------|-------------|--|--|--|--|--|

| PLE CIOCK NATIO         | T2                                                   | Т3        | Т4          |  |  |  |  |  |

| 1:2, 1:3, 1:4, 1:5, 1:6 | 1/4 CLKin                                            | 1/2 CLKin | 3/4 CLKin   |  |  |  |  |  |

| 1:2.5                   | 3/10 CLKin                                           | 1/2 CLKin | 8/10 CLKin  |  |  |  |  |  |

| 1:3.5                   | 4/14 CLKin                                           | 1/2 CLKin | 11/14 CLKin |  |  |  |  |  |

This table is a representation of the information in Table 14.

Figure 11. Internal Tick Spacing for Memory Controller Signals

Freescale Semiconductor 25

MPC8272 PowerQUICC II Family Hardware Specifications, Rev. 3

As shown in this table, the clocking mode is set according to two sources:

- PCI\_CFG[0]— An input signal. Also defined as "PCI\_HOST\_EN." See Chapter 6, "External Signals," and Chapter 9, "PCI Bridge," in the SoC reference manual.

- PCI\_MODCK—Bit 27 in the Hard Reset Configuration Word. See Chapter 5, "Reset," in the SoC reference manual.

| Pi                      | ins                    | Clocking Mode | PCI Clock Frequency Range (MHz)   | Reference |  |

|-------------------------|------------------------|---------------|-----------------------------------|-----------|--|

| PCI_CFG[0] <sup>1</sup> | PCI_MODCK <sup>2</sup> | Clocking wode | For Clock Frequency Hange (WITIZ) | neierence |  |

| 0                       | 0                      | PCI host      | 50–66                             | Table 17  |  |

| 0                       | 1                      | ]             | 25–50                             | Table 18  |  |

| 1                       | 0                      | PCI agent     | 50–66                             | Table 19  |  |

| 1                       | 1                      |               | 25–50                             | Table 20  |  |

**Table 16. SoC Clocking Modes**

Within each mode, the configuration of bus, core, PCI, and CPM frequencies is determined by seven bits during the power-on reset—three hardware configuration pins (MODCK[1–3]) and four bits from hardware configuration word[28-31] (MODCK\_H). Both the PLLs and the dividers are set according to the selected clock operation mode as described in the following sections.

### NOTE

Clock configurations change only after PORESET is asserted.

# **NOTE: Tval (Output Hold)**

The minimum Tval = 2 ns when PCI MODCK = 1, and the minimum Tval = 1 ns when PCI\_MODCK = 0. Therefore, designers should use clock configurations that fit this condition to achieve PCI-compliant AC timing.

#### 7.1 **PCI Host Mode**

These tables show configurations for PCI host mode. The frequency values listed are for the purpose of illustration only. Users must select a mode and input bus frequency so that the resulting configuration does not exceed the frequency rating of the user's device. Note that in PCI host mode the input clock is the bus clock.

MPC8272 PowerQUICC II Family Hardware Specifications, Rev. 3 Freescale Semiconductor 27

PCI\_HOST\_EN

<sup>&</sup>lt;sup>2</sup> Determines PCI clock frequency range.

Table 17. Clock Configurations for PCI Host Mode  $(PCI\_MODCK=0)^{1,2}$

| Mode <sup>3</sup>      |      | Clock<br>Hz) | CPM                                   |         | Clock<br>Hz) | CPU                                   |       | Clock<br>Hz) | PCI                             | PCI C<br>(MH |      |

|------------------------|------|--------------|---------------------------------------|---------|--------------|---------------------------------------|-------|--------------|---------------------------------|--------------|------|

| MODCK_H-<br>MODCK[1-3] | Low  | High         | Multiplication<br>Factor <sup>4</sup> | Low     | High         | Multiplication<br>Factor <sup>5</sup> | Low   | High         | Division<br>Factor <sup>6</sup> | Low          | High |

|                        |      |              | Defau                                 | ılt Mod | es (MO       | DCK_H=0000)                           |       |              |                                 |              |      |

| 0000_000               | 60.0 | 66.7         | 2                                     | 120.0   | 133.3        | 2.5                                   | 150.0 | 166.7        | 2                               | 60.0         | 66.7 |

| 0000_001               | 50.0 | 66.7         | 2                                     | 100.0   | 133.3        | 3                                     | 150.0 | 200.0        | 2                               | 50.0         | 66.7 |

| 0000_010               | 60.0 | 80.0         | 2.5                                   | 150.0   | 200.0        | 3                                     | 180.0 | 240.0        | 3                               | 50.0         | 66.7 |

| 0000_011               | 60.0 | 80.0         | 2.5                                   | 150.0   | 200.0        | 3.5                                   | 210.0 | 280.0        | 3                               | 50.0         | 66.7 |

| 0000_100               | 60.0 | 80.0         | 2.5                                   | 150.0   | 200.0        | 4                                     | 240.0 | 320.0        | 3                               | 50.0         | 66.7 |

| 0000_101               | 50.0 | 66.7         | 3                                     | 150.0   | 200.0        | 3                                     | 150.0 | 200.0        | 3                               | 50.0         | 66.7 |

| 0000_110               | 50.0 | 66.7         | 3.5                                   | 150.0   | 200.0        | 3.5                                   | 175.0 | 233.3        | 3                               | 50.0         | 66.7 |

| 0000_111               | 50.0 | 66.7         | 3                                     | 150.0   | 200.0        | 4                                     | 200.0 | 266.6        | 3                               | 50.0         | 66.7 |

|                        | ı    | ı            | F                                     | ull Cor | nfigurati    | on Modes                              | ı     | I            |                                 |              | 1    |

| 0001_000               | 50.0 | 66.7         | 3                                     | 150.0   | 200.0        | 5                                     | 250.0 | 333.3        | 3                               | 50.0         | 66.7 |

| 0001_001               | 50.0 | 66.7         | 3                                     | 150.0   | 200.0        | 6                                     | 300.0 | 400.0        | 3                               | 50.0         | 66.7 |

| 0001_010               | 50.0 | 66.7         | 3                                     | 150.0   | 200.0        | 7                                     | 350.0 | 466.6        | 3                               | 50.0         | 66.7 |

| 0001_011               | 50.0 | 66.7         | 3                                     | 150.0   | 200.0        | 8                                     | 400.0 | 533.3        | 3                               | 50.0         | 66.7 |

|                        |      |              |                                       | I       |              |                                       |       | I            |                                 |              |      |

| 0010_000               | 50.0 | 66.7         | 4                                     | 200.0   | 266.6        | 5                                     | 250.0 | 333.3        | 4                               | 50.0         | 66.7 |

| 0010_001               | 50.0 | 66.7         | 4                                     | 200.0   | 266.6        | 6                                     | 300.0 | 400.0        | 4                               | 50.0         | 66.7 |

| 0010_010               | 50.0 | 66.7         | 4                                     | 200.0   | 266.6        | 7                                     | 350.0 | 466.6        | 4                               | 50.0         | 66.7 |

| 0010_011               | 50.0 | 66.7         | 4                                     | 200.0   | 266.6        | 8                                     | 400.0 | 533.3        | 4                               | 50.0         | 66.7 |

|                        |      |              |                                       | I       |              |                                       |       | I            |                                 |              |      |

| 0010_100               | 75.0 | 100.0        | 4                                     | 300.0   | 400.0        | 5                                     | 375.0 | 500.0        | 6                               | 50.0         | 66.7 |

| 0010_101               | 75.0 | 100.0        | 4                                     | 300.0   | 400.0        | 5.5                                   | 412.5 | 549.9        | 6                               | 50.0         | 66.7 |

| 0010_110               | 75.0 | 100.0        | 4                                     | 300.0   | 400.0        | 6                                     | 450.0 | 599.9        | 6                               | 50.0         | 66.7 |

|                        |      | 1            |                                       |         | 1            | ı                                     |       |              |                                 |              |      |

| 0011_000               | 50.0 | 66.7         | 5                                     | 250.0   | 333.3        | 5                                     | 250.0 | 333.3        | 5                               | 50.0         | 66.7 |

| 0011_001               | 50.0 | 66.7         | 5                                     | 250.0   | 333.3        | 6                                     | 300.0 | 400.0        | 5                               | 50.0         | 66.7 |

| 0011_010               | 50.0 | 66.7         | 5                                     | 250.0   | 333.3        | 7                                     | 350.0 | 466.6        | 5                               | 50.0         | 66.7 |

| 0011_011               | 50.0 | 66.7         | 5                                     | 250.0   | 333.3        | 8                                     | 400.0 | 533.3        | 5                               | 50.0         | 66.7 |

|                        |      |              |                                       |         |              |                                       |       |              |                                 |              |      |

| 0100_000               |      |              |                                       |         |              | Reserved                              |       |              |                                 |              |      |

MPC8272 PowerQUICC II Family Hardware Specifications, Rev. 3

Table 17. Clock Configurations for PCI Host Mode (PCI\_MODCK=0)<sup>1,2</sup> (continued)

| Mode <sup>3</sup>      |      | Clock<br>Hz) | CPM<br>Multiplication |          | Clock<br>Hz) | CPU<br>Multiplication |       | Clock<br>Hz) | PCI<br>Division     |          | Clock<br>Hz) |

|------------------------|------|--------------|-----------------------|----------|--------------|-----------------------|-------|--------------|---------------------|----------|--------------|

| MODCK_H-<br>MODCK[1-3] | Low  | High         | Factor <sup>4</sup>   | Low      | High         | Factor <sup>5</sup>   | Low   | High         | Factor <sup>6</sup> | Low      | High         |

| 0100_001               | 50.0 | 66.7         | 6                     | 300.0    | 400.0        | 6                     | 300.0 | 400.0        | 6                   | 50.0     | 66.7         |

| 0100_010               | 50.0 | 66.7         | 6                     | 300.0    | 400.0        | 7                     | 350.0 | 466.6        | 6                   | 50.0     | 66.7         |

| 0100_011               | 50.0 | 66.7         | 6                     | 300.0    | 400.0        | 8                     | 400.0 | 533.3        | 6                   | 50.0     | 66.7         |

|                        |      |              |                       |          |              |                       |       |              |                     |          |              |

| 0101_000               | 60.0 | 66.7         | 2                     | 120.0    | 133.3        | 2.5                   | 150.0 | 166.7        | 2                   | 60.0     | 66.7         |

| 0101_001               | 50.0 | 66.7         | 2                     | 100.0    | 133.3        | 3                     | 150.0 | 200.0        | 2                   | 50.0     | 66.7         |

| 0101_010               | 50.0 | 66.7         | 2                     | 100.0    | 133.3        | 3.5                   | 175.0 | 233.3        | 2                   | 50.0     | 66.7         |

| 0101_011               | 50.0 | 66.7         | 2                     | 100.0    | 133.3        | 4                     | 200.0 | 266.6        | 2                   | 50.0     | 66.7         |

| 0101_100               | 50.0 | 66.7         | 2                     | 100.0    | 133.3        | 4.5                   | 225.0 | 300.0        | 2                   | 50.0     | 66.7         |

|                        |      |              |                       | I        | I            |                       | I     |              |                     | I        |              |

| 0101_101               | 83.3 | 111.1        | 3                     | 250.0    | 333.3        | 3.5                   | 291.7 | 388.9        | 5                   | 50.0     | 66.7         |

| 0101_110               | 83.3 | 111.1        | 3                     | 250.0    | 333.3        | 4                     | 333.3 | 444.4        | 5                   | 50.0     | 66.7         |

| 0101_111               | 83.3 | 111.1        | 3                     | 250.0    | 333.3        | 4.5                   | 375.0 | 500.0        | 5                   | 50.0     | 66.7         |

|                        |      |              |                       |          |              |                       |       |              |                     |          |              |

| 0110_000               | 60.0 | 80.0         | 2.5                   | 150.0    | 200.0        | 2.5                   | 150.0 | 200.0        | 3                   | 50.0     | 66.7         |

| 0110_001               | 60.0 | 80.0         | 2.5                   | 150.0    | 200.0        | 3                     | 180.0 | 240.0        | 3                   | 50.0     | 66.7         |

| 0110_010               | 60.0 | 80.0         | 2.5                   | 150.0    | 200.0        | 3.5                   | 210.0 | 280.0        | 3                   | 50.0     | 66.7         |

| 0110_011               | 60.0 | 80.0         | 2.5                   | 150.0    | 200.0        | 4                     | 240.0 | 320.0        | 3                   | 50.0     | 66.7         |

| 0110_100               | 60.0 | 80.0         | 2.5                   | 150.0    | 200.0        | 4.5                   | 270.0 | 360.0        | 3                   | 50.0     | 66.7         |

| 0110_101               | 60.0 | 80.0         | 2.5                   | 150.0    | 200.0        | 5                     | 300.0 | 400.0        | 3                   | 50.0     | 66.7         |

| 0110_110               | 60.0 | 80.0         | 2.5                   | 150.0    | 200.0        | 6                     | 360.0 | 480.0        | 3                   | 50.0     | 66.7         |

|                        |      | ı            |                       |          |              |                       | 1     |              |                     |          |              |

| 0111_000               |      |              |                       |          |              | Reserved              |       |              |                     |          |              |

| 0111_001               | 50.0 | 66.7         | 3                     | 150.0    | 200.0        | 3                     | 150.0 | 200.0        | 3                   | 50.0     | 66.7         |

| 0111_010               | 50.0 | 66.7         | 3                     | 150.0    | 200.0        | 3.5                   | 175.0 | 233.3        | 3                   | 50.0     | 66.7         |

| 0111_011               | 50.0 | 66.7         | 3                     | 150.0    | 200.0        | 4                     | 200.0 | 266.6        | 3                   | 50.0     | 66.7         |

| 0111_100               | 50.0 | 66.7         | 3                     | 150.0    | 200.0        | 4.5                   | 225.0 | 300.0        | 3                   | 50.0     | 66.7         |

|                        | 1    | 1            | l                     | <u>I</u> | <u>I</u>     | l                     | l     | <u>I</u>     | <u> </u>            | <u>I</u> | <u>I</u>     |

| 1000_000               |      |              |                       |          |              | Reserved              |       |              |                     |          |              |

| 1000_001               | 66.7 | 88.9         | 3                     | 200.0    | 266.6        | 3                     | 200.0 | 266.6        | 4                   | 50.0     | 66.7         |

Table 18. Clock Configurations for PCI Host Mode (PCI\_MODCK=1) $^{1,2}$

| Mode <sup>3</sup>      |          | Clock<br>Hz) | CPM                                   |         | Clock<br>Hz) | CPU                                   |         | Clock<br>Hz) | PCI                             | PCI C<br>(MH |      |

|------------------------|----------|--------------|---------------------------------------|---------|--------------|---------------------------------------|---------|--------------|---------------------------------|--------------|------|

| MODCK_H-<br>MODCK[1-3] | Low      | High         | Multiplication<br>Factor <sup>4</sup> | Low     | High         | Multiplication<br>Factor <sup>5</sup> | Low     | High         | Division<br>Factor <sup>6</sup> | Low          | High |

|                        |          |              | Defa                                  | ult Mod | es (MO       | DCK_H=0000)                           |         |              |                                 |              |      |

| 0000_000               | 60.0     | 100.0        | 2                                     | 120.0   | 200.0        | 2.5                                   | 150.0   | 250.0        | 4                               | 30.0         | 50.0 |

| 0000_001               | 50.0     | 100.0        | 2                                     | 100.0   | 200.0        | 3                                     | 150.0   | 300.0        | 4                               | 25.0         | 50.0 |

| 0000_010               | 60.0     | 120.0        | 2.5                                   | 150.0   | 300.0        | 3                                     | 180.0   | 360.0        | 6                               | 25.0         | 50.0 |

| 0000_011               | 60.0     | 120.0        | 2.5                                   | 150.0   | 300.0        | 3.5                                   | 210.0   | 420.0        | 6                               | 25.0         | 50.0 |

| 0000_100               | 60.0     | 120.0        | 2.5                                   | 150.0   | 300.0        | 4                                     | 240.0   | 480.0        | 6                               | 25.0         | 50.0 |

| 0000_101               | 50.0     | 100.0        | 3                                     | 150.0   | 300.0        | 3                                     | 150.0   | 300.0        | 6                               | 25.0         | 50.0 |

| 0000_110               | 50.0     | 100.0        | 3                                     | 150.0   | 300.0        | 3.5                                   | 175.0   | 350.0        | 6                               | 25.0         | 50.0 |

| 0000_111               | 50.0     | 100.0        | 3                                     | 150.0   | 300.0        | 4                                     | 200.0   | 400.0        | 6                               | 25.0         | 50.0 |

|                        | <u>l</u> | <u>l</u>     | F                                     | ull Cor | nfigurati    | on Modes                              | <b></b> |              |                                 | <u> </u>     | ļ    |

| 0001_000               | 50.0     | 100.0        | 3                                     | 150.0   | 300.0        | 5                                     | 250.0   | 500.0        | 6                               | 25.0         | 50.0 |

| 0001_001               | 50.0     | 100.0        | 3                                     | 150.0   | 300.0        | 6                                     | 300.0   | 600.0        | 6                               | 25.0         | 50.0 |

| 0001_010               | 50.0     | 100.0        | 3                                     | 150.0   | 300.0        | 7                                     | 350.0   | 700.0        | 6                               | 25.0         | 50.0 |

| 0001_011               | 50.0     | 100.0        | 3                                     | 150.0   | 300.0        | 8                                     | 400.0   | 800.0        | 6                               | 25.0         | 50.0 |

|                        |          |              |                                       |         |              |                                       |         |              |                                 |              |      |

| 0010_000               | 50.0     | 100.0        | 4                                     | 200.0   | 400.0        | 5                                     | 250.0   | 500.0        | 8                               | 25.0         | 50.0 |

| 0010_001               | 50.0     | 100.0        | 4                                     | 200.0   | 400.0        | 6                                     | 300.0   | 600.0        | 8                               | 25.0         | 50.0 |

| 0010_010               | 50.0     | 100.0        | 4                                     | 200.0   | 400.0        | 7                                     | 350.0   | 700.0        | 8                               | 25.0         | 50.0 |

| 0010_011               | 50.0     | 100.0        | 4                                     | 200.0   | 400.0        | 8                                     | 400.0   | 800.0        | 8                               | 25.0         | 50.0 |

|                        | 1        | 1            |                                       | Т       | Т            |                                       | Т       | Π            |                                 | Т            | Г    |

| 0010_100               | 37.5     | 75.0         | 4                                     |         | 300.0        | 5                                     |         | 375.0        | 6                               | 25.0         | 50.0 |

| 0010_101               | 37.5     | 75.0         | 4                                     | 150.0   | 300.0        | 5.5                                   | 206.3   | 412.5        | 6                               | 25.0         | 50.0 |

| 0010_110               | 37.5     | 75.0         | 4                                     | 150.0   | 300.0        | 6                                     | 225.0   | 450.0        | 6                               | 25.0         | 50.0 |

| 0011_000               | 30.0     | 50.0         | 5                                     | 150.0   | 250.0        | 5                                     | 150.0   | 250.0        | 5                               | 30.0         | 50.0 |

| 0011_001               | 25.0     | 50.0         | 5                                     | 125.0   | 250.0        | 6                                     |         | 300.0        | 5                               | 25.0         | 50.0 |

| 0011_010               | 25.0     | 50.0         | 5                                     |         | 250.0        | 7                                     |         | 350.0        | 5                               | 25.0         | 50.0 |

| 0011_011               | 25.0     | 50.0         | 5                                     |         | 250.0        | 8                                     |         | 400.0        |                                 | 25.0         | 50.0 |

|                        | 1        | ı            |                                       | ı       | ı            |                                       | ı       | ı            |                                 | ı            |      |

| 0100_000               |          |              |                                       |         |              | Reserved                              |         |              |                                 |              |      |

<sup>6</sup> CPM\_CLK/PCI\_CLK ratio. When PCI\_MODCK = 1, the ratio of CPM\_CLK/PCI\_CLK should be calculated from PCIDF as follows:

PCIDF = 3 > CPM\_CLK/PCI\_CLK = 4

PCIDF = 5 > CPM\_CLK/PCI\_CLK = 6

PCIDF = 7 > CPM\_CLK/PCI\_CLK = 8

PCIDF = 9 > CPM\_CLK/PCI\_CLK = 5

PCIDF = B > CPM\_CLK/PCI\_CLK = 6

# 7.2 PCI Agent Mode

These tables show configurations for PCI agent mode. The frequency values listed are for the purpose of illustration only. Users must select a mode and input bus frequency so that the resulting configuration does not exceed the frequency rating of the user's device. Note that in PCI agent mode the input clock is PCI clock.

Table 19. Clock Configurations for PCI Agent Mode (PCI\_MODCK=0)<sup>1,2</sup>

| Mode <sup>3</sup>      | PCI (                        | Clock<br>Hz) | CPM<br>Multiplication |         | Clock<br>Hz) | CPU<br>Multiplication |                 | Clock<br>Hz) | Bus<br>Division |      | Clock<br>Hz) |  |

|------------------------|------------------------------|--------------|-----------------------|---------|--------------|-----------------------|-----------------|--------------|-----------------|------|--------------|--|

| MODCK_H-<br>MODCK[1-3] | Low                          | High         | Factor <sup>4</sup>   | Low     | High         | Factor <sup>5</sup>   | Low High Factor | Low          | High            |      |              |  |

|                        | Default Modes (MODCK_H=0000) |              |                       |         |              |                       |                 |              |                 |      |              |  |

| 0000_000               | 60.0                         | 66.7         | 2                     | 120.0   | 133.3        | 2.5                   | 150.0           | 166.7        | 2               | 60.0 | 66.7         |  |

| 0000_001               | 50.0                         | 66.7         | 2                     | 100.0   | 133.3        | 3                     | 150.0           | 200.0        | 2               | 50.0 | 66.7         |  |

| 0000_010               | 50.0                         | 66.7         | 3                     | 150.0   | 200.0        | 3                     | 150.0           | 200.0        | 3               | 50.0 | 66.7         |  |

| 0000_011               | 50.0                         | 66.7         | 3                     | 150.0   | 200.0        | 4                     | 200.0           | 266.6        | 3               | 50.0 | 66.7         |  |

| 0000_100               | 50.0                         | 66.7         | 3                     | 150.0   | 200.0        | 3                     | 180.0           | 240.0        | 2.5             | 60.0 | 80.0         |  |

| 0000_101               | 50.0                         | 66.7         | 3                     | 150.0   | 200.0        | 3.5                   | 210.0           | 280.0        | 2.5             | 60.0 | 80.0         |  |

| 0000_110               | 50.0                         | 66.7         | 4                     | 200.0   | 266.6        | 3.5                   | 233.3           | 311.1        | 3               | 66.7 | 88.9         |  |

| 0000_111               | 50.0                         | 66.7         | 4                     | 200.0   | 266.6        | 3                     | 240.0           | 320.0        | 2.5             | 80.0 | 106.7        |  |

|                        |                              |              | F                     | ull Con | figurat      | ion Modes             |                 |              |                 |      |              |  |

| 0001_001               | 60.0                         | 66.7         | 2                     | 120.0   | 133.3        | 5                     | 150.0           | 166.7        | 4               | 30.0 | 33.3         |  |

| 0001_010               | 50.0                         | 66.7         | 2                     | 100.0   | 133.3        | 6                     | 150.0           | 200.0        | 4               | 25.0 | 33.3         |  |

| 0001_011               | 50.0                         | 66.7         | 2                     | 100.0   | 133.3        | 7                     | 175.0           | 233.3        | 4               | 25.0 | 33.3         |  |

| 0001_100               | 50.0                         | 66.7         | 2                     | 100.0   | 133.3        | 8                     | 200.0           | 266.6        | 4               | 25.0 | 33.3         |  |

|                        |                              |              |                       |         |              |                       |                 |              |                 |      |              |  |

| 0010_001               | 50.0                         | 66.7         | 3                     | 150.0   | 200.0        | 3                     | 180.0           | 240.0        | 2.5             | 60.0 | 80.0         |  |

| 0010_010               | 50.0                         | 66.7         | 3                     | 150.0   | 200.0        | 3.5                   | 210.0           | 280.0        | 2.5             | 60.0 | 80.0         |  |

| 0010_011               | 50.0                         | 66.7         | 3                     | 150.0   | 200.0        | 4                     | 240.0           | 320.0        | 2.5             | 60.0 | 80.0         |  |

| 0010_100               | 50.0                         | 66.7         | 3                     | 150.0   | 200.0        | 4.5                   | 270.0           | 360.0        | 2.5             | 60.0 | 80.0         |  |

|                        |                              |              |                       |         |              |                       |                 |              |                 |      |              |  |

MPC8272 PowerQUICC II Family Hardware Specifications, Rev. 3

Table 19. Clock Configurations for PCI Agent Mode (PCI\_MODCK=0)<sup>1,2</sup> (continued)

| Mode <sup>3</sup>      | PCI ( | Clock<br>Hz) | CPM<br>Multiplication |       | Clock<br>Hz) | CPU<br>Multiplication |       |       |        | Bus Clock<br>(MHz) |       |

|------------------------|-------|--------------|-----------------------|-------|--------------|-----------------------|-------|-------|--------|--------------------|-------|

| MODCK_H-<br>MODCK[1-3] | Low   | High         | Factor <sup>4</sup>   | Low   | High         | Factor <sup>5</sup>   | Low   | High  | Factor | Low                | High  |

| 0011_000               |       | Reserved     |                       |       |              |                       |       |       |        |                    |       |

| 0011_001               |       | Reserved     |                       |       |              |                       |       |       |        |                    |       |

| 0011_010               |       |              |                       |       |              | Reserved              |       |       |        |                    |       |

| 0011_011               |       | Reserved     |                       |       |              |                       |       |       |        |                    |       |

| 0011_100               |       |              |                       |       |              | Reserved              |       |       |        |                    |       |

|                        |       |              |                       |       |              |                       |       |       |        |                    |       |

| 0100_000               |       |              |                       |       |              | Reserved              |       |       |        |                    |       |

| 0100_001               | 50.0  | 66.7         | 3                     | 150.0 | 200.0        | 3                     | 150.0 | 200.0 | 3      | 50.0               | 66.7  |

| 0100_010               | 50.0  | 66.7         | 3                     | 150.0 | 200.0        | 3.5                   | 175.0 | 200.0 | 3      | 50.0               | 66.7  |

| 0100_011               | 50.0  | 66.7         | 3                     | 150.0 | 200.0        | 4                     | 200.0 | 266.6 | 3      | 50.0               | 66.7  |

| 0100_100               | 50.0  | 66.7         | 3                     | 150.0 | 200.0        | 4.5                   | 225.0 | 300.0 | 3      | 50.0               | 66.7  |

|                        | l.    | •            |                       | l.    | •            |                       | •     | l .   |        | l.                 | l.    |

| 0101_000               | 50.0  | 66.7         | 5                     | 250.0 | 333.3        | 2.5                   | 250.0 | 333.3 | 2.5    | 100.0              | 133.3 |

| 0101_001               | 50.0  | 66.7         | 5                     | 250.0 | 333.3        | 3                     | 300.0 | 400.0 | 2.5    | 100.0              | 133.3 |

| 0101_010               | 50.0  | 66.7         | 5                     | 250.0 | 333.3        | 3.5                   | 350.0 | 466.6 | 2.5    | 100.0              | 133.3 |

| 0101_011               | 50.0  | 66.7         | 5                     | 250.0 | 333.3        | 4                     | 400.0 | 533.3 | 2.5    | 100.0              | 133.3 |

| 0101_100               | 50.0  | 66.7         | 5                     | 250.0 | 333.3        | 4.5                   | 450.0 | 599.9 | 2.5    | 100.0              | 133.3 |

| 0101_101               | 50.0  | 66.7         | 5                     | 250.0 | 333.3        | 5                     | 500.0 | 666.6 | 2.5    | 100.0              | 133.3 |

| 0101_110               | 50.0  | 66.7         | 5                     | 250.0 | 333.3        | 5.5                   | 550.0 | 733.3 | 2.5    | 100.0              | 133.3 |

|                        |       |              |                       |       |              |                       |       |       |        |                    |       |

| 0110_000               |       | Reserved     |                       |       |              |                       |       |       |        |                    |       |

| 0110_001               | 50.0  | 66.7         | 4                     | 200.0 | 266.6        | 3                     | 200.0 | 266.6 | 3      | 66.7               | 88.9  |

| 0110_010               | 50.0  | 66.7         | 4                     | 200.0 | 266.6        | 3.5                   | 233.3 | 311.1 | 3      | 66.7               | 88.9  |

| 0110_011               | 50.0  | 66.7         | 4                     | 200.0 | 266.6        | 4                     | 266.7 | 355.5 | 3      | 66.7               | 88.9  |

| 0110_100               | 50.0  | 66.7         | 4                     | 200.0 | 266.6        | 4.5                   | 300.0 | 400.0 | 3      | 66.7               | 88.9  |

|                        |       |              |                       |       |              |                       |       |       |        |                    |       |

| 0111_000               | 50.0  | 66.7         | 3                     | 150.0 | 200.0        | 2                     | 150.0 | 200.0 | 2      | 75.0               | 100.0 |

| 0111_001               | 50.0  | 66.7         | 3                     | 150.0 | 200.0        | 2.5                   | 187.5 | 250.0 | 2      | 75.0               | 100.0 |

| 0111_010               | 50.0  | 66.7         | 3                     | 150.0 | 200.0        | 3                     | 225.0 | 300.0 | 2      | 75.0               | 100.0 |

| 0111_011               | 50.0  | 66.7         | 3                     | 150.0 | 200.0        | 3.5                   | 262.5 | 350.0 | 2      | 75.0               | 100.0 |

Table 20. Clock Configurations for PCI Agent Mode (PCI\_MODCK=1)<sup>1,2</sup>

| Mode <sup>3</sup>      | PCI Clock<br>(MHz) | Mode | CPM                                   |         | Clock<br>Hz) | CPU<br>Multiplication |       | Clock<br>Hz) | Bus                |      | Clock<br>Hz) |

|------------------------|--------------------|------|---------------------------------------|---------|--------------|-----------------------|-------|--------------|--------------------|------|--------------|

| MODCK_H-<br>MODCK[1-3] | Low                | High | Multiplication<br>Factor <sup>4</sup> | Low     | High         | Factor <sup>5</sup>   | Low   | High         | Division<br>Factor | Low  | High         |

|                        |                    |      | Defau                                 | ılt Mod | es (MO       | DCK_H=0000)           |       |              |                    |      |              |

| 0000_000               | 30.0               | 50.0 | 4                                     | 120.0   | 200.0        | 2.5                   | 150.0 | 250.0        | 2                  | 60.0 | 100.0        |

| 0000_001               | 25.0               | 50.0 | 4                                     | 100.0   | 200.0        | 3                     | 150.0 | 300.0        | 2                  | 50.0 | 100.0        |

| 0000_010               | 25.0               | 50.0 | 6                                     | 150.0   | 300.0        | 3                     | 150.0 | 300.0        | 3                  | 50.0 | 100.0        |

| 0000_011               | 25.0               | 50.0 | 6                                     | 150.0   | 300.0        | 4                     | 200.0 | 400.0        | 3                  | 50.0 | 100.0        |

| 0000_100               | 25.0               | 50.0 | 6                                     | 150.0   | 300.0        | 3                     | 180.0 | 360.0        | 2.5                | 60.0 | 120.0        |

| 0000_101               | 25.0               | 50.0 | 6                                     | 150.0   | 300.0        | 3.5                   | 210.0 | 420.0        | 2.5                | 60.0 | 120.0        |

| 0000_110               | 25.0               | 50.0 | 8                                     | 200.0   | 400.0        | 3.5                   | 233.3 | 466.7        | 3                  | 66.7 | 133.3        |

| 0000_111               | 25.0               | 50.0 | 8                                     | 200.0   | 400.0        | 3                     | 240.0 | 480.0        | 2.5                | 80.0 | 160.0        |

|                        | I                  |      | F                                     | ull Cor | nfigurati    | on Modes              | I     | I            |                    | I    |              |

| 0001_001               | 30.0               | 50.0 | 4                                     | 120.0   | 200.0        | 5                     | 150.0 | 250.0        | 4                  | 30.0 | 50.0         |

| 0001_010               | 25.0               | 50.0 | 4                                     | 100.0   | 200.0        | 6                     | 150.0 | 300.0        | 4                  | 25.0 | 50.0         |

| 0001_011               | 25.0               | 50.0 | 4                                     | 100.0   | 200.0        | 7                     | 175.0 | 350.0        | 4                  | 25.0 | 50.0         |

| 0001_100               | 25.0               | 50.0 | 4                                     | 100.0   | 200.0        | 8                     | 200.0 | 400.0        | 4                  | 25.0 | 50.0         |

|                        | I                  |      |                                       |         |              |                       |       | I            |                    | I    |              |

| 0010_001               | 25.0               | 50.0 | 6                                     | 150.0   | 300.0        | 3                     | 180.0 | 360.0        | 2.5                | 60.0 | 120.0        |

| 0010_010               | 25.0               | 50.0 | 6                                     | 150.0   | 300.0        | 3.5                   | 210.0 | 420.0        | 2.5                | 60.0 | 120.0        |

| 0010_011               | 25.0               | 50.0 | 6                                     | 150.0   | 300.0        | 4                     | 240.0 | 480.0        | 2.5                | 60.0 | 120.0        |

| 0010_100               | 25.0               | 50.0 | 6                                     | 150.0   | 300.0        | 4.5                   | 270.0 | 540.0        | 2.5                | 60.0 | 120.0        |

|                        | •                  |      |                                       | •       | •            |                       | •     |              |                    |      |              |

| 0011_000               | Reserved           |      |                                       |         |              |                       |       |              |                    |      |              |

| 0011_001               | 37.5               | 50.0 | 4                                     | 150.0   | 200.0        | 3                     | 150.0 | 200.0        | 3                  | 50.0 | 66.7         |

| 0011_010               | 32.1               | 50.0 | 4                                     | 128.6   | 200.0        | 3.5                   | 150.0 | 233.3        | 3                  | 42.9 | 66.7         |

| 0011_011               | 28.1               | 50.0 | 4                                     | 112.5   | 200.0        | 4                     | 150.0 | 266.7        | 3                  | 37.5 | 66.7         |

| 0011_100               | 25.0               | 50.0 | 4                                     | 100.0   | 200.0        | 4.5                   | 150.0 | 300.0        | 3                  | 33.3 | 66.7         |

|                        |                    |      |                                       |         |              |                       |       |              |                    |      |              |

| 0100_000               | Reserved           |      |                                       |         |              |                       |       |              |                    |      |              |

| 0100_001               | 25.0               | 50.0 | 6                                     | 150.0   | 300.0        | 3                     | 150.0 | 300.0        | 3                  | 50.0 | 100.0        |

| 0100_010               | 25.0               | 50.0 | 6                                     | 150.0   | 300.0        | 3.5                   | 175.0 | 350.0        | 3                  | 50.0 | 100.0        |

| 0100_011               | 25.0               | 50.0 | 6                                     | 150.0   | 300.0        | 4                     | 200.0 | 400.0        | 3                  | 50.0 | 100.0        |

MPC8272 PowerQUICC II Family Hardware Specifications, Rev. 3

Table 21. Pinout (continued)

| Pin N                                  |                      |            |  |  |  |  |

|----------------------------------------|----------------------|------------|--|--|--|--|

| MPC8272/MPC8248 and<br>MPC8271/MPC8247 | MPC8272/MPC8271 Only | Ball       |  |  |  |  |

| T:                                     | TS                   |            |  |  |  |  |

| A                                      | A3                   |            |  |  |  |  |

| A                                      | B5                   |            |  |  |  |  |

| A                                      | 2                    | D8         |  |  |  |  |

| A                                      | 3                    | C6         |  |  |  |  |

| A                                      | 4                    | A4         |  |  |  |  |

| A                                      | 5                    | A6         |  |  |  |  |

| A                                      | 6                    | В6         |  |  |  |  |

| A                                      | 7                    | C7         |  |  |  |  |

| A                                      | 8                    | B7         |  |  |  |  |

| A                                      | 9                    | A7         |  |  |  |  |

| A1                                     | 0                    | D9         |  |  |  |  |

| A1                                     | E11                  |            |  |  |  |  |

| A1                                     | C9                   |            |  |  |  |  |

| A1                                     | A13                  |            |  |  |  |  |

| A1                                     | A14                  |            |  |  |  |  |

| A1                                     | A15                  |            |  |  |  |  |

| A1                                     | 6                    | B10        |  |  |  |  |

| A1                                     | 7                    | A10        |  |  |  |  |

| A1                                     | 8                    | B11        |  |  |  |  |

| A1                                     | 9                    | A11        |  |  |  |  |

| A2                                     | 20                   | D12        |  |  |  |  |

| A2                                     | 21                   | A12        |  |  |  |  |

| A2                                     | 22                   | D13        |  |  |  |  |

| A2                                     | 23                   | B13        |  |  |  |  |

| A2                                     | 24                   | C13        |  |  |  |  |

| A2                                     | A25                  |            |  |  |  |  |

| A2                                     | 26                   | B14        |  |  |  |  |

| A2                                     | A27                  |            |  |  |  |  |

|                                        | A28                  |            |  |  |  |  |

| A2                                     |                      | E14<br>A14 |  |  |  |  |

MPC8272 PowerQUICC II Family Hardware Specifications, Rev. 3

### **Pinout**

Table 21. Pinout (continued)

| Pin N                               |                      |      |  |  |  |

|-------------------------------------|----------------------|------|--|--|--|

| MPC8272/MPC8248 and MPC8271/MPC8247 | MPC8272/MPC8271 Only | Ball |  |  |  |

| A3                                  | 30                   | B15  |  |  |  |

| A3                                  | A15                  |      |  |  |  |

| тт                                  | В3                   |      |  |  |  |

| тт                                  | T1                   | E8   |  |  |  |

| тт                                  | -2                   | D7   |  |  |  |

| тт                                  | -3                   | C4   |  |  |  |

| тт                                  | <sup>-</sup> 4       | E7   |  |  |  |

| TB                                  | ST                   | E3   |  |  |  |

| TSI                                 | Z0                   | E4   |  |  |  |

| TSI                                 | Z1                   | E5   |  |  |  |

| TSI                                 | Z2                   | C3   |  |  |  |

| TSI                                 | Z3                   | D5   |  |  |  |

| AAG                                 | AACK                 |      |  |  |  |

| ĀRT                                 | C2                   |      |  |  |  |

| DBG/                                | DBG/IRQ7             |      |  |  |  |

| DBB/I                               | DBB/IRQ3             |      |  |  |  |

| D                                   | D0                   |      |  |  |  |

| D                                   | D1                   |      |  |  |  |

| D                                   | D2                   |      |  |  |  |

| D                                   | D3                   |      |  |  |  |

| D                                   | 4                    | P4   |  |  |  |

| D                                   | 5                    | M4   |  |  |  |

| D                                   | 6                    | J4   |  |  |  |

| D                                   | 7                    | G1   |  |  |  |

| D                                   | 8                    | W6   |  |  |  |

| D                                   | Y3                   |      |  |  |  |

| D1                                  | 0                    | V1   |  |  |  |

| D1                                  | 1                    | N6   |  |  |  |

| D1                                  | 2                    | P3   |  |  |  |

| D1                                  | 3                    | M2   |  |  |  |

| D1                                  | 4                    | J5   |  |  |  |

MPC8272 PowerQUICC II Family Hardware Specifications, Rev. 3

### **Pinout**

Table 21. Pinout (continued)

| Pin Name                                         |      |

|--------------------------------------------------|------|

| MPC8272/MPC8248 and MPC8271/MPC8247 MPC8271 Only | Ball |

| D46                                              | H4   |

| D47                                              | F2   |

| D48                                              | AB1  |

| D49                                              | U4   |

| D50                                              | U1   |

| D51                                              | R3   |

| D52                                              | N3   |

| D53                                              | K2   |

| D54                                              | H5   |

| D55                                              | F4   |

| D56                                              | AA3  |

| D57                                              | U5   |

| D58                                              | U2   |

| D59                                              | P5   |

| D60                                              | МЗ   |

| D61                                              | K4   |

| D62                                              | НЗ   |

| D63                                              | E1   |

| IRQ3/CKSTP_OUT/EXT_BR3                           | B16  |

| IRQ4/CORE_SRESET/EXT_BG3                         | C15  |

| IRQ5/TBEN/EXT_DBG3/CINT                          | Y4   |

| PSDVAL                                           | C19  |

| TA                                               | AA4  |

| TEA                                              | AB6  |

| GBL/IRQ1                                         | D15  |

| CI/BADDR29/IRQ2                                  | D16  |

| WT/BADDR30/IRQ3                                  | C16  |

| BADDR31/ <del>IRQ5/CINT</del>                    | E17  |

| CPU_BR/INT_OUT                                   | B20  |

| CS0                                              | AE6  |

| CS1                                              | AD7  |

MPC8272 PowerQUICC II Family Hardware Specifications, Rev. 3

# Table 21. Pinout (continued)

| Pin N                                  | Pin Name             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|----------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MPC8272/MPC8248 and<br>MPC8271/MPC8247 | MPC8272/MPC8271 Only | Ball                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| CLK                                    | IN2                  | C21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| No cor                                 | nect <sup>4</sup>    | D19 <sup>4</sup> , J3 <sup>4</sup> , AD24 <sup>5</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |