#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

E·XF

| Product Status                  | Active                                                     |

|---------------------------------|------------------------------------------------------------|

| Core Processor                  | PowerPC G2_LE                                              |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                             |

| Speed                           | 400MHz                                                     |

| Co-Processors/DSP               | Communications; RISC CPM, Security; SEC                    |

| RAM Controllers                 | DRAM, SDRAM                                                |

| Graphics Acceleration           | No                                                         |

| Display & Interface Controllers | -                                                          |

| Ethernet                        | 10/100Mbps (2)                                             |

| SATA                            | -                                                          |

| USB                             | USB 2.0 (1)                                                |

| Voltage - I/O                   | 3.3V                                                       |

| Operating Temperature           | 0°C ~ 105°C (TA)                                           |

| Security Features               | Cryptography, Random Number Generator                      |

| Package / Case                  | 516-BBGA                                                   |

| Supplier Device Package         | 516-FPBGA (27x27)                                          |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8272vrtiea |

|                                 |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

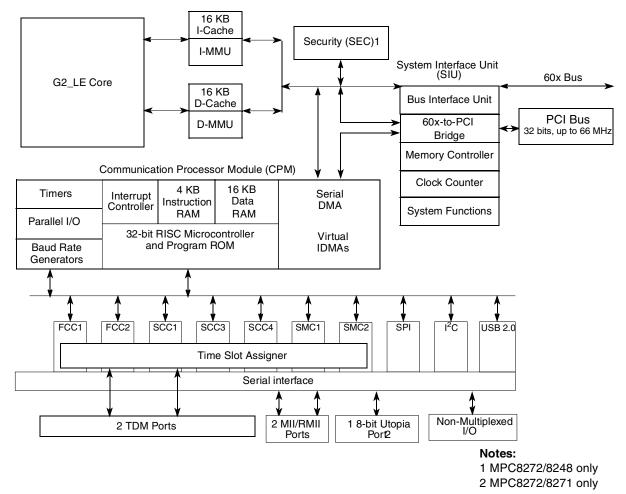

This figure shows the block diagram of the SoC.

## 1.1 Features

The major features of the SoC are as follows:

- Dual-issue integer (G2\_LE) core

- A core version of the MPC603e microprocessor

- System core microprocessor supporting frequencies of 266–400 MHz

- Separate 16 KB data and instruction caches:

- Four-way set associative

- Physically addressed

- LRU replacement algorithm

- Power Architecture®-compliant memory management unit (MMU)

- Common on-chip processor (COP) test interface

- Supports bus snooping for cache coherency

#### **DC Electrical Characteristics**

<sup>5</sup> MPC8272 and MPC8271 only.

Table 6.

| Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Symbol           | Min | Мах   | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|-------|------|

| Input high voltage—all inputs except TCK, TRST and PORESET <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V <sub>IH</sub>  | 2.0 | 3.465 | V    |

| Input low voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | V <sub>IL</sub>  | GND | 0.8   | V    |

| CLKIN input high voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | V <sub>IHC</sub> | 2.4 | 3.465 | V    |

| CLKIN input low voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V <sub>ILC</sub> | GND | 0.4   | V    |

| Input leakage current, V <sub>IN</sub> = VDDH <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I <sub>IN</sub>  |     | 10    | μA   |

| Hi-Z (off state) leakage current, V <sub>IN</sub> = VDDH <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I <sub>OZ</sub>  |     | 10    | μA   |

| Signal low input current, $V_{IL} = 0.8 V^3$                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ١L               | _   | 1     | μA   |

| Signal high input current, V <sub>IH</sub> = 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | I <sub>H</sub>   | _   | 1     | μA   |

| Output high voltage, $I_{OH} = -2 \text{ mA}$<br>except UTOPIA mode, and open drain pins<br>In UTOPIA mode <sup>4</sup> (UTOPIA pins only): $I_{OH} = -8.0 \text{mA}$                                                                                                                                                                                                                                                                                                                                                      | V <sub>OH</sub>  | 2.4 | _     | V    |

| In UTOPIA mode <sup>4</sup> (UTOPIA pins only): I <sub>OL</sub> = 8.0mA                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V <sub>OL</sub>  | _   | 0.5   | V    |

| IoL = 6.0mA         BR         BG         ABB/IRQ2         TS         A[0-31]         TTI[0-4]         TBST         TSIZE[0-3]         AACK         ARTRY         DBG         DBB/IRQ3         D[0-63]         //EXT_BR3         //EXT_BR3         //EXT_BG3         /TEN/EXT_DBG3/CINT         PSDVAL         TA         TEA         GBL/IRQ1         CI/BADDR29/IRQ2         WT/BADDR30/IRQ3         BADDR31/IRQ5/CINT         CPU_BR         IRQ0/NMI_OUT         /PCL_RST         HRESET         SRESET         REQONF | V <sub>OL</sub>  |     | 0.4   | V    |

**Thermal Characteristics**

## 4.2 Estimation with Junction-to-Case Thermal Resistance

Historically, the thermal resistance has frequently been expressed as the sum of a junction-to-case thermal resistance and a case-to-ambient thermal resistance:

$$R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$$

where:

$R_{\theta JA}$  = junction-to-ambient thermal resistance (°C/W)

$R_{\theta JC}$  = junction-to-case thermal resistance (°C/W)

$R_{\theta CA}$  = case-to-ambient thermal resistance (°C/W)

$R_{\theta JC}$  is device related and cannot be influenced by the user. The user adjusts the thermal environment to affect the case-to-ambient thermal resistance,  $R_{\theta CA}$ . For instance, the user can change the air flow around the device, add a heat sink, change the mounting arrangement on the printed circuit board, or change the thermal dissipation on the printed circuit board surrounding the device. This thermal model is most useful for ceramic packages with heat sinks where some 90% of the heat flows through the case and the heat sink to the ambient environment. For most packages, a better model is required.

## 4.3 Estimation with Junction-to-Board Thermal Resistance

A simple package thermal model which has demonstrated reasonable accuracy (about 20%) is a two-resistor model consisting of a junction-to-board and a junction-to-case thermal resistance. The junction-to-case thermal resistance covers the situation where a heat sink is used or where a substantial amount of heat is dissipated from the top of the package. The junction-to-board thermal resistance describes the thermal performance when most of the heat is conducted to the printed circuit board. It has been observed that the thermal performance of most plastic packages, especially PBGA packages, is strongly dependent on the board temperature.

If the board temperature is known, an estimate of the junction temperature in the environment can be made using the following equation:

$$T_{J} = T_{B} + (R_{\theta JB} \times P_{D})$$

where:

$R_{\theta JB}$  = junction-to-board thermal resistance (°C/W)  $T_B$  = board temperature (°C)  $P_D$  = power dissipation in package

If the board temperature is known and the heat loss from the package case to the air can be ignored, acceptable predictions of junction temperature can be made. For this method to work, the board and board mounting must be similar to the test board used to determine the junction-to-board thermal resistance, namely a 2s2p (board with a power and a ground plane) and by attaching the thermal balls to the ground plane.

Thermal Characteristics

# 4.4 Estimation Using Simulation

When the board temperature is not known, a thermal simulation of the application is needed. The simple two-resistor model can be used with the thermal simulation of the application, or a more accurate and complex model of the package can be used in the thermal simulation.

# 4.5 **Experimental Determination**

To determine the junction temperature of the device in the application after prototypes are available, the thermal characterization parameter ( $\Psi_{JT}$ ) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using the following equation:

$$T_J = T_T + (\Psi_{JT} \times P_D)$$

where:

$\Psi_{JT}$  = thermal characterization parameter

$T_T$  = thermocouple temperature on top of package

$P_D$  = power dissipation in package

The thermal characterization parameter is measured per JEDEC JESD51-2 specification using a 40-gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the case to avoid measurement errors caused by cooling effects of the thermocouple wire.

## 4.6 Layout Practices

Each VDD and VDDH pin should be provided with a low-impedance path to the board's power supplies. Each ground pin should likewise be provided with a low-impedance path to ground. The power supply pins drive distinct groups of logic on chip. The VDD and VDDH power supplies should be bypassed to ground using bypass capacitors located as close as possible to the four sides of the package. For filtering high frequency noise, a capacitor of 0.1uF on each VDD and VDDH pin is recommended. Further, for medium frequency noise, a total of 2 capacitors of 47uF for VDD and 2 capacitors of 47uF for VDDH are also recommended. The capacitor leads and associated printed circuit traces connecting to chip VDD, VDDH and ground should be kept to less than half an inch per capacitor lead. Boards should employ separate inner layers for power and GND planes.

All output pins on the SoC have fast rise and fall times. Printed circuit (PC) trace interconnection length should be minimized to minimize overdamped conditions and reflections caused by these fast output switching times. This recommendation particularly applies to the address and data buses. Maximum PC trace lengths of six inches are recommended. Capacitance calculations should consider all device loads as well as parasitic capacitances due to the PC traces. Attention to proper PCB layout and bypassing becomes especially critical in systems with higher capacitive loads because these loads create higher transient currents in the VDD and GND circuits. Pull up all unused inputs or signals that will be inputs during reset. Special care should be taken to minimize the noise levels on the PLL supply pins.

**AC Electrical Characteristics**

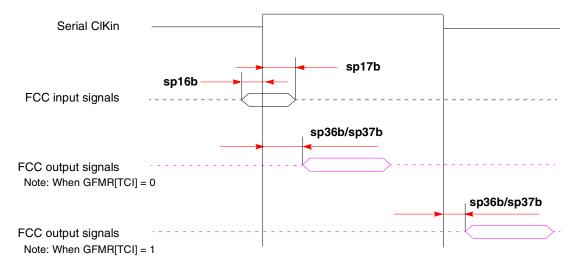

This figure shows the FCC external clock.

Figure 4. FCC External Clock Diagram

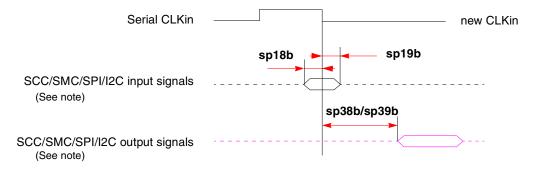

This figure shows the SCC/SMC/SPI/I<sup>2</sup>C external clock.

Note: There are four possible timing conditions for SPI:

- 1. Input sampled on the rising edge and output driven on the rising edge.

- 2. Input sampled on the rising edge and output driven on the falling edge.

- 3. Input sampled on the falling edge and output driven on the falling edge (shown).

- 4. Input sampled on the falling edge and output driven on the rising edge.

**Note:** There are two possible timing conditions for SCC/SMC/I<sup>2</sup>C:

- 1. Input sampled on the falling edge and output driven on the falling edge (shown).

- 2. Input sampled on the falling edge and output driven on the rising edge.

#### Figure 5. SCC/SMC/SPI/I<sup>2</sup>C External Clock Diagram

## **NOTE: Conditions**

The following conditions must be met in order to operate the MPC8272 family devices with 133 MHz bus: single PowerQUICC II Bus mode must be used (no external master, BCR[EBM] = 0); data bus must be in Pipeline mode (BRx[DR] = 1); internal arbiter and memory controller must be used. For expected load of above 40 pF, it is recommended that data and address buses be configured to low (25  $\Omega$ ) impedance (SIUMCR[HLBE0] = 1, SIUMCR[HLBE1] = 1).

| Spec N | umber          |                                                    | Value (ns) |           |            |            |           |           |            |            |  |  |

|--------|----------------|----------------------------------------------------|------------|-----------|------------|------------|-----------|-----------|------------|------------|--|--|

|        | Characteristic |                                                    | Se         | tup       |            | Hold       |           |           |            |            |  |  |

| Setup  | Hold           |                                                    | 66<br>MHz  | 83<br>MHz | 100<br>MHz | 133<br>MHz | 66<br>MHz | 83<br>MHz | 100<br>MHz | 133<br>MHz |  |  |

| sp11   | sp10           | AACK/TA/TS/DBG/BG/BR/ARTRY/TEA                     | 6          | 5         | 3.5        | N/A        | 0.5       | 0.5       | 0.5        | N/A        |  |  |

| sp12   | sp10           | Data bus in normal mode                            | 5          | 4         | 3.5        | N/A        | 0.5       | 0.5       | 0.5        | N/A        |  |  |

| sp13   | sp10           | Data bus in pipeline mode (without ECC and PARITY) | N/A        | 4         | 2.5        | 1.5        | N/A       | 0.5       | 0.5        | 0.5        |  |  |

| sp15   | sp10           | All other pins                                     | 5          | 4         | 3.5        | N/A        | 0.5       | 0.5       | 0.5        | N/A        |  |  |

## Table 12. AC Characteristics for SIU Inputs<sup>1</sup>

<sup>1</sup> Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of CLKIN. Timings are measured at the pin.

This table lists SIU output characteristics.

Table 13. AC Characteristics for SIU Outputs<sup>1</sup>

| Spec Number |      |                               | Value (ns) |           |            |                  |               |           |            |                |  |  |

|-------------|------|-------------------------------|------------|-----------|------------|------------------|---------------|-----------|------------|----------------|--|--|

|             |      | Characteristic                | ſ          | Maximu    | m Delay    | /                | Minimum Delay |           |            |                |  |  |

| Мах         | Min  |                               |            | 83<br>MHz | 100<br>MHz | 133<br>MHz       | 66<br>MHz     | 83<br>MHz | 100<br>MHz | 133<br>MHz     |  |  |

| sp31        | sp30 | PSDVAL/TEA/TA                 | 7          | 6         | 5.5        | N/A              | 1             | 1         | 1          | N/A            |  |  |

| sp32        | sp30 | ADD/ADD_atr./BADDR/CI/GBL/WT  | 8          | 6.5       | 5.5        | 4.5 <sup>2</sup> | 1             | 1         | 1          | 1 <sup>2</sup> |  |  |

| sp33        | sp30 | Data bus <sup>3</sup>         | 6.5        | 6.5       | 5.5        | 4.5              | 0.8           | 0.8       | 0.8        | 1              |  |  |

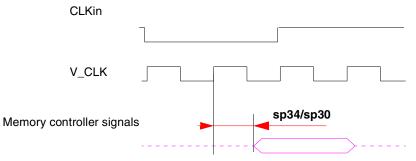

| sp34        | sp30 | Memory controller signals/ALE | 6          | 5.5       | 5.5        | 4.5              | 1             | 1         | 1          | 1              |  |  |

| sp35        | sp30 | All other signals             | 6          | 5.5       | 5.5        | N/A              | 1             | 1         | 1          | N/A            |  |  |

<sup>1</sup> Output specifications are measured from the 50% level of the rising edge of CLKIN to the 50% level of the signal. Timings are measured at the pin.

<sup>2</sup> Value is for ADD only; other sp32/sp30 signals are not applicable.

<sup>3</sup> To achieve 1 ns of hold time at 66.67/83.33/100 MHZ, a minimum loading of 20 pF is required.

**AC Electrical Characteristics**

This figure shows signal behavior in MEMC mode.

Figure 10. MEMC Mode Diagram

NOTE

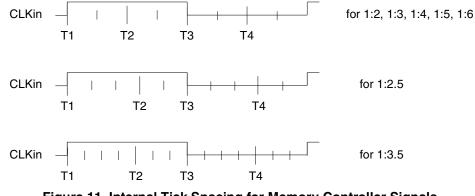

Generally, all SoC bus and system output signals are driven from the rising edge of the input clock (CLKin). Memory controller signals, however, trigger on four points within a CLKin cycle. Each cycle is divided by four internal ticks: T1, T2, T3, and T4. T1 always occurs at the rising edge, and T3 at the falling edge, of CLKin. However, the spacing of T2 and T4 depends on the PLL clock ratio selected, as shown in Table 14.

| Table 14. | . Tick Spacing for Memory Controller Signals |

|-----------|----------------------------------------------|

|-----------|----------------------------------------------|

| PLL Clock Ratio         | Tick Spacing (T1 Occurs at the Rising Edge of CLKin) |           |             |  |  |  |  |  |

|-------------------------|------------------------------------------------------|-----------|-------------|--|--|--|--|--|

|                         | T2                                                   | тз        | Т4          |  |  |  |  |  |

| 1:2, 1:3, 1:4, 1:5, 1:6 | 1/4 CLKin                                            | 1/2 CLKin | 3/4 CLKin   |  |  |  |  |  |

| 1:2.5                   | 3/10 CLKin                                           | 1/2 CLKin | 8/10 CLKin  |  |  |  |  |  |

| 1:3.5                   | 4/14 CLKin                                           | 1/2 CLKin | 11/14 CLKin |  |  |  |  |  |

This table is a representation of the information in Table 14.

Figure 11. Internal Tick Spacing for Memory Controller Signals

**AC Electrical Characteristics**

## NOTE

The UPM machine outputs change on the internal tick determined by the memory controller programming; the AC specifications are relative to the internal tick. Note that SDRAM and GPCM machine outputs change on CLKin's rising edge.

# 6.3 JTAG Timings

This table lists the JTAG timings.

| Parameter                                                                 | Symbol <sup>2</sup>                        | Min      | Max      | Unit     | Notes      |

|---------------------------------------------------------------------------|--------------------------------------------|----------|----------|----------|------------|

| JTAG external clock frequency of operation                                | f <sub>JTG</sub>                           | 0        | 33.3     | MHz      | —          |

| JTAG external clock cycle time                                            | t <sub>JTG</sub>                           | 30       |          | ns       | —          |

| JTAG external clock pulse width measured at 1.4V                          | t <sub>JTKHKL</sub>                        | 15       |          | ns       | —          |

| JTAG external clock rise and fall times                                   | t <sub>JTGR</sub> and<br>t <sub>JTGF</sub> | 0        | 5        | ns       | 6          |

| TRST assert time                                                          | t <sub>TRST</sub>                          | 25       | _        | ns       | 3,6        |

| Input setup times<br>Boundary-scan data<br>TMS, TDI                       | t <sub>JTDVKH</sub><br>t <sub>JTIVKH</sub> | 4<br>4   | _        | ns<br>ns | 4,7<br>4,7 |

| Input hold times<br>Boundary-scan data<br>TMS, TDI                        | t <sub>JTDXKH</sub><br>t <sub>JTIXKH</sub> | 10<br>10 |          | ns<br>ns | 4,7<br>4,7 |

| Output valid times<br>Boundary-scan data<br>TDO                           | t <sub>JTKLDV</sub><br>t <sub>JTKLOV</sub> |          | 10<br>10 | ns<br>ns | 5 7<br>5 7 |

| Output hold times<br>Boundary-scan data<br>TDO                            | t <sub>JTKLDX</sub><br>t <sub>JTKLOX</sub> | 1<br>1   |          | ns<br>ns | 5,7<br>5,7 |

| JTAG external clock to output high impedance<br>Boundary-scan data<br>TDO | t <sub>JTKLDZ</sub><br>t <sub>JTKLOZ</sub> | 1        | 10<br>10 | ns<br>ns | 5,6<br>5,6 |

Table 15. JTAG Timings<sup>1</sup>

<sup>I</sup> All outputs are measured from the midpoint voltage of the falling/rising edge of t<sub>TCLK</sub> to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50-Ω load. Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

<sup>2</sup> The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t(<sub>(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub></sub>

- <sup>3</sup> TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

- <sup>4</sup> Non-JTAG signal input timing with respect to t<sub>TCLK</sub>.

- <sup>5</sup> Non-JTAG signal output timing with respect to t<sub>TCLK</sub>.

- <sup>6</sup> Guaranteed by design.

- <sup>7</sup> Guaranteed by design and device characterization.

| Mode <sup>3</sup> Bus Clock<br>(MHz) |       | CPM Clock<br>CPM (MHz) |                       |       | CPU   |                | Clock | PCI   | PCI Clock<br>(MHz)  |      |      |  |

|--------------------------------------|-------|------------------------|-----------------------|-------|-------|----------------|-------|-------|---------------------|------|------|--|

|                                      |       | 12)                    | CPM<br>Multiplication | (IVI) | nz)   | Multiplication | (11)  | Hz)   | Z) PCI<br>Division  |      |      |  |

| MODCK_H-<br>MODCK[1-3]               | Low   | High                   | Factor <sup>4</sup>   | Low   | High  |                | Low   | High  | Factor <sup>6</sup> | Low  | High |  |

| 1000_010                             | 66.7  | 133.3                  | 3                     | 200.0 | 400.0 | 3.5            | 233.3 | 466.7 | 8                   | 25.0 | 50.0 |  |

| 1000_011                             | 66.7  | 133.3                  | 3                     | 200.0 | 400.0 | 4              | 266.7 | 533.3 | 8                   | 25.0 | 50.0 |  |

| 1000_100                             | 66.7  | 133.3                  | 3                     | 200.0 | 400.0 | 4.5            | 300.0 | 600.0 | 8                   | 25.0 | 50.0 |  |

| 1000_101                             | 66.7  | 133.3                  | 3                     | 200.0 | 400.0 | 6              | 400.0 | 800.0 | 8                   | 25.0 | 50.0 |  |

| 1000_110                             | 66.7  | 133.3                  | 3                     | 200.0 | 400.0 | 6.5            | 433.3 | 866.7 | 8                   | 25.0 | 50.0 |  |

|                                      |       |                        |                       |       | •     |                |       | •     |                     | •    | •    |  |

| 1001_000                             |       |                        |                       |       |       | Reserved       |       |       |                     |      |      |  |

| 1001_001                             |       |                        |                       |       |       | Reserved       |       |       |                     |      |      |  |

| 1001_010                             | 57.1  | 114.3                  | 3.5                   | 200.0 | 400.0 | 3.5            | 200.0 | 400.0 | 8                   | 25.0 | 50.0 |  |

| 1001_011                             | 57.1  | 114.3                  | 3.5                   | 200.0 | 400.0 | 4              | 228.6 | 457.1 | 8                   | 25.0 | 50.0 |  |

| 1001_100                             | 57.1  | 114.3                  | 3.5                   | 200.0 | 400.0 | 4.5            | 257.1 | 514.3 | 8                   | 25.0 | 50.0 |  |

| 1001_101                             | 42.9  | 85.7                   | 3.5                   | 150.0 | 300.0 | 5              | 214.3 | 428.6 | 6                   | 25.0 | 50.0 |  |

| 1001_110                             | 42.9  | 85.7                   | 3.5                   | 150.0 | 300.0 | 5.5            | 235.7 | 471.4 | 6                   | 25.0 | 50.0 |  |

| 1001_111                             | 42.9  | 85.7                   | 3.5                   | 150.0 | 300.0 | 6              | 257.1 | 514.3 | 6                   | 25.0 | 50.0 |  |

|                                      |       |                        |                       |       |       |                |       |       |                     |      | •    |  |

| 1010_000                             | 75.0  | 150.0                  | 2                     | 150.0 | 300.0 | 2              | 150.0 | 300.0 | 6                   | 25.0 | 50.0 |  |

| 1010_001                             | 75.0  | 150.0                  | 2                     | 150.0 | 300.0 | 2.5            | 187.5 | 375.0 | 6                   | 25.0 | 50.0 |  |

| 1010_010                             | 75.0  | 150.0                  | 2                     | 150.0 | 300.0 | 3              | 225.0 | 450.0 | 6                   | 25.0 | 50.0 |  |

| 1010_011                             | 75.0  | 150.0                  | 2                     | 150.0 | 300.0 | 3.5            | 262.5 | 525.0 | 6                   | 25.0 | 50.0 |  |

| 1010_100                             | 75.0  | 150.0                  | 2                     | 150.0 | 300.0 | 4              | 300.0 | 600.0 | 6                   | 25.0 | 50.0 |  |

|                                      |       |                        |                       |       |       |                |       |       |                     |      | •    |  |

| 1010_101                             | 100.0 | 200.0                  | 2                     | 200.0 | 400.0 | 2.5            | 250.0 | 500.0 | 8                   | 25.0 | 50.0 |  |

| 1010_110                             | 100.0 | 200.0                  | 2                     | 200.0 | 400.0 | 3              | 300.0 | 600.0 | 8                   | 25.0 | 50.0 |  |

| 1010_111                             | 100.0 | 200.0                  | 2                     | 200.0 | 400.0 | 3.5            | 350.0 | 700.0 | 8                   | 25.0 | 50.0 |  |

|                                      |       |                        |                       |       | 1     |                |       | 1     |                     | 1    |      |  |

| 1011_000                             |       |                        |                       |       |       | Reserved       |       |       |                     |      |      |  |

| 1011_001                             | 80.0  | 160.0                  | 2.5                   | 200.0 | 400.0 | 2.5            | 200.0 | 400.0 | 8                   | 25.0 | 50.0 |  |

| 1011_010                             | 80.0  | 160.0                  | 2.5                   | 200.0 | 400.0 | 3              | 240.0 | 480.0 | 8                   | 25.0 | 50.0 |  |

| 1011_011                             | 80.0  | 160.0                  | 2.5                   | 200.0 | 400.0 | 3.5            | 280.0 | 560.0 | 8                   | 25.0 | 50.0 |  |

| 1011_100                             | 80.0  | 160.0                  | 2.5                   | 200.0 | 400.0 | 4              | 320.0 | 640.0 | 8                   | 25.0 | 50.0 |  |

| Mode <sup>3</sup>      |      | Clock<br>Hz) | CPM                                   |       | Clock<br>Hz) | CPU<br>Multiplication |       | Clock<br>Hz) | Bus                |       | Clock<br>Hz) |

|------------------------|------|--------------|---------------------------------------|-------|--------------|-----------------------|-------|--------------|--------------------|-------|--------------|

| MODCK_H-<br>MODCK[1-3] | Low  | High         | Multiplication<br>Factor <sup>4</sup> | Low   | High         | Eactor <sup>5</sup>   | Low   | High         | Division<br>Factor | Low   | High         |

|                        |      |              |                                       |       |              |                       |       |              |                    |       |              |

| 1000_000               |      |              | Γ                                     |       |              | Reserved              |       |              | r                  |       |              |

| 1000_001               | 50.0 | 66.7         | 3                                     | 150.0 | 200.0        | 2.5                   | 150.0 | 166.7        | 2.5                | 60.0  | 80.0         |

| 1000_010               | 50.0 | 66.7         | 3                                     | 150.0 | 200.0        | 3                     | 180.0 | 240.0        | 2.5                | 60.0  | 80.0         |

| 1000_011               | 50.0 | 66.7         | 3                                     | 150.0 | 200.0        | 3.5                   | 210.0 | 280.0        | 2.5                | 60.0  | 80.0         |

| 1000_100               | 50.0 | 66.7         | 3                                     | 150.0 | 200.0        | 4                     | 240.0 | 320.0        | 2.5                | 60.0  | 80.0         |

| 1000_101               | 50.0 | 66.7         | 3                                     | 150.0 | 200.0        | 4.5                   | 270.0 | 360.0        | 2.5                | 60.0  | 80.0         |

| 1001_000               |      |              |                                       |       |              | Reserved              |       |              |                    |       |              |

| 1001_001               |      |              |                                       |       |              | Reserved              |       |              |                    |       |              |

| 1001_010               |      |              |                                       |       |              | Reserved              |       |              |                    |       |              |

| 1001_011               | 50.0 | 66.7         | 4                                     | 200.0 | 266.6        | 4                     | 200.0 | 266.6        | 4                  | 50.0  | 66.7         |

| 1001_100               | 50.0 | 66.7         | 4                                     | 200.0 |              | 4.5                   | 225.0 |              | 4                  | 50.0  | 66.7         |

|                        |      |              |                                       |       |              |                       |       |              |                    |       |              |

| 1010_000               |      |              |                                       |       |              | Reserved              |       |              |                    |       |              |

| 1010_001               | 50.0 | 66.7         | 4                                     | 200.0 | 266.6        | 3                     | 200.0 | 266.6        | 3                  | 66.7  | 88.9         |

| 1010_010               | 50.0 | 66.7         | 4                                     | 200.0 | 266.6        | 3.5                   | 233.3 | 311.1        | 3                  | 66.7  | 88.9         |

| 1010_011               | 50.0 | 66.7         | 4                                     | 200.0 | 266.6        | 4                     | 266.7 | 355.5        | 3                  | 66.7  | 88.9         |

| 1010_100               | 50.0 | 66.7         | 4                                     | 200.0 | 266.6        | 4.5                   | 300.0 | 400.0        | 3                  | 66.7  | 88.9         |

|                        |      |              |                                       |       |              |                       |       |              |                    |       |              |

| 1011_000               |      |              |                                       |       |              | Reserved              |       |              |                    |       |              |

| 1011_001               | 50.0 | 66.7         | 4                                     | 200.0 | 266.6        | 2.5                   | 200.0 | 266.6        | 2.5                | 80.0  | 106.7        |

| 1011_010               | 50.0 | 66.7         | 4                                     | 200.0 | 266.6        | 3                     | 240.0 | 320.0        | 2.5                | 80.0  | 106.         |

| 1011_011               | 50.0 | 66.7         | 4                                     | 200.0 | 266.6        | 3.5                   | 280.0 | 373.3        | 2.5                | 80.0  | 106.         |

| 1011_100               | 50.0 | 66.7         | 4                                     | 200.0 | 266.6        | 4                     | 320.0 | 426.6        | 2.5                | 80.0  | 106.7        |

|                        | 1    | 1            | 1                                     | 1     | 1            |                       | 1     | r            |                    | 1     |              |

| 1011_101               | 50.0 | 66.7         | 4                                     | 200.0 | 266.6        | 2.5                   | 250.0 | 333.3        | 2                  | 100.0 | 133.3        |

| 1011_110               | 50.0 | 66.7         | 4                                     | 200.0 | 266.6        | 3                     | 300.0 | 400.0        | 2                  | 100.0 | 133.3        |

| 1011_111               | 50.0 | 66.7         | 4                                     | 200.0 | 266.6        | 3.5                   | 350.0 | 466.6        | 2                  | 100.0 | 133.3        |

## Table 19. Clock Configurations for PCI Agent Mode (PCI\_MODCK=0)<sup>1,2</sup> (continued)

| Table 20. Clock Configurations for PCI Agent Mode (PCI_M | IODCK=1) <sup>1,2</sup> (continued) |

|----------------------------------------------------------|-------------------------------------|

|----------------------------------------------------------|-------------------------------------|

| Mode <sup>3</sup>      | PCI (<br>(MI | Clock<br>Hz) | CPM<br>Multiplication |       | Clock<br>Hz) | CPU<br>Multiplication    |       | Clock<br>Hz) | Bus<br>Division |      | Clock<br>Hz) |

|------------------------|--------------|--------------|-----------------------|-------|--------------|--------------------------|-------|--------------|-----------------|------|--------------|

| MODCK_H-<br>MODCK[1-3] | Low          | High         | Factor <sup>4</sup>   | Low   | High         | High Factor <sup>5</sup> | Low   | High         | Factor          | Low  | High         |

| 0100_100               | 25.0         | 50.0         | 6                     | 150.0 | 300.0        | 4.5                      | 225.0 | 450.0        | 3               | 50.0 | 100.0        |

|                        |              |              |                       |       |              |                          |       |              |                 |      |              |

| 0101_000               | 30.0         | 50.0         | 5                     | 150.0 | 250.0        | 2.5                      | 150.0 | 250.0        | 2.5             | 60.0 | 100.0        |

| 0101_001               | 25.0         | 50.0         | 5                     | 125.0 | 250.0        | 3                        | 150.0 | 300.0        | 2.5             | 50.0 | 100.0        |

| 0101_010               | 25.0         | 50.0         | 5                     | 125.0 | 250.0        | 3.5                      | 175.0 | 350.0        | 2.5             | 50.0 | 100.0        |

| 0101_011               | 25.0         | 50.0         | 5                     | 125.0 | 250.0        | 4                        | 200.0 | 400.0        | 2.5             | 50.0 | 100.0        |

| 0101_100               | 25.0         | 50.0         | 5                     | 125.0 | 250.0        | 4.5                      | 225.0 | 450.0        | 2.5             | 50.0 | 100.0        |

| 0101_101               | 25.0         | 50.0         | 5                     | 125.0 | 250.0        | 5                        | 250.0 | 500.0        | 2.5             | 50.0 | 100.0        |

| 0101_110               | 25.0         | 50.0         | 5                     | 125.0 | 250.0        | 5.5                      | 275.0 | 550.0        | 2.5             | 50.0 | 100.0        |

|                        |              |              |                       |       |              |                          |       |              |                 |      |              |

| 0110_000               |              |              |                       |       |              | Reserved                 |       |              |                 |      |              |

| 0110_001               | 25.0         | 50.0         | 8                     | 200.0 | 400.0        | 3                        | 200.0 | 400.0        | 3               | 66.7 | 133.3        |

| 0110_010               | 25.0         | 50.0         | 8                     | 200.0 | 400.0        | 3.5                      | 233.3 | 466.7        | 3               | 66.7 | 133.3        |

| 0110_011               | 25.0         | 50.0         | 8                     | 200.0 | 400.0        | 4                        | 266.7 | 533.3        | 3               | 66.7 | 133.3        |

| 0110_100               | 25.0         | 50.0         | 8                     | 200.0 | 400.0        | 4.5                      | 300.0 | 600.0        | 3               | 66.7 | 133.3        |

|                        |              |              |                       |       |              |                          |       |              |                 |      |              |

| 0111_000               | 25.0         | 50.0         | 6                     | 150.0 | 300.0        | 2                        | 150.0 | 300.0        | 2               | 75.0 | 150.0        |

| 0111_001               | 25.0         | 50.0         | 6                     | 150.0 | 300.0        | 2.5                      | 187.5 | 375.0        | 2               | 75.0 | 150.0        |

| 0111_010               | 25.0         | 50.0         | 6                     | 150.0 | 300.0        | 3                        | 225.0 | 450.0        | 2               | 75.0 | 150.0        |

| 0111_011               | 25.0         | 50.0         | 6                     | 150.0 | 300.0        | 3.5                      | 262.5 | 525.0        | 2               | 75.0 | 150.0        |

|                        |              |              |                       |       |              |                          |       |              |                 |      |              |

| 1000_000               |              |              |                       |       |              | Reserved                 |       |              |                 |      |              |

| 1000_001               | 25.0         | 50.0         | 6                     | 150.0 | 300.0        | 2.5                      | 150.0 | 300.0        | 2.5             | 60.0 | 120.0        |

| 1000_010               | 25.0         | 50.0         | 6                     | 150.0 | 300.0        | 3                        | 180.0 | 360.0        | 2.5             | 60.0 | 120.0        |

| 1000_011               | 25.0         | 50.0         | 6                     | 150.0 | 300.0        | 3.5                      | 210.0 | 420.0        | 2.5             | 60.0 | 120.0        |

| 1000_100               | 25.0         | 50.0         | 6                     | 150.0 | 300.0        | 4                        | 240.0 | 480.0        | 2.5             | 60.0 | 120.0        |

| 1000_101               | 25.0         | 50.0         | 6                     | 150.0 | 300.0        | 4.5                      | 270.0 | 540.0        | 2.5             | 60.0 | 120.0        |

|                        |              |              |                       |       |              |                          |       |              |                 |      |              |

| 1001_000               |              |              |                       |       |              | Reserved                 |       |              |                 |      |              |

| 1001_001               |              |              |                       |       |              | Reserved                 |       |              |                 |      |              |

| Pin Name                               |                      |      |

|----------------------------------------|----------------------|------|

| MPC8272/MPC8248 and<br>MPC8271/MPC8247 | MPC8272/MPC8271 Only | Ball |

| A3                                     | 0                    | B15  |

| A3                                     | 1                    | A15  |

| TT                                     | 0                    | B3   |

| TT                                     | 1                    | E8   |

| TT                                     | 2                    | D7   |

| TT                                     | 3                    | C4   |

| TT                                     | 4                    | E7   |

| TBS                                    | T                    | E3   |

| TSI                                    | ZO                   | E4   |

| TSI                                    | Z1                   | E5   |

| TSI                                    | 72                   | C3   |

| TSI                                    | Z3                   | D5   |

| AAC                                    | <del>א</del> כ       | D3   |

| ARTRY                                  |                      | C2   |

| DBG/IRQ7                               |                      | F16  |

| DBB/IRQ3                               |                      | D18  |

| D0                                     |                      | AC1  |

| D1                                     |                      | AA1  |

| D2                                     |                      | V3   |

| D3                                     |                      | R5   |

| D4                                     |                      | P4   |

| D5                                     |                      | M4   |

| D6                                     |                      | J4   |

| D7                                     |                      | G1   |

| D8                                     |                      | W6   |

| D9                                     |                      | Y3   |

| D1                                     | 0                    | V1   |

| D1                                     | 1                    | N6   |

| D1                                     | 2                    | P3   |

| D1                                     | 3                    | M2   |

| D14                                    |                      | J5   |

#### Table 21. Pinout (continued)

Pinout

| Table 21. Pinout (continued)           |                      |      |  |  |

|----------------------------------------|----------------------|------|--|--|

| Pin I                                  |                      |      |  |  |

| MPC8272/MPC8248 and<br>MPC8271/MPC8247 | MPC8272/MPC8271 Only | Ball |  |  |

| D                                      | 46                   | H4   |  |  |

| D                                      | 47                   | F2   |  |  |

| D                                      | 48                   | AB1  |  |  |

| D                                      | 49                   | U4   |  |  |

| D                                      | 50                   | U1   |  |  |

| D                                      | 51                   | R3   |  |  |

| D                                      | 52                   | N3   |  |  |

| D                                      | 53                   | K2   |  |  |

| D                                      | 54                   | H5   |  |  |

| D                                      | 55                   | F4   |  |  |

| D                                      | 56                   | AA3  |  |  |

| D                                      | 57                   | U5   |  |  |

| D                                      | 58                   | U2   |  |  |

| D59                                    |                      | P5   |  |  |

| D60                                    |                      | М3   |  |  |

| D61                                    |                      | K4   |  |  |

| D62                                    |                      | H3   |  |  |

| D63                                    |                      | E1   |  |  |

| IRQ3/CKSTP_OUT/EXT_BR3                 |                      | B16  |  |  |

| IRQ4/CORE_SRESET/EXT_BG3               |                      | C15  |  |  |

| IRQ5/TBEN/EXT_DBG3/CINT                |                      | Y4   |  |  |

| PSDVAL                                 |                      | C19  |  |  |

| ī                                      | Ā                    | AA4  |  |  |

| TEA                                    |                      | AB6  |  |  |

| GBL/IRQ1                               |                      | D15  |  |  |

| CI/BADDR29/IRQ2                        |                      | D16  |  |  |

| WT/BADDR30/IRQ3                        |                      | C16  |  |  |

| BADDR31                                | /IRQ5/CINT           | E17  |  |  |

| CPU_BR                                 | /INT_OUT             | B20  |  |  |

| C                                      | <u>S0</u>            | AE6  |  |  |

|                                        |                      |      |  |  |

#### Table 21. Pinout (continued)

MPC8272 PowerQUICC II Family Hardware Specifications, Rev. 3

CS1

AD7

| Table 21. Pinout | (continued) |

|------------------|-------------|

|------------------|-------------|

| Pin Name                               |                        |      |

|----------------------------------------|------------------------|------|

| MPC8272/MPC8248 and<br>MPC8271/MPC8247 | MPC8272/MPC8271 Only   | Ball |

| C                                      | 52                     | AF5  |

| C                                      | 53                     | AC8  |

| C                                      | 54                     | AF6  |

| C                                      | 55                     | AD8  |

| CS6/BC                                 | TL1/SMI                | AC9  |

| CS7/TL                                 | BISYNC                 | AB9  |

| BADDR                                  | 27/IRQ1                | AB8  |

| BADDR                                  | 28/IRQ2                | AC7  |

| ALE/                                   | IRQ4                   | AF4  |

| BC                                     | TLO                    | AF3  |

| PWE0/PSDI                              | DQM0/PBS0              | AD6  |

| PWE1/PSDI                              | DQM1/PBS1              | AE5  |

| PWE2/PSDI                              | DQM2/PBS2              | AE3  |

| PWE3/PSDI                              | DQM3/PBS3              | AF2  |

| PWE4/PSDI                              | PWE4/PSDDQM4/PBS4      |      |

| PWE5/PSDI                              | PWE5/PSDDQM5/PBS5      |      |

| PWE6/PSDI                              | PWE6/PSDDQM6/PBS6      |      |

| PWE7/PSDI                              | PWE7/PSDDQM7/PBS7      |      |

| PSDA10/PGPL0                           |                        | AE2  |

| PSDWE/PGPL1                            |                        | AD3  |

| POE/PSDF                               | AS/PGPL2               | AB4  |

| PSDCAS                                 | 5/PGPL3                | AC3  |

| PGTA/PUPM                              | WAIT/PGPL4             | AD2  |

| PSDAMU                                 | X/PGPL5                | AC2  |

| PCI_N                                  | PCI_MODE <sup>1</sup>  |      |

| PCI_CFG0 (P                            | PCI_CFG0 (PCI_HOST_EN) |      |

| PCI_CFG1 (Ē                            | PCI_CFG1 (PCI_ARB_EN)  |      |

| PCI_CFG2 (D                            | DLL_ENABLE)            | AE23 |

| PCI_                                   | PAR                    | AF12 |

| PCI_F                                  | RAME                   | AD15 |

| PCI_                                   | TRDY                   | AF16 |

Pinout

#### Table 21. Pinout (continued)

| Pin Name                               |                      |      |

|----------------------------------------|----------------------|------|

| MPC8272/MPC8248 and<br>MPC8271/MPC8247 | MPC8272/MPC8271 Only | Ball |

| PCI_II                                 | RDY CONTRACT         | AF15 |

| PCI_S                                  | TOP                  | AE15 |

| PCI_DE                                 | VSEL                 | AE14 |

| PCI_ID                                 | DSEL                 | AC17 |

| PCI_P                                  | ERR                  | AD14 |

| PCI_S                                  | ERR                  | AD13 |

| PCI_R                                  | EQ0                  | AE20 |

| PCI_REQ1/CI                            | PCI_HS_ES            | AF14 |

| PCI_G                                  | NTO                  | AD20 |

| PCI_GNT1/CP                            | CI_HS_LED            | AE13 |

| PCI_GNT2/CPC                           | CI_HS_ENUM           | AF21 |

| PCI_F                                  | AST                  | AF22 |

| PCI_INTA                               |                      | AE21 |

| PCI_REQ2                               |                      | AB14 |

| DLLOUT                                 |                      | AC22 |

| PCI_AD0                                |                      | AF7  |

| PCI_AD1                                |                      | AE10 |

| PCI_AD2                                |                      | AB10 |

| PCI_/                                  | AD3                  | AD10 |

| PCI_/                                  | AD4                  | AE9  |

| PCI_/                                  | AD5                  | AF8  |

| PCI_/                                  | AD6                  | AC10 |

| PCI_/                                  | AD7                  | AE11 |

| PCI_/                                  | AD8                  | AB11 |

| PCI_AD9                                |                      | AF10 |

| PCI_A                                  | D10                  | AF9  |

| PCI_A                                  | D11                  | AB12 |

| PCI_A                                  | D12                  | AC12 |

| PCI_A                                  | D13                  | AD12 |

| PCI_A                                  | D14                  | AF11 |

| PCI_AD15                               |                      | AB13 |

| Pin Name                                                    |                     |                   |

|-------------------------------------------------------------|---------------------|-------------------|

| MPC8272/MPC8248 and<br>MPC8271/MPC8247 MPC8272/MPC8271 Only |                     | Ball              |

| PA31/FCC1_MII_COL                                           | FCC1_UT_TXENB       | G22 <sup>3</sup>  |

| PB18/FCC2_MII_                                              | _HDLC_RXD3          | T25 <sup>3</sup>  |

| PB19/FCC2_MII_                                              | HDLC_RXD2           | P22 <sup>3</sup>  |

| PB20/FCC2_MII_HE                                            | DLC_RMII_RXD1       | L25 <sup>3</sup>  |

| PB21/FCC2_MII_HDLC_RMII                                     | _RXD0/FCC2_TRAN_RXD | J26 <sup>3</sup>  |

| PB22/FCC2_MII_HDLC_T><br>FCC2_RMI                           |                     | U23 <sup>3</sup>  |

| PB23/FCC2_MII_HDLC_T                                        | XD1/FCC2_RMII_TXD1  | U26 <sup>3</sup>  |

| PB24/FCC2_MII_HDLC                                          | _TXD2/L1RSYNCB2     | M24 <sup>3</sup>  |

| PB25/FCC2_MII_HDLC                                          | _TXD3/L1TSYNCB2     | M23 <sup>3</sup>  |

| PB26/FCC2_MII_(                                             | CRS/L1RXDB2         | H24 <sup>3</sup>  |

| PB27/FCC2_MII_0                                             | COL/L1TXDB2         | E25 <sup>3</sup>  |

| PB28/FCC2_MII_RMII_RX                                       | _ER/FCC2_RTS/TXD1   | D26 <sup>3</sup>  |

| PB29/FCC2_MII_                                              | _RMII_TX_EN         | K21 <sup>3</sup>  |

| PB30/FCC2_MII_RX_DV/                                        | FCC2_RMII_CRS_DV    | D24 <sup>3</sup>  |

| PB31/FCC2_MII_TX_ER                                         |                     | E23 <sup>3</sup>  |

| PC0/DREQ3/BRGO7/S                                           | MSYN1/L1CLKOA2      | AF23 <sup>3</sup> |

| PC1/BRG06/L1RQA2                                            |                     | AD23 <sup>3</sup> |

| PC4/SMRXD1/SI2_L1ST4/FCC2_CD                                |                     | AB22 <sup>3</sup> |

| PC5/SMTXD1/SI2_L                                            | 1ST3/FCC2_CTS       | AE24 <sup>3</sup> |

| PC6/FCC1_CD/SI2_L1ST2                                       | FCC1_UT_RXADDR2     | AF24 <sup>3</sup> |

| PC7/FCC1_CTS                                                | FCC1_UT_TXADDR2     | AE26 <sup>3</sup> |

| PC8/CD4/RTS1/SI                                             | 2_L1ST2/CTS3        | AC24 <sup>3</sup> |

| PC9/CTS4/L1                                                 | TSYNCA2             | AA23 <sup>3</sup> |

| PC10/CD3/USB_RN                                             |                     | AB25 <sup>3</sup> |

| PC11/CTS3/USB_RP/L1TXD3A2                                   |                     | V22 <sup>3</sup>  |

| PC12 FCC1_UT_RXADDR1                                        |                     | AA26 <sup>3</sup> |

| PC13/BRGO5 FCC1_UT_TXADDR1                                  |                     | V23 <sup>3</sup>  |

| PC14/CD1                                                    | FCC1_UT_RXADDR0     | W24 <sup>3</sup>  |

| PC15/CTS1                                                   | FCC1_UT_TXADDR0     | U24 <sup>3</sup>  |

| PC16/CLK16                                                  |                     | T23 <sup>3</sup>  |

| Pin Name                               |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|----------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MPC8272/MPC8248 and<br>MPC8271/MPC8247 | MPC8272/MPC8271 Only | Ball                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| CLKI                                   | N2                   | C21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| No con                                 | nect <sup>4</sup>    | D19 <sup>4</sup> , J3 <sup>4</sup> , AD24 <sup>5</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| l/O po                                 | ower                 | B4, F3, J2, N4, AD1, AD5, AE8,<br>AC13, AD18, AB24, AB26, W23, R25,<br>M25, F25, C25, C22, B17, B12, B8,<br>E6, F6, H6, L5, L6, P6, T6, U6, V5,<br>Y5, AA6, AA8, AA10, AA11, AA14,<br>AA16, AA17, AB19, AB20, W21, U21,<br>T21, P21, N21, M22, J22, H21, F21,<br>F19, F17, E16, F14, E13, E12, F10,<br>E10, E9                                                                                                                                                                                                                                                                                            |  |

| Core F                                 | ower                 | F5, K5, M5, AA5, AB7, AA13, AA19,<br>AA21, Y22, AC25, U22, R22, L21,<br>H22, E22, E20, E15, F13, F11, F8,<br>L3, V4, W3, AC11, AD11, AB15, U25,<br>T24, J24, H25, F23, B19, D17, C17,<br>D10, C10                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Grou                                   | Ind                  | E19, E2, K1, Y2, AE1, AE4, AD9,<br>AC14, AE17, AC19, AE25, V24, P26,<br>M26, G26, E26, B21, C12, C11, C8,<br>A8, B18, A18, A2, B1, B2, A5, C5, D4,<br>D6, G2, L4, P1, R1, R4, AC4, AE7,<br>AC23, Y25, N24, J23, A23, D23, D20,<br>E18, A13, A16, K10, K11, K12, K13,<br>K14, K15, K16, K17, L10, L11, L12,<br>L13, L14, L15, L16, L17, M10, M11,<br>M12, M13, M14, M15, M16, M17,<br>N10, N11, N12, N13, N14, N15, N16,<br>N17, P10, P11, P12, P13, P14, P15,<br>P16, P17, R10, R11,R12, R13, R14,<br>R15, R16, R17, T10, T11, T12, T13,<br>T14, T15, T16, T17, U10, U11, U12,<br>U13, U14, U15, U16, U17 |  |

#### Table 21. Pinout (continued)

<sup>1</sup> Must be tied to ground.

$^2$  Should be tied to VDDH via a 2K  $\Omega$  external pull-up resistor.

<sup>3</sup> The default configuration of the CPM pins (PA[8–31], PB[18–31], PC[0–1,4–29], PD[7–25, 29–31]) is input. To prevent excessive DC current, it is recommended either to pull unused pins to GND or VDDH, or to configure them as outputs.

<sup>4</sup> This pin is not connected. It should be left floating.

<sup>5</sup> Must be pulled down or left floating

Ordering Information

# **10 Ordering Information**

This figure provides an example of the Freescale part numbering nomenclature for the SoC. In addition to the processor frequency, the part numbering scheme also consists of a part modifier that indicates any enhancement(s) in the part from the original production design. Each part number also contains a revision code that refers to the die mask revision number and is specified in the part numbering scheme for identification purposes only. For more information, contact your local Freescale sales office.

Figure 15. Freescale Part Number Key

# **11 Document Revision History**

This table summarizes changes to this document.

| Table 23. Document Revision History |

|-------------------------------------|

|-------------------------------------|

| Revision | Date    | Substantive Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3        | 09/2011 | In Figure 15, "Freescale Part Number Key," added speed decoding information below processor frequency information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2        | 12/2008 | <ul> <li>Modified Figure 5, "SCC/SMC/SPI/I2C External Clock Diagram," and added second section of figure notes.</li> <li>In Table 12, modified "Data bus in pipeline mode" row and showed 66 MHz as "N/A."</li> <li>In Section 10, "Ordering Information," added "F = 133" to CPU/CPM/Bus Frequency.</li> <li>Added footnote concerning CPM_CLK/PCI_CLK ratio to column "PCI Division Factor" in Table 17, "Clock Configurations for PCI Host Mode (PCI_MODCK=0)," and Table 18, "Clock Configurations for PCI Host Mode (PCI_MODCK=1),."</li> <li>Removed overbar from DLL_ENABLE in Table 21, "Pinout."</li> </ul> |

| 1.5      | 12/2006 | Section 6, "AC Electrical Characteristics," removed deratings statement and clarified AC timing descriptions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1.4      | 05/2006 | Added row for 133 MHz configurations to Table 8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1.3      | 02/2006 | Inserted Section 6.3, "JTAG Timings."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Revision | Date    | Substantive Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2      | 09/2005 | <ul> <li>Added 133-MHz to the list of frequencies in the opening sentence of Section 6, "AC Electrical Characteristics".</li> <li>Added 133 MHz columns to Table 9, Table 11, Table 12, and Table 13.</li> <li>Added footnote 2 to Table 13.</li> <li>Added the conditions note directly above Table 12.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |