Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | -                                                                     |

| Core Size                  | -                                                                     |

| Speed                      | -                                                                     |

| Connectivity               | -                                                                     |

| Peripherals                | -                                                                     |

| Number of I/O              | -                                                                     |

| Program Memory Size        |                                                                       |

| Program Memory Type        | -                                                                     |

| EEPROM Size                | -                                                                     |

| RAM Size                   |                                                                       |

| Voltage - Supply (Vcc/Vdd) | -                                                                     |

| Data Converters            | -                                                                     |

| Oscillator Type            | -                                                                     |

| Operating Temperature      | -                                                                     |

| Mounting Type              | · .                                                                   |

| Package / Case             | -                                                                     |

| Supplier Device Package    | · · · · · · · · · · · · · · · · · · ·                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8272vrtmfa |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Overview

- Floating-point unit (FPU) supports floating-point arithmetic

- Support for cache locking

- Low-power consumption

- Separate power supply for internal logic (1.5 V) and for I/O (3.3 V)

- Separate PLLs for G2\_LE core and for the communications processor module (CPM)

- G2\_LE core and CPM can run at different frequencies for power/performance optimization

- Internal core/bus clock multiplier that provides ratios 2:1, 2.5:1, 3:1, 3.5:1, 4:1, 4.5:1, 5:1, 5.5:1, 6:1, 7:1, 8:1

- Internal CPM/bus clock multiplier that provides ratios 2:1, 2.5:1, 3:1, 3.5:1, 4:1, 5:1, 6:1, 8:1 ratios

- 64-bit data and 32-bit address 60x bus

- Bus supports multiple master designs—up to two external masters

- Supports single transfers and burst transfers

- 64-, 32-, 16-, and 8-bit port sizes controlled by on-chip memory controller

- 60x-to-PCI bridge

- Programmable host bridge and agent

- 32-bit data bus, 66 MHz, 3.3 V

- Synchronous and asynchronous 60x and PCI clock modes

- All internal address space available to external PCI host

- DMA for memory block transfers

- PCI-to-60x address remapping

- System interface unit (SIU)

- Clock synthesizer

- Reset controller

- Real-time clock (RTC) register

- Periodic interrupt timer

- Hardware bus monitor and software watchdog timer

- IEEE 1149.1 JTAG test access port

- Eight bank memory controller

- Glueless interface to SRAM, page mode SDRAM, DRAM, EPROM, Flash, and other user-definable peripherals

- Byte write enables

- 32-bit address decodes with programmable bank size

- Three user-programmable machines, general-purpose chip-select machine, and page mode pipeline SDRAM machine

- Byte selects for 64-bit bus width (60x)

- Dedicated interface logic for SDRAM

- Disable CPU mode

- Integrated security engine (SEC) (MPC8272 and MPC8248 only)

- Supports DES, 3DES, MD-5, SHA-1, AES, PKEU, RNG and RC-4 encryption algorithms in hardware

- Communications processor module (CPM)

- Embedded 32-bit communications processor (CP) uses a RISC architecture for flexible support for communications peripherals

- Interfaces to G2\_LE core through on-chip dual-port RAM and DMA controller. (Dual-port RAM size is 16 KB plus 4 KB dedicated instruction RAM.)

- Microcode tracing capabilities

- Eight CPM trap registers

- Universal serial bus (USB) controller

- Supports USB 2.0 full/low rate compatible

- USB host mode

- Supports control, bulk, interrupt, and isochronous data transfers

- CRC16 generation and checking

- NRZI encoding/decoding with bit stuffing

- Supports both 12- and 1.5-Mbps data rates (automatic generation of preamble token and data rate configuration). Note that low-speed operation requires an external hub.

- Flexible data buffers with multiple buffers per frame

- Supports local loopback mode for diagnostics (12 Mbps only)

- Supports USB slave mode

- Four independent endpoints support control, bulk, interrupt, and isochronous data transfers

- CRC16 generation and checking

- CRC5 checking

- NRZI encoding/decoding with bit stuffing

- 12- or 1.5-Mbps data rate

- Flexible data buffers with multiple buffers per frame

- Automatic retransmission upon transmit error

- Serial DMA channels for receive and transmit on all serial channels

- Parallel I/O registers with open-drain and interrupt capability

- Virtual DMA functionality executing memory-to-memory and memory-to-I/O transfers

- Two fast communication controllers (FCCs) supporting the following protocols:

- 10-/100-Mbit Ethernet/IEEE 802.3 CDMA/CS interface through media independent interface (MII)

- Transparent

- HDLC—up to T3 rates (clear channel)

- PCI bridge

- PCI Specification revision 2.2-compliant and supports frequencies up to 66 MHz

- On-chip arbitration

- Support for PCI to 60x memory and 60x memory to PCI streaming

- PCI host bridge or peripheral capabilities

- Includes four DMA channels for the following transfers:

- PCI-to-60x to 60x-to-PCI

- 60x-to-PCI to PCI-to-60x

- PCI-to-60x to PCI-to-60x

- 60x-to-PCI to 60x-to-PCI

- Includes the configuration registers required by the PCI standard (which are automatically loaded from the EPROM to configure the MPC8272) and message and doorbell registers

- Supports the  $I_2O$  standard

- Hot-Swap friendly (supports the Hot Swap Specification as defined by PICMG 2.1 R1.0 August 3, 1998)

- Support for 66 MHz, 3.3 V specification

- 60x-PCI bus core logic, which uses a buffer pool to allocate buffers for each port

# 2 **Operating Conditions**

This table shows the maximum electrical ratings.

Table 3. Absolute Maximum Ratings<sup>1</sup>

| Rating                           | Symbol           | Value           | Unit |

|----------------------------------|------------------|-----------------|------|

| Core supply voltage <sup>2</sup> | VDD              | -0.3 - 2.25     | V    |

| PLL supply voltage <sup>2</sup>  | VCCSYN           | -0.3 - 2.25     | V    |

| I/O supply voltage <sup>3</sup>  | VDDH             | -0.3 - 4.0      | V    |

| Input voltage <sup>4</sup>       | VIN              | GND(-0.3) - 3.6 | V    |

| Junction temperature             | Тј               | 120             | °C   |

| Storage temperature range        | T <sub>STG</sub> | (–55) – (+150)  | °C   |

<sup>1</sup> Absolute maximum ratings are stress ratings only; functional operation (see Table 4) at the maximums is not guaranteed. Stress beyond those listed may affect device reliability or cause permanent damage.

- <sup>2</sup> Caution: VDD/VCCSYN must not exceed VDDH by more than 0.4 V during normal operation. It is recommended that VDD/VCCSYN should be raised before or simultaneous with VDDH during power-on reset. VDD/VCCSYN may exceed VDDH by more than 0.4 V during power-on reset for no more than 100 ms.

- <sup>3</sup> Caution: VDDH can exceed VDD/VCCSYN by 3.3 V during power on reset by no more than 100 mSec. VDDH should not exceed VDD/VCCSYN by more than 2.5 V during normal operation.

- <sup>4</sup> Caution: VIN must not exceed VDDH by more than 2.5 V at any time, including during power-on reset.

**DC Electrical Characteristics**

| Characteristic          | Symbol          | Min | Мах | Unit |

|-------------------------|-----------------|-----|-----|------|

| I <sub>OL</sub> = 6.0mA | V <sub>OL</sub> | —   | 0.4 | V    |

| BR                      | _               |     |     |      |

| BG/IRQ6                 |                 |     |     |      |

| ABB/IRQ2                |                 |     |     |      |

| TS                      |                 |     |     |      |

| A[0-31]                 |                 |     |     |      |

| TT[0-4]                 |                 |     |     |      |

| TBST                    |                 |     |     |      |

| TSIZE[0-3]              |                 |     |     |      |

| AACK                    |                 |     |     |      |

| ARTRY                   |                 |     |     |      |

| DBG/IRQ7                |                 |     |     |      |

| DBB/IRQ3                |                 |     |     |      |

|                         |                 |     |     |      |

|                         |                 |     |     |      |

|                         |                 |     |     |      |

| IRQ5/TBEN/EXT_DBG3/CINT |                 |     |     |      |

| PSDVAL<br>TA            |                 |     |     |      |

|                         |                 |     |     |      |

| GBL/IRQ1                |                 |     |     |      |

| CI/BADDR29/IRQ2         |                 |     |     |      |

| WT/BADDR30/IRQ3         |                 |     |     |      |

| BADDR31/IRQ5/CINT       |                 |     |     |      |

| CPU_BR/INT_OUT          |                 |     |     |      |

| IRQ0/NMI_OUT            |                 |     |     |      |

| PORESET/PCI_RST         |                 |     |     |      |

| HRESET                  |                 |     |     |      |

| SRESET                  |                 |     |     |      |

| RSTCONF                 |                 |     |     |      |

|                         |                 |     |     |      |

# Table 5. DC Electrical Characteristics<sup>1</sup> (continued)

#### **DC Electrical Characteristics**

| Characteristic                     | Symbol          | Min | Max | Unit |

|------------------------------------|-----------------|-----|-----|------|

| I <sub>OL</sub> = 5.3mA            | V <sub>OL</sub> |     | 0.4 | V    |

| <u>ČŠ</u> [0–5]                    | 01              |     |     |      |

| CS6/BCTL1/SMI                      |                 |     |     |      |

| CS7/TLBSYNC                        |                 |     |     |      |

| BADDR27/ IRQ1                      |                 |     |     |      |

| BADDR28/ IRQ2                      |                 |     |     |      |

| ALE/ IRQ4                          |                 |     |     |      |

| BCTL0                              |                 |     |     |      |

| PWE[0-7]/PSDDQM[0-7]/PBS[0-7]      |                 |     |     |      |

| PSDA10/PGPL0                       |                 |     |     |      |

| PSDWE/PGPL1                        |                 |     |     |      |

| POE/PSDRAS/PGPL2                   |                 |     |     |      |

| PSDCAS/PGPL3                       |                 |     |     |      |

| PGTA/PUPMWAIT/PGPL4                |                 |     |     |      |

| PSDAMUX/PGPL5                      |                 |     |     |      |

| PCI_CFG0 (PCI_HOST_EN)             |                 |     |     |      |

| PCI_CFG1 (PCI_ARB_EN)              |                 |     |     |      |

| PCI_CFG2 (DLL_ENABLE)              |                 |     |     |      |

| MODCK1/RSRV/TC(0)/BNKSEL(0)        |                 |     |     |      |

| MODCK2/CSE0/TC(1)/BNKSEL(1)        |                 |     |     |      |

| MODCK3CSE1/TC(2)/BNKSEL(2)         |                 |     |     |      |

| $I_{OL} = 3.2 \text{mA}$           |                 |     |     |      |

| PCI_PAR                            |                 |     |     |      |

| PCI_FRAME                          |                 |     |     |      |

| PCI_TRDY                           |                 |     |     |      |

| PCI_IRDY                           |                 |     |     |      |

| PCI_STOP                           |                 |     |     |      |

| PCI_DEVSEL                         |                 |     |     |      |

| PCI_IDSEL                          |                 |     |     |      |

| PCI_PERR                           |                 |     |     |      |

| PCI_SERR                           |                 |     |     |      |

| PCI_REQ0                           |                 |     |     |      |

| PCI_REQ1/ CPI_HS_ES                |                 |     |     |      |

| PCI_GNT0                           |                 |     |     |      |

| PCI_GNT1/ CPI_HS_LES               |                 |     |     |      |

| PCI_GNT2/ CPI_HS_ENUM              |                 |     |     |      |

| PCI_RST                            |                 |     |     |      |

| PCI_INTA                           |                 |     |     |      |

| PCI_REQ2                           |                 |     |     |      |

| DLLOUT                             |                 |     |     |      |

| PCI_AD(0-31)                       |                 |     |     |      |

| PCI_AD(0-31)<br>PCI_C(0-3)/BE(0-3) |                 |     |     |      |

| PA[8–31]                           |                 |     |     |      |

| PB[18–31]                          |                 |     |     |      |

| PC[0–1,4–29]                       |                 |     |     |      |

| PD[7–25, 29–31]                    |                 |     |     |      |

| TDO                                |                 |     |     |      |

|                                    |                 |     |     |      |

## Table 5. DC Electrical Characteristics<sup>1</sup> (continued)

The default configuration of the CPM pins (PA[8-31], PB[18-31], PC[0-1,4-29], PD[7-25, 29-31]) is input. To prevent excessive DC current, it is recommended either to pull unused pins to GND or VDDH, or to configure them as outputs.

<sup>2</sup> TCK, TRST and PORESET have min VIH = 2.5V.

<sup>3</sup> V<sub>IL</sub> for IIC interface does not match IIC standard, but does meet IIC standard for V<sub>OL</sub> and should not cause any compatibility issue.

<sup>4</sup> The leakage current is measured for nominal VDDH,VCCSYN, and VDD.

## 4.7 References

Semiconductor Equipment and Materials International(415) 964-5111 805 East Middlefield Rd. Mountain View, CA 94043

MIL-SPEC and EIA/JESD (JEDEC) Specifications800-854-7179 or (Available from Global Engineering Documents)303-397-7956

JEDEC Specifications http://www.jedec.org

- 1. C.E. Triplett and B. Joiner, "An Experimental Characterization of a 272 PBGA Within an Automotive Engine Controller Module," Proceedings of SemiTherm, San Diego, 1998, pp. 47–54.

- 2. B. Joiner and V. Adams, "Measurement and Simulation of Junction to Board Thermal Resistance and Its Application in Thermal Modeling," Proceedings of SemiTherm, San Diego, 1999, pp. 212–220.

# 5 **Power Dissipation**

This table provides preliminary, estimated power dissipation for various configurations. Note that suitable thermal management is required to ensure the junction temperature does not exceed the maximum specified value. Also note that the I/O power should be included when determining whether to use a heat sink. For a complete list of possible clock configurations, see Section 7, "Clock Configuration Modes."

|              | СРМ                      |              | CPU                |              | P <sub>INT</sub> (W) <sup>2,3</sup><br>Vddl 1.5 Volts |         |  |

|--------------|--------------------------|--------------|--------------------|--------------|-------------------------------------------------------|---------|--|

| Bus<br>(MHz) | Multiplication<br>Factor | CPM<br>(MHz) | CPM Multiplication | CPU<br>(MHz) |                                                       |         |  |

|              | Factor                   |              | Factor             |              | Nominal                                               | Maximum |  |

| 66.67        | 3                        | 200          | 4                  | 266          | 1                                                     | 1.2     |  |

| 100          | 2                        | 200          | 3                  | 300          | 1.1                                                   | 1.3     |  |

| 100          | 2                        | 200          | 4                  | 400          | 1.3                                                   | 1.5     |  |

| 133          | 2                        | 267          | 3                  | 400          | 1.5                                                   | 1.8     |  |

Table 8. Estimated Power Dissipation for Various Configurations<sup>1</sup>

<sup>1</sup> Test temperature =  $105^{\circ}$  C

<sup>2</sup>  $P_{INT} = I_{DD} \times V_{DD}$  Watts

<sup>3</sup> Values do not include I/O. Add the following estimates for active I/O based on the following bus speeds:

66.7 MHz = 0.35 W (nominal), 0.4 W (maximum)

83.3 MHz = 0.4 W (nominal), 0.5 W (maximum)

100 MHz = 0.5 W (nominal), 0.6 W (maximum)

133 MHz = 0.7 W (nominal), 0.8 W (maximum)

AC Electrical Characteristics

# 6 AC Electrical Characteristics

The following sections include illustrations and tables of clock diagrams, signals, and CPM outputs and inputs for 66.67/83.33/100/133 MHz devices. Note that AC timings are based on a 50-pf load for MAX Delay and 10-pf load for MIN delay. Typical output buffer impedances are shown in this table.

| Output Buffers    | Typical Impedance ( $\Omega$ ) |

|-------------------|--------------------------------|

| 60x bus           | 45 or 27 <sup>2</sup>          |

| Memory controller | 45 or 27 <sup>2</sup>          |

| Parallel I/O      | 45                             |

| PCI               | 27                             |

<sup>1</sup> These are typical values at 65° C. Impedance may vary by ±25% with process and temperature.

<sup>2</sup> Impedance value is selected through SIUMCR[20,21]. See the SoC reference manual.

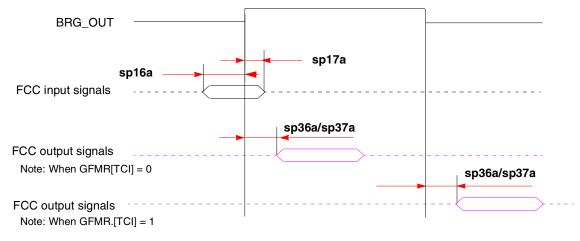

## 6.1 CPM AC Characteristics

This table lists CPM output characteristics.

| Spec Number |                |                                               |           | Value (ns) |            |               |           |            |            |     |

|-------------|----------------|-----------------------------------------------|-----------|------------|------------|---------------|-----------|------------|------------|-----|

| Max Min     | Characteristic | Maximum Delay                                 |           |            |            | Minimum Delay |           |            |            |     |

|             |                | 66<br>MHz                                     | 83<br>MHz | 100<br>MHz | 133<br>MHz | 66<br>MHz     | 83<br>MHz | 100<br>MHz | 133<br>MHz |     |

| sp36a       | sp37a          | FCC outputs—internal clock (NMSI)             | 6         | 5.5        | 5.5        | 5.5           | 0.5       | 0.5        | 0.5        | 0.5 |

| sp36b       | sp37b          | FCC outputs—external clock (NMSI)             |           | 8          | 8          | 8             | 2         | 2          | 2          | 2   |

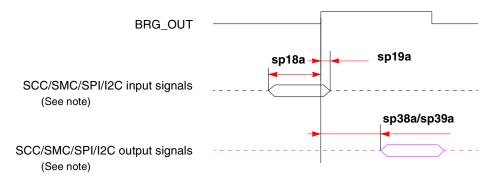

| sp38a       | sp39a          | SCC/SMC/SPI/I2C outputs—internal clock (NMSI) |           | 10         | 10         | 10            | 0         | 0          | 0          | 0   |

| sp38b       | sp39b          | SCC/SMC/SPI/I2C outputs—external clock (NMSI) | 8         | 8          | 8          | 8             | 2         | 2          | 2          | 2   |

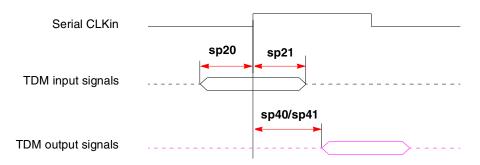

| sp40        | sp41           | TDM outputs/SI                                | 11        | 11         | 11         | 11            | 2.5       | 2.5        | 2.5        | 2.5 |

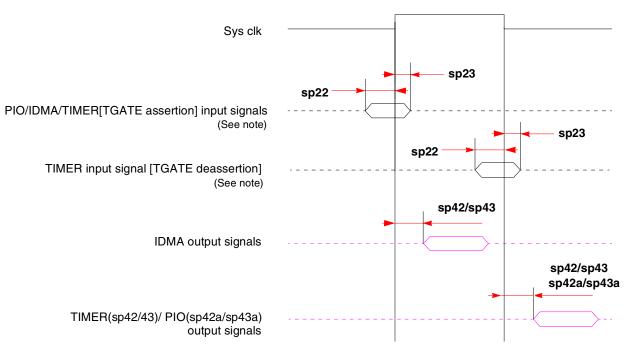

| sp42        | sp43           | TIMER/IDMA outputs                            |           | 11         | 11         | 11            | 0.5       | 0.5        | 0.5        | 0.5 |

| sp42a       | sp43a          | PIO outputs                                   | 11        | 11         | 11         | 11            | 0.5       | 0.5        | 0.5        | 0.5 |

### Table 10. AC Characteristics for CPM Outputs<sup>1</sup>

<sup>1</sup> Output specifications are measured from the 50% level of the rising edge of CLKIN to the 50% level of the signal. Timings are measured at the pin.

This table lists CPM input characteristics.

#### NOTE: Rise/Fall Time on CPM Input Pins

It is recommended that the rise/fall time on CPM input pins should not exceed 5 ns. This should be enforced especially on clock signals. Rise time refers to signal transitions from 10% to 90% of VCC; fall time refers to transitions from 90% to 10% of VCC.

| Spec Number |                |                                              |   | Value (ns) |            |            |           |           |            |            |

|-------------|----------------|----------------------------------------------|---|------------|------------|------------|-----------|-----------|------------|------------|

|             | Characteristic | Setup                                        |   |            |            | Hold       |           |           |            |            |

| Setup       | Setup Hold     |                                              |   | 83<br>MHz  | 100<br>MHz | 133<br>MHz | 66<br>MHz | 83<br>MHz | 100<br>MHz | 133<br>MHz |

| sp16a       | sp17a          | FCC inputs—internal clock (NMSI)             | 6 | 6          | 6          | 6          | 0         | 0         | 0          | 0          |

| sp16b       | sp17b          | FCC inputs-external clock (NMSI)             |   | 2.5        | 2.5        | 2.5        | 2         | 2         | 2          | 2          |

| sp18a       | sp19a          | SCC/SMC/SPI/I2C inputs—internal clock (NMSI) |   | 6          | 6          | 6          | 0         | 0         | 0          | 0          |

| sp18b       | sp19b          | SCC/SMC/SPI/I2C inputs—external clock (NMSI) |   | 4          | 4          | 4          | 2         | 2         | 2          | 2          |

| sp20        | sp21           | TDM inputs/SI                                |   | 3          | 3          | 3          | 2.5       | 2.5       | 2.5        | 2.5        |

| sp22        | sp23           | PIO/TIMER/IDMA inputs                        | 8 | 8          | 8          | 8          | 0.5       | 0.5       | 0.5        | 0.5        |

### Table 11. AC Characteristics for CPM Inputs<sup>1</sup>

<sup>1</sup> Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of CLKIN. Timings are measured at the pin.

#### NOTE

Although the specifications generally reference the rising edge of the clock, the following AC timing diagrams also apply when the falling edge is the active edge.

This figure shows the FCC internal clock.

Figure 3. FCC Internal Clock Diagram

This figure shows the SCC/SMC/SPI/I<sup>2</sup>C internal clock.

Note: There are four possible timing conditions for SCC and SPI:

- 1. Input sampled on the rising edge and output driven on the rising edge (shown).

- 2. Input sampled on the rising edge and output driven on the falling edge.

- 3. Input sampled on the falling edge and output driven on the falling edge.

- 4. Input sampled on the falling edge and output driven on the rising edge.

Figure 6. SCC/SMC/SPI/I<sup>2</sup>C Internal Clock Diagram

This figure shows TDM input and output signals.

Note: There are four possible TDM timing conditions:

- 1. Input sampled on the rising edge and output driven on the rising edge (shown).

- 2. Input sampled on the rising edge and output driven on the falling edge.

- 3. Input sampled on the falling edge and output driven on the falling edge.

- 4. Input sampled on the falling edge and output driven on the rising edge.

Figure 7. TDM Signal Diagram

#### **AC Electrical Characteristics**

This figure shows PIO and timer signals.

Note: TGATE is asserted on the rising edge of the clock; it is deasserted on the falling edge.

Figure 8. PIO and Timer Signal Diagram

## 6.2 SIU AC Characteristics

This table lists SIU input characteristics.

## NOTE: CLKIN Jitter and Duty Cycle

The CLKIN input to the SoC should not exceed +/- 150 psec of jitter (peak-to-peak). This represents total input jitter—the combination of short term (peak-to-peak) and long term (cumulative). The duty cycle of CLKIN should not exceed the ratio of 40:60.

## **NOTE: Spread Spectrum Clocking**

Spread spectrum clocking is allowed with 1% input frequency down-spread at maximum 60 KHz modulation rate regardless of input frequency.

## **NOTE: PCI AC Timing**

The SoC meets the timing requirements of *PCI Specification Revision 2.2.* See Section 7, "Clock Configuration Modes," and "Note: Tval (Output Hold)" to determine if a specific clock configuration is compliant.

**AC Electrical Characteristics**

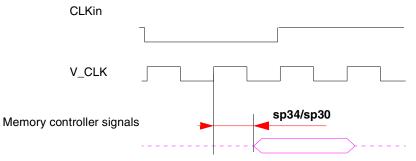

This figure shows signal behavior in MEMC mode.

Figure 10. MEMC Mode Diagram

NOTE

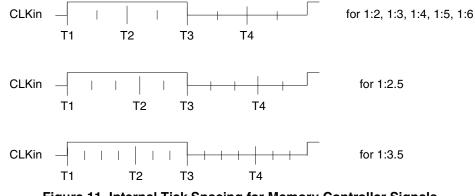

Generally, all SoC bus and system output signals are driven from the rising edge of the input clock (CLKin). Memory controller signals, however, trigger on four points within a CLKin cycle. Each cycle is divided by four internal ticks: T1, T2, T3, and T4. T1 always occurs at the rising edge, and T3 at the falling edge, of CLKin. However, the spacing of T2 and T4 depends on the PLL clock ratio selected, as shown in Table 14.

| Table 14. | . Tick Spacing for Memory Controller Signals |

|-----------|----------------------------------------------|

|-----------|----------------------------------------------|

| PLL Clock Ratio         | Tick Spacing (T1 Occurs at the Rising Edge of CLKin) |           |             |  |  |

|-------------------------|------------------------------------------------------|-----------|-------------|--|--|

|                         | T2                                                   | тз        | Т4          |  |  |

| 1:2, 1:3, 1:4, 1:5, 1:6 | 1/4 CLKin                                            | 1/2 CLKin | 3/4 CLKin   |  |  |

| 1:2.5                   | 3/10 CLKin                                           | 1/2 CLKin | 8/10 CLKin  |  |  |

| 1:3.5                   | 4/14 CLKin                                           | 1/2 CLKin | 11/14 CLKin |  |  |

This table is a representation of the information in Table 14.

Figure 11. Internal Tick Spacing for Memory Controller Signals

# 7 Clock Configuration Modes

As shown in this table, the clocking mode is set according to two sources:

- PCI\_CFG[0]— An input signal. Also defined as "PCI\_HOST\_EN." See Chapter 6, "External Signals," and Chapter 9, "PCI Bridge," in the SoC reference manual.

- PCI\_MODCK—Bit 27 in the Hard Reset Configuration Word. See Chapter 5, "Reset," in the SoC reference manual.

| Pi                      | ns                     | Clocking Mode | PCI Clock Frequency Range (MHz) | Reference |

|-------------------------|------------------------|---------------|---------------------------------|-----------|

| PCI_CFG[0] <sup>1</sup> | PCI_MODCK <sup>2</sup> | Clocking Mode | Torolock rrequency hange (Milz) | neierence |

| 0                       | 0                      | PCI host      | 50–66                           | Table 17  |

| 0                       | 1                      |               | 25–50                           | Table 18  |

| 1                       | 0                      | PCI agent     | 50–66                           | Table 19  |

| 1                       | 1                      |               | 25–50                           | Table 20  |

#### Table 16. SoC Clocking Modes

<sup>1</sup> PCI\_HOST\_EN

<sup>2</sup> Determines PCI clock frequency range.

Within each mode, the configuration of bus, core, PCI, and CPM frequencies is determined by seven bits during the power-on reset—three hardware configuration pins (MODCK[1–3]) and four bits from hardware configuration word[28–31] (MODCK\_H). Both the PLLs and the dividers are set according to the selected clock operation mode as described in the following sections.

## NOTE

Clock configurations change only after PORESET is asserted.

## NOTE: Tval (Output Hold)

The minimum Tval = 2 ns when  $PCI\_MODCK = 1$ , and the minimum Tval = 1 ns when  $PCI\_MODCK = 0$ . Therefore, designers should use clock configurations that fit this condition to achieve PCI-compliant AC timing.

## 7.1 PCI Host Mode

These tables show configurations for PCI host mode. The frequency values listed are for the purpose of illustration only. Users must select a mode and input bus frequency so that the resulting configuration does not exceed the frequency rating of the user's device. Note that in PCI host mode the input clock is the bus clock.

| Mode <sup>3</sup>      | Bus Clock<br>(MHz) |       |                     |          | CPM<br>Multiplication |                                       | Clock<br>Hz) | CPU   |                                 | Clock<br>Hz) | PCI  |  | Clock<br>Hz) |

|------------------------|--------------------|-------|---------------------|----------|-----------------------|---------------------------------------|--------------|-------|---------------------------------|--------------|------|--|--------------|

| MODCK_H-<br>MODCK[1-3] | Low                | High  | Factor <sup>4</sup> | Low      | High                  | Multiplication<br>Factor <sup>5</sup> | Low          | High  | Division<br>Factor <sup>6</sup> | Low          | High |  |              |

|                        |                    |       | Defau               | ult Mode | es (MO                | DCK_H=0000)                           |              |       |                                 |              |      |  |              |

| 0000_000               | 60.0               | 100.0 | 2                   | 120.0    | 200.0                 | 2.5                                   | 150.0        | 250.0 | 4                               | 30.0         | 50.0 |  |              |

| 0000_001               | 50.0               | 100.0 | 2                   | 100.0    | 200.0                 | 3                                     | 150.0        | 300.0 | 4                               | 25.0         | 50.0 |  |              |

| 0000_010               | 60.0               | 120.0 | 2.5                 | 150.0    | 300.0                 | 3                                     | 180.0        | 360.0 | 6                               | 25.0         | 50.0 |  |              |

| 0000_011               | 60.0               | 120.0 | 2.5                 | 150.0    | 300.0                 | 3.5                                   | 210.0        | 420.0 | 6                               | 25.0         | 50.0 |  |              |

| 0000_100               | 60.0               | 120.0 | 2.5                 | 150.0    | 300.0                 | 4                                     | 240.0        | 480.0 | 6                               | 25.0         | 50.0 |  |              |

| 0000_101               | 50.0               | 100.0 | 3                   | 150.0    | 300.0                 | 3                                     | 150.0        | 300.0 | 6                               | 25.0         | 50.0 |  |              |

| 0000_110               | 50.0               | 100.0 | 3                   | 150.0    | 300.0                 | 3.5                                   | 175.0        | 350.0 | 6                               | 25.0         | 50.0 |  |              |

| 0000_111               | 50.0               | 100.0 | 3                   | 150.0    | 300.0                 | 4                                     | 200.0        | 400.0 | 6                               | 25.0         | 50.0 |  |              |

|                        | •                  |       | ŀ                   | ull Cor  | figurati              | on Modes                              | •            |       |                                 | •            | •    |  |              |

| 0001_000               | 50.0               | 100.0 | 3                   | 150.0    | 300.0                 | 5                                     | 250.0        | 500.0 | 6                               | 25.0         | 50.0 |  |              |

| 0001_001               | 50.0               | 100.0 | 3                   | 150.0    | 300.0                 | 6                                     | 300.0        | 600.0 | 6                               | 25.0         | 50.0 |  |              |

| 0001_010               | 50.0               | 100.0 | 3                   | 150.0    | 300.0                 | 7                                     | 350.0        | 700.0 | 6                               | 25.0         | 50.0 |  |              |

| 0001_011               | 50.0               | 100.0 | 3                   | 150.0    | 300.0                 | 8                                     | 400.0        | 800.0 | 6                               | 25.0         | 50.0 |  |              |

|                        |                    | •     |                     |          |                       |                                       |              | •     |                                 |              |      |  |              |

| 0010_000               | 50.0               | 100.0 | 4                   | 200.0    | 400.0                 | 5                                     | 250.0        | 500.0 | 8                               | 25.0         | 50.0 |  |              |

| 0010_001               | 50.0               | 100.0 | 4                   | 200.0    | 400.0                 | 6                                     | 300.0        | 600.0 | 8                               | 25.0         | 50.0 |  |              |

| 0010_010               | 50.0               | 100.0 | 4                   | 200.0    | 400.0                 | 7                                     | 350.0        | 700.0 | 8                               | 25.0         | 50.0 |  |              |

| 0010_011               | 50.0               | 100.0 | 4                   | 200.0    | 400.0                 | 8                                     | 400.0        | 800.0 | 8                               | 25.0         | 50.0 |  |              |

|                        |                    |       |                     |          |                       |                                       |              |       |                                 |              |      |  |              |

| 0010_100               | 37.5               | 75.0  | 4                   | 150.0    | 300.0                 | 5                                     | 187.5        | 375.0 | 6                               | 25.0         | 50.0 |  |              |

| 0010_101               | 37.5               | 75.0  | 4                   | 150.0    | 300.0                 | 5.5                                   | 206.3        | 412.5 | 6                               | 25.0         | 50.0 |  |              |

| 0010_110               | 37.5               | 75.0  | 4                   | 150.0    | 300.0                 | 6                                     | 225.0        | 450.0 | 6                               | 25.0         | 50.0 |  |              |

|                        |                    |       |                     |          |                       |                                       |              |       |                                 |              |      |  |              |

| 0011_000               | 30.0               | 50.0  | 5                   | 150.0    | 250.0                 | 5                                     | 150.0        | 250.0 | 5                               | 30.0         | 50.0 |  |              |

| 0011_001               | 25.0               | 50.0  | 5                   | 125.0    | 250.0                 | 6                                     | 150.0        | 300.0 | 5                               | 25.0         | 50.0 |  |              |

| 0011_010               | 25.0               | 50.0  | 5                   | 125.0    | 250.0                 | 7                                     | 175.0        | 350.0 | 5                               | 25.0         | 50.0 |  |              |

| 0011_011               | 25.0               | 50.0  | 5                   | 125.0    | 250.0                 | 8                                     | 200.0        | 400.0 | 5                               | 25.0         | 50.0 |  |              |

|                        |                    |       |                     |          |                       |                                       |              |       |                                 |              |      |  |              |

| 0100_000               |                    |       |                     |          |                       | Reserved                              |              |       |                                 |              |      |  |              |

# Table 18. Clock Configurations for PCI Host Mode (PCI\_MODCK=1)<sup>1,2</sup>

| Mode <sup>3</sup>      | Bus Clock<br>(MHz) |       |                     |       | CPM<br>Multiplication | CPM Clock<br>(MHz)  |       | CPU<br>Multiplication | CPU Clock<br>(MHz)  |      | PCI<br>Division |  | Clock<br>Hz) |

|------------------------|--------------------|-------|---------------------|-------|-----------------------|---------------------|-------|-----------------------|---------------------|------|-----------------|--|--------------|

| MODCK_H-<br>MODCK[1-3] | Low                | High  | Factor <sup>4</sup> | Low   | High                  | Factor <sup>5</sup> | Low   | High                  | Factor <sup>6</sup> | Low  | High            |  |              |

| 0100_001               | 25.0               | 50.0  | 6                   | 150.0 | 300.0                 | 6                   | 150.0 | 300.0                 | 6                   | 25.0 | 50.0            |  |              |

| 0100_010               | 25.0               | 50.0  | 6                   | 150.0 | 300.0                 | 7                   | 175.0 | 350.0                 | 6                   | 25.0 | 50.0            |  |              |

| 0100_011               | 25.0               | 50.0  | 6                   | 150.0 | 300.0                 | 8                   | 200.0 | 400.0                 | 6                   | 25.0 | 50.0            |  |              |

| 0101_000               | 60.0               | 100.0 | 2                   | 120.0 | 200.0                 | 2.5                 | 150.0 | 250.0                 | 4                   | 30.0 | 50.0            |  |              |

| 0101_001               | 50.0               | 100.0 | 2                   | 100.0 | 200.0                 | 3                   | 150.0 | 300.0                 | 4                   | 25.0 | 50.0            |  |              |

| 0101_010               | 50.0               | 100.0 | 2                   | 100.0 | 200.0                 | 3.5                 | 175.0 | 350.0                 | 4                   | 25.0 | 50.0            |  |              |

| 0101_011               | 50.0               | 100.0 | 2                   | 100.0 | 200.0                 | 4                   | 200.0 | 400.0                 | 4                   | 25.0 | 50.0            |  |              |

| 0101_100               | 50.0               | 100.0 | 2                   | 100.0 | 200.0                 | 4.5                 | 225.0 | 450.0                 | 4                   | 25.0 | 50.0            |  |              |

|                        |                    |       |                     |       |                       |                     |       |                       |                     |      |                 |  |              |

| 0101_101               | 42.9               | 83.3  | 3                   | 128.6 | 250.0                 | 3.5                 | 150.0 | 291.7                 | 5                   | 25.7 | 50.0            |  |              |

| 0101_110               | 41.7               | 83.3  | 3                   | 125.0 | 250.0                 | 4                   | 166.7 | 333.3                 | 5                   | 25.0 | 50.0            |  |              |

| 0101_111               | 41.7               | 83.3  | 3                   | 125.0 | 250.0                 | 4.5                 | 187.5 | 375.0                 | 5                   | 25.0 | 50.0            |  |              |

|                        | 1                  | 1     |                     |       | 1                     |                     | 1     |                       |                     |      |                 |  |              |

| 0110_000               | 60.0               | 120.0 | 2.5                 | 150.0 | 300.0                 | 2.5                 | 150.0 | 300.0                 | 6                   | 25.0 | 50.0            |  |              |

| 0110_001               | 60.0               | 120.0 | 2.5                 | 150.0 | 300.0                 | 3                   | 180.0 | 360.0                 | 6                   | 25.0 | 50.0            |  |              |

| 0110_010               | 60.0               | 120.0 | 2.5                 | 150.0 | 300.0                 | 3.5                 | 210.0 | 420.0                 | 6                   | 25.0 | 50.0            |  |              |

| 0110_011               | 60.0               | 120.0 | 2.5                 | 150.0 | 300.0                 | 4                   | 240.0 | 480.0                 | 6                   | 25.0 | 50.0            |  |              |

| 0110_100               | 60.0               | 120.0 | 2.5                 | 150.0 | 300.0                 | 4.5                 | 270.0 | 540.0                 | 6                   | 25.0 | 50.0            |  |              |

| 0110_101               | 60.0               | 120.0 | 2.5                 | 150.0 | 300.0                 | 5                   | 300.0 | 600.0                 | 6                   | 25.0 | 50.0            |  |              |

| 0110_110               | 60.0               | 120.0 | 2.5                 | 150.0 | 300.0                 | 6                   | 360.0 | 720.0                 | 6                   | 25.0 | 50.0            |  |              |

| 0111_000               |                    |       |                     |       |                       | Reserved            |       |                       |                     |      |                 |  |              |

| 0111_001               | 50.0               | 100.0 | 3                   | 150.0 | 300.0                 | 3                   | 150.0 | 300.0                 | 6                   | 25.0 | 50.0            |  |              |

| 0111_010               | 50.0               | 100.0 | 3                   | 150.0 | 300.0                 | 3.5                 | 175.0 | 350.0                 | 6                   | 25.0 | 50.0            |  |              |

| 0111_011               | 50.0               | 100.0 | 3                   | 150.0 | 300.0                 | 4                   | 200.0 | 400.0                 | 6                   | 25.0 | 50.0            |  |              |

| 0111_100               | 50.0               | 100.0 | 3                   | 150.0 | 300.0                 | 4.5                 | 225.0 | 450.0                 | 6                   | 25.0 | 50.0            |  |              |

|                        | I                  |       |                     |       |                       |                     |       |                       |                     |      |                 |  |              |

| 1000_000               |                    |       | ſ                   |       |                       | Reserved            |       | I                     |                     |      |                 |  |              |

| 1000_001               | 66.7               | 133.3 | 3                   | 200.0 | 400.0                 | 3                   | 200.0 | 400.0                 | 8                   | 25.0 | 50.0            |  |              |

| Table 18. Clock Configurations for PCI Host Mode (PCI_MODCK=1) <sup>1,2</sup> (continued) |

|-------------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------------|

| Mode <sup>3</sup>      | Bus Clock |       | СРМ                   |       | Clock | CPU                 |       | Clock | PCI                 |      | Clock<br>Hz) |

|------------------------|-----------|-------|-----------------------|-------|-------|---------------------|-------|-------|---------------------|------|--------------|

|                        | (MI       | 1Z)   | CPM<br>Multiplication | (IVI) | Hz)   | Multiplication      | (IVI  | Hz)   | Division            | (IVI | ΠZ)          |

| MODCK_H-<br>MODCK[1-3] | Low       | High  | Factor <sup>4</sup>   | Low   | High  | Factor <sup>5</sup> | Low   | High  | Factor <sup>6</sup> | Low  | High         |

| 1000_010               | 66.7      | 133.3 | 3                     | 200.0 | 400.0 | 3.5                 | 233.3 | 466.7 | 8                   | 25.0 | 50.0         |

| 1000_011               | 66.7      | 133.3 | 3                     | 200.0 | 400.0 | 4                   | 266.7 | 533.3 | 8                   | 25.0 | 50.0         |

| 1000_100               | 66.7      | 133.3 | 3                     | 200.0 | 400.0 | 4.5                 | 300.0 | 600.0 | 8                   | 25.0 | 50.0         |

| 1000_101               | 66.7      | 133.3 | 3                     | 200.0 | 400.0 | 6                   | 400.0 | 800.0 | 8                   | 25.0 | 50.0         |

| 1000_110               | 66.7      | 133.3 | 3                     | 200.0 | 400.0 | 6.5                 | 433.3 | 866.7 | 8                   | 25.0 | 50.0         |

|                        |           |       |                       |       | 1     |                     |       | 1     |                     | 1    |              |

| 1001_000               |           |       |                       |       |       | Reserved            |       |       |                     |      |              |

| 1001_001               |           |       |                       |       |       | Reserved            |       |       |                     |      |              |

| 1001_010               | 57.1      | 114.3 | 3.5                   | 200.0 | 400.0 | 3.5                 | 200.0 | 400.0 | 8                   | 25.0 | 50.0         |

| 1001_011               | 57.1      | 114.3 | 3.5                   | 200.0 | 400.0 | 4                   | 228.6 | 457.1 | 8                   | 25.0 | 50.0         |

| 1001_100               | 57.1      | 114.3 | 3.5                   | 200.0 | 400.0 | 4.5                 | 257.1 | 514.3 | 8                   | 25.0 | 50.0         |

| 1001_101               | 42.9      | 85.7  | 3.5                   | 150.0 | 300.0 | 5                   | 214.3 | 428.6 | 6                   | 25.0 | 50.0         |

| 1001_110               | 42.9      | 85.7  | 3.5                   | 150.0 | 300.0 | 5.5                 | 235.7 | 471.4 | 6                   | 25.0 | 50.0         |

| 1001_111               | 42.9      | 85.7  | 3.5                   | 150.0 | 300.0 | 6                   | 257.1 | 514.3 | 6                   | 25.0 | 50.0         |

|                        |           |       |                       |       |       |                     |       |       |                     |      |              |

| 1010_000               | 75.0      | 150.0 | 2                     | 150.0 | 300.0 | 2                   | 150.0 | 300.0 | 6                   | 25.0 | 50.0         |

| 1010_001               | 75.0      | 150.0 | 2                     | 150.0 | 300.0 | 2.5                 | 187.5 | 375.0 | 6                   | 25.0 | 50.0         |

| 1010_010               | 75.0      | 150.0 | 2                     | 150.0 | 300.0 | 3                   | 225.0 | 450.0 | 6                   | 25.0 | 50.0         |

| 1010_011               | 75.0      | 150.0 | 2                     | 150.0 | 300.0 | 3.5                 | 262.5 | 525.0 | 6                   | 25.0 | 50.0         |

| 1010_100               | 75.0      | 150.0 | 2                     | 150.0 | 300.0 | 4                   | 300.0 | 600.0 | 6                   | 25.0 | 50.0         |

|                        |           |       |                       |       | 1     |                     |       | 1     |                     | 1    |              |

| 1010_101               | 100.0     | 200.0 | 2                     | 200.0 | 400.0 | 2.5                 | 250.0 | 500.0 | 8                   | 25.0 | 50.0         |

| 1010_110               | 100.0     | 200.0 | 2                     | 200.0 | 400.0 | 3                   | 300.0 | 600.0 | 8                   | 25.0 | 50.0         |

| 1010_111               | 100.0     | 200.0 | 2                     | 200.0 | 400.0 | 3.5                 | 350.0 | 700.0 | 8                   | 25.0 | 50.0         |

|                        |           |       |                       |       |       |                     |       |       |                     |      |              |

| 1011_000               |           |       |                       |       |       | Reserved            |       |       |                     |      |              |

| 1011_001               | 80.0      | 160.0 | 2.5                   | 200.0 | 400.0 | 2.5                 | 200.0 | 400.0 | 8                   | 25.0 | 50.0         |

| 1011_010               | 80.0      | 160.0 | 2.5                   | 200.0 | 400.0 | 3                   | 240.0 | 480.0 | 8                   | 25.0 | 50.0         |

| 1011_011               | 80.0      | 160.0 | 2.5                   | 200.0 | 400.0 | 3.5                 | 280.0 | 560.0 | 8                   | 25.0 | 50.0         |

| 1011_100               | 80.0      | 160.0 | 2.5                   | 200.0 | 400.0 | 4                   | 320.0 | 640.0 | 8                   | 25.0 | 50.0         |

| Mode <sup>3</sup>      | PCI Clock<br>(MHz) |          | CPM<br>Multiplication | CPM Clock<br>(MHz) |        | CPU<br>Multiplication | CPU Clock<br>(MHz) |       | Bus<br>Division | Bus Clock<br>(MHz) |      |

|------------------------|--------------------|----------|-----------------------|--------------------|--------|-----------------------|--------------------|-------|-----------------|--------------------|------|

| MODCK_H-<br>MODCK[1-3] | Low                | High     | Factor <sup>4</sup>   |                    | Factor | Low                   | High               |       |                 |                    |      |

|                        | 1                  |          |                       |                    |        |                       |                    |       |                 |                    |      |

| 1000_000               |                    |          | 1                     |                    |        | Reserved              |                    |       |                 |                    | r    |

| 1000_001               | 50.0               | 66.7     | 3                     | 150.0              | 200.0  | 2.5                   | 150.0              | 166.7 | 2.5             | 60.0               | 80.0 |

| 1000_010               | 50.0               | 66.7     | 3                     | 150.0              | 200.0  | 3                     | 180.0              | 240.0 | 2.5             | 60.0               | 80.0 |

| 1000_011               | 50.0               | 66.7     | 3                     | 150.0              | 200.0  | 3.5                   | 210.0              | 280.0 | 2.5             | 60.0               | 80.0 |

| 1000_100               | 50.0               | 66.7     | 3                     | 150.0              | 200.0  | 4                     | 240.0              | 320.0 | 2.5             | 60.0               | 80.0 |

| 1000_101               | 50.0               | 66.7     | 3                     | 150.0              | 200.0  | 4.5                   | 270.0              | 360.0 | 2.5             | 60.0               | 80.0 |

| 1001 000               |                    |          |                       |                    |        |                       |                    |       |                 |                    |      |

| 1001_000               |                    |          |                       |                    |        | Reserved              |                    |       |                 |                    |      |

| 1001_001               |                    | Reserved |                       |                    |        |                       |                    |       |                 |                    |      |

| 1001_010               |                    |          |                       |                    |        | Reserved              |                    |       |                 |                    |      |

| 1001_011               | 50.0               | 66.7     | 4                     | 200.0              | 266.6  | 4                     | 200.0              | 266.6 | 4               | 50.0               | 66.7 |

| 1001_100               | 50.0               | 66.7     | 4                     | 200.0              | 266.6  | 4.5                   | 225.0              | 300.0 | 4               | 50.0               | 66.7 |

| 1010_000               |                    |          |                       |                    |        | Reserved              |                    |       |                 |                    |      |

| 1010_001               | 50.0               | 66.7     | 4                     | 200.0              | 266.6  | 3                     | 200.0              | 266.6 | 3               | 66.7               | 88.9 |

| 1010_010               | 50.0               | 66.7     | 4                     | 200.0              | 266.6  | 3.5                   | 233.3              | 311.1 | 3               | 66.7               | 88.9 |

| 1010_011               | 50.0               | 66.7     | 4                     | 200.0              | 266.6  | 4                     | 266.7              | 355.5 | 3               | 66.7               | 88.9 |

| 1010_100               | 50.0               | 66.7     | 4                     | 200.0              |        |                       | 300.0              | 400.0 | 3               | 66.7               | 88.9 |

|                        | 1                  |          |                       |                    |        |                       |                    |       |                 |                    | L    |

| 1011_000               |                    |          |                       |                    |        | Reserved              |                    |       |                 |                    |      |

| 1011_001               | 50.0               | 66.7     | 4                     | 200.0              | 266.6  | 2.5                   | 200.0              | 266.6 | 2.5             | 80.0               | 106. |

| 1011_010               | 50.0               | 66.7     | 4                     | 200.0              | 266.6  | 3                     | 240.0              | 320.0 | 2.5             | 80.0               | 106. |

| 1011_011               | 50.0               | 66.7     | 4                     | 200.0              | 266.6  | 3.5                   | 280.0              | 373.3 | 2.5             | 80.0               | 106. |

| 1011_100               | 50.0               | 66.7     | 4                     | 200.0              |        |                       | 320.0              | 426.6 | 2.5             | 80.0               | 106. |

|                        |                    |          |                       |                    |        |                       |                    |       | -               |                    |      |

|                        | 50.0               | 66.7     | 4                     | 200.0              | 266.6  | 2.5                   | 250.0              | 333.3 | 2               | 100.0              | 133. |

| 1011_101               | 1                  | 66.7     | 4                     | 200.0              | 266.6  | 3                     | 300.0              | 400.0 | 2               | 100.0              | 133. |

| 1011_101<br>1011_110   | 50.0               | 00.7     |                       |                    |        |                       |                    |       |                 |                    |      |

## Table 19. Clock Configurations for PCI Agent Mode (PCI\_MODCK=0)<sup>1,2</sup> (continued)

| Mode <sup>3</sup>            | PCI Clock<br>(MHz) |      |                     |       |       | CPU<br>Multiplication | CPU Clock<br>(MHz) |       | Bus<br>Division | Bus Clock<br>(MHz) |       |

|------------------------------|--------------------|------|---------------------|-------|-------|-----------------------|--------------------|-------|-----------------|--------------------|-------|

| MODCK_H-<br>MODCK[1-3]       | Low                | High | Factor <sup>4</sup> | Low   | High  | Factor <sup>5</sup>   | Low                | High  | Factor          | Low                | High  |

| Default Modes (MODCK_H=0000) |                    |      |                     |       |       |                       |                    |       |                 |                    |       |

| 0000_000                     | 30.0               | 50.0 | 4                   | 120.0 | 200.0 | 2.5                   | 150.0              | 250.0 | 2               | 60.0               | 100.0 |

| 0000_001                     | 25.0               | 50.0 | 4                   | 100.0 | 200.0 | 3                     | 150.0              | 300.0 | 2               | 50.0               | 100.0 |

| 0000_010                     | 25.0               | 50.0 | 6                   | 150.0 | 300.0 | 3                     | 150.0              | 300.0 | 3               | 50.0               | 100.0 |

| 0000_011                     | 25.0               | 50.0 | 6                   | 150.0 | 300.0 | 4                     | 200.0              | 400.0 | 3               | 50.0               | 100.0 |

| 0000_100                     | 25.0               | 50.0 | 6                   | 150.0 | 300.0 | 3                     | 180.0              | 360.0 | 2.5             | 60.0               | 120.0 |

| 0000_101                     | 25.0               | 50.0 | 6                   | 150.0 | 300.0 | 3.5                   | 210.0              | 420.0 | 2.5             | 60.0               | 120.0 |

| 0000_110                     | 25.0               | 50.0 | 8                   | 200.0 | 400.0 | 3.5                   | 233.3              | 466.7 | 3               | 66.7               | 133.3 |

| 0000_111                     | 25.0               | 50.0 | 8                   | 200.0 | 400.0 | 3                     | 240.0              | 480.0 | 2.5             | 80.0               | 160.0 |

| Full Configuration Modes     |                    |      |                     |       |       |                       |                    |       |                 |                    |       |

| 0001_001                     | 30.0               | 50.0 | 4                   | 120.0 | 200.0 | 5                     | 150.0              | 250.0 | 4               | 30.0               | 50.0  |

| 0001_010                     | 25.0               | 50.0 | 4                   | 100.0 | 200.0 | 6                     | 150.0              | 300.0 | 4               | 25.0               | 50.0  |

| 0001_011                     | 25.0               | 50.0 | 4                   | 100.0 | 200.0 | 7                     | 175.0              | 350.0 | 4               | 25.0               | 50.0  |

| 0001_100                     | 25.0               | 50.0 | 4                   | 100.0 | 200.0 | 8                     | 200.0              | 400.0 | 4               | 25.0               | 50.0  |

|                              |                    |      |                     |       |       |                       |                    |       |                 |                    |       |

| 0010_001                     | 25.0               | 50.0 | 6                   | 150.0 | 300.0 | 3                     | 180.0              | 360.0 | 2.5             | 60.0               | 120.0 |

| 0010_010                     | 25.0               | 50.0 | 6                   | 150.0 | 300.0 | 3.5                   | 210.0              | 420.0 | 2.5             | 60.0               | 120.0 |

| 0010_011                     | 25.0               | 50.0 | 6                   | 150.0 | 300.0 | 4                     | 240.0              | 480.0 | 2.5             | 60.0               | 120.0 |

| 0010_100                     | 25.0               | 50.0 | 6                   | 150.0 | 300.0 | 4.5                   | 270.0              | 540.0 | 2.5             | 60.0               | 120.0 |

|                              |                    |      |                     |       |       |                       |                    |       |                 |                    |       |

| 0011_000                     |                    |      |                     |       |       | Reserved              |                    |       |                 |                    |       |

| 0011_001                     | 37.5               | 50.0 | 4                   | 150.0 | 200.0 | 3                     | 150.0              | 200.0 | 3               | 50.0               | 66.7  |

| 0011_010                     | 32.1               | 50.0 | 4                   | 128.6 | 200.0 | 3.5                   | 150.0              | 233.3 | 3               | 42.9               | 66.7  |

| 0011_011                     | 28.1               | 50.0 | 4                   | 112.5 | 200.0 | 4                     | 150.0              | 266.7 | 3               | 37.5               | 66.7  |

| 0011_100                     | 25.0               | 50.0 | 4                   | 100.0 | 200.0 | 4.5                   | 150.0              | 300.0 | 3               | 33.3               | 66.7  |

|                              |                    |      |                     |       |       |                       |                    |       |                 |                    |       |

| 0100_000                     |                    |      |                     |       |       | Reserved              |                    |       |                 |                    |       |

| 0100_001                     | 25.0               | 50.0 | 6                   | 150.0 | 300.0 | 3                     | 150.0              | 300.0 | 3               | 50.0               | 100.0 |

| 0100_010                     | 25.0               | 50.0 | 6                   | 150.0 | 300.0 | 3.5                   | 175.0              | 350.0 | 3               | 50.0               | 100.0 |

| 0100_011                     | 25.0               | 50.0 | 6                   | 150.0 | 300.0 | 4                     | 200.0              | 400.0 | 3               | 50.0               | 100.0 |

# Table 20. Clock Configurations for PCI Agent Mode (PCI\_MODCK=1)<sup>1,2</sup>

## Table 20. Clock Configurations for PCI Agent Mode (PCI\_MODCK=1)<sup>1,2</sup> (continued)

| MODCK[1-3]           1001_010           1001_011 | Low<br>25.0<br>25.0 | High<br>50.0<br>50.0 | Multiplication<br>Factor <sup>4</sup> | Low   | High  | Multiplication<br>Factor <sup>5</sup> | Low   | High  | Division<br>Factor | Low   | High  |

|--------------------------------------------------|---------------------|----------------------|---------------------------------------|-------|-------|---------------------------------------|-------|-------|--------------------|-------|-------|

| 1001_011<br>1001_100                             |                     |                      | 8                                     |       |       |                                       |       | ingn  |                    | LOW   | ingi  |

| 1001_100                                         |                     |                      | 8                                     |       |       | Reserved                              |       |       |                    |       |       |

|                                                  | 25.0                | 50.0                 | 1                                     | 200.0 | 400.0 | 4                                     | 200.0 | 400.0 | 4                  | 50.0  | 100.0 |

| 1010_000                                         |                     |                      | 8                                     | 200.0 | 400.0 | 4.5                                   | 225.0 | 450.0 | 4                  | 50.0  | 100.0 |

| 1010_000                                         |                     |                      |                                       |       |       | Reserved                              |       |       |                    |       |       |

| 1010_001                                         | 25.0                | 50.0                 | 8                                     | 200.0 | 400.0 | 3                                     | 200.0 | 400.0 | 3                  | 66.7  | 133.3 |

|                                                  | 25.0                | 50.0                 | 8                                     | 200.0 | 400.0 | 3.5                                   | 233.3 | 466.7 | 3                  | 66.7  | 133.3 |

|                                                  | 25.0                | 50.0                 | 8                                     | 200.0 | 400.0 | 4                                     | 266.7 | 533.3 | 3                  | 66.7  | 133.3 |

| 1010_100                                         | 25.0                | 50.0                 | 8                                     | 200.0 | 400.0 | 4.5                                   | 300.0 | 600.0 | 3                  | 66.7  | 133.3 |

|                                                  |                     |                      |                                       |       |       |                                       |       |       |                    |       |       |

| 1011_000                                         |                     |                      |                                       |       |       | Reserved                              |       |       |                    |       |       |

| 1011_001                                         | 25.0                | 50.0                 | 8                                     | 200.0 | 400.0 | 2.5                                   | 200.0 | 400.0 | 2.5                | 80.0  | 160.0 |

| 1011_010                                         | 25.0                | 50.0                 | 8                                     | 200.0 | 400.0 | 3                                     | 240.0 | 480.0 | 2.5                | 80.0  | 160.0 |

| 1011_011                                         | 25.0                | 50.0                 | 8                                     | 200.0 | 400.0 | 3.5                                   | 280.0 | 560.0 | 2.5                | 80.0  | 160.0 |

| 1011_100                                         | 25.0                | 50.0                 | 8                                     | 200.0 | 400.0 | 4                                     | 320.0 | 640.0 | 2.5                | 80.0  | 160.0 |

|                                                  |                     |                      |                                       |       | 1     |                                       | 1     |       |                    |       | r     |

| 1011_101                                         | 25.0                | 50.0                 | 8                                     | 200.0 | 400.0 | 2.5                                   | 250.0 | 500.0 | 2                  | 100.0 | 200.0 |

| 1011_110                                         | 25.0                | 50.0                 | 8                                     | 200.0 | 400.0 | 3                                     | 300.0 | 600.0 | 2                  | 100.0 | 200.0 |

| 1011_111                                         | 25.0                | 50.0                 | 8                                     | 200.0 | 400.0 | 3.5                                   | 350.0 | 700.0 | 2                  | 100.0 | 200.0 |

| 1100_101                                         | 25.0                | 50.0                 | 6                                     | 150.0 | 300.0 | 4                                     | 200.0 | 400.0 | 3                  | 50.0  | 100.0 |

|                                                  | 25.0                | 50.0                 | 6                                     | 150.0 | 300.0 | 4.5                                   | 225.0 | 450.0 | 3                  | 50.0  | 100.0 |

| 1100_111                                         | 25.0                | 50.0                 | 6                                     | 150.0 | 300.0 | 5                                     | 250.0 | 500.0 | 3                  | 50.0  | 100.0 |

| 1101_000                                         | 25.0                | 50.0                 | 6                                     | 150.0 | 300.0 | 5.5                                   | 275.0 | 550.0 | 3                  | 50.0  | 100.0 |

|                                                  |                     |                      | •                                     |       |       | •                                     |       |       |                    |       |       |

| 1101_001                                         | 25.0                | 50.0                 | 6                                     | 150.0 | 300.0 | 3.5                                   | 210.0 | 420.0 | 2.5                | 60.0  | 120.0 |

| 1101_010                                         | 25.0                | 50.0                 | 6                                     | 150.0 | 300.0 | 4                                     | 240.0 | 480.0 | 2.5                | 60.0  | 120.0 |

| 1101_011                                         | 25.0                | 50.0                 | 6                                     | 150.0 | 300.0 | 4.5                                   | 270.0 | 540.0 | 2.5                | 60.0  | 120.0 |

| 1101_100                                         | 25.0                | 50.0                 | 6                                     | 150.0 | 300.0 | 5                                     | 300.0 | 600.0 | 2.5                | 60.0  | 120.0 |

| Table 21. Pinout | (continued) |

|------------------|-------------|

|------------------|-------------|

| Pin N                                  | lame                 |      |  |  |  |  |  |

|----------------------------------------|----------------------|------|--|--|--|--|--|

| MPC8272/MPC8248 and<br>MPC8271/MPC8247 | MPC8272/MPC8271 Only | Ball |  |  |  |  |  |

| C                                      | 52                   | AF5  |  |  |  |  |  |

| C                                      | CS3                  |      |  |  |  |  |  |

| C                                      | CS4                  |      |  |  |  |  |  |

| C                                      | 55                   | AD8  |  |  |  |  |  |

| CS6/BC                                 | TL1/SMI              | AC9  |  |  |  |  |  |

| CS7/TL                                 | BISYNC               | AB9  |  |  |  |  |  |

| BADDR                                  | 27/IRQ1              | AB8  |  |  |  |  |  |

| BADDR                                  | 28/IRQ2              | AC7  |  |  |  |  |  |

| ALE/                                   | IRQ4                 | AF4  |  |  |  |  |  |

| BC                                     | TLO                  | AF3  |  |  |  |  |  |

| PWE0/PSDI                              | DQM0/PBS0            | AD6  |  |  |  |  |  |

| PWE1/PSDI                              | PWE1/PSDDQM1/PBS1    |      |  |  |  |  |  |

| PWE2/PSDI                              | PWE2/PSDDQM2/PBS2    |      |  |  |  |  |  |

| PWE3/PSDI                              | DQM3/PBS3            | AF2  |  |  |  |  |  |

| PWE4/PSDI                              | DQM4/PBS4            | AC6  |  |  |  |  |  |

| PWE5/PSDI                              | DQM5/PBS5            | AC5  |  |  |  |  |  |

| PWE6/PSDI                              | DQM6/PBS6            | AD4  |  |  |  |  |  |

| PWE7/PSDI                              | DQM7/PBS7            | AB5  |  |  |  |  |  |

| PSDA10                                 | )/PGPL0              | AE2  |  |  |  |  |  |

| PSDWE                                  | /PGPL1               | AD3  |  |  |  |  |  |

| POE/PSDF                               | AS/PGPL2             | AB4  |  |  |  |  |  |

| PSDCAS                                 | 5/PGPL3              | AC3  |  |  |  |  |  |

| PGTA/PUPM                              | WAIT/PGPL4           | AD2  |  |  |  |  |  |

| PSDAMU                                 | X/PGPL5              | AC2  |  |  |  |  |  |

| PCI_N                                  | 10DE <sup>1</sup>    | AD22 |  |  |  |  |  |

| PCI_CFG0 (P                            | CI_HOST_EN)          | AC21 |  |  |  |  |  |

| PCI_CFG1 (Ē                            | PCI_ARB_EN)          | AE22 |  |  |  |  |  |

| PCI_CFG2 (D                            | DLL_ENABLE)          | AE23 |  |  |  |  |  |

| PCI_                                   | PAR                  | AF12 |  |  |  |  |  |

| PCI_F                                  | RAME                 | AD15 |  |  |  |  |  |

| PCI_                                   | TRDY                 | AF16 |  |  |  |  |  |

**Document Revision History**