Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuils                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | 80C51                                                                        |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 40MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IDE/ATAPI, Memory Card, SPI, UART/USART, USB               |

| Peripherals                | Audio, I <sup>2</sup> S, MP3, PCM, POR, WDT                                  |

| Number of I/O              | 32                                                                           |

| Program Memory Size        | 64KB (64K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 2.25K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.3V                                                                  |

| Data Converters            | -                                                                            |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 100-TFBGA                                                                    |

| Supplier Device Package    | 100-CTBGA (9x9)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51snd2c-7ftul |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

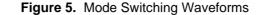

In order to prevent any incorrect operation while operating in X2 mode, user must be aware that all peripherals using clock frequency as time reference (timers, etc.) will have their time reference divided by 2. For example, a free running timer generating an interrupt every 20 ms will then generate an interrupt every 10 ms.

PLL

**PLL Description**

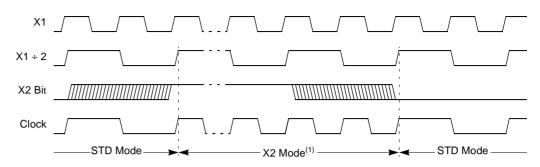

The AT8xC51SND2C PLL is used to generate internal high frequency clock (the PLL Clock) synchronized with an external low-frequency (the Oscillator Clock). The PLL clock provides the MP3 decoder, the audio interface, and the USB interface clocks. Figure 6 shows the internal structure of the PLL.

The PFLD block is the Phase Frequency Comparator and Lock Detector. This block makes the comparison between the reference clock coming from the N divider and the reverse clock coming from the R divider and generates some pulses on the Up or Down signal depending on the edge position of the reverse clock. The PLLEN bit in PLLCON register is used to enable the clock generation. When the PLL is locked, the bit PLOCK in PLLCON register (see Table 18) is set.

The CHP block is the Charge Pump that generates the voltage reference for the VCO by injecting or extracting charges from the external filter connected on PFILT pin (see Figure 7). Value of the filter components are detailed in the Section "DC Characteristics".

The VCO block is the Voltage Controlled Oscillator controlled by the voltage  $V_{ref}$  produced by the charge pump. It generates a square wave signal: the PLL clock.

Table 49. SFR Addresses and Reset Values

|     | 0/8                                | 1/9                                             | 2/A                  | 3/B                               | 4/C                  | 5/D                 | 6/E                  | 7/F                               | -   |

|-----|------------------------------------|-------------------------------------------------|----------------------|-----------------------------------|----------------------|---------------------|----------------------|-----------------------------------|-----|

| F8h | UEPINT<br>0000 0000                | DAT16H<br>XXXX XXXX                             |                      | NVERS<br>XXXX XXXX <sup>(2)</sup> |                      |                     |                      |                                   | FFh |

| F0h | B <sup>(1)</sup><br>0000 0000      |                                                 |                      |                                   |                      |                     |                      |                                   | F7h |

| E8h |                                    | PLLCON<br>0000 1000                             | USBCLK<br>0000 0000  | MP3CLK<br>0000 0000               | AUDCLK<br>0000 0000  | MMCLK<br>0000 0000  | PLLNDIV<br>0000 0000 | PLLRDIV<br>0000 0000              | EFh |

| E0h | ACC <sup>(1)</sup><br>0000 0000    |                                                 | UBYCTLX<br>0000 0000 |                                   | MMCON0<br>0000 0000  | MMCON1<br>0000 0000 | MMCON2<br>0000 0000  | MMINT<br>0000 0011                | E7h |

| D8h | P5 <sup>(1)</sup><br>XXXX 1111     |                                                 |                      |                                   | MMDAT<br>1111 1111   | MMCMD<br>1111 1111  | MMSTA<br>0000 0000   | MMMSK<br>1111 1111                | DFh |

| D0h | PSW <sup>(1)</sup><br>0000 0000    | FCON <sup>(3)</sup><br>1111 0000 <sup>(4)</sup> |                      |                                   | UEPCONX<br>1000 0000 | UEPRST<br>0000 0000 |                      |                                   | D7h |

| C8h | MP3STA <sup>(1)</sup><br>0000 0001 |                                                 |                      |                                   |                      |                     | UEPSTAX<br>0000 0000 | UEPDATX<br>XXXX XXXX              | CFh |

| C0h | P4 <sup>(1)</sup><br>1111 1111     |                                                 | UEPIEN<br>0000 0000  | SPCON<br>0001 0100                | SPSTA<br>0000 0000   | SPDAT<br>XXXX XXXX  | USBADDR<br>0000 0000 | UEPNUM<br>0000 0000               | C7h |

| B8h | IPL0 <sup>(1)</sup><br>X000 0000   | SADEN<br>0000 0000                              | UFNUML<br>0000 0000  | UFNUMH<br>0000 0000               | USBCON<br>0000 0000  | USBINT<br>0000 0000 | USBIEN<br>0001 0000  |                                   | BFh |

| B0h | P3 <sup>(1)</sup><br>1111 1111     | IEN1<br>0000 0000                               | IPL1<br>0000 0000    | IPH1<br>0000 0000                 | MP3BAS<br>0000 0000  | MP3MED<br>0000 0000 | MP3TRE<br>0000 0000  | IPH0<br>X000 0000                 | B7h |

| A8h | IEN0 <sup>(1)</sup><br>0000 0000   | SADDR<br>0000 0000                              | MP3CON<br>0011 1111  |                                   | MP3DAT<br>0000 0000  | MP3ANC<br>0000 0000 |                      | MP3STA1<br>0100 0001              | AFh |

| A0h | P2 <sup>(1)</sup><br>1111 1111     |                                                 | AUXR1<br>XXXX 00X0   | KBCON<br>0000 1111                | KBSTA<br>0000 0000   |                     | WDTRST<br>XXX XXXX   | WDTPRG<br>XXXX X000               | A7h |

| 98h | SCON<br>0000 0000                  | SBUF<br>XXXX XXXX                               | AUDCON0<br>0000 1000 | AUDCON1<br>1011 0010              | AUDSTA<br>1100 0000  | AUDDAT<br>1111 1111 | MP3VOL<br>0000 0000  | MP3VOR<br>0000 0000               | 9Fh |

| 90h | AUXCON <sup>(1)</sup><br>1111 1111 | BRL<br>0000 0000                                | BDRCON<br>XXX0 0000  | SSCON<br>0000 0000                | SSSTA<br>1111 1000   | SSDAT<br>1111 1111  | SSADR<br>1111 1110   |                                   | 97h |

| 88h | TCON <sup>(1)</sup><br>0000 0000   | TMOD<br>0000 0000                               | TL0<br>0000 0000     | TL1<br>0000 0000                  | TH0<br>0000 0000     | TH1<br>0000 0000    | AUXR<br>X000 1101    | CKCON<br>0000 000X <sup>(5)</sup> | 8Fh |

| 80h | P0 <sup>(1)</sup><br>1111 1111     | SP<br>0000 0111                                 | DPL<br>0000 0000     | DPH<br>0000 0000                  |                      |                     |                      | PCON<br>00XX 0000                 | 87h |

|     | 0/8                                | 1/9                                             | 2/A                  | 3/B                               | 4/C                  | 5/D                 | 6/E                  | 7/F                               | -   |

Notes: 1. SFR registers with least significant nibble address equal to 0 or 8 are bit-addressable.

NVERS reset value depends on the silicon version: 1000 0100 for AT89C51SND2C product and 0000 0001 for AT83SND2C product.

- 3. FCON register is only available in AT89C51SND2C product.

- 4. FCON reset value is 00h in case of reset with hardware condition.

- 5. CKCON reset value depends on the X2B bit (programmed or unprogrammed) in the Hardware Byte.

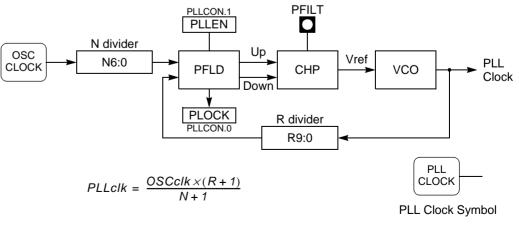

Figure 19. Interrupt Control System

## Table 55. IPH0 Register

IPH0 (S:B7h) – Interrupt Priority High Register 0

| 7             | 6               | 5                                   | 4                                                                                                 | 3                                        | 2      | 1 | 0 |  |  |  |  |

|---------------|-----------------|-------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------|--------|---|---|--|--|--|--|

| -             | IPHAUD          | IPHMP3 IPHS IPHT1 IPHX1 IPHT0 IPHX0 |                                                                                                   |                                          |        |   |   |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                         | Description                                                                                       |                                          |        |   |   |  |  |  |  |

| 7             | -               | Reserved<br>The value re            | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                   |                                          |        |   |   |  |  |  |  |

| 6             | IPHAUD          |                                     | Audio Interface Interrupt Priority Level MSB<br>Refer to Table 51 for priority level description. |                                          |        |   |   |  |  |  |  |

| 5             | IPHMP3          |                                     | MP3 Decoder Interrupt Priority Level MSB<br>Refer to Table 51 for priority level description.     |                                          |        |   |   |  |  |  |  |

| 4             | IPHS            |                                     | •                                                                                                 | <b>rity Level MS</b><br>ty level descri  |        |   |   |  |  |  |  |

| 3             | IPHT1           |                                     | rrupt Priority<br>le 51 for priori                                                                | <b>Level MSB</b><br>ty level descri      | ption. |   |   |  |  |  |  |

| 2             | IPHX1           |                                     |                                                                                                   | r <b>ity Level MS</b><br>ty level descri |        |   |   |  |  |  |  |

| 1             | IPHT0           |                                     | Timer 0 Interrupt Priority Level MSB<br>Refer to Table 51 for priority level description.         |                                          |        |   |   |  |  |  |  |

| 0             | IPHX0           |                                     | •                                                                                                 | r <b>ity Level MS</b><br>ty level descri |        |   |   |  |  |  |  |

Reset Value = X000 0000b

# Table 58. IPL1 RegisterIPL1 (S:B2h) – Interrupt Priority Low Register 1

| 7             | 6               | 5                               | 4                                                                                                     | 3                                       | 2              | 1      | 0      |  |  |  |  |

|---------------|-----------------|---------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------|--------|--------|--|--|--|--|

| -             | IPLUSB          | -                               | IPLKB                                                                                                 | -                                       | IPLSPI         | IPLI2C | IPLMMC |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                     | Description                                                                                           |                                         |                |        |        |  |  |  |  |

| 7             | -               | Reserved<br>The value re        | Reserved<br>The value read from this bit is always 0. Do not set this bit.                            |                                         |                |        |        |  |  |  |  |

| 6             | IPLUSB          |                                 | JSB Interrupt Priority Level LSB<br>Refer to Table 51 for priority level description.                 |                                         |                |        |        |  |  |  |  |

| 5             | -               | <b>Reserved</b><br>The value re | Reserved<br>The value read from this bit is always 0. Do not set this bit.                            |                                         |                |        |        |  |  |  |  |

| 4             | IPLKB           | -                               | •                                                                                                     | <b>ity Level LSB</b><br>ty level descri |                |        |        |  |  |  |  |

| 3             | -               | <b>Reserved</b><br>The value re | ad from this b                                                                                        | it is always 0.                         | Do not set thi | s bit. |        |  |  |  |  |

| 2             | IPLSPI          |                                 | et Priority Lev<br>le 51 for priori                                                                   | <b>vel LSB</b><br>ty level descri       | ption.         |        |        |  |  |  |  |

| 1             | IPLI2C          |                                 | Two Wire Controller Interrupt Priority Level LSB<br>Refer to Table 51 for priority level description. |                                         |                |        |        |  |  |  |  |

| 0             | IPLMMC          |                                 | u <b>pt Priority L</b> o<br>le 51 for priori                                                          | e <b>vel LSB</b><br>ty level descri     | ption.         |        |        |  |  |  |  |

Reset Value = 0000 0000b

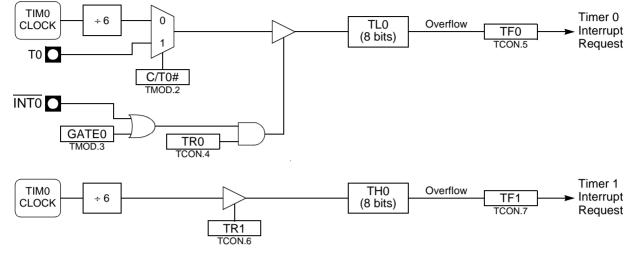

3. Figure 32 gives the autoreload period calculation formulas for both TF0 and TF1 flags.

Figure 33. Timer/Counter 0 in Mode 3: 2 8-bit Counters

#### Figure 34. Mode 3 Overflow Period Formula

$$TF0_{PER} = \frac{6 \cdot (256 - TL0)}{F_{TIM0}} \qquad TF1_{PER} = \frac{6 \cdot (256 - TH0)}{F_{TIM0}}$$

Timer 1

Timer 1 is identical to Timer 0 except for Mode 3 which is a hold-count mode. The following comments help to understand the differences:

- Timer 1 functions as either a Timer or event Counter in three modes of operation.

Figure 27 through Figure 31 show the logical configuration for modes 0, 1, and 2.

Timer 1's mode 3 is a hold-count mode.

- Timer 1 is controlled by the four high-order bits of TMOD register (see Figure 63) and bits 2, 3, 6 and 7 of TCON register (see Figure 62). TMOD register selects the method of Timer gating (GATE1), Timer or Counter operation (C/T1#) and mode of operation (M11 and M01). TCON register provides Timer 1 control functions: overflow flag (TF1), run control bit (TR1), interrupt flag (IE1) and interrupt type control bit (IT1).

- Timer 1 can serve as the Baud Rate Generator for the Serial Port. Mode 2 is best suited for this purpose.

- For normal Timer operation (GATE1 = 0), setting TR1 allows TL1 to be incremented by the selected input. Setting GATE1 and TR1 allows external pin INT1 to control Timer operation.

- Timer 1 overflow (count rolls over from all 1s to all 0s) sets the TF1 flag generating an interrupt request.

- When Timer 0 is in mode 3, it uses Timer 1's overflow flag (TF1) and run control bit (TR1). For this situation, use Timer 1 only for applications that do not require an interrupt (such as a Baud Rate Generator for the Serial Port) and switch Timer 1 in and out of mode 3 to turn it off and on.

- It is important to stop the Timer/Counter before changing modes.

| Table 102. | Dac Control Register Register - DAC_CTRL (0 | )0h) |

|------------|---------------------------------------------|------|

|            |                                             |      |

| 7             | 6               | 5                         | 4                                                                                    | 3                        | 2      | 1      | 0      |  |  |

|---------------|-----------------|---------------------------|--------------------------------------------------------------------------------------|--------------------------|--------|--------|--------|--|--|

| ONPADRV       | ONAUXIN         | ONDACR                    | ONDACL                                                                               | ONLNOR                   | ONLNOL | ONLNIR | ONLNIL |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Descript                  | ion                                                                                  |                          |        |        |        |  |  |

| 7             | ONPADRV         |                           | l mono PA driv<br>ower down. Se                                                      | ver<br>et to power up    |        |        |        |  |  |

| 6             | ONAUXIN         |                           | Differential mono auxiliary input amplifier<br>Clear to power down. Set to power up. |                          |        |        |        |  |  |

| 5             | ONDACR          | Ũ                         | Right channel DAC<br>Clear to power down. Set to power up.                           |                          |        |        |        |  |  |

| 4             | ONDACL          | Left chann<br>Clear to po |                                                                                      | et to power up.          |        |        |        |  |  |

| 3             | ONLNOR          | Ũ                         | inel line out di<br>ower down. Se                                                    | river<br>et to power up. |        |        |        |  |  |

| 2             | ONLNOL          |                           | Left channel line out driver<br>Clear to power down. Set to power up.                |                          |        |        |        |  |  |

| 1             | ONLNIR          | J                         | Right channel line in amplifier<br>Clear to power down. Set to power up.             |                          |        |        |        |  |  |

| 0             | ONLNIL          |                           | el line in amp<br>ower down. Se                                                      | lifier<br>et to power up |        |        |        |  |  |

Reset Value = 0000000b

## Table 103. DAC Left Line In Gain Register - DAC\_LLIG (01h)

| 7             | 6               | 5        | 4                                         | 3     | 2     | 1     | 0     |  |  |  |

|---------------|-----------------|----------|-------------------------------------------|-------|-------|-------|-------|--|--|--|

| -             | -               | -        | LLIG4                                     | LLIG3 | LLIG2 | LLIG1 | LLIG0 |  |  |  |

| Bit<br>Number | Bit<br>Mnemonie |          | Description                               |       |       |       |       |  |  |  |

| 7:5           | -               | Not use  | Not used                                  |       |       |       |       |  |  |  |

| 4:0           | LLIG 4:0        | Left cha | Left channel line in analog gain selector |       |       |       |       |  |  |  |

Reset Value = 00000101b

## Register

## Table 119. PA Control Register - PA\_CTRL (11h)I

| 7                          |            | 6    | 5          |                                     | 4            | 3            | 2        | 1        | 0        |  |

|----------------------------|------------|------|------------|-------------------------------------|--------------|--------------|----------|----------|----------|--|

| -                          | - APAON AF |      | APAPR<br>H | EC                                  | APALP        | APAGAIN3     | APAGAIN2 | APAGAIN1 | APAGAIN0 |  |

| Bit<br>Number Bit Mnemonic |            |      | emonic     | Des                                 | cription     |              |          |          |          |  |

| 7                          | -          |      |            | Not used                            |              |              |          |          |          |  |

| 6                          |            | AP   | AON        | Audio power amplifier on bit        |              |              |          |          |          |  |

| 5                          | 5 APAPRECH |      |            | Audio power amplifier precharge bit |              |              |          |          |          |  |

| 4                          |            | AP   | ALP        | Audio power amplifier low power bit |              |              |          |          |          |  |

| 3:0                        |            | APAG | AIN3:0     | Aud                                 | io power amp | olifier gain |          |          |          |  |

Reset Value = 0000000b

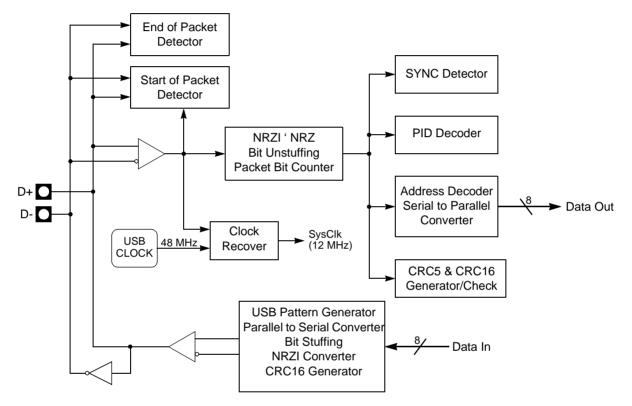

#### Serial Interface Engine (SIE)

The SIE performs the following functions:

- NRZI data encoding and decoding.

- Bit stuffing and unstuffing.

- CRC generation and checking.

- ACKs and NACKs automatic generation.

- TOKEN type identifying.

- Address checking.

- Clock recovery (using DPLL).

Table 126. UEPCONX Register

UEPCONX (S:D4h) – USB Endpoint X Control Register (X = EPNUM set in UEPNUM)

| 7             | 6               | 5                                                       | 4                                                                                                                                                                                                                                                                                         | 3                                                       | 2              | 1             | 0            |  |  |  |

|---------------|-----------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------|---------------|--------------|--|--|--|

| EPEN          | NAKIEN          | NAKOUT                                                  | NAKIN                                                                                                                                                                                                                                                                                     | DTGL                                                    | EPDIR          | EPTYPE1       | EPTYPE0      |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                             |                                                                                                                                                                                                                                                                                           |                                                         |                |               |              |  |  |  |

| 7             | EPEN            | Set to enabl<br>should alway<br>the device co           | Endpoint Enable Bit<br>Set to enable the endpoint according to the device configuration. Endpoint 0<br>should always be enabled after a hardware or USB bus reset and participate in<br>the device configuration.<br>Clear to disable the endpoint according to the device configuration. |                                                         |                |               |              |  |  |  |

| 6             | NAKIEN          | Set this bit to                                         | NAK Interrupt enable<br>Set this bit to enable NAK IN or NAK OUT interrupt.<br>Clear this bit to disable NAK IN or NAK OUT Interrupt.                                                                                                                                                     |                                                         |                |               |              |  |  |  |

| 5             | NAKOUT          | This bit is se<br>of a OUT red<br>set.                  | NAK OUT received<br>This bit is set by hardware when an NAK handshake has been sent in response<br>of a OUT request from the Host. This triggers a USB interrupt when NAKIEN is<br>set.<br>This bit should be cleared by software.                                                        |                                                         |                |               |              |  |  |  |

| 4             | NAKIN           | of a IN reque                                           | t by hardware                                                                                                                                                                                                                                                                             | e when an NA<br>ost. This trigg<br>by software.         |                |               |              |  |  |  |

| 3             | DTGL            | Set by hardw                                            |                                                                                                                                                                                                                                                                                           | <b>Read-only)</b><br>DATA1 packet<br>n a DATA0 pac      |                | ed.           |              |  |  |  |

| 2             | EPDIR           | Clear to conf                                           | ure IN directio                                                                                                                                                                                                                                                                           | on for Bulk, Int<br>rection for Bull<br>Control endpoir | , Interrupt an |               |              |  |  |  |

| 1-0           | EPTYPE1:0       | be configured<br>00 Control<br>01 Isochro<br>10 Bulk en | according to<br>d as Control):<br>endpoint<br>nous endpoin                                                                                                                                                                                                                                |                                                         | configuration  | (Endpoint 0 s | hould always |  |  |  |

Reset Value = 1000 0000b

#### Table 127. UEPSTAX Register

UEPSTAX (S:CEh) – USB Endpoint X Status and Control Register (X = EPNUM set in UEPNUM)

| 7             | 6               | 5                                                                              | 4                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3                                                                                                             | 2                                                          | 1                                                                | 0                                                              |  |  |  |

|---------------|-----------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------|--|--|--|

| DIR           | RXOUTB1         | STALLRQ                                                                        | TXRDY                                                                                                                                                                                                                                                                                                                                                                                                                             | STLCRC                                                                                                        | RXSETUP                                                    | RXOUTB0                                                          | ТХСМР                                                          |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                               |                                                            |                                                                  |                                                                |  |  |  |

| 7             | DIR             | This bit is rele<br>Set for the da<br>Note: This bit<br>changed. Thi           | Control Endpoint Direction Bit<br>This bit is relevant only if the endpoint is configured in Control type.<br>Set for the data stage. Clear otherwise.<br>Note: This bit should be configured on RXSETUP interrupt before any other bit is<br>changed. This also determines the status phase (IN for a control write and OUT<br>for a control read). This bit should be cleared for status stage of a Control Out<br>transaction. |                                                                                                               |                                                            |                                                                  |                                                                |  |  |  |

| 6             | RXOUTB1         | This bit is se<br>FIFO data b<br>triggered if en<br>rejected (NA<br>Endpoints. | t by hardward<br>ank 1 (only<br>nabled and al<br>K'ed) until th<br>Ild be cleared                                                                                                                                                                                                                                                                                                                                                 | <b>c 1 for Endpo</b><br>e after a new<br>in Ping-pong<br>I the following<br>his bit has be<br>d by the device | packet has b<br>mode). Then<br>OUT packets<br>een cleared, | een stored in<br>, the endpoin<br>to the endpoin<br>excepted for | the endpoint<br>t interrupt is<br>nt bank 1 are<br>Isochronous |  |  |  |

| Bit Position | 47        | 46                  | [45:40]  | [39:8]          | [7:1]     | 0       |

|--------------|-----------|---------------------|----------|-----------------|-----------|---------|

| Width (bits) | 1         | 1                   | 6        | 32              | 7         | 1       |

| Value        | '0'       | ʻ0'                 | '111111' | -               | '1111111' | '1'     |

| Description  | Start bit | Transmission<br>bit | Reserved | OCR<br>register | Reserved  | End bit |

Table 141. R3 Response Format (OCR Register)

#### Table 142. R4 Response Format (Fast I/O)

| Bit Position | 47        | 46                  | [45:40]          | [39:8]   | [7:1] | 0       |

|--------------|-----------|---------------------|------------------|----------|-------|---------|

| Width (bits) | 1         | 1                   | 6                | 32       | 7     | 1       |

| Value        | '0'       | '0'                 | '100111'         | -        | -     | '1'     |

| Description  | Start bit | Transmission<br>bit | Command<br>Index | Argument | CRC7  | End bit |

Table 143. R5 Response Format

| Bit Position | 47        | 46                  | [45:40]          | [39:8]   | [7:1] | 0       |

|--------------|-----------|---------------------|------------------|----------|-------|---------|

| Width (bits) | 1         | 1                   | 6                | 32       | 7     | 1       |

| Value        | '0'       | '0'                 | '101000'         | -        | -     | '1'     |

| Description  | Start bit | Transmission<br>bit | Command<br>Index | Argument | CRC7  | End bit |

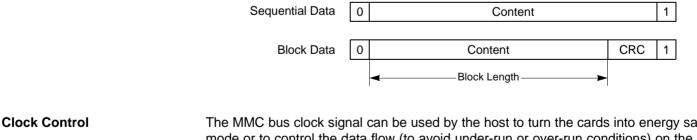

#### **Data Packet Format**

There are 2 types of data packets: stream and block. As shown in Figure 89, stream data packets have an indeterminate length while block packets have a fixed length depending on the block length. Each data packet is preceded by a Start bit: a low level on MCMD line and succeeded by an End bit: a high level on MCMD line. Due to the fact that there is no predefined end in stream packets, CRC protection is not included in this case. The CRC protection algorithm for block data is a 16-bit CCITT polynomial.

#### Figure 89. Data Token Format

The MMC bus clock signal can be used by the host to turn the cards into energy saving mode or to control the data flow (to avoid under-run or over-run conditions) on the bus. The host is allowed to lower the clock frequency or shut it down. There are a few restrictions the host must follow:

- The bus frequency can be changed at any time (under the restrictions of maximum data transfer frequency, defined by the cards, and the identification frequency defined by the specification document).

- It is an obvious requirement that the clock must be running for the card to output data or response tokens. After the last MultiMedia Card bus transaction, the host is

This time-out may be disarmed after receiving 8 data (F1FI flag set) or after receiving end of frame (EOFI flag set) in case of block length less than 8 data (1, 2 or 4).

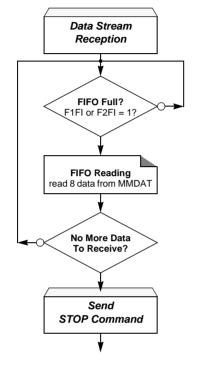

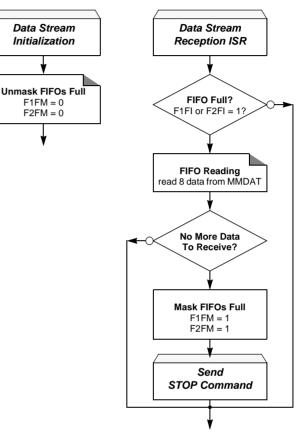

Data Reading

Data is read from the FIFO by reading to MMDAT register. Each time one FIFO becomes full (F1FI or F2FI set), user is requested to flush this FIFO by reading 8 data.

a. Polling mode

b. Interrupt mode

#### Table 152. MMDAT Register

MMDAT (S:DCh) – MMC Data Register

| 7             | 6               | 5                           | 4   | 3                | 2             | 1   | 0   |

|---------------|-----------------|-----------------------------|-----|------------------|---------------|-----|-----|

| MD7           | MD6             | MD5                         | MD4 | MD3              | MD2           | MD1 | MD0 |

| Bit<br>Number | Bit<br>Mnemonic | Description                 |     |                  |               |     |     |

| 7 - 0         | MD7:0           | MMC Data B<br>Input (write) |     | d) register of t | he data FIFO. |     |     |

Reset Value = 1111 1111b

### Table 153. MMCLK Register

MMCLK (S:EDh) – MMC Clock Divider Register

| 7             | 6               | 5                                                            | 4     | 3     | 2     | 1     | 0     |

|---------------|-----------------|--------------------------------------------------------------|-------|-------|-------|-------|-------|

| MMCD7         | MMCD6           | MMCD5                                                        | MMCD4 | MMCD3 | MMCD2 | MMCD1 | MMCD0 |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                  |       |       |       |       |       |

| 7 - 0         | MMCD7:0         | MMC Clock Divider<br>8-bit divider for MMC clock generation. |       |       |       |       |       |

Reset Value = 0000 0000b

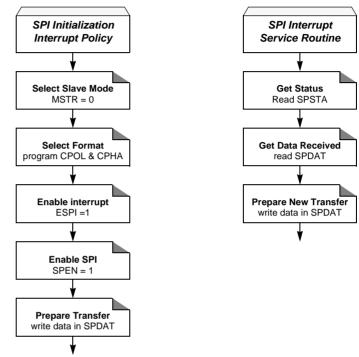

Slave Mode with Interrupt Policy

Figure 111 shows the initialization phase and the transfer phase flows using the interrupt.

The transfer format depends on the master controller.

Reading SPSTA at the beginning of the ISR is mandatory for clearing the SPIF flag. Clear is effective when reading SPDAT.

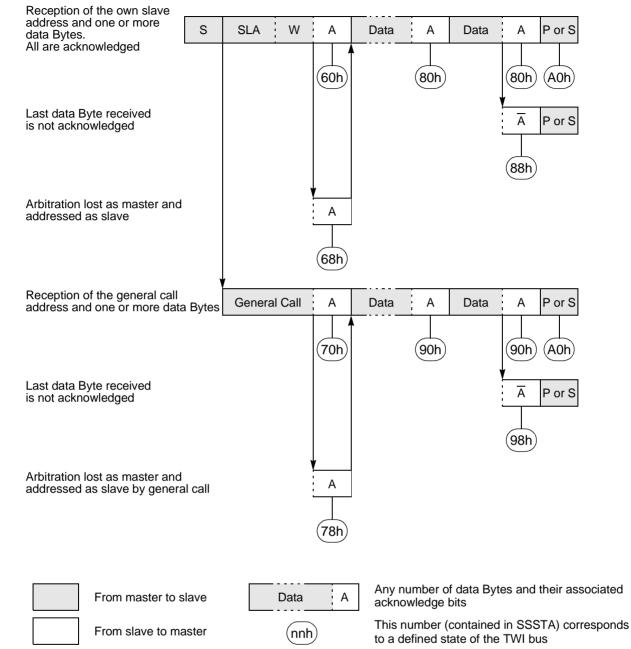

#### Figure 135. Format and States in the Slave Receiver Mode

## Registers

# Table 173.AUXCON RegisterAUXCON (S:90h) – Auxiliary Control Register

| 7             | 6              | 5                   | 4                                                                                                                                                                                                            | 3       | 2       | 1      | 0    |

|---------------|----------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|--------|------|

| SDA           | SCL            | -                   | AUDCDOUT                                                                                                                                                                                                     | AUDCDIN | AUDCCLK | AUDCCS | KIN0 |

| Bit<br>Number | Bit<br>Mnemoni | c Descriptio        | Description                                                                                                                                                                                                  |         |         |        |      |

| 7             | SDA            |                     | <b>TWI Serial Data</b><br>SDA is the bidirectional Two Wire data line.                                                                                                                                       |         |         |        |      |

| 6             | SCL            | When TW slave perip | <b>TWI Serial Clock</b><br>When TWI controller is in master mode, SCL outputs the serial clock to the slave peripherals. When TWI controller is in slave mode, SCL receives clock rom the master controller. |         |         |        |      |

| 5:1           |                |                     | Audio DAC Control<br>Refer to Audio DAC interface section                                                                                                                                                    |         |         |        |      |

| 0             | KIN0           | Keyboard            | Keyboard Input Line                                                                                                                                                                                          |         |         |        |      |

Reset Value = 1111 1111b

### Table 174. SSCON Register

SSCON (S:93h) – Synchronous Serial Control Register

| 7     | 6    | 5     | 4     | 3   | 2    | 1     | 0     |

|-------|------|-------|-------|-----|------|-------|-------|

| SSCR2 | SSPE | SSSTA | SSSTO | SSI | SSAA | SSCR1 | SSCR0 |

#### Timings

Test conditions: capacitive load on all pins= 50 pF.

### Table 194. External IDE 16-bit Bus Cycle - Data Read AC Timings

## $V_{DD}$ = 2.7 to 3.3 V, $T_A$ = -40 to +85°C

|                   |                                 |                         | e Clock<br>rd Mode      |                           | e Clock<br>Iode           |      |

|-------------------|---------------------------------|-------------------------|-------------------------|---------------------------|---------------------------|------|

| Symbol            | Parameter                       | Min                     | Max                     | Min                       | Max                       | Unit |

| T <sub>CLCL</sub> | Clock Period                    | 50                      |                         | 50                        |                           | ns   |

| T <sub>LHLL</sub> | ALE Pulse Width                 | 2·T <sub>CLCL</sub> -15 |                         | T <sub>CLCL</sub> -15     |                           | ns   |

| T <sub>AVLL</sub> | Address Valid to ALE Low        | T <sub>CLCL</sub> -20   |                         | 0.5·T <sub>CLCL</sub> -20 |                           | ns   |

| T <sub>LLAX</sub> | Address hold after ALE Low      | T <sub>CLCL</sub> -20   |                         | 0.5·T <sub>CLCL</sub> -20 |                           | ns   |

| T <sub>LLRL</sub> | ALE Low to RD Low               | 3-T <sub>CLCL</sub> -30 |                         | 1.5·T <sub>CLCL</sub> -30 |                           | ns   |

| T <sub>RLRH</sub> | RD Pulse Width                  | 6·T <sub>CLCL</sub> -25 |                         | 3·T <sub>CLCL</sub> -25   |                           | ns   |

| T <sub>RHLH</sub> | RD high to ALE High             | T <sub>CLCL</sub> -20   | T <sub>CLCL</sub> +20   | 0.5·T <sub>CLCL</sub> -20 | 0.5·T <sub>CLCL</sub> +20 | ns   |

| T <sub>AVDV</sub> | Address Valid to Valid Data In  |                         | 9.T <sub>CLCL</sub> -65 |                           | 4.5·T <sub>CLCL</sub> -65 | ns   |

| T <sub>AVRL</sub> | Address Valid to RD Low         | 4-T <sub>CLCL</sub> -30 |                         | 2·T <sub>CLCL</sub> -30   |                           | ns   |

| T <sub>RLDV</sub> | RD Low to Valid Data            |                         | 5·T <sub>CLCL</sub> -30 |                           | 2.5·T <sub>CLCL</sub> -30 | ns   |

| T <sub>RLAZ</sub> | RD Low to Address Float         |                         | 0                       |                           | 0                         | ns   |

| T <sub>RHDX</sub> | Data Hold After RD High         | 0                       |                         | 0                         |                           | ns   |

| T <sub>RHDZ</sub> | Instruction Float After RD High |                         | 2·T <sub>CLCL</sub> -25 |                           | T <sub>CLCL</sub> -25     | ns   |

#### Table 195. External IDE 16-bit Bus Cycle - Data Write AC Timings

## $V_{DD}$ = 2.7 to 3.3 V, $T_A$ = -40 to +85°C

|                   |                            |                         | Variable Clock<br>Standard Mode |                           | Variable Clock<br>X2 Mode |      |  |

|-------------------|----------------------------|-------------------------|---------------------------------|---------------------------|---------------------------|------|--|

| Symbol            | Parameter                  | Min                     | Max                             | Min                       | Max                       | Unit |  |

| T <sub>CLCL</sub> | Clock Period               | 50                      |                                 | 50                        |                           | ns   |  |

| T <sub>LHLL</sub> | ALE Pulse Width            | 2.T <sub>CLCL</sub> -15 |                                 | T <sub>CLCL</sub> -15     |                           | ns   |  |

| T <sub>AVLL</sub> | Address Valid to ALE Low   | T <sub>CLCL</sub> -20   |                                 | 0.5·T <sub>CLCL</sub> -20 |                           | ns   |  |

| T <sub>LLAX</sub> | Address hold after ALE Low | T <sub>CLCL</sub> -20   |                                 | 0.5·T <sub>CLCL</sub> -20 |                           | ns   |  |

| T <sub>LLWL</sub> | ALE Low to WR Low          | 3.T <sub>CLCL</sub> -30 |                                 | 1.5·T <sub>CLCL</sub> -30 |                           | ns   |  |

| T <sub>WLWH</sub> | WR Pulse Width             | 6∙T <sub>CLCL</sub> -25 |                                 | 3.T <sub>CLCL</sub> -25   |                           | ns   |  |

| T <sub>WHLH</sub> | WR High to ALE High        | T <sub>CLCL</sub> -20   | T <sub>CLCL</sub> +20           | 0.5·T <sub>CLCL</sub> -20 | 0.5·T <sub>CLCL</sub> +20 | ns   |  |

| T <sub>AVWL</sub> | Address Valid to WR Low    | 4.T <sub>CLCL</sub> -30 |                                 | 2·T <sub>CLCL</sub> -30   |                           | ns   |  |

| T <sub>QVWH</sub> | Data Valid to WR High      | 7.T <sub>CLCL</sub> -20 |                                 | 3.5·T <sub>CLCL</sub> -20 |                           | ns   |  |

| T <sub>WHQX</sub> | Data Hold after WR High    | T <sub>CLCL</sub> -15   |                                 | 0.5·T <sub>CLCL</sub> -15 |                           | ns   |  |

#### **Flash Memory**

#### Definition of symbols

#### Table 203. Flash Memory Timing Symbol Definitions

| Signals |            |  |  |

|---------|------------|--|--|

| S       | ISP        |  |  |

| R       | RST        |  |  |

| В       | FBUSY flag |  |  |

| Conditions |                 |  |  |  |

|------------|-----------------|--|--|--|

| L          | Low             |  |  |  |

| V          | Valid           |  |  |  |

| х          | No Longer Valid |  |  |  |

#### Timings

#### Table 204. Flash Memory AC Timing

### $V_{DD}$ = 2.7 to 3.3 V, $T_A$ = -40 to +85°C

| Symbol            | Parameter                              | Min  | Тур | Max | Unit  |

|-------------------|----------------------------------------|------|-----|-----|-------|

| T <sub>SVRL</sub> | Input ISP Valid to RST Edge            | 50   |     |     | ns    |

| T <sub>RLSX</sub> | Input ISP Hold after RST Edge          | 50   |     |     | ns    |

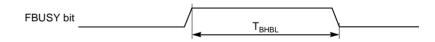

| T <sub>BHBL</sub> | FLASH Internal Busy (Programming) Time |      | 10  |     | ms    |

| N <sub>FCY</sub>  | Number of Flash Write Cycles           | 100K |     |     | Cycle |

| T <sub>FDR</sub>  | Flash Data Retention Time              | 10   |     |     | Years |

#### Waveforms

#### Figure 165. FLASH Memory - ISP Waveforms

Note: 1. ISP must be driven through a pull-down resistor (see Section "In System Programming", page 212).

#### Figure 166. FLASH Memory - Internal Busy Waveforms

#### **External Clock Drive and Logic Level References**

#### Definition of symbols

#### Table 205. External Clock Timing Symbol Definitions

| Signals |       |  |  |

|---------|-------|--|--|

| С       | Clock |  |  |

| Conditions |                 |  |  |  |

|------------|-----------------|--|--|--|

| н          | High            |  |  |  |

| L          | Low             |  |  |  |

| х          | No Longer Valid |  |  |  |

#### Timings

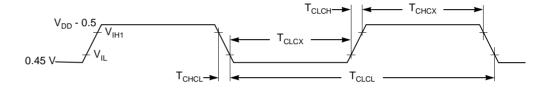

Table 206. External Clock AC Timings

# 226 AT8xC51SND2C

### $V_{DD}$ = 2.7 to 3.3 V, $T_A$ = -40 to +85°C

| Symbol            | Parameter               | Min | Max | Unit |

|-------------------|-------------------------|-----|-----|------|

| T <sub>CLCL</sub> | Clock Period            | 50  |     | ns   |

| T <sub>CHCX</sub> | High Time               | 10  |     | ns   |

| T <sub>CLCX</sub> | Low Time                | 10  |     | ns   |

| T <sub>CLCH</sub> | Rise Time               | 3   |     | ns   |

| T <sub>CHCL</sub> | Fall Time               | 3   |     | ns   |

| T <sub>CR</sub>   | Cyclic Ratio in X2 mode | 40  | 60  | %    |

#### Waveforms

#### Figure 167. External Clock Waveform

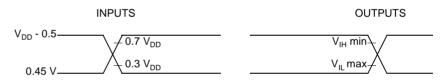

#### Figure 168. AC Testing Input/Output Waveforms

- Note: 1. During AC testing, all inputs are driven at  $V_{\text{DD}}$  -0.5 V for a logic 1 and 0.45 V for a logic 0.

- Timing measurements are made on all outputs at V<sub>IH</sub> min for a logic 1 and V<sub>IL</sub> max for a logic 0.

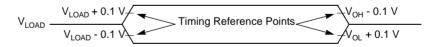

- Figure 169. Float Waveforms

Note: For timing purposes, a port pin is no longer floating when a 100 mV change from load voltage occurs and begins to float when a 100 mV change from the loading  $V_{OH}/V_{OL}$  level occurs with  $I_{OL}/I_{OH}$  = ±20 mA.