Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f15355-e-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

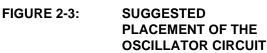

# 2.5 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to Section 9.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-3. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins, and other signals in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times, and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

# 2.6 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

# TABLE 4-5:PIC16(L)F15354/55 MEMORY MAP, BANKS 8-15

|      | BANK 8                  |      | BANK 9                  |      | BANK 10                 |      | BANK 11                 |      | BANK 12                 |      | BANK 13       |      | BANK 14       |      | BANK 15       |

|------|-------------------------|------|-------------------------|------|-------------------------|------|-------------------------|------|-------------------------|------|---------------|------|---------------|------|---------------|

| 400h |                         | 480h |                         | 500h |                         | 580h |                         | 600h |                         | 680h |               | 700h |               | 780h |               |

|      | Core Register           |      | Core Register |      | Core Register |      | Core Register |

|      | (Table 4-3)             |      | (Table 4-3)   |      | (Table 4-3)   |      | (Table 4-3)   |

| 40Bh |                         | 48Bh |                         | 50Bh |                         | 58Bh |                         | 60Bh |                         | 68Bh |               | 70Bh |               | 78Bh |               |

| 40Ch | —                       | 48Ch | —                       | 50Ch | —                       | 58Ch | NCO1ACCL                | 60Ch | CWG1CLK                 | 68Ch | —             | 70Ch | PIR0          | 78Ch |               |

| 40Dh | _                       | 48Dh | _                       | 50Dh | _                       | 58Dh | NCO1ACCH                | 60Dh | CWG1DAT                 | 68Dh |               | 70Dh | PIR1          | 78Dh |               |

| 40Eh | _                       | 48Eh | _                       | 50Eh | —                       | 58Eh | NCO1ACCU                | 60Eh | CWG1DBR                 | 68Eh | _             | 70Eh | PIR2          | 78Eh |               |

| 40Fh | _                       | 48Fh | _                       | 50Fh | —                       | 58Fh | NCO1INCL                | 60Fh | CWG1DBF                 | 68Fh | _             | 70Fh | PIR3          | 78Fh |               |

| 410h | —                       | 490h | —                       | 510h | —                       | 590h | NCO1INCH                | 610h | CWG1CON0                | 690h | _             | 710h | PIR4          | 790h | _             |

| 411h | —                       | 491h | _                       | 511h | —                       | 591h | NCO1INCU                | 611h | CWG1CON1                | 691h | _             | 711h | PIR5          | 791h | _             |

| 412h | —                       | 492h | —                       | 512h | —                       | 592h | NCO1CON                 | 612h | CWG1AS0                 | 692h | —             | 712h | PIR6          | 792h | _             |

| 413h | —                       | 493h | —                       | 513h | —                       | 593h | NCO1CLK                 | 613h | CWG1AS1                 | 693h | —             | 713h | PIR7          | 793h | —             |

| 414h | —                       | 494h | —                       | 514h | —                       | 594h | —                       | 614h | CWG1STR                 | 694h | _             | 714h | _             | 794h | —             |

| 415h | —                       | 495h | —                       | 515h | —                       | 595h | _                       | 615h | —                       | 695h | _             | 715h | —             | 795h | _             |

| 416h | —                       | 496h | _                       | 516h | —                       | 596h | _                       | 616h | —                       | 696h | _             | 716h | PIE0          | 796h | PMD0          |

| 417h | —                       | 497h | _                       | 517h | —                       | 597h | _                       | 617h | —                       | 697h | _             | 717h | PIE1          | 797h | PMD1          |

| 418h | _                       | 498h | _                       | 518h | _                       | 598h | _                       | 618h | _                       | 698h | _             | 718h | PIE2          | 798h | PMD2          |

| 419h | _                       | 499h | _                       | 519h | _                       | 599h | _                       | 619h | _                       | 699h | _             | 719h | PIE3          | 799h | PMD3          |

| 41Ah | —                       | 49Ah | _                       | 51Ah | —                       | 59Ah |                         | 61Ah | —                       | 69Ah | _             | 71Ah | PIE4          | 79Ah | PMD4          |

| 41Bh | _                       | 49Bh | _                       | 51Bh | _                       | 59Bh | _                       | 61Bh | _                       | 69Bh |               | 71Bh | PIE5          | 79Bh | PMD5          |

| 41Ch |                         | 49Ch | _                       | 51Ch | _                       | 59Ch | TMR0                    | 61Ch | _                       | 69Ch | _             | 71Ch | PIE6          | 79Ch |               |

| 41Dh |                         | 49Dh | _                       | 51Dh | _                       | 59Dh | PR0                     | 61Dh | _                       | 69Dh | _             | 71Dh | PIE7          | 79Dh |               |

| 41Eh |                         | 49Eh | _                       | 51Eh | _                       | 59Eh | TMR0CON0                | 61Eh | _                       | 69Eh | _             | 71Eh | —             | 79Eh |               |

| 41Fh | —                       | 49Fh | —                       | 51Fh | —                       | 59Fh | TMR0CON1                | 61Fh | —                       | 69Fh | —             | 71Fh | —             | 79Fh | _             |

| 420h |                         | 4A0h |                         | 520h |                         | 5A0h |                         | 620h |                         | 6A0h |               | 720h |               | 7A0h |               |

|      | General                 |      |               |      |               |      |               |

|      | Purpose                 |      | Unimplemented |      | Unimplemented |      | Unimplemented |

|      | Register                |      | Read as '0'   |      | Read as '0'   |      | Read as '0'   |

|      | 80 Bytes <sup>(2)</sup> |      |               |      |               |      |               |

| 46Fh |                         | 4EFh |                         | 56Fh |                         | 5EFh |                         | 66Fh |                         | 6EFh |               | 76Fh |               | 7EFh |               |

| 470h | Common RAM              | 4F0h | Common RAM              | 570h | Common RAM              | 5F0h | Common RAM              | 670h | Common RAM              | 6F0h | Common RAM    | 770h | Common RAM    | 7F0h | Common RAM    |

|      | Accesses                |      | Accesses      |      | Accesses      |      | Accesses      |

| 47Fh | 70h-7Fh                 | 4FFh | 70h-7Fh                 | 57Fh | 70h-7Fh                 | 5FFh | 70h-7Fh                 | 67Fh | 70h-7Fh                 | 6FFh | 70h-7Fh       | 77Fh | 70h-7Fh       | 7FFh | 70h-7Fh       |

Note 1: Unimplemented locations read as '0'.

2: Present only in PIC16(L)F15355.

# 5.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Program memory protection and data memory are controlled independently. Internal access to the program memory is unaffected by any code protection setting.

#### 5.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Self-writing the program memory is dependent upon the write protection setting. See **Section 5.4** "Write **Protection**" for more information.

# 5.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as boot loader software, can be protected while allowing other regions of the program memory to be modified.

The WRTAPP, WRTSAF, WRTB, WRTC bits in Configuration Words (Register 5-4) define whether the corresponding region of the program memory block is protected or not.

## 5.5 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See Section 13.3.6 "NVMREG Access to Device Information Area, Device Configuration Area, User ID, Device ID and Configuration Words" for more information on accessing these memory locations. For more information on checksum calculation, see the "PIC16(L)F153xx Memory Programming Specification" (DS40001838).

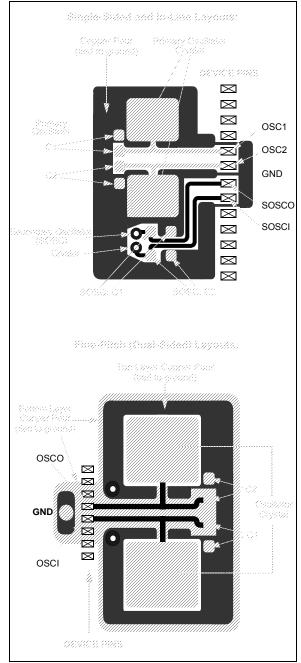

## 9.4 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM is enabled by setting the FCMEN bit in the Configuration Words. The FSCM is applicable to all external Oscillator modes (LP, XT, HS, ECL, ECM, ECH and Secondary Oscillator).

## 9.4.1 FAIL-SAFE DETECTION

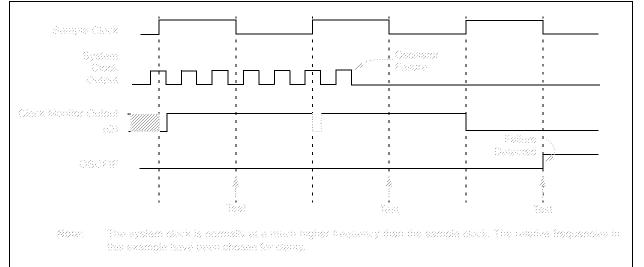

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64. See Figure 9-9. Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the external clock goes low.

FIGURE 9-10: FSCM TIMING DIAGRAM

## 9.4.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM switches the device clock to the HFINTOSC at 1 MHz clock frequency and sets the bit flag OSFIF of the PIR1 register. Setting this flag will generate an interrupt if the OSFIE bit of the PIE1 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation, by writing to the NOSC and NDIV bits of the OSCCON1 register.

#### 9.4.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or changing the NOSC and NDIV bits of the OSCCON1 register. When switching to the external oscillator, or external oscillator and PLL, the OST is restarted. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON1. When the OST times out, the Fail-Safe condition is cleared after successfully switching to the external clock source. The OSFIF bit should be cleared prior to switching to the external clock source. If the Fail-Safe condition still exists, the OSFIF flag will again become set by hardware.

## 9.4.4 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after any type of Reset. The OST is not used with the EC Clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed. Therefore, the device will always be executing code while the OST is operating.

# PIC16(L)F15354/55

| U-0          | U-0                                           | U-0               | U-0            | U-0            | U-0              | R/W-0/0          | R/W-0/0     |  |

|--------------|-----------------------------------------------|-------------------|----------------|----------------|------------------|------------------|-------------|--|

|              | —                                             | —                 | _              | —              | —                | TMR2IE           | TMR1IE      |  |

| bit 7        |                                               |                   |                |                |                  |                  | bit 0       |  |

|              |                                               |                   |                |                |                  |                  |             |  |

| Legend:      |                                               |                   |                |                |                  |                  |             |  |

| R = Read     | able bit                                      | W = Writable      | bit            | U = Unimpler   | mented bit, read | as '0'           |             |  |

| u = Bit is   | unchanged                                     | x = Bit is unkn   | own            | -n/n = Value a | at POR and BOI   | R/Value at all o | ther Resets |  |

| '1' = Bit is | set                                           | '0' = Bit is clea | ared           | HS = Hardwa    | are set          |                  |             |  |

|              |                                               |                   |                |                |                  |                  |             |  |

| bit 7-2      | Unimplemer                                    | ted: Read as '    | )'             |                |                  |                  |             |  |

| bit 1        | TMR2IE: TM                                    | R2 to PR2 Mate    | h Interrupt Er | nable bit      |                  |                  |             |  |

|              |                                               | the Timer2 to I   |                |                |                  |                  |             |  |

|              |                                               | s the Timer2 to   |                | -              |                  |                  |             |  |

| bit 0        |                                               | er1 Overflow In   | •              |                |                  |                  |             |  |

|              |                                               | the Timer1 ove    |                |                |                  |                  |             |  |

|              | 0 = Enables                                   | s the Timer1 ove  | eniow interrup | )(             |                  |                  |             |  |

| Note:        | Note: Bit PEIE of the INTCON register must be |                   |                |                |                  |                  |             |  |

| Note.        | set to enable a                               | •                 |                |                |                  |                  |             |  |

|              | controlled by regis                           | • • •             |                |                |                  |                  |             |  |

# REGISTER 10-6: PIE4: PERIPHERAL INTERRUPT ENABLE REGISTER 4

| R/W-0/0                                                                                                                                                           | R/W-0/0                                                   | R/W-0/0                                                                                        | R/W-0/0   | U-0          | U-0              | U-0              | R/W-0/0      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------|--------------|------------------|------------------|--------------|

| CLC4IE                                                                                                                                                            | CLC3IE                                                    | CLC2IE                                                                                         | CLC1IE    | _            | —                | —                | TMR1GIE      |

| bit 7                                                                                                                                                             |                                                           |                                                                                                |           |              |                  |                  | bit C        |

|                                                                                                                                                                   |                                                           |                                                                                                |           |              |                  |                  |              |

| Legend:                                                                                                                                                           |                                                           |                                                                                                |           |              |                  |                  |              |

| R = Readable                                                                                                                                                      |                                                           | W = Writable                                                                                   |           |              | mented bit, read |                  |              |

| u = Bit is unc                                                                                                                                                    | •                                                         | x = Bit is unkr                                                                                |           | -n/n = Value | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is se                                                                                                                                                   | t                                                         | '0' = Bit is clea                                                                              | ared      | HS = Hardwa  | are set          |                  |              |

| bit 7 CLC4IE: CLC4 Interrupt Enable bit<br>1 = CLC4 interrupt enabled<br>0 = CLC4 interrupt disabled                                                              |                                                           |                                                                                                |           |              |                  |                  |              |

| bit 6                                                                                                                                                             | 1 = CLC3 ir                                               | CLC3IE: CLC3 Interrupt Enable bit<br>1 = CLC3 interrupt enabled<br>0 = CLC3 interrupt disabled |           |              |                  |                  |              |

| bit 5                                                                                                                                                             | 1 = CLC2 ir                                               | C2 Interrupt Ena<br>nterrupt enableo<br>nterrupt disableo                                      | ł         |              |                  |                  |              |

| bit 4                                                                                                                                                             | 1 = CLC1 ir                                               | C1 Interrupt Ena<br>nterrupt enableo<br>nterrupt disableo                                      | Ł         |              |                  |                  |              |

| bit 3-1                                                                                                                                                           | Unimplemer                                                | nted: Read as '                                                                                | 0'        |              |                  |                  |              |

| bit 0 <b>TMR1GIE:</b> Timer1 Gate Interrupt Enable bit<br>1 = Enables the Timer1 gate acquisition interrupt<br>0 = Disables the Timer1 gate acquisition interrupt |                                                           |                                                                                                |           |              |                  |                  |              |

| se                                                                                                                                                                | it PEIE of the IN<br>et to enable a<br>ontrolled by regis | ny peripheral                                                                                  | interrupt |              |                  |                  |              |

## REGISTER 10-7: PIE5: PERIPHERAL INTERRUPT ENABLE REGISTER 5

# 12.7 Register Definitions: Windowed Watchdog Timer Control

## REGISTER 12-1: WDTCON0: WATCHDOG TIMER CONTROL REGISTER 0

| U-0            | U-0                                                                                                        | R/W <sup>(3)</sup> -q/q <sup>(2)</sup>                           | R/W <sup>(3)</sup> -q/q <sup>(2)</sup>            | R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W-0/0    |  |  |

|----------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|------------|--|--|

| -              | —                                                                                                          |                                                                  |                                                   | WDTPS<4:0>(1)                          |                                        |                                        | SWDTEN     |  |  |

| oit 7          |                                                                                                            |                                                                  |                                                   |                                        |                                        |                                        | bit        |  |  |

|                |                                                                                                            |                                                                  |                                                   |                                        |                                        |                                        |            |  |  |

| Legend:        |                                                                                                            |                                                                  |                                                   |                                        |                                        |                                        |            |  |  |

| R = Readab     | le bit                                                                                                     | W = Writable b                                                   | bit                                               | U = Unimplem                           | ented bit, read                        | as '0'                                 |            |  |  |

| u = Bit is un  | changed                                                                                                    | x = Bit is unkn                                                  | own                                               | -n/n = Value a                         | t POR and BO                           | R/Value at all ot                      | her Resets |  |  |

| 1' = Bit is se | et                                                                                                         | '0' = Bit is clea                                                | ired                                              | q = Value depe                         | ends on conditi                        | on                                     |            |  |  |

|                | Unimulana                                                                                                  | nted. Deed ee 's                                                 | <b>,</b> 3                                        |                                        |                                        |                                        |            |  |  |

| oit 7-6        | =                                                                                                          | ented: Read as '0                                                |                                                   | ala at hita(1)                         |                                        |                                        |            |  |  |

| oit 5-1        |                                                                                                            | <b>0&gt;:</b> Watchdog Tir                                       | ner Prescale So                                   | elect bits                             |                                        |                                        |            |  |  |

|                |                                                                                                            | Prescale Rate                                                    |                                                   | ham val. (4,00)                        |                                        |                                        |            |  |  |

|                | 11111 = R                                                                                                  | eserved. Results                                                 | in minimum in                                     | lervar (1:32)                          |                                        |                                        |            |  |  |

|                | •                                                                                                          |                                                                  |                                                   |                                        |                                        |                                        |            |  |  |

|                | •                                                                                                          |                                                                  |                                                   |                                        |                                        |                                        |            |  |  |

|                | 10011 = R                                                                                                  | eserved. Results                                                 | in minimum in                                     | terval (1:32)                          |                                        |                                        |            |  |  |

|                | 10010 = 1:8388608 (2 <sup>23</sup> ) (Interval 256s nominal)                                               |                                                                  |                                                   |                                        |                                        |                                        |            |  |  |

|                | 10001 = <b>1</b> :                                                                                         | :4194304 (2 <sup>22</sup> ) (I                                   | 194304 (2 <sup>22</sup> ) (Interval 128s nominal) |                                        |                                        |                                        |            |  |  |

|                | $10000 = 1:2097152 (2^{21})$ (Interval 64s nominal)<br>$01111 = 1:1048576 (2^{20})$ (Interval 32s nominal) |                                                                  |                                                   |                                        |                                        |                                        |            |  |  |

|                |                                                                                                            |                                                                  |                                                   |                                        |                                        |                                        |            |  |  |

|                | 01110 = 1:                                                                                                 | :524288 (2 <sup>19</sup> ) (In<br>:262144 (2 <sup>18</sup> ) (In | terval 16s nomi                                   | nal)                                   |                                        |                                        |            |  |  |

|                | 01101 = 1                                                                                                  | :262144 (2 <sup>10</sup> ) (In<br>:131072 (2 <sup>17</sup> ) (In | terval 8s nomin                                   | al)                                    |                                        |                                        |            |  |  |

|                |                                                                                                            | :65536 (Interval 2                                               |                                                   |                                        |                                        |                                        |            |  |  |

|                |                                                                                                            | :32768 (Interval 1                                               |                                                   |                                        |                                        |                                        |            |  |  |

|                |                                                                                                            | :16384 (Interval 5                                               | ,                                                 | l)                                     |                                        |                                        |            |  |  |

|                |                                                                                                            | :8192 (Interval 25                                               |                                                   |                                        |                                        |                                        |            |  |  |

|                |                                                                                                            | :4096 (Interval 12                                               |                                                   |                                        |                                        |                                        |            |  |  |

|                |                                                                                                            | :2048 (Interval 64                                               |                                                   |                                        |                                        |                                        |            |  |  |

|                |                                                                                                            | :1024 (Interval 32                                               | ,                                                 |                                        |                                        |                                        |            |  |  |

|                |                                                                                                            | :512 (Interval 16<br>:256 (Interval 8 m                          | ,                                                 |                                        |                                        |                                        |            |  |  |

|                |                                                                                                            | :128 (Interval 4 m                                               |                                                   |                                        |                                        |                                        |            |  |  |

|                |                                                                                                            | :64 (Interval 2 ms                                               |                                                   |                                        |                                        |                                        |            |  |  |

|                |                                                                                                            | :32 (Interval 1 ms                                               |                                                   |                                        |                                        |                                        |            |  |  |

| pit 0          |                                                                                                            | Software Enable/I                                                | Disable for Wat                                   | chdog Timer bi                         | t                                      |                                        |            |  |  |

|                | If WDTE<1:                                                                                                 |                                                                  |                                                   |                                        |                                        |                                        |            |  |  |

|                | This bit is ig                                                                                             |                                                                  |                                                   |                                        |                                        |                                        |            |  |  |

|                | <u>If WDTE&lt;1:</u><br>1 = WDT is                                                                         |                                                                  |                                                   |                                        |                                        |                                        |            |  |  |

|                | 1 = WDT is<br>0 = WDT is                                                                                   |                                                                  |                                                   |                                        |                                        |                                        |            |  |  |

|                | If WDTE<1:                                                                                                 |                                                                  |                                                   |                                        |                                        |                                        |            |  |  |

|                | <u></u>                                                                                                    |                                                                  |                                                   |                                        |                                        |                                        |            |  |  |

- 2: When WDTCPS <4:0> in CONFIG3 = 11111, the Reset value of WDTPS<4:0> is 01011. Otherwise, the Reset value of WDTPS<4:0> is equal to WDTCPS<4:0> in CONFIG3.

- 3: When WDTCPS <4:0> in CONFIG3  $\neq$  11111, these bits are read-only.

## 19.2.1 CALIBRATION

## **Single-Point Calibration**

Single-point calibration is performed by application software using Equation 19-1 and the assumed Mt. A reading of VTSENSE at a known temperature is taken, and the theoretical temperature is calculated by temporarily setting TOFFSET = 0. Then TOFFSET is computed as the difference of the actual and calculated temperatures. Finally, TOFFSET is stored in nonvolatile memory within the device, and is applied to future readings to gain a more accurate measurement.

The magnitude of error in a typical single-point calibration is approximately 3-4°C.

- Note 1: The TOFFSET value may be determined by the user with a temperature test, or it can be based on the Microchip-supplied data from the DIA table. Please refer to Section 6.0 "Device Information Area" for more information.

- 2: Although the measurement range is -40°C to +125 °C, due to the variations in the value of Mv, the single-point calculated TSENSE value may indicate a temperature from -140°C to +225°C, before the calibration offset is applied.

# Higher-Order Calibration

If the application requires more precise temperature measurement, additional calibrations steps will be necessary. For these applications, two-point or threepoint calibration is recommended.

### 19.2.2 TEMPERATURE RESOLUTION

The resolution of the ADC reading, Ma (°C/count), depends on both the ADC resolution N and the reference voltage used for conversion, as shown in Equation 19-2. It is recommended to use the smallest VREF value, such as 2.048 FVR reference voltage, instead of VDD.

| Note: | Refer   | to     | Sec    | tion 3 | 37.0 | "Electrical |

|-------|---------|--------|--------|--------|------|-------------|

|       | Specifi | icatio | ons"   | for    | FVR  | reference   |

|       | voltage | accu   | iracy. |        |      |             |

## EQUATION 19-2: TEMPERATURE RESOLUTION (°C/LSb)

$$Ma = \frac{V_{REF}}{2^N} \times Mt$$

$$Ma = \frac{\frac{V_{REF}}{2^{N}}}{Mv}$$

Where:

Mv = sensor voltage sensitivity (V/°C)

VREF = Reference voltage of the ADC module (in Volts)

N = Resolution of the ADC

## EXAMPLE 19-1: TEMPERATURE RESOLUTION

Using VREF = 2.048V and a 10-bit ADC provides 2 mV/LSb measurements.

Because Mv can vary from -2.40 to -2.65 mV/°C, the range of Ma = 0.75 to 0.83 °C/LSb.

# 19.3 ADC Acquisition Time

To ensure accurate temperature measurements, the user must wait a fixed amount of time for the ADC value to settle, after the ADC input multiplexer is connected to the temperature indicator output, before the conversion is performed. This specification is provided in **Section 37.0 "Electrical Specifications"**.

| U-0                                     | U-0 | U-0               | R/W-0/0 | R/W-0/0                                               | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|-----------------------------------------|-----|-------------------|---------|-------------------------------------------------------|---------|---------|---------|--|

| —                                       | —   | —                 |         |                                                       | ADAC1   | 「<3:0>  |         |  |

| bit 7                                   |     |                   |         |                                                       |         |         | bit 0   |  |

|                                         |     |                   |         |                                                       |         |         |         |  |

| Legend:                                 |     |                   |         |                                                       |         |         |         |  |

| R = Readable b                          | oit | W = Writable      | bit     | U = Unimplemented bit, read as '0'                    |         |         |         |  |

| u = Bit is unchanged x = Bit is unknown |     |                   |         | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |

| '1' = Bit is set                        |     | '0' = Bit is clea | ared    |                                                       |         |         |         |  |

### REGISTER 20-3: ADACT: A/D AUTO-CONVERSION TRIGGER

bit 7-4 Unimplemented: Read as '0'

bit 3-0 ADACT<3:0>: Auto-Conversion Trigger Selection bits<sup>(1)</sup> (see Table 20-2)

**Note 1:** This is a rising edge sensitive input for all sources.

# PIC16(L)F15354/55

| Name     | Bit 7       | Bit 6  | Bit 5     | Bit 4  | Bit 3                        | Bit 2   | Bit 1   | Bit 0  | Register<br>on Page |  |

|----------|-------------|--------|-----------|--------|------------------------------|---------|---------|--------|---------------------|--|

| INTCON   | GIE         | PEIE   |           | —      | —                            | —       |         | INTEDG | 119                 |  |

| PIE1     | OSFIE       | CSWIE  |           |        |                              |         | _       | ADIE   | 121                 |  |

| PIR1     | OSFIF       | CSWIF  | -         | _      | _                            | _       | -       | ADIF   | 129                 |  |

| TRISA    | TRISA7      | TRISA6 | TRISA5    | TRISA4 | TRISA3                       | TRISA2  | TRISA1  | TRISA0 | 173                 |  |

| TRISB    | TRISB7      | TRISB6 | TRISB5    | TRISB4 | TRISB3                       | TRISB2  | TRISB1  | TRISB0 | 178                 |  |

| TRISC    | TRISC7      | TRISC6 | TRISC5    | TRISC4 | TRISC3                       | TRISC2  | TRISC1  | TRISC0 | 183                 |  |

| ANSELA   | ANSA7       | ANSA6  | ANSA5     | ANSA4  | ANSA3                        | ANSA2   | ANSA1   | ANSA0  | 174                 |  |

| ANSELB   | ANSB7       | ANSB6  | ANSB5     | ANSB4  | ANSB3                        | ANSB2   | ANSB1   | ANSB0  | 179                 |  |

| ANSELC   | ANSC7       | ANSC6  | ANSC5     | ANSC4  | ANSC3                        | ANSC2   | ANSC1   | ANSC0  | 184                 |  |

| ADCON0   |             |        | CHS<      | 5:0>   |                              |         | GO/DONE | ADON   | 229                 |  |

| ADCON1   | ADFM        | ŀ      | ADCS<2:0> | >      |                              |         | ADPREF  | <1:0>  | 230                 |  |

| ADACT    | —           | —      | —         | _      |                              | ADA     | CT<3:0> |        | 231                 |  |

| ADRESH   |             |        |           | ADRE   | SH<7:0>                      |         |         |        | 232                 |  |

| ADRESL   | ADRESL<7:0> |        |           |        |                              |         |         |        |                     |  |

| FVRCON   | FVREN       | FVRRDY | TSEN      | TSRNG  | TSRNG CDAFVR<1:0> ADFVR<1:0> |         |         |        |                     |  |

| DAC1CON1 | —           | —      | —         |        |                              | DAC1R<4 | :0>     | -      | 238                 |  |

| OSCSTAT1 | EXTOR       | HFOR   | MFOR      | LFOR   | SOR                          | ADOR    |         | PLLR   | 110                 |  |

## TABLE 20-3: SUMMARY OF REGISTERS ASSOCIATED WITH ADC

**Legend:** – = unimplemented read as '0'. Shaded cells are not used for the ADC module.

**Note 1:** Unimplemented, read as '1'.

# 21.4 Operation During Sleep

The DAC continues to function during Sleep. When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the DAC1CON0 register are not affected.

# 21.5 Effects of a Reset

A device Reset affects the following:

- DAC is disabled.

- DAC output voltage is removed from the DAC10UT1/2 pins.

- The DAC1R<4:0> range select bits are cleared.

# 23.12 Register Definitions: Comparator Control

## REGISTER 23-1: CMxCON0: COMPARATOR Cx CONTROL REGISTER 0

| R/W-0/0                                                            | R-0/0                                                                                                           | U-0                                                                                               | R/W-0/0          | U-0              | U-0            | R/W-0/0           | R/W-0/0      |  |  |  |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------|------------------|----------------|-------------------|--------------|--|--|--|

| ON                                                                 | OUT                                                                                                             | _                                                                                                 | POL              |                  | —              | HYS               | SYNC         |  |  |  |

| bit 7                                                              | ·                                                                                                               |                                                                                                   |                  |                  |                |                   | bit (        |  |  |  |

|                                                                    |                                                                                                                 |                                                                                                   |                  |                  |                |                   |              |  |  |  |

| Legend:                                                            |                                                                                                                 |                                                                                                   |                  |                  |                |                   |              |  |  |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0' |                                                                                                                 |                                                                                                   |                  |                  |                |                   |              |  |  |  |

| u = Bit is und                                                     | changed                                                                                                         | x = Bit is unk                                                                                    | nown             | -n/n = Value a   | at POR and BC  | OR/Value at all o | other Resets |  |  |  |

| 1' = Bit is se                                                     | t                                                                                                               | '0' = Bit is cle                                                                                  | ared             |                  |                |                   |              |  |  |  |

|                                                                    |                                                                                                                 |                                                                                                   |                  |                  |                |                   |              |  |  |  |

| bit 7                                                              | •                                                                                                               | ator Enable bit                                                                                   |                  |                  |                |                   |              |  |  |  |

|                                                                    |                                                                                                                 | tor is enabled                                                                                    | and consumes     | no active pow    | er             |                   |              |  |  |  |

| bit 6                                                              | <ul> <li>0 = Comparator is disabled and consumes no active power</li> <li>OUT: Comparator Output bit</li> </ul> |                                                                                                   |                  |                  |                |                   |              |  |  |  |

|                                                                    | If CxPOL = 1 (inverted polarity):                                                                               |                                                                                                   |                  |                  |                |                   |              |  |  |  |

|                                                                    | 1 = CxVP < 0                                                                                                    |                                                                                                   |                  |                  |                |                   |              |  |  |  |

|                                                                    | 0 = CxVP > 0                                                                                                    | CxVN<br>(noninverted p                                                                            | olarity):        |                  |                |                   |              |  |  |  |

|                                                                    | 1 = CxVP > 0                                                                                                    |                                                                                                   | olanty).         |                  |                |                   |              |  |  |  |

|                                                                    | 0 = CxVP <                                                                                                      | CxVN                                                                                              |                  |                  |                |                   |              |  |  |  |

| bit 5                                                              | Unimplemen                                                                                                      | ted: Read as '                                                                                    | 0'               |                  |                |                   |              |  |  |  |

| bit 4                                                              | POL: Compa                                                                                                      | rator Output P                                                                                    | olarity Select b | it               |                |                   |              |  |  |  |

|                                                                    |                                                                                                                 | tor output is in                                                                                  |                  |                  |                |                   |              |  |  |  |

| bit 3-2                                                            | •                                                                                                               | tor output is no                                                                                  |                  |                  |                |                   |              |  |  |  |

| bit 1                                                              | -                                                                                                               | ited: Read as '                                                                                   |                  |                  |                |                   |              |  |  |  |

|                                                                    | -                                                                                                               | rator Hysteres                                                                                    |                  |                  |                |                   |              |  |  |  |

|                                                                    |                                                                                                                 | <ul> <li>1 = Comparator hysteresis enabled</li> <li>0 = Comparator hysteresis disabled</li> </ul> |                  |                  |                |                   |              |  |  |  |

| bit 0                                                              | SYNC: Comp                                                                                                      | barator Output                                                                                    | Synchronous N    | Mode bit         |                |                   |              |  |  |  |

|                                                                    | •                                                                                                               | •                                                                                                 | •                | ) pin is synchro | onous to chang | ges on Timer1     | clock source |  |  |  |

|                                                                    |                                                                                                                 |                                                                                                   |                  | Timer1 clock so  |                |                   |              |  |  |  |

|                                                                    | 0 = Compara                                                                                                     | ator output to T                                                                                  | imer1 and I/O    | pin is asynchro  | nous           |                   |              |  |  |  |

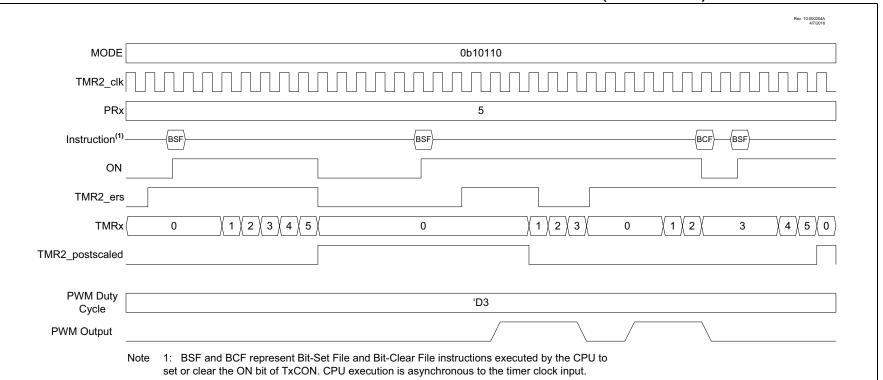

# FIGURE 27-13: LEVEL-TRIGGERED HARDWARE LIMIT ONE-SHOT MODE TIMING DIAGRAM (MODE = 10110)

PIC16(L)F15354/55

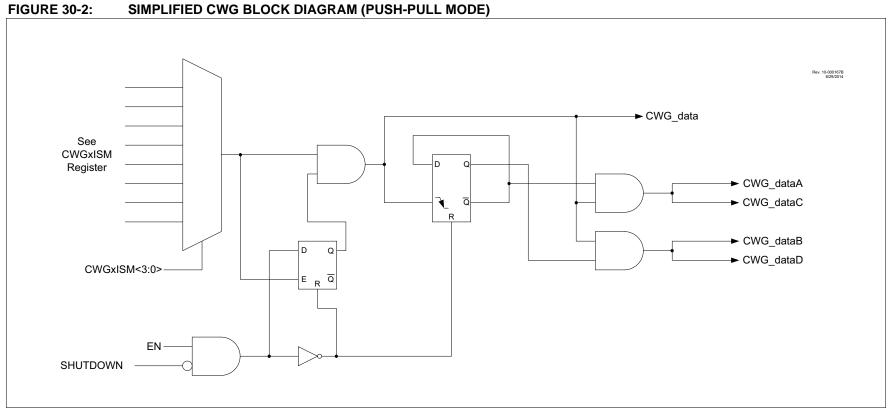

# SIMPLIFIED CWG BLOCK DIAGRAM (PUSH-PULL MODE)

PIC16(L)F15354/55

## 31.1.2 DATA GATING

Outputs from the input multiplexers are directed to the desired logic function input through the data gating stage. Each data gate can direct any combination of the four selected inputs.

#### **Note:** Data gating is undefined at power-up.

The gate stage is more than just signal direction. The gate can be configured to direct each input signal as inverted or non-inverted data. The output of each gate can be inverted before going on to the logic function stage.

The gating is in essence a 1-to-4 input AND/NAND/OR/NOR gate. When every input is inverted and the output is inverted, the gate is an OR of all enabled data inputs. When the inputs and output are not inverted, the gate is an AND or all enabled inputs.

Table 31-3 summarizes the basic logic that can be obtained in gate 1 by using the gate logic select bits. The table shows the logic of four input variables, but each gate can be configured to use less than four. If no inputs are selected, the output will be zero or one, depending on the gate output polarity bit.

| CLCxGLSy | LCxGyPOL | Gate Logic   |

|----------|----------|--------------|

| 0x55     | 1        | 4-input AND  |

| 0x55     | 0        | 4-input NAND |

| 0xAA     | 1        | 4-input NOR  |

| 0xAA     | 0        | 4-input OR   |

| 0x00     | 0        | Logic 0      |

| 0x00     | 1        | Logic 1      |

#### TABLE 31-3: DATA GATING LOGIC

It is possible (but not recommended) to select both the true and negated values of an input. When this is done, the gate output is zero, regardless of the other inputs, but may emit logic glitches (transient-induced pulses). If the output of the channel must be zero or one, the recommended method is to set all gate bits to zero and use the gate polarity bit to set the desired level.

Data gating is configured with the logic gate select registers as follows:

- Gate 1: CLCxGLS0 (Register 31-7)

- Gate 2: CLCxGLS1 (Register 31-8)

- Gate 3: CLCxGLS2 (Register 31-9)

- Gate 4: CLCxGLS3 (Register 31-10)

Register number suffixes are different than the gate numbers because other variations of this module have multiple gate selections in the same register. Data gating is indicated in the right side of Figure 31-2. Only one gate is shown in detail. The remaining three gates are configured identically with the exception that the data enables correspond to the enables for that gate.

#### 31.1.3 LOGIC FUNCTION

There are eight available logic functions including:

- AND-OR

- OR-XOR

- AND

- S-R Latch

- D Flip-Flop with Set and Reset

- D Flip-Flop with Reset

- J-K Flip-Flop with Reset

- · Transparent Latch with Set and Reset

Logic functions are shown in Figure 31-2. Each logic function has four inputs and one output. The four inputs are the four data gate outputs of the previous stage. The output is fed to the inversion stage and from there to other peripherals, an output pin, and back to the CLCx itself.

#### 31.1.4 OUTPUT POLARITY

The last stage in the Configurable Logic Cell is the output polarity. Setting the LCxPOL bit of the CLCxPOL register inverts the output signal from the logic stage. Changing the polarity while the interrupts are enabled will cause an interrupt for the resulting output transition.

# PIC16(L)F15354/55

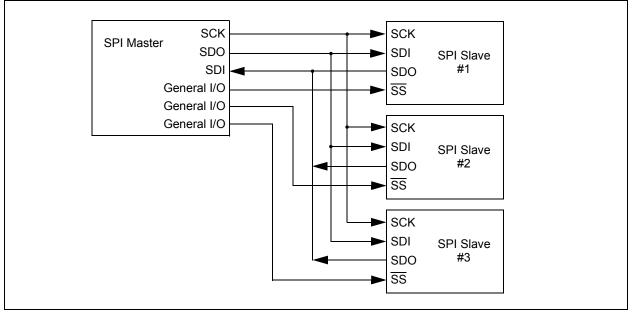

## FIGURE 32-4: SPI MASTER AND MULTIPLE SLAVE CONNECTION

## 32.2.1 SPI MODE REGISTERS

The MSSP module has five registers for SPI mode operation. These are:

- MSSP STATUS register (SSPxSTAT)

- MSSP Control register 1 (SSPxCON1)

- MSSP Control register 3 (SSPxCON3)

- MSSP Data Buffer register (SSPxBUF)

- MSSP Address register (SSPxADD)

- MSSP Shift register (SSPxSR) (Not directly accessible)

SSPxCON1 and SSPxSTAT are the control and status registers in SPI mode operation. The SSPxCON1 register is readable and writable. The lower six bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write.

In one SPI master mode, SSPxADD can be loaded with a value used in the Baud Rate Generator. More information on the Baud Rate Generator is available in **Section 32.7 "Baud Rate Generator"**.

SSPxSR is the shift register used for shifting data in and out. SSPxBUF provides indirect access to the SSPxSR register. SSPxBUF is the buffer register to which data bytes are written, and from which data bytes are read.

In receive operations, SSPxSR and SSPxBUF together create a buffered receiver. When SSPxSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set.

During transmission, the SSPxBUF is not buffered. A write to SSPxBUF will write to both SSPxBUF and SSPxSR.

## 32.5.3 SLAVE TRANSMISSION

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPxSTAT register is set. The received address is loaded into the SSPxBUF register, and an ACK pulse is sent by the slave on the ninth bit.

Following the ACK, slave hardware clears the CKP bit and the SCL pin is held low (see **Section 32.5.6** "**Clock Stretching**" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data.

The transmit data must be loaded into the SSPxBUF register which also loads the SSPxSR register. Then the SCL pin should be released by setting the CKP bit of the SSPxCON1 register. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time.

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. This ACK value is copied to the ACKSTAT bit of the SSPxCON2 register. If ACKSTAT is set (not ACK), then the data transfer is complete. In this case, when the not ACK is latched by the slave, the slave goes idle and waits for another occurrence of the Start bit. If the SDA line was low (ACK), the next transmit data must be loaded into the SSPxBUF register. Again, the SCL pin must be released by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPxIF bit must be cleared by software and the SSPxSTAT register is used to determine the status of the byte. The SSPxIF bit is set on the falling edge of the ninth clock pulse.

#### 32.5.3.1 Slave Mode Bus Collision

A slave receives a read request and begins shifting data out on the SDA line. If a bus collision is detected and the SBCDE bit of the SSPxCON3 register is set, the BCL1IF bit of the PIR3 register is set. Once a bus collision is detected, the slave goes idle and waits to be addressed again. User software can use the BCL1IF bit to handle a slave bus collision.

#### 32.5.3.2 7-bit Transmission

A master device can transmit a read request to a slave, and then clock data out of the slave. The list below outlines what software for a slave will need to do to accomplish a standard transmission. Figure 32-18 can be used as a reference to this list.

- 1. Master sends a Start condition on SDA and SCL.

- 2. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit set is received by the Slave setting SSPxIF bit.

- 4. Slave hardware generates an ACK and sets SSPxIF.

- 5. SSPxIF bit is cleared by user.

- 6. Software reads the received address from SSPxBUF, clearing BF.

- 7.  $R/\overline{W}$  is set so CKP was automatically cleared after the ACK.

- 8. The slave software loads the transmit data into SSPxBUF.

- 9. CKP bit is set releasing SCL, allowing the master to clock the data out of the slave.

- 10. SSPxIF is set after the ACK response from the master is loaded into the ACKSTAT register.

- 11. SSPxIF bit is cleared.

- 12. The slave software checks the ACKSTAT bit to see if the master wants to clock out more data.

- **Note 1:** If the master ACKs the clock will be stretched.

- ACKSTAT is the only bit updated on the rising edge of SCL (9th) rather than the falling.

- 13. Steps 9-13 are repeated for each transmitted byte.

- 14. If the master sends a not ACK; the clock is not held, but SSPxIF is still set.

- 15. The master sends a Restart condition or a Stop.

- 16. The slave is no longer addressed.

## 33.3 EUSART Baud Rate Generator (BRG)

The Baud Rate Generator (BRG) is an 8-bit or 16-bit timer that is dedicated to the support of both the asynchronous and synchronous EUSART operation. By default, the BRG operates in 8-bit mode. Setting the BRG16 bit of the BAUDxCON register selects 16-bit mode.

The SPxBRGH, SPxBRGL register pair determines the period of the free running baud rate timer. In Asynchronous mode the multiplier of the baud rate period is determined by both the BRGH bit of the TXxSTA register and the BRG16 bit of the BAUDxCON register. In Synchronous mode, the BRGH bit is ignored.

Table 33-1 contains the formulas for determining the baud rate. Example 33-1 provides a sample calculation for determining the baud rate and baud rate error.

Typical baud rates and error values for various Asynchronous modes have been computed for your convenience and are shown in Table 33-3. It may be advantageous to use the high baud rate (BRGH = 1), or the 16-bit BRG (BRG16 = 1) to reduce the baud rate error. The 16-bit BRG mode is used to achieve slow baud rates for fast oscillator frequencies.

Writing a new value to the SPxBRGH, SPxBRGL register pair causes the BRG timer to be reset (or cleared). This ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

If the system clock is changed during an active receive operation, a receive error or data loss may result. To avoid this problem, check the status of the RCIDL bit to make sure that the receive operation is idle before changing the system clock.

## EXAMPLE 33-1: CALCULATING BAUD RATE ERROR

For a device with Fosc of 16 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG:

Desired Baud Rate =  $\frac{FOSC}{64([SPBRGH:SPBRGL] + 1)}$

Solving for SPxBRGH:SPxBRGL:

| $X = \frac{Fosc}{\frac{Desired Baud Rate}{64} - 1}$                     |

|-------------------------------------------------------------------------|

| $= \frac{\frac{16000000}{9600}}{64} - 1$                                |

| = [25.042] = 25                                                         |

| $Calculated Baud Rate = \frac{16000000}{64(25+1)}$                      |

| = 9615                                                                  |

| Error = $\frac{Calc. Baud Rate - Desired Baud Rate}{Desired Baud Rate}$ |

| $=\frac{(9615-9600)}{9600} = 0.16\%$                                    |

# 36.0 INSTRUCTION SET SUMMARY

Each instruction is a 14-bit word containing the operation code (opcode) and all required operands. The opcodes are broken into three broad categories.

- Byte Oriented

- Bit Oriented

- Literal and Control

The literal and control category contains the most varied instruction word format.

Table 36-3 lists the instructions recognized by the MPASMTM assembler.

All instructions are executed within a single instruction cycle, with the following exceptions, which may take two or three cycles:

- Subroutine entry takes two cycles (CALL, CALLW)

- Returns from interrupts or subroutines take two cycles (RETURN, RETLW, RETFIE)

- Program branching takes two cycles (GOTO, BRA, BRW, BTFSS, BTFSC, DECFSZ, INCSFZ)

- One additional instruction cycle will be used when any instruction references an indirect file register and the file select register is pointing to program memory.

One instruction cycle consists of 4 oscillator cycles; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution rate of 1 MHz.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

# 36.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

## TABLE 36-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                            |

| W     | Working register (accumulator)                                                                                                                                                  |

| b     | Bit address within an 8-bit file register                                                                                                                                       |

| k     | Literal field, constant data or label                                                                                                                                           |

| x     | Don't care location (= 0 or 1).<br>The assembler will generate code with $x = 0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                   |

| n     | FSR or INDF number. (0-1)                                                                                                                                                       |

| mm    | Prepost increment-decrement mode selection                                                                                                                                      |

# TABLE 36-2: ABBREVIATION DESCRIPTIONS

| Field | Description     |

|-------|-----------------|

| PC    | Program Counter |

| TO    | Time-Out bit    |

| С     | Carry bit       |

| DC    | Digit Carry bit |

| Z     | Zero bit        |

| PD    | Power-Down bit  |

## **39.2 MPLAB XC Compilers**

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.