Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 224 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 28-SPDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15354-e-sp |

**TABLE 1-2:** PIC16(L)F15354/55 PINOUT DESCRIPTION (CONTINUED)

| Name                                                                                | Function              | Input<br>Type    | Output Type | Description                                                                                       |

|-------------------------------------------------------------------------------------|-----------------------|------------------|-------------|---------------------------------------------------------------------------------------------------|

| RC1/ANC1/CCP2 <sup>(1)</sup> /IOCC1/SOSCI                                           | RC1                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                              |

|                                                                                     | ANC1                  | AN               | ı           | ADC Channel C1 input.                                                                             |

|                                                                                     | CCP2 <sup>(1)</sup>   | TTL/ST           | CMOS/OD     | CCP2 Capture Input.                                                                               |

|                                                                                     | IOCC1                 | TTL/ST           | -           | Interrupt-on-change input.                                                                        |

|                                                                                     | SOSCI                 | AN               | -           | 32.768 kHz secondary oscillator crystal driver input.                                             |

| RC2/ANC2/CCP1 <sup>(1)</sup> /IOCC2                                                 | RC2                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                              |

|                                                                                     | ANC2                  | AN               | -           | ADC Channel C2 input.                                                                             |

|                                                                                     | CCP1 <sup>(1)</sup>   | TTL/ST           | CMOS/OD     | CCP1 Capture Input.                                                                               |

|                                                                                     | IOCC2                 | TTL/ST           | -           | Interrupt-on-change input.                                                                        |

| RC3/ANC3/SCL1 <sup>(3,4)</sup> /SCK1 <sup>(1)</sup> /T2IN <sup>(1)</sup> /<br>IOCC3 | RC3                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                              |

| 10003                                                                               | ANC3                  | AN               | -           | ADC Channel C3 input.                                                                             |

|                                                                                     | SCL1 <sup>(3,4)</sup> | I <sup>2</sup> C | OD          | MSSP1 I <sup>2</sup> C input/output.                                                              |

|                                                                                     | SCK1 <sup>(1)</sup>   | TTL/ST           | CMOS/OD     | MSSP1 SPI clock input/output (default input location, SCK1 is a PPS remappable input and output). |

|                                                                                     | T2IN <sup>(1)</sup>   | TTL/ST           | _           | Timer2 external input.                                                                            |

|                                                                                     | IOCC3                 | TTL/ST           |             | Interrupt-on-change input.                                                                        |

| RC4/ANC4/SDA1 <sup>(3,4)</sup> /SDI1 <sup>(1)</sup> /IOCC4                          | RC4                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                              |

|                                                                                     | ANC4                  | AN               | _           | ADC Channel C4 input.                                                                             |

|                                                                                     | SDA1 <sup>(3,4)</sup> | I <sup>2</sup> C | OD          | MSSP1 I <sup>2</sup> C serial data input/output.                                                  |

|                                                                                     | SDI1 <sup>(1)</sup>   | TTL/ST           |             | MSSP1 SPI serial data input.                                                                      |

|                                                                                     | IOCC4                 | TTL/ST           | ı           | Interrupt-on-change input.                                                                        |

| RC5/ANC5/IOCC5                                                                      | RC5                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                              |

|                                                                                     | ANC5                  | AN               | ı           | ADC Channel C5 input.                                                                             |

|                                                                                     | IOCC5                 | TTL/ST           | _           | Interrupt-on-change input.                                                                        |

| RC6/ANC6/TX1/CK1 <sup>(1)</sup> /IOCC6                                              | RC6                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                              |

|                                                                                     | ANC6                  | AN               | ı           | ADC Channel C6 input.                                                                             |

|                                                                                     | TX1                   | _                | CMOS        | EUSART1 asynchronous transmit.                                                                    |

|                                                                                     | CK1 <sup>(1)</sup>    | TTL/ST           | CMOS/OD     | EUSART 1 synchronous mode clock input/output.                                                     |

|                                                                                     | IOCC6                 | TTL/ST           | _           | Interrupt-on-change input.                                                                        |

| RC7/ANC7/RX1/DT1 <sup>(3)</sup> /IOCC7                                              | RC7                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                              |

|                                                                                     | ANC7                  | AN               | _           | ADC Channel C7 input.                                                                             |

|                                                                                     | RX1                   | TTL/ST           | _           | EUSART1 Asynchronous mode receiver data input.                                                    |

|                                                                                     | DT1 <sup>(3)</sup>    | TTL/ST           | CMOS/OD     | EUSART1 Synchronous mode data input/output.                                                       |

|                                                                                     | IOCC7                 | TTL/ST           | _           | Interrupt-on-change input.                                                                        |

AN = Analog input or output Legend: TTL = TTL compatible input

CMOS = CMOS compatible input or output

OD = Open-Drain

ST = Schmitt Trigger input with CMOS levels I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C

Note 1:

HV = High Voltage XTAL = Crystal levels

This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 15-2 for details on which PORT pins may be used for this signal.

All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin

options as described in Table 15-3.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

| IADEL -            | † 10. O. LO.                                    | AL I GIIGIIGII      | KE OIO I EK                    | OOMMAN | DAINIO 0 | 00 (0011111 | iold) |       |       |                       |                            |  |

|--------------------|-------------------------------------------------|---------------------|--------------------------------|--------|----------|-------------|-------|-------|-------|-----------------------|----------------------------|--|

| Address            | Name                                            | Bit 7               | Bit 6                          | Bit 5  | Bit 4    | Bit 3       | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |  |

| Bank 1             | Bank 1                                          |                     |                                |        |          |             |       |       |       |                       |                            |  |

|                    | CPU CORE REGISTERS; see Table 4-3 for specifics |                     |                                |        |          |             |       |       |       |                       |                            |  |

| 08Ch Unimplemented |                                                 |                     |                                |        |          |             |       |       |       | _                     | _                          |  |

| 09Bh               | ADRESL                                          | ADC Result Register | Low                            |        |          |             |       |       |       | xxxx xxxx             | uuuu uuuu                  |  |

| 09Ch               | ADRESH                                          | ADC Result Register | High                           |        |          |             |       |       |       | xxxx xxxx             | uuuu uuuu                  |  |

| 09Dh               | ADCON0                                          |                     | CHS<5:0> GO/DONE ADON          |        |          |             |       |       |       |                       | 0000 0000                  |  |

| 09Eh               | ADCON1                                          | ADFM                | ADFM ADCS<2:0> — — ADPREF<1:0> |        |          |             |       |       |       | 000000                | 000000                     |  |

| 09Fh               | ADACT — — — ADACT<3:0> 0000                     |                     |                                |        |          |             |       | 0000  |       |                       |                            |  |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

| Address | Name                                            | Bit 7                 | Bit 6               | Bit 5             | Bit 4    | Bit 3  | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |  |

|---------|-------------------------------------------------|-----------------------|---------------------|-------------------|----------|--------|-------|-------|-------|-----------------------|----------------------------|--|

| Bank 3  | Bank 3                                          |                       |                     |                   |          |        |       |       |       |                       |                            |  |

|         | CPU CORE REGISTERS; see Table 4-3 for specifics |                       |                     |                   |          |        |       |       |       |                       |                            |  |

| 18Ch    | SSP1BUF                                         | Synchronous Serial Po | ort Receive Buffer/ | Transmit Register | -        |        |       |       |       | xxxx xxxx             | xxxx xxxx                  |  |

| 18Dh    | SSP1ADD                                         |                       |                     |                   | ADD<     | 7:0>   |       |       |       | 0000 0000             | 0000 0000                  |  |

| 18Eh    | SSP1MSK                                         |                       |                     |                   | MSK<     | 7:0>   |       |       |       | 1111 1111             | 1111 1111                  |  |

| 18Fh    | SSP1STAT                                        | SMP                   | CKE                 | D/ <del>A</del>   | Р        | S      | R/W   | UA    | BF    | 0000 0000             | 0000 0000                  |  |

| 190h    | SSP1CON1                                        | WCOL                  | SSPOV               | SSPEN             | CKP      | SSPM3  | SSPM2 | SSPM1 | SSPM0 | 0000 0000             | 0000 0000                  |  |

| 191h    | SSP1CON2                                        | GCEN                  | ACKSTAT             | ACKDT             | ACKEN    | RCEN   | PEN   | RSEN  | SEN   | 0000 0000             | 0000 0000                  |  |

| 192h    | SSP1CON3                                        | ACKTIM                | PCIE                | SCIE              | BOEN     | SDAHT  | SBCDE | AHEN  | DHEN  | 0000 0000             | 0000 0000                  |  |

| 193h    | _                                               |                       |                     |                   | Unimpler | mented |       |       |       |                       |                            |  |

| 194h    | _                                               |                       |                     |                   | Unimpler | mented |       |       |       |                       |                            |  |

| 195h    |                                                 |                       |                     |                   | Unimpler | mented |       |       |       |                       |                            |  |

| 196h    | SSP2BUF                                         | Synchronous Serial Po | ort Receive Buffer/ | Transmit Register | -        |        |       |       |       | xxxx xxxx             | xxxx xxxx                  |  |

| 197h    | SSP2ADD                                         |                       |                     |                   | ADD<     | 7:0>   |       |       |       | 0000 0000             | 0000 0000                  |  |

| 198h    | SSP2MSK                                         |                       |                     |                   | MSK<     | 7:0>   |       |       |       | 1111 1111             | 1111 1111                  |  |

| 199h    | SSP2STAT                                        | SMP                   | CKE                 | D/ <del>A</del>   | Р        | S      | R/W   | UA    | BF    | 0000 0000             | 0000 0000                  |  |

| 19Ah    | SSP2CON1                                        | WCOL                  | SSPOV               | SSPEN             | CKP      | SSPM3  | SSPM2 | SSPM1 | SSPM0 | 0000 0000             | 0000 0000                  |  |

| 19Bh    | SSP2CON2                                        | GCEN                  | ACKSTAT             | ACKDT             | ACKEN    | RCEN   | PEN   | RSEN  | SEN   | 0000 0000             | 0000 0000                  |  |

| 19Ch    | SSP2CON3                                        | ACKTIM                | PCIE                | SCIE              | BOEN     | SDAHT  | SBCDE | AHEN  | DHEN  | 0000 0000             | 0000 0000                  |  |

| 19Dh    |                                                 |                       |                     |                   | Unimpler | mented |       |       |       |                       |                            |  |

| 19Eh    | h — Unimplemented                               |                       |                     |                   |          |        |       |       |       |                       |                            |  |

| 19Fh    | I                                               |                       |                     |                   | Unimpler | mented |       |       |       |                       |                            |  |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

## 8.3 Register Definitions: Brown-out Reset Control

### REGISTER 8-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u               | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |

|-----------------------|-----|-----|-----|-----|-----|-----|--------|

| SBOREN <sup>(1)</sup> | _   | _   | _   | _   | _   | _   | BORRDY |

| bit 7                 |     |     |     |     |     |     | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared q = Value depends on condition

bit 7 SBOREN: Software Brown-out Reset Enable bit<sup>(1)</sup>

If BOREN <1:0> in Configuration Words ≠ 01:

SBOREN is read/write, but has no effect on the BOR.

If BOREN <1:0> in Configuration Words = 01:

1 = BOR Enabled 0 = BOR Disabled

bit 6-1 **Unimplemented:** Read as '0'

bit 0 BORRDY: Brown-out Reset Circuit Ready Status bit

1 = The Brown-out Reset circuit is active0 = The Brown-out Reset circuit is inactive

**Note 1:** BOREN<1:0> bits are located in Configuration Words.

© 2016 Microchip Technology Inc.

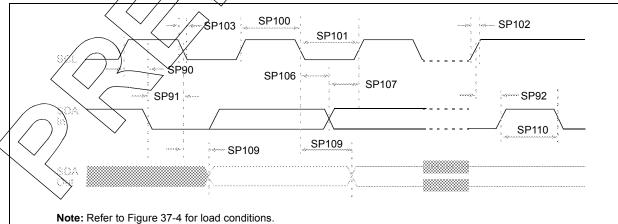

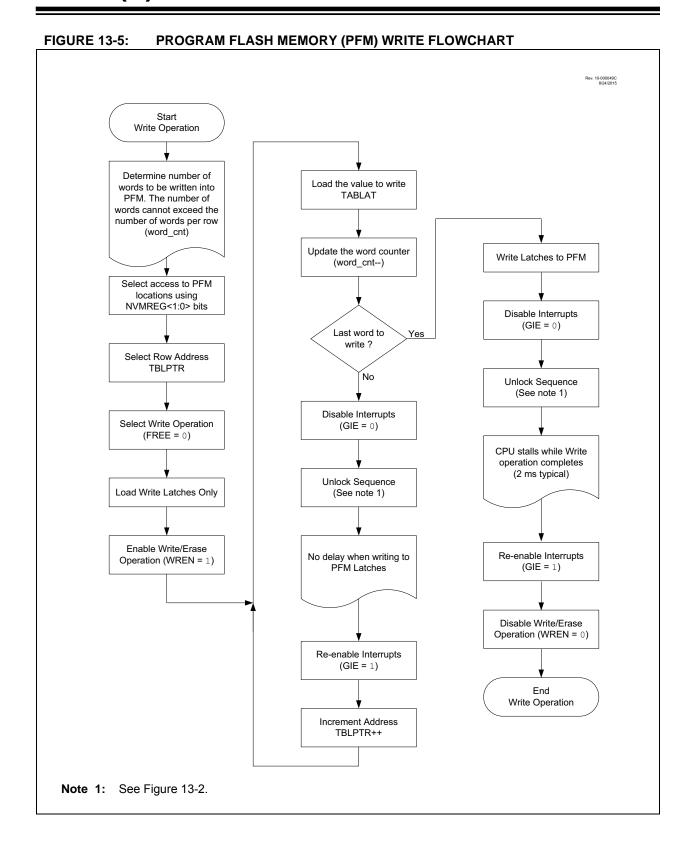

## 13.3.5 MODIFYING FLASH PROGRAM MEMORY

When modifying existing data in a program memory row, and data within that row must be preserved, it must first be read and saved in a RAM image. Program memory is modified using the following steps:

- Load the starting address of the row to be modified.

- 2. Read the existing data from the row into a RAM image.

- 3. Modify the RAM image to contain the new data to be written into program memory.

- Load the starting address of the row to be rewritten.

- 5. Erase the program memory row.

- Load the write latches with data from the RAM image.

- 7. Initiate a programming operation.

FIGURE 13-6: FLASH PROGRAM MEMORY MODIFY FLOWCHART

#### 14.0 I/O PORTS

TABLE 14-1: PORT AVAILABILITY PER DEVICE

| Device            | PORTA | PORTB | PORTC | PORTE |

|-------------------|-------|-------|-------|-------|

| PIC16(L)F15354/55 | •     | •     | •     | •     |

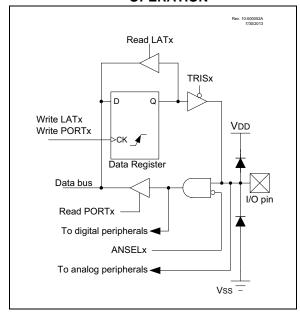

Each port has ten standard registers for its operation. These registers are:

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

- TRISx registers (data direction)

- · ANSELx registers (analog select)

- WPUx registers (weak pull-up)

- INLVLx (input level control)

- · SLRCONx registers (slew rate)

- ODCONx registers (open-drain)

Most port pins share functions with device peripherals, both analog and digital. In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output; however, the pin can still be read.

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports that support analog inputs have an associated ANSELx register. When an ANSEL bit is set, the digital input buffer associated with that bit is disabled.

Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 14-1.

FIGURE 14-1: GENERIC I/O PORT OPERATION

#### 14.1 I/O Priorities

Each pin defaults to the PORT data latch after Reset. Other functions are selected with the peripheral pin select logic. See **Section 15.0 "Peripheral Pin Select (PPS) Module"** for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx register. Digital output functions may continue to control the pin when it is in Analog mode.

Analog outputs, when enabled, take priority over the digital outputs and force the digital output driver to the high-impedance state.

### 14.2 PORTA Registers

#### 14.2.1 DATA REGISTER

PORTA is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 14-2). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 14.2.8 shows how to initialize PORTA.

Reading the PORTA register (Register 14-1) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATA).

The PORT data latch LATA (Register 14-3) holds the output port data, and contains the latest value of a LATA or PORTA write.

#### **EXAMPLE 14-1: INITIALIZING PORTA**

```

; This code example illustrates

; initializing the PORTA register. The

; other ports are initialized in the same

; manner.

BANKSEL PORTA

CLRF

PORTA

;Init PORTA

BANKSEL LATA

;Data Latch

LATA

CLRF

BANKSEL ANSELA

;digital I/O

CLRF

ANSELA

BANKSEL TRISA

MOVLW

B'00111000' ;Set RA<5:3> as inputs

MOVWF

;and set RA<2:0> as

TRISA

;outputs

```

#### 14.2.2 DIRECTION CONTROL

The TRISA register (Register 14-2) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

#### 14.2.3 OPEN-DRAIN CONTROL

The ODCONA register (Register 14-6) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONA bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONA bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

**Note:** It is not necessary to set open-drain control when using the pin for I<sup>2</sup>C; the I<sup>2</sup>C module controls the pin and makes the pin open-drain.

#### 14.2.4 SLEW RATE CONTROL

The SLRCONA register (Register 14-7) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONA bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONA bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

#### 14.2.5 INPUT THRESHOLD CONTROL

The INLVLA register (Register 14-8) controls the input voltage threshold for each of the available PORTA input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTA register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 37-4 for more information on threshold levels.

Note: Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

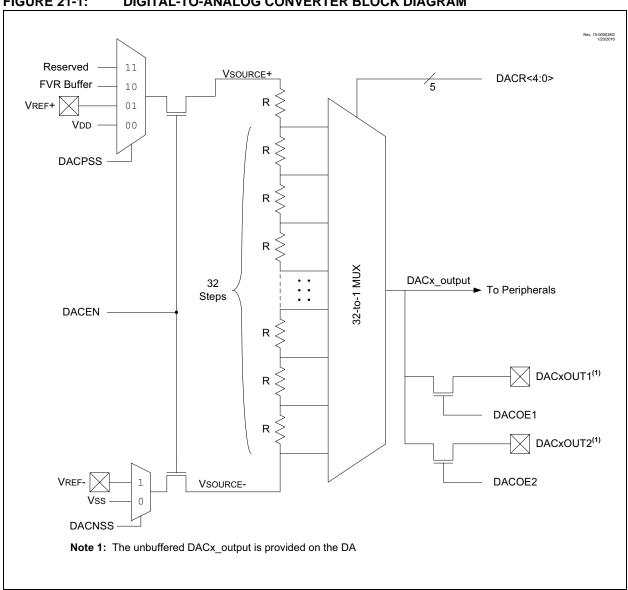

**FIGURE 21-1: DIGITAL-TO-ANALOG CONVERTER BLOCK DIAGRAM**

#### **FIGURE 21-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE**

#### 23.10 CWG1 Auto-shutdown Source

The output of the comparator module can be used as an auto-shutdown source for the CWG1 module. When the output of the comparator is active and the corresponding ASxE is enabled, the CWG operation will be suspended immediately (see **Section 30.10** "Auto-Shutdown").

## 23.11 Operation in Sleep Mode

The comparator module can operate during Sleep. The comparator clock source is based on the Timer1 clock source. If the Timer1 clock source is either the system clock (Fosc) or the instruction clock (Fosc/4), Timer1 will not operate during Sleep, and synchronized comparator outputs will not operate.

A comparator interrupt will wake the device from Sleep. The CxIE bits of the PIE2 register must be set to enable comparator interrupts.

## REGISTER 26-2: T1GCON: TIMER1 GATE CONTROL REGISTER

| R/W-0/u | R/W-0/u | R/W-0/u | R/W-0/u | R/W/HC-0/u | R-x/x | U-0 | U-0   |

|---------|---------|---------|---------|------------|-------|-----|-------|

| GE      | GPOL    | GTM     | GSPM    | GGO/DONE   | GVAL  | _   | _     |

| bit 7   |         |         |         |            |       |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HC = Bit is cleared by hardware                       |

| bit 7   | GE: Timer1 Gate Enable bit                                                                                                               |

|---------|------------------------------------------------------------------------------------------------------------------------------------------|

| DIL 1   | If ON = 0:                                                                                                                               |

|         | This bit is ignored                                                                                                                      |

|         | If ON = 1:                                                                                                                               |

|         | 1 = Timer1 counting is controlled by the Timer1 gate function                                                                            |

|         | 0 = Timer1 is always counting                                                                                                            |

| bit 6   | GPOL: Timer1 Gate Polarity bit                                                                                                           |

|         | 1 = Timer1 gate is active-high (Timer1 counts when gate is high)                                                                         |

|         | 0 = Timer1 gate is active-low (Timer1 counts when gate is low)                                                                           |

| bit 5   | GTM: Timer1 Gate Toggle Mode bit                                                                                                         |

|         | 1 = Timer1 Gate Toggle mode is enabled                                                                                                   |

|         | 0 = Timer1 Gate Toggle mode is disabled and toggle flip-flop is cleared                                                                  |

|         | Timer1 gate flip-flop toggles on every rising edge.                                                                                      |

| bit 4   | GSPM: Timer1 Gate Single-Pulse Mode bit                                                                                                  |

|         | 1 = Timer1 Gate Single-Pulse mode is enabled                                                                                             |

|         | 0 = Timer1 Gate Single-Pulse mode is disabled                                                                                            |

| bit 3   | GGO/DONE: Timer1 Gate Single-Pulse Acquisition Status bit                                                                                |

|         | 1 = Timer1 gate single-pulse acquisition is ready, waiting for an edge                                                                   |

|         | 0 = Timer1 gate single-pulse acquisition has completed or has not been started<br>This bit is automatically cleared when GSPM is cleared |

| bit 2   | GVAL: Timer1 Gate Value Status bit                                                                                                       |

| DIL Z   | Indicates the current state of the Timer1 gate that could be provided to TMR1H:TMR1L                                                     |

|         | Unaffected by Timer1 Gate Enable (GE)                                                                                                    |

| bit 1-0 | Unimplemented: Read as '0'                                                                                                               |

| ~       | •:::::p:•:::•:::•::: \0.00 00 0                                                                                                          |

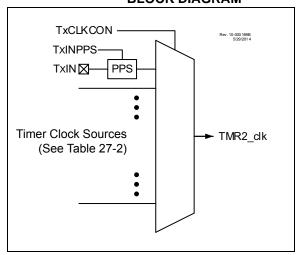

## FIGURE 27-2: TIMER2 CLOCK SOURCE BLOCK DIAGRAM

### 27.1 Timer2 Operation

Timer2 operates in three major modes:

- · Free Running Period

- · One-shot

- Monostable

Within each mode there are several options for starting, stopping, and reset. Table 27-1 lists the options.

In all modes, the TMR2 count register is incremented on the rising edge of the clock signal from the programmable prescaler. When TMR2 equals T2PR, a high level is output to the postscaler counter. TMR2 is cleared on the next clock input.

An external signal from hardware can also be configured to gate the timer operation or force a TMR2 count Reset. In Gate modes the counter stops when the gate is disabled and resumes when the gate is enabled. In Reset modes the TMR2 count is reset on either the level or edge from the external source.

The TMR2 and T2PR registers are both directly readable and writable. The TMR2 register is cleared and the T2PR register initializes to FFh on any device Reset. Both the prescaler and postscaler counters are cleared on the following events:

- · a write to the TMR2 register

- · a write to the T2CON register

- · any device Reset

- · External Reset Source event that resets the timer.

Note: TMR2 is not cleared when T2CON is written.

### 27.1.1 FREE RUNNING PERIOD MODE

The value of TMR2 is compared to that of the Period register, T2PR, on each TMR2\_clk cycle. When the two values match, the comparator resets the value of TMR2 to 00h on the next rising TMR2\_clk edge and increments

the output postscaler counter. When the postscaler count equals the value in the OUTPS<4:0> bits of the TMRxCON1 register, a one TMR2\_clk period wide pulse occurs on the TMR2\_postscaled output, and the postscaler count is cleared.

#### 27.1.2 ONE-SHOT MODE

The One-Shot mode is identical to the Free Running Period mode except that the ON bit is cleared and the timer is stopped when TMR2 matches T2PR and will not restart until the T2ON bit is cycled off and on. Postscaler OUTPS<4:0> values other than 0 are meaningless in this mode because the timer is stopped at the first period event and the postscaler is reset when the timer is restarted.

#### 27.1.3 MONOSTABLE MODE

Monostable modes are similar to One-Shot modes except that the ON bit is not cleared and the timer can be restarted by an external Reset event.

### 27.2 Timer2 Output

The Timer2 module's primary output is TMR2\_posts-caled, which pulses for a single TMR2\_clk period when the postscaler counter matches the value in the OUTPS bits of the TMR2CON register. The T2PR post-scaler is incremented each time the TMR2 value matches the T2PR value. This signal can be selected as an input to several other input modules:

- · The ADC module, as an Auto-conversion Trigger

- · COG. as an auto-shutdown source

In addition, the Timer2 is also used by the CCP module for pulse generation in PWM mode. Both the actual TMR2 value as well as other internal signals are sent to the CCP module to properly clock both the period and pulse width of the PWM signal. See Section 28.0 "Capture/Compare/PWM Modules" for more details on setting up Timer2 for use with the CCP, as well as the timing diagrams in Section 27.5 "Operation Examples" for examples of how the varying Timer2 modes affect CCP PWM output.

#### 27.3 External Reset Sources

In addition to the clock source, the Timer2 also takes in an external Reset source. This external Reset source is selected for Timer2 with the T2RST register. This source can control starting and stopping of the timer, as well as resetting the timer, depending on which mode the timer is in. The mode of the timer is controlled by the MODE<4:0> bits of the TMRxHLT register. Edge-Triggered modes require six Timer clock periods between external triggers. Level-Triggered modes require the triggering level to be at least three Timer clock periods long. External triggers are ignored while in Debug Freeze mode.

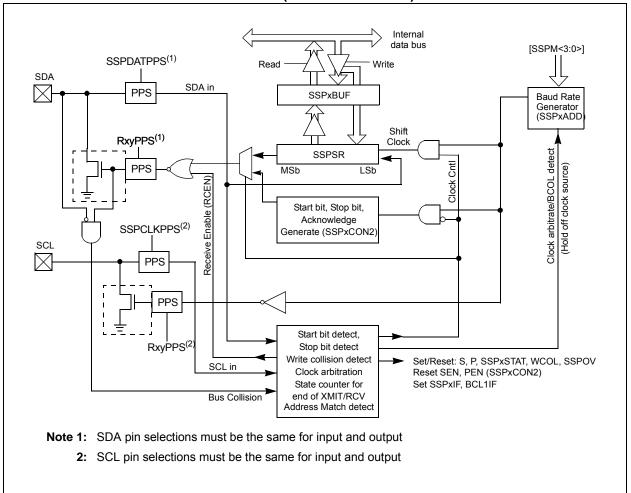

The I<sup>2</sup>C interface supports the following modes and features:

- · Master mode

- · Slave mode

- · Byte NACKing (Slave mode)

- · Limited multi-master support

- · 7-bit and 10-bit addressing

- · Start and Stop interrupts

- · Interrupt masking

- · Clock stretching

- · Bus collision detection

- · General call address matching

- · Address masking

- · Selectable SDA hold times

Figure 32-2 is a block diagram of the  $I^2C$  interface module in Master mode. Figure 32-3 is a diagram of the  $I^2C$  interface module in Slave mode.

- Note 1: In devices with more than one MSSP module, it is very important to pay close attention to SSPxCONx register names. SSPxCON1 and SSPxCON2 registers control different operational aspects of the same module, while SSPxCON1 and SSP2CON1 control the same features for two different modules.

- 2: Throughout this section, generic references to an MSSPx module in any of its operating modes may be interpreted as being equally applicable to MSSPx or MSSP2. Register names, module I/O signals, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module when required.

FIGURE 32-2: MSSP BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

#### 32.4.4 SDA HOLD TIME

The hold time of the SDA pin is selected by the SDAHT bit of the SSPxCON3 register. Hold time is the time SDA is held valid after the falling edge of SCL. Setting the SDAHT bit selects a longer 300 ns minimum hold time and may help on buses with large capacitance.

TABLE 32-1: I<sup>2</sup>C BUS TERMS

| TERM                | Description                                                                                                                                                                         |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmitter         | The device which shifts data out onto the bus.                                                                                                                                      |

| Receiver            | The device which shifts data in from the bus.                                                                                                                                       |

| Master              | The device that initiates a transfer, generates clock signals and terminates a transfer.                                                                                            |

| Slave               | The device addressed by the master.                                                                                                                                                 |

| Multi-master        | A bus with more than one device that can initiate data transfers.                                                                                                                   |

| Arbitration         | Procedure to ensure that only one master at a time controls the bus. Winning arbitration ensures that the message is not corrupted.                                                 |

| Synchronization     | Procedure to synchronize the clocks of two or more devices on the bus.                                                                                                              |

| Idle                | No master is controlling the bus, and both SDA and SCL lines are high.                                                                                                              |

| Active              | Any time one or more master devices are controlling the bus.                                                                                                                        |

| Addressed<br>Slave  | Slave device that has received a matching address and is actively being clocked by a master.                                                                                        |

| Matching<br>Address | Address byte that is clocked into a slave that matches the value stored in SSPxADD.                                                                                                 |

| Write Request       | Slave receives a matching address with R/W bit clear, and is ready to clock in data.                                                                                                |

| Read Request        | Master sends an address byte with the R/W bit set, indicating that it wishes to clock data out of the Slave. This data is the next and all following bytes until a Restart or Stop. |

| Clock Stretching    | When a device on the bus hold SCL low to stall communication.                                                                                                                       |

| Bus Collision       | Any time the SDA line is sampled low by the module while it is outputting and expected high state.                                                                                  |

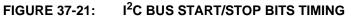

#### 32.4.5 START CONDITION

The I<sup>2</sup>C specification defines a Start condition as a transition of SDA from a high to a low state while SCL line is high. A Start condition is always generated by the master and signifies the transition of the bus from an Idle to an active state. Figure 32-12 shows wave forms for Start and Stop conditions.

#### 32.4.6 STOP CONDITION

A Stop condition is a transition of the SDA line from low-to-high state while the SCL line is high.

Note: At least one SCL low time must appear before a Stop is valid, therefore, if the SDA line goes low then high again while the SCL line stays high, only the Start condition is detected.

#### 32.4.7 RESTART CONDITION

A Restart is valid any time that a Stop would be valid. A master can issue a Restart if it wishes to hold the bus after terminating the current transfer. A Restart has the same effect on the slave that a Start would, resetting all slave logic and preparing it to clock in an address. The master may want to address the same or another slave. Figure 32-13 shows the wave form for a Restart condition.

In 10-bit Addressing Slave mode a Restart is required for the master to clock data out of the addressed slave. Once a slave has been fully addressed, matching both high and low address bytes, the master can issue a Restart and the high address byte with the  $R/\overline{W}$  bit set. The slave logic will then hold the clock and prepare to clock out data.

## 32.4.8 START/STOP CONDITION INTERRUPT MASKING

The SCIE and PCIE bits of the SSPxCON3 register can enable the generation of an interrupt in Slave modes that do not typically support this function. Slave modes where interrupt on Start and Stop detect are already enabled, these bits will have no effect.

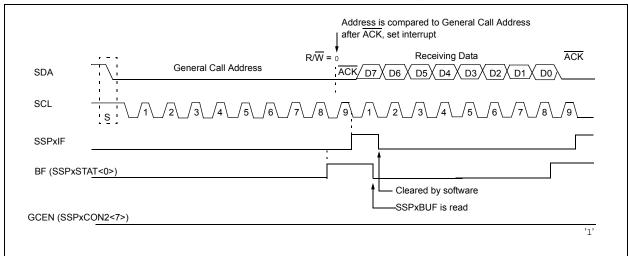

#### 32.5.8 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the I<sup>2</sup>C bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master device. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is a reserved address in the  $I^2C$  protocol, defined as address  $0 \times 0.0$ . When the GCEN bit of the SSPxCON2 register is set, the slave module will automatically ACK the reception of this address regardless of the value stored in SSPxADD. After the slave clocks in an address of all zeros with the R/W bit clear, an interrupt is generated and slave software can read SSPxBUF and respond. Figure 32-24 shows a general call reception sequence.

In 10-bit Address mode, the UA bit will not be set on the reception of the general call address. The slave will prepare to receive the second byte as data, just as it would in 7-bit mode.

If the AHEN bit of the SSPxCON3 register is set, just as with any other address reception, the slave hardware will stretch the clock after the eighth falling edge of SCL. The slave must then set its ACKDT value and release the clock with communication progressing as it would normally.

FIGURE 32-24: SLAVE MODE GENERAL CALL ADDRESS SEQUENCE

#### 32.5.9 SSP MASK REGISTER

An SSP Mask (SSPxMSK) register (Register 32-5) is available in I<sup>2</sup>C Slave mode as a mask for the value held in the SSPxSR register during an address comparison operation. A zero ('0') bit in the SSPxMSK register has the effect of making the corresponding bit of the received address a "don't care".

This register is reset to all '1's upon any Reset condition and, therefore, has no effect on standard SSP operation until written with a mask value.

The SSP Mask register is active during:

- 7-bit Address mode: address compare of A<7:1>.

- 10-bit Address mode: address compare of A<7:0>

only. The SSP mask has no effect during the

reception of the first (high) byte of the address.

## 33.2 Clock Accuracy with Asynchronous Operation

The factory calibrates the internal oscillator block output (INTOSC). However, the INTOSC frequency may drift as VDD or temperature changes, and this directly affects the asynchronous baud rate. Two methods may be used to adjust the baud rate clock, but both require a reference clock source of some kind.

The first (preferred) method uses the OSCTUNE register to adjust the INTOSC output. Adjusting the value in the OSCTUNE register allows for fine resolution changes to the system clock source. See Section 9.2.2.2 "Internal Oscillator Frequency Adjustment" for more information.

The other method adjusts the value in the Baud Rate Generator. This can be done automatically with the Auto-Baud Detect feature (see Section 33.3.1 "Auto-Baud Detect"). There may not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change in the peripheral clock frequency.

### FIGURE 33-8: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

### 33.3.4 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN bus standard. A Break character consists of a Start bit, followed by 12 '0' bits and a Stop bit.

To send a Break character, set the SENDB and TXEN bits of the TXxSTA register. The Break character transmission is then initiated by a write to the TXxREG. The value of data written to TXxREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

The TRMT bit of the TXxSTA register indicates when the transmit operation is active or idle, just as it does during normal transmission. See Figure 33-9 for the timing of the Break character sequence.

### 33.3.4.1 Break and Sync Transmit Sequence

The following sequence will start a message frame header made up of a Break, followed by an auto-baud Sync byte. This sequence is typical of a LIN bus master.

- 1. Configure the EUSART for the desired mode.

- Set the TXEN and SENDB bits to enable the Break sequence.

- 3. Load the TXxREG with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXxREG to load the Sync character into the transmit FIFO buffer.

- After the Break has been sent, the SENDB bit is reset by hardware and the Sync character is then transmitted.

When the TXxREG becomes empty, as indicated by the TXxIF, the next data byte can be written to TXxREG.

#### REGISTER 33-3: BAUDXCON: BAUD RATE CONTROL REGISTER

| R-0/0  | R-1/1 | U-0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0 |

|--------|-------|-----|---------|---------|-----|---------|---------|

| ABDOVF | RCIDL | _   | SCKP    | BRG16   | _   | WUE     | ABDEN   |

| bit 7  |       |     |         |         |     |         | bit 0   |

Legend:

bit 3

bit 2

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets '1' = Bit is set '0' = Bit is cleared

bit 7 ABDOVF: Auto-Baud Detect Overflow bit

Asynchronous mode:

1 = Auto-baud timer overflowed0 = Auto-baud timer did not overflow

Synchronous mode:

Don't care

bit 6 RCIDL: Receive Idle Flag bit

<u>Asynchronous mode</u>: 1 = Receiver is Idle

0 = Start bit has been received and the receiver is receiving

Synchronous mode:

Don't care

bit 5 **Unimplemented:** Read as '0'

bit 4 SCKP: Clock/Transmit Polarity Select bit

Asynchronous mode:

1 = Idle state for transmit (TX) is a low level 0 = Idle state for transmit (TX) is a high level

Synchronous mode:

1 = Idle state for clock (CK) is a high level 0 = Idle state for clock (CK) is a low level BRG16: 16-bit Baud Rate Generator bit

1 = 16-bit Baud Rate Generator is used0 = 8-bit Baud Rate Generator is used

Unimplemented: Read as '0'

bit 1 **WUE**: Wake-up Enable bit

Asynchronous mode:

1 = USART will continue to sample the Rx pin – interrupt generated on falling edge; bit cleared in hardware on following rising edge.

0 = RX pin not monitored nor rising edge detected

Synchronous mode:

Unused in this mode – value ignored

bit 0 ABDEN: Auto-Baud Detect Enable bit

Asynchronous mode:

1 = Enable baud rate measurement on the next character – requires reception of a SYNCH field (55h):

cleared in hardware upon completion

0 = Baud rate measurement disabled or completed

Synchronous mode:

Unused in this mode – value ignored

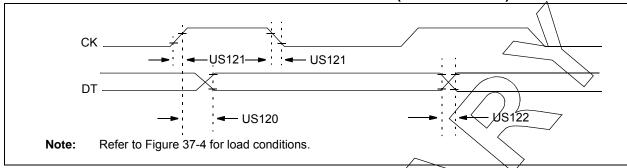

## FIGURE 37-15: EUSART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

## TABLE 37-21: EUSART SYNCHRONOUS TRANSMISSION CHARACTERISTICS

| Standard      | Operating Cor |                                   |                     |                |       |                                                  |

|---------------|---------------|-----------------------------------|---------------------|----------------|-------|--------------------------------------------------|

| Param.<br>No. | Symbol        | Characteristic                    | Min.                | Max.           | Units | Conditions                                       |

| US120         | TCKH2DTV      | SYNC XMIT (Master and Slave)      | _                   | 80             | ns    | $3.0 \text{V} \leq \text{VDD} \leq 5.5 \text{V}$ |

|               |               | Clock high to data-out valid      | /-/                 | 100            | ns    | $1.8V \le VDD \le 5.5V$                          |

| US121         | TCKRF         | Clock out rise time and fall time | / -/                | 45             | ns    | $3.0V \leq V \text{DD} \leq 5.5V$                |

|               |               | (Master mode)                     | 7                   | <b>&gt;</b> 50 | ns    | $1.8V \leq V \text{DD} \leq 5.5V$                |

| US122         | TDTRF         | Data-out rise time and fall time  | $\langle - \rangle$ | 45             | ns    | $3.0V \leq V \text{DD} \leq 5.5V$                |

|               |               |                                   | \                   | 50             | ns    | $1.8V \leq V \text{DD} \leq 5.5V$                |

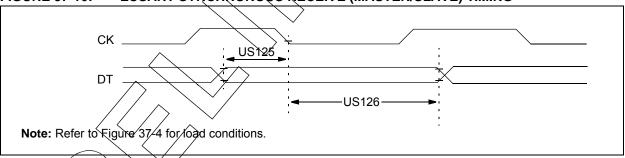

FIGURE 37-16: EUSART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

## TABLE 3/1-22: EUSART SYNCHRONOUS RECEIVE REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) |         |                                                                   |      |      |       |            |  |  |  |

|---------------------------------------------------------|---------|-------------------------------------------------------------------|------|------|-------|------------|--|--|--|

| Param.<br>No.                                           | Symbol  | Characteristic                                                    | Min. | Max. | Units | Conditions |  |  |  |

| ÚS125 Ti                                                | DTV2CKL | SYNC RCV (Master and Slave) Data-setup before CK ↓ (DT hold time) | 10   | _    | ns    |            |  |  |  |

| US126 TO                                                | CKL2DTL | Data-hold after CK $\downarrow$ (DT hold time)                    | 15   | _    | ns    |            |  |  |  |

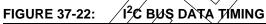

TABLE 37-24: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) |         |                 |              |      |     |      |       |                                                       |  |  |  |

|---------------------------------------------------------|---------|-----------------|--------------|------|-----|------|-------|-------------------------------------------------------|--|--|--|

| Param.<br>No.                                           | Symbol  | Characteristic  |              | Min. | Тур | Max. | Units | Conditions                                            |  |  |  |

| SP90*                                                   | Tsu:sta | Start condition | 100 kHz mode | 4700 | Ż   | _    | ns    | Only relevant for Repeated Start                      |  |  |  |

|                                                         |         | Setup time      | 400 kAz mode | 600  | _   | _    |       | condition                                             |  |  |  |

| SP91*                                                   | THD:STA | Start condition | 100 kHz mode | 4000 | _   | _    | ns    | After this period, the first clock pulse is generated |  |  |  |

|                                                         |         | Hold time       | 400 kHz mode | 600  | _   | _    |       |                                                       |  |  |  |

| SP92*                                                   | Tsu:sto | Stop condition  | 100 kHz mode | 4700 | _   | _    | ns    |                                                       |  |  |  |

|                                                         |         | Setup time      | 400 kHz mode | 600  | _   | _    |       |                                                       |  |  |  |

| SP93                                                    | THD:STO | Stop condition  | 100 kHz mode | 4000 | _   | _    | ns    |                                                       |  |  |  |

|                                                         |         | Hold time       | 400 kHz mode | 600  | _   | _    |       |                                                       |  |  |  |

<sup>\*</sup> These parameters are characterized but not tested.