### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 224 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15354-e-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **PIN ALLOCATION TABLES**

Preliminary

TABLE 3:

### 28-Pin PDIP/SOIC/SSOP 28-Pin UQFN Reference Comparator I/O<sup>(2)</sup> ADC C1IN0-2 RA0 27 ANA0 \_ C2IN0-C1IN1-RA1 3 28 ANA1 \_ \_ C2IN1-C1IN0+ RA2 4 1 ANA2 DAC10UT1 \_ \_ C2IN0+ RA3 5 2 ANA3 VREF+ C1IN1+ \_ DAC1REF+ RA4 6 3 ANA4 \_ RA5 7 4 ANA5 \_ \_ \_ RA6 10 7 ANA6 \_ \_ \_ RA7 9 6 ANA7 — \_ \_ RB0 21 18 ANB0 C2IN1+ \_ \_ C1IN3-RB1 22 19 ANB1 \_ \_ C2IN3-RB2 23 20 ANB2 \_ \_ \_

ANB3

ANB4

ADACT<sup>(1)</sup>

ANB5

ANB6

ANB7

C1IN2-

C2IN2-

\_

\_

\_

\_

\_

\_

\_

—

\_

\_

\_

\_

—

\_

RB3

RB4

RB5

RB6

RB7

21

22

23

24

25

24

25

26

27

28

1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Note

28-PIN ALLOCATION TABLE (PIC16(L)F15354, PIC16(L)F15355)

NC0

Timers

\_

\_

\_

**TOCKI**

\_

\_

\_

\_

\_

\_

\_

\_

T1G<sup>(1)</sup>

\_

\_

PWM

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

CCP

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

—

CWG

\_

\_

\_

\_

\_

\_

CWG1IN<sup>(1)</sup>

\_

\_

\_

\_

\_

\_

DAC

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

—

DAC10UT2

2: All digital output signals shown in this row are PPS remappable. These signals may be mapped to output onto one or more PORTx pin options.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers. 3:

These pins are configured for I<sup>2</sup>C logic levels. PPS assignments to the other pins will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C 4: specific or SMBus input buffer thresholds.

EUSART

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

TX2

CK2(1)

RX2

DT2<sup>(1)</sup>

ZCD

\_

\_

\_

\_

\_

\_

ZCD1

\_

\_\_\_\_

\_

—

MSSP

\_

\_

\_

SS1(1)

\_

\_

SS2(1)

SCK2.

SCL2(1,4)

SDA2,

SDI2(1,4)

\_

\_\_\_\_

\_

\_

\_

Interrupt

IOCA0

IOCA1

IOCA2

IOCA3

IOCA4

IOCA5

IOCA6

IOCA7

INT<sup>(1)</sup>

IOCB0

IOCB1

IOCB2

IOCB3

IOCB4

IOCB5

IOCB6

IOCB7

CLKR

\_

\_

—

\_

\_

\_

—

\_

\_

\_

\_

\_

\_

\_

—

\_

CLC

CLCIN0<sup>(1)</sup>

CLCIN1<sup>(1)</sup>

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

CLCIN2<sup>(1)</sup>

CLCIN3<sup>(1)</sup>

Pull-up

Υ

Υ

Υ

Υ

Υ

Υ

Υ

Υ

Υ

Υ

Υ

Υ

Υ

Υ

Υ

Υ

Basic

\_

\_\_\_\_

\_

\_

\_ CLKOUT

OSC2 CLKIN

OSC1

\_

\_

\_

\_

**ICSPCLK**

**ICSPDAT**

| <b>D</b> |

|----------|

|          |

| 6        |

|          |

|          |

|          |

|          |

| 535      |

| ω        |

| ا کر     |

|          |

| 5<br>J   |

| S<br>J   |

### TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

| Address      | Address     Name     Bit 7     Bit 6     Bit 5     Bit 4     Bit 3     Bit 2     Bit 1     Bit 0     Value on:<br>POR, BOR     Value on:<br>MCLR |  |  |  |  |  |  |  |  |   |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|---|--|--|--|

| Bank 13      | Bank 13                                                                                                                                          |  |  |  |  |  |  |  |  |   |  |  |  |

|              | CPU CORE REGISTERS; see Table 4-3 for specifics                                                                                                  |  |  |  |  |  |  |  |  |   |  |  |  |

| 68Ch<br>69Fh | — Unimplemented —                                                                                                                                |  |  |  |  |  |  |  |  | _ |  |  |  |

| Legend:      |                                                                                                                                                  |  |  |  |  |  |  |  |  |   |  |  |  |

| Address | Name     | Bit 7    | Bit 6    | Bit 5       | Bit 4         | Bit 3             | Bit 2     | Bit 1       | Bit 0    | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------|----------|----------|----------|-------------|---------------|-------------------|-----------|-------------|----------|-----------------------|----------------------------|

| Bank 60 |          |          |          |             |               |                   |           |             |          |                       |                            |

|         |          |          |          | CPU COF     | RE REGISTERS; | see Table 4-3 for | specifics |             |          |                       |                            |

| 1E0Ch   | _        |          |          |             | Unimple       | mented            |           |             |          |                       |                            |

| 1E0Dh   | _        |          |          |             | Unimple       | mented            |           |             |          |                       |                            |

| 1E0Eh   | _        |          |          |             | Unimple       | mented            |           |             |          |                       |                            |

| 1E0Fh   | CLCDATA  | _        | _        |             | _             | MLC4OUT           | MLC3OUT   | MLC2OUT     | MLC1OUT  | xxxx                  | uuuu                       |

| 1E10h   | CLCCON   | LC1EN    | —        | LC10UT      | LC1INTP       | LC1INTN           |           | LC1MODE<2:0 | )>       | 0-00 0000             | 0-00 0000                  |

| 1E11h   | CLC1POL  | LC1POL   | _        | _           | —             | LC1G4POL          | LC1G3POL  | LC1G2POL    | LC1G1POL | 0 xxxx                | 0 uuuu                     |

| 1E12h   | CLC1SEL0 | _        | _        | LC1D1S<5:0> |               |                   |           |             |          | xx xxxx               | uu uuuu                    |

| 1E13h   | CLC1SEL1 | _        | —        |             | LC1D2S<5:0>   |                   |           |             |          |                       | uu uuu                     |

| 1E14h   | CLC1SEL2 | _        | —        |             |               | LC1               | 03S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E15h   | CLC1SEL3 | _        | —        | LC1D4S<5:0> |               |                   |           |             |          | xx xxxx               | uu uuu                     |

| 1E16h   | CLC1GLS0 | LC1G1D4T | LC1G4D3N | LC1G1D3T    | LC1G1D3N      | LC1G1D2T          | LC1G1D2N  | LC1G1D1T    | LC1G1D1N | xxxx xxxx             | uuuu uuu                   |

| 1E17h   | CLC1GLS1 | LC1G2D4T | LC1G4D3N | LC1G2D3T    | LC1G2D3N      | LC1G2D2T          | LC1G2D2N  | LC1G2D1T    | LC1G2D1N | xxxx xxxx             | uuuu uuu                   |

| 1E18h   | CLC1GLS2 | LC1G3D4T | LC1G4D3N | LC1G3D3T    | LC1G3D3N      | LC1G3D2T          | LC1G3D2N  | LC1G3D1T    | LC1G3D1N | xxxx xxxx             | uuuu uuu                   |

| 1E19h   | CLC1GLS3 | LC1G4D4T | LC1G4D3N | LC1G4D3T    | LC1G4D3N      | LC1G4D2T          | LC1G4D2N  | LC1G4D1T    | LC1G4D1N | xxxx xxxx             | uuuu uuu                   |

| 1E1Ah   | CLC2CON  | LC2EN    | —        | LC2OUT      | LC2INTP       | LC2INTN           |           | LC2MODE<2:0 | )>       | 0-00 0000             | 0-00 000                   |

| 1E1Bh   | CLC2POL  | LC2POL   | _        | _           | —             | LC2G4POL          | LC2G3POL  | LC2G2POL    | LC2G1POL | 0 xxxx                | 0 uuu                      |

| 1E1Ch   | CLC2SEL0 | _        | _        |             |               | LC2               | 01S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E1Dh   | CLC2SEL1 | _        | —        |             |               | LC2               | )2S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E1Eh   | CLC2SEL2 | _        |          |             |               | LC2               | 03S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E1Fh   | CLC2SEL3 | _        | _        |             |               | LC2               | 04S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E20h   | CLC2GLS0 | LC2G1D4T | LC2G4D3N | LC2G1D3T    | LC2G1D3N      | LC2G1D2T          | LC2G1D2N  | LC2G1D1T    | LC2G1D1N | xxxx xxxx             | uuuu uuu                   |

| 1E21h   | CLC2GLS1 | LC2G2D4T | LC2G4D3N | LC2G2D3T    | LC2G2D3N      | LC2G2D2T          | LC2G2D2N  | LC2G2D1T    | LC2G2D1N | xxxx xxxx             | นนนน นนนเ                  |

| 1E22h   | CLC2GLS2 | LC2G3D4T | LC2G4D3N | LC2G3D3T    | LC2G3D3N      | LC2G3D2T          | LC2G3D2N  | LC2G3D1T    | LC2G3D1N | xxxx xxxx             | uuuu uuu                   |

| 1E23h   | CLC2GLS3 | LC2G4D4T | LC2G4D3N | LC2G4D3T    | LC2G4D3N      | LC2G4D2T          | LC2G4D2N  | LC2G4D1T    | LC2G4D1N | xxxx xxxx             | uuuu uuu                   |

| 1E24h   | CLC3CON  | LC3EN    | _        | LC3OUT      | LC3INTP       | LC3INTN           |           | LC3MODE     |          | 0-00 0000             | 0-00 000                   |

| 1E25h   | CLC3POL  | LC3POL   | —        | -           | —             | LC3G4POL          | LC3G3POL  | LC3G2POL    | LC3G1POL | 0 xxxx                | 0 uuu                      |

| 1E26h   | CLC3SEL0 | _        | _        |             | •             | LC3E              | 01S<5:0>  |             |          | xx xxxx               | uu uuuu                    |

| 1E27h   | CLC3SEL1 | _        | —        |             |               | LC3E              | )2S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E28h   | CLC3SEL2 | _        | _        |             |               | LC3               | 03S<5:0>  |             |          | xx xxxx               | uu uuuu                    |

| 1E29h   | CLC3SEL3 | _        | _        |             |               | LC3               | 04S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E2Ah   | CLC3GLS0 | LC3G1D4T | LC3G4D3N | LC3G1D3T    | LC3G1D3N      | LC3G1D2T          | LC3G1D2N  | LC3G1D1T    | LC3G1D1N | XXXX XXXX             | uuuu uuu                   |

### TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', x = reserved. Shaded locations unimplemented, read as '0'.

| Address   | Name   | Bit 7         | Bit 6 | Bit 5   | Bit 4         | Bit 3            | Bit 2       | Bit 1   | Bit 0   | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|-----------|--------|---------------|-------|---------|---------------|------------------|-------------|---------|---------|-----------------------|----------------------------|

| Bank 62   |        |               |       |         |               |                  |             |         |         |                       |                            |

|           |        |               |       | CPU COF | RE REGISTERS; | see Table 4-3 fo | r specifics |         |         |                       |                            |

| 1F0Ch     | _      |               |       |         | Unimple       | mented           |             |         |         |                       |                            |

| 1F0Dh     | _      |               |       |         | Unimple       | mented           |             |         |         |                       |                            |

| 1F0Eh     | _      |               |       |         | Unimple       | mented           |             |         |         |                       |                            |

| 1F0Fh     | _      |               |       |         | Unimple       | mented           |             |         |         |                       |                            |

| 1F10h     | RA0PPS | —             | —     | —       |               |                  | RA0PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F11h     | RA1PPS | —             | —     | —       |               |                  | RA1PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F12h     | RA2PPS | —             | _     | —       |               |                  | RA2PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F13h     | RA3PPS | —             | _     | —       |               |                  | RA3PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F14h     | RA4PPS | -             | -     | —       |               |                  |             | 00 0000 | uu uuuu |                       |                            |

| 1F15h     | RA5PPS | —             | _     | _       |               | RA5PPS<4:0>      |             |         |         |                       | uu uuuu                    |

| 1F16h     | RA6PPS | —             | _     | _       |               | RA6PPS<4:0>      |             |         |         |                       | uu uuuu                    |

| 1F17h     | RA7PPS | _             | _     | _       | RA7PPS<4:0>   |                  |             |         |         | 00 0000               | uu uuuu                    |

| 1F18h     | RB0PPS | _             | _     | _       | RB0PPS<4:0>   |                  |             |         |         | 00 0000               | uu uuuu                    |

| 1F19h     | RB1PPS | _             | _     | _       | RB1PPS<4:0>   |                  |             |         |         | 00 0000               | uu uuuu                    |

| 1F1Ah     | RB2PPS | _             | _     | _       |               | RB2PPS<4:0>      |             |         |         |                       | uu uuuu                    |

| 1F1Bh     | RB3PPS | _             | _     | _       |               |                  | RB3PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F1Ch     | RB4PPS | _             | _     | _       |               |                  | RB4PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F1Dh     | RB5PPS | _             | _     | _       |               |                  | RB5PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F1Eh     | RB6PPS | _             | _     | _       |               |                  | RB6PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F1Fh     | RB7PPS | _             | _     | _       |               |                  | RB7PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F20h     | RC0PPS | _             | _     | _       |               |                  | RC0PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F21h     | RC1PPS | _             | _     | _       |               |                  | RC1PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F22h     | RC2PPS | —             | _     | —       |               |                  | RC2PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F23h     | RC3PPS | —             | _     | —       |               |                  | RC3PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F24h     | RC4PPS | —             | _     | —       |               |                  | RC4PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F25h     | RC5PPS | —             | _     | —       |               |                  | RC5PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F26h     | RC6PPS | —             | _     | —       |               |                  | RC6PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F27h     | RC7PPS | —             | _     | —       |               |                  | RC7PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F28h<br> | _      | Unimplemented |       |         |               |                  |             |         |         | -                     | _                          |

### TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

# PIC16(L)F15354/55

| R/W-0/0              | R/W-0/0                                                                                                                                                                                                                | R/W-0/0                                                                                                                                                                                                                                         | R/W-0/0        | R/W-0/0         | R/W-0/0             | U-0              | U-0          |  |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|---------------------|------------------|--------------|--|--|

| EXTOEN               | HFOEN                                                                                                                                                                                                                  | MFOEN                                                                                                                                                                                                                                           | LFOEN          | SOSCEN          | ADOEN               | —                | —            |  |  |

| bit 7                |                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                 |                |                 |                     |                  | bit 0        |  |  |

|                      |                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                 |                |                 |                     |                  |              |  |  |

| Legend:              |                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                 |                |                 |                     |                  |              |  |  |

| R = Readable         | bit                                                                                                                                                                                                                    | W = Writable                                                                                                                                                                                                                                    | bit            | U = Unimpler    | nented bit, read    | d as '0'         |              |  |  |

| u = Bit is unchanged |                                                                                                                                                                                                                        | x = Bit is unkr                                                                                                                                                                                                                                 | nown           | -n/n = Value a  | at POR and BO       | R/Value at all o | other Resets |  |  |

| '1' = Bit is set     |                                                                                                                                                                                                                        | '0' = Bit is clea                                                                                                                                                                                                                               | ared           |                 |                     |                  |              |  |  |

| bit 7                | 1 = EXTOS                                                                                                                                                                                                              | ternal Oscillato<br>C is explicitly e<br>C could be ena                                                                                                                                                                                         | nabled, operat | ing as specifie | (1)<br>d by FEXTOSC | ;                |              |  |  |

| bit 6                | <ul> <li><b>HFOEN:</b> HFINTOSC Oscillator Manual Request Enable bit</li> <li>1 = HFINTOSC is explicitly enabled, operating as specified by OSCFRQ</li> <li>0 = HFINTOSC could be enabled by another module</li> </ul> |                                                                                                                                                                                                                                                 |                |                 |                     |                  |              |  |  |

| bit 5                | 1 = MFINTOS                                                                                                                                                                                                            | NTOSC Oscilla<br>SC is explicitly of SC could be en                                                                                                                                                                                             | enabled        |                 | bit                 |                  |              |  |  |

| bit 4                | 1 = LFINTO                                                                                                                                                                                                             | <ul> <li>0 = MFINTOSC could be enabled by another module</li> <li>LFOEN: LFINTOSC (31 kHz) Oscillator Manual Request Enable bit</li> <li>1 = LFINTOSC is explicitly enabled</li> <li>0 = LFINTOSC could be enabled by another module</li> </ul> |                |                 |                     |                  |              |  |  |

| bit 3                | 1 = Seconda                                                                                                                                                                                                            | <ul> <li>SOSCEN: Secondary (Timer1) Oscillator Manual Request bit</li> <li>1 = Secondary oscillator is explicitly enabled, operating as specified by SOSCPWR</li> <li>0 = Secondary oscillator could be enabled by another module</li> </ul>    |                |                 |                     |                  |              |  |  |

| bit 2                | ADOEN: FRC Oscillator Manual Request Enable bit<br>1 = FRC is explicitly enabled<br>0 = FRC could be enabled by another module                                                                                         |                                                                                                                                                                                                                                                 |                |                 |                     |                  |              |  |  |

| bit 1-0              | Unimplemen                                                                                                                                                                                                             | tad. Dood os '                                                                                                                                                                                                                                  | o'             |                 |                     |                  |              |  |  |

### REGISTER 9-5: OSCEN: OSCILLATOR MANUAL ENABLE REGISTER

| FIGURE 10-2:                                                                  | INTERRUPT LA                                    | TENCY  |                   |                    |                |                              |  |  |  |  |

|-------------------------------------------------------------------------------|-------------------------------------------------|--------|-------------------|--------------------|----------------|------------------------------|--|--|--|--|

|                                                                               |                                                 |        |                   |                    |                | Rev. 10-030269E<br>8/31/2016 |  |  |  |  |

|                                                                               | 3   Q4 Q1   Q2   Q3   Q4                        |        | Q1   Q2   Q3   Q4 |                    |                | Q1   Q2   Q3   Q4            |  |  |  |  |

|                                                                               |                                                 |        |                   |                    |                |                              |  |  |  |  |

| INT<br>pin Valid Interrupt<br>window <sup>(1)</sup> 1 Cycle Instruction at PC |                                                 |        |                   |                    |                |                              |  |  |  |  |

| Fetch PC -                                                                    | 1 PC                                            | PC + 1 |                   | PC = 0x0004        | PC = 0x0005    | PC = 0x0006                  |  |  |  |  |

| Execute PC -                                                                  | 21 PC - 1                                       | РС     | NOP               | NOP                | PC = 0x0004    | PC = 0x0005                  |  |  |  |  |

| Indeterminate Latency Latency                                                 |                                                 |        |                   |                    |                |                              |  |  |  |  |

|                                                                               | upt may occur at any t<br>interrupt may occur a |        |                   | ow, the actual lat | ency can vary. |                              |  |  |  |  |

|                           | Q1   Q2   Q3   Q4                               | Q1   Q2   Q3   Q4     | Q1   Q2   Q3   Q4       | Q1   Q2   Q3   Q4                     | 4 Q1   Q2   Q3   Q4     |

|---------------------------|-------------------------------------------------|-----------------------|-------------------------|---------------------------------------|-------------------------|

| OSC1                      |                                                 |                       |                         |                                       |                         |

|                           | (4)                                             |                       |                         |                                       |                         |

| INT pin                   |                                                 | , (1)                 | 1<br>1                  | 1                                     | <u> </u>                |

| INTF                      | , (1) (5)                                       |                       | Interrupt Latency (2)   | -<br>-<br>-<br>-<br>-<br>-<br>-       |                         |

| GIE                       |                                                 |                       |                         | · · · · · · · · · · · · · · · · · · · |                         |

| INSTRUCTION               | <br>I FLOW                                      |                       |                         | <u>-</u>                              |                         |

| PC                        | C PC                                            | PC + 1                | PC + 1                  | 0004h                                 | X0005h                  |

| Instruction (<br>Fetched  | Inst (PC)                                       | Inst (PC + 1)         | -                       | Inst (0004h)                          | Inst (0005h)            |

| Instruction (<br>Executed | Inst (PC – 1)                                   | Inst (PC)             | Forced NOP              | Forced NOP                            | Inst (0004h)            |

| Note 1: IN                | NTF flag is sampled here                        | e (every Q1).         |                         |                                       |                         |

|                           | synchronous interrupt la atency is the same whe |                       |                         |                                       | instruction cycle time. |

| 3: F                      | or minimum width of IN                          | pulse, refer to AC sp | ecifications in Section | n 37.0 "Electrical Spe                | ecifications".          |

4: INTF is enabled to be set any time during the Q4-Q1 cycles.

| U-0                  | R/W-0/0                                                                                      | R/W-0/0                                                                                             | R/W/HC-0/0                                                | R/W/HC-x/q                                                    | R/W-0/0          | R/S/HC-0/0                                 | R/S/HC-0/0         |

|----------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------|------------------|--------------------------------------------|--------------------|

| _                    | NVMREGS                                                                                      | LWLO                                                                                                | FREE                                                      | WRERR <sup>(1,2,3)</sup>                                      | WREN             | WR <sup>(4,5,6)</sup>                      | RD                 |

| bit 7                |                                                                                              |                                                                                                     |                                                           |                                                               |                  |                                            | bit                |

|                      |                                                                                              |                                                                                                     |                                                           |                                                               |                  |                                            |                    |

| Legend:              |                                                                                              |                                                                                                     |                                                           |                                                               |                  |                                            |                    |

| R = Readable         | e bit                                                                                        | W = Writable b                                                                                      | it                                                        | U = Unimpleme                                                 | nted bit, read a | s '0'                                      |                    |

| S = Bit can or       | nly be set                                                                                   | x = Bit is unkno                                                                                    | own                                                       | -n/n = Value at I                                             | POR and BOR/     | Value at all other F                       | Resets             |

| '1' = Bit is set     |                                                                                              | '0' = Bit is clea                                                                                   | red                                                       | HC = Bit is clear                                             | red by hardware  | e                                          |                    |

| bit 7                | Unimplement                                                                                  | ed: Read as '0'                                                                                     |                                                           |                                                               |                  |                                            |                    |

| bit 6                |                                                                                              | -                                                                                                   |                                                           | and Device ID Rec                                             | gisters          |                                            |                    |

| bit 5                | When FREE =<br>1 = The next                                                                  | WR command u<br>WR command w                                                                        | odates the write                                          |                                                               | l within the row | ; no memory opera                          | ation is initiated |

| bit 4                | When NVMRE<br>1 = Performs<br>address is                                                     | rase Enable bit<br><u>GS:NVMADR po</u><br>an erase operat<br>s erased (to all 1<br>operations have  | ion with the nex<br>s) to prepare for                     | t WR command; f<br>writing.                                   | he 32-word pse   | eudo-row containii                         | ng the indicate    |

| bit 3                | This bit is norm<br>1 = A write op<br>NVMADR                                                 | ram/Erase Error<br>nally set by hardy<br>peration was inte<br>points to a write<br>ram or erase ope | ware.<br>errupted by a Re<br>e-protected addr             | ess.                                                          | nlock sequence   | e, or WR was writt                         | en to one whi      |

| bit 2                | 1 = Allows pro                                                                               | am/Erase Enable<br>ogram/erase cyc<br>ogramming/eras                                                | les                                                       | -lash                                                         |                  |                                            |                    |

| bit 1                | WR: Write Cor<br><u>When NVMRE</u><br>1 = Initiates th                                       |                                                                                                     | n <u>ts to a PFM loc</u><br>cated by Table 1              | <u>ation</u> :<br>3-4                                         |                  |                                            |                    |

| bit 0                | RD: Read Con<br>1 = Initiates a<br>bit is clea                                               | trol bit <sup>(7)</sup><br>read at address                                                          | = NVMADR1, a<br>eration is compl                          | nd loads data to N<br>ete. The bit can o                      |                  | akes one instructio<br>cleared) in softwar |                    |

| 2: B<br>3: B<br>4: T | it is undefined while<br>it must be cleared I<br>it may be written to<br>his bit can only be | e WR = 1.<br>by software; harc<br>o '1' by software i                                               | lware will not cle<br>n order to imple<br>he unlock seque | ear this bit.<br>ment test sequen<br>ence of <b>Section 1</b> | 3.3.2 "NVM Ur    | nlock Sequence".                           |                    |

### REGISTER 13-5: NVMCON1: NONVOLATILE MEMORY CONTROL 1 REGISTER

5: Operations are self-timed, and the WR bit is cleared by hardware when complete.6: Once a write operation is initiated, setting this bit to zero will have no effect.

### 14.5 Register Definitions: PORTB

### REGISTER 14-9: PORTB: PORTB REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RB7     | RB6     | RB5     | RB4     | RB3     | RB2     | RB1     | RB0     |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend: |         |         |         |         |         |         |         |

| Legenu.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

### bit 7-0 **RB<7:0>**: PORTB I/O Value bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. The actual I/O pin values are read from the PORTB register.

### REGISTER 14-10: TRISB: PORTB TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISB7  | TRISB6  | TRISB5  | TRISB4  | TRISB3  | TRISB2  | TRISB1  | TRISB0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 TRISB<7:0>: PORTB Tri-State Control bit

- 1 = PORTB pin configured as an input (tri-stated)

- 0 = PORTB pin configured as an output

### 19.2.1 CALIBRATION

### **Single-Point Calibration**

Single-point calibration is performed by application software using Equation 19-1 and the assumed Mt. A reading of VTSENSE at a known temperature is taken, and the theoretical temperature is calculated by temporarily setting TOFFSET = 0. Then TOFFSET is computed as the difference of the actual and calculated temperatures. Finally, TOFFSET is stored in nonvolatile memory within the device, and is applied to future readings to gain a more accurate measurement.

The magnitude of error in a typical single-point calibration is approximately 3-4°C.

- Note 1: The TOFFSET value may be determined by the user with a temperature test, or it can be based on the Microchip-supplied data from the DIA table. Please refer to Section 6.0 "Device Information Area" for more information.

- 2: Although the measurement range is -40°C to +125 °C, due to the variations in the value of Mv, the single-point calculated TSENSE value may indicate a temperature from -140°C to +225°C, before the calibration offset is applied.

### Higher-Order Calibration

If the application requires more precise temperature measurement, additional calibrations steps will be necessary. For these applications, two-point or threepoint calibration is recommended.

### 19.2.2 TEMPERATURE RESOLUTION

The resolution of the ADC reading, Ma (°C/count), depends on both the ADC resolution N and the reference voltage used for conversion, as shown in Equation 19-2. It is recommended to use the smallest VREF value, such as 2.048 FVR reference voltage, instead of VDD.

| Note: | Refer   | to   | Sec    | tion 3 | 37.0      | "Electrical |

|-------|---------|------|--------|--------|-----------|-------------|

|       | Specifi | ons" | for    | FVR    | reference |             |

|       | voltage | accu | iracy. |        |           |             |

### EQUATION 19-2: TEMPERATURE RESOLUTION (°C/LSb)

$$Ma = \frac{V_{REF}}{2^N} \times Mt$$

$$Ma = \frac{\frac{V_{REF}}{2^{N}}}{Mv}$$

Where:

Mv = sensor voltage sensitivity (V/°C)

VREF = Reference voltage of the ADC module (in Volts)

N = Resolution of the ADC

### EXAMPLE 19-1: TEMPERATURE RESOLUTION

Using VREF = 2.048V and a 10-bit ADC provides 2 mV/LSb measurements.

Because Mv can vary from -2.40 to -2.65 mV/°C, the range of Ma = 0.75 to 0.83 °C/LSb.

### 19.3 ADC Acquisition Time

To ensure accurate temperature measurements, the user must wait a fixed amount of time for the ADC value to settle, after the ADC input multiplexer is connected to the temperature indicator output, before the conversion is performed. This specification is provided in **Section 37.0 "Electrical Specifications"**.

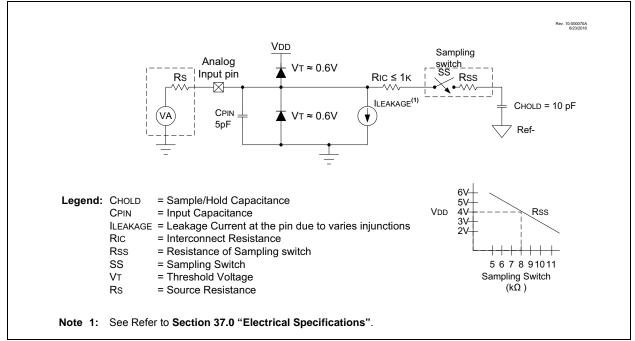

### FIGURE 20-4: ANALOG INPUT MODEL

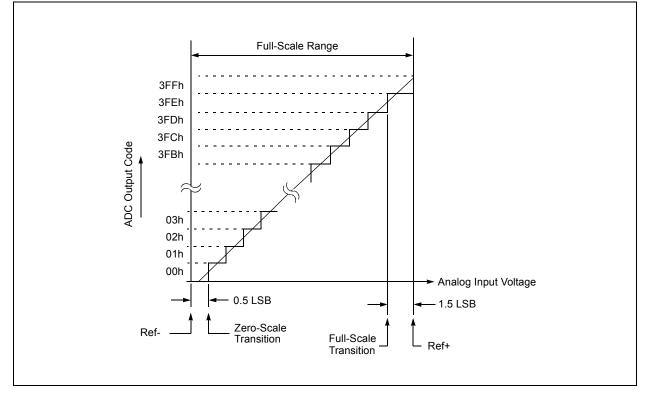

### FIGURE 20-5: ADC TRANSFER FUNCTION

### 22.1 NCO OPERATION

The NCO operates by repeatedly adding a fixed value to an accumulator. Additions occur at the input clock rate. The accumulator will overflow with a carry periodically, which is the raw NCO output (NCO\_overflow). This effectively reduces the input clock by the ratio of the addition value to the maximum accumulator value. See Equation 22-1.

The NCO output can be further modified by stretching the pulse or toggling a flip-flop. The modified NCO output is then distributed internally to other peripherals and can be optionally output to a pin. The accumulator overflow also generates an interrupt (NCO\_overflow).

The NCO period changes in discrete steps to create an average frequency.

### EQUATION 22-1: NCO OVERFLOW FREQUENCY

FOVERFLOW= <u>NCO Clock Frequency × Increment Value</u>

$2^{20}$

### 22.1.1 NCO CLOCK SOURCES

Clock sources available to the NCO include:

- HFINTOSC

- Fosc

- LC1\_out

- LC2\_out

- LC3\_out

- LC4\_out

- MFINTOSC (500 kHz)

- MFINTOSC (32 kHz)

- SOSC

- CLKR

The NCO clock source is selected by configuring the N1CKS<2:0> bits in the NCO1CLK register.

### 22.1.2 ACCUMULATOR

The accumulator is a 20-bit register. Read and write access to the accumulator is available through three registers:

- NCO1ACCL

- NCO1ACCH

- NCO1ACCU

### 22.1.3 ADDER

The NCO Adder is a full adder, which operates synchronously from the source clock. The addition of the previous result and the increment value replaces the accumulator value on the rising edge of each input clock.

### 22.1.4 INCREMENT REGISTERS

The increment value is stored in three registers making up a 20-bit incrementer. In order of LSB to MSB they are:

- NCO1INCL

- NCO1INCH

- NCO1INCU

When the NCO module is enabled, the NCO1INCU and NCO1INCH registers should be written first, then the NCO1INCL register. Writing to the NCO1INCL register initiates the increment buffer registers to be loaded simultaneously on the second rising edge of the NCO clk signal.

The registers are readable and writable. The increment registers are double-buffered to allow value changes to be made without first disabling the NCO module.

When the NCO module is disabled, the increment buffers are loaded immediately after a write to the increment registers.

Note: The increment buffer registers are not useraccessible.

2: In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge of the clock.

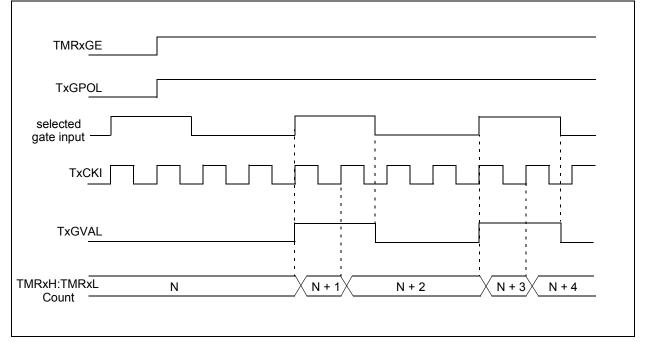

### FIGURE 26-3: TIMER1 GATE ENABLE MODE

© 2016 Microchip Technology Inc.

### 27.5.2 HARDWARE GATE MODE

The Hardware Gate modes operate the same as the Software Gate mode except the TMRx\_ers external signal gates the timer. When used with the CCP the gating extends the PWM period. If the timer is stopped when the PWM output is high then the duty cycle is also extended.

When MODE<4:0> = 00001 then the timer is stopped when the external signal is high. When MODE<4:0> = 00010 then the timer is stopped when the external signal is low.

Figure 27-5 illustrates the Hardware Gating mode for MODE<4:0> = 00001 in which a high input level starts the counter.

|                                 | Rev. 10.000 1998<br>\$500/2014                                                                                                                                                                                                                                                                                            |  |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MODE                            | 0b00001                                                                                                                                                                                                                                                                                                                   |  |

| TMRx_clk                        |                                                                                                                                                                                                                                                                                                                           |  |

| TMRx_ers_                       |                                                                                                                                                                                                                                                                                                                           |  |

| PRx                             | 5                                                                                                                                                                                                                                                                                                                         |  |

| TMRx(                           | $0 \qquad \begin{pmatrix} 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 1 \\ 1 \\ 2 \\ 1 \\ 1 \\ 1 \\ 2 \\ 1 \\ 1$ |  |

| TMRx_postscaled_                |                                                                                                                                                                                                                                                                                                                           |  |

| PWM Duty<br>Cycle<br>PWM Output | 3                                                                                                                                                                                                                                                                                                                         |  |

| Name     | Bit 7                                | Bit 6                                | Bit 5             | Bit 4        | Bit 3  | Bit 2       | Bit 1    | Bit 0  | Register<br>on Page |  |  |

|----------|--------------------------------------|--------------------------------------|-------------------|--------------|--------|-------------|----------|--------|---------------------|--|--|

| INTCON   | GIE                                  | PEIE                                 |                   |              | —      | _           | —        | INTEDG | 119                 |  |  |

| PIR4     | —                                    | _                                    | _                 | _            | —      | _           | TMR2IF   | TMR1IF | 132                 |  |  |

| PIE4     | —                                    | —                                    | _                 | _            | _      | _           | TMR2IE   | TMR1IE | 124                 |  |  |

| CCP1CON  | EN                                   | —                                    | OUT               | FMT          |        | MODE        | =<3:0>   |        | 317                 |  |  |

| CCP1CAP  |                                      |                                      |                   |              |        |             | CTS<2:0> |        | 319                 |  |  |

| CCPR1L   | Capture/Compare/PWM Register 1 (LSB) |                                      |                   |              |        |             |          |        |                     |  |  |

| CCPR1H   | Capture/Con                          | Capture/Compare/PWM Register 1 (MSB) |                   |              |        |             |          |        |                     |  |  |

| CCP2CON  | EN                                   | —                                    | OUT FMT MODE<3:0> |              |        |             |          |        |                     |  |  |

| CCP2CAP  | _                                    | _                                    | _                 | _            | _      |             | CTS<2:0> |        | 319                 |  |  |

| CCPR2L   | Capture/Con                          | npare/PWM F                          | Register 1 (LS    | B)           |        |             |          |        | 319                 |  |  |

| CCPR2H   | Capture/Con                          | npare/PWM F                          | Register 1 (MS    | SB)          |        |             |          |        | 319                 |  |  |

| CCPTMRS0 | _                                    | _                                    | _                 | _            | C2TSE  | L<1:0>      | C1TSE    | L<1:0> | 320                 |  |  |

| CCPTMRS1 | _                                    | _                                    | _                 | _            | P2TSE  | L<1:0>      | C1TSE    | L<1:0> | 321                 |  |  |

| CCP1PPS  | _                                    | _                                    |                   |              | CCP1PI | PS<5:0>     |          |        | 196                 |  |  |

| CCP2PPS  | _                                    | _                                    |                   |              | CCP2PI | PS<5:0>     |          |        | 196                 |  |  |

| RxyPPS   | —                                    | —                                    | — RxyPPS<4:0>     |              |        |             |          |        |                     |  |  |

| ADACT    | —                                    | —                                    | _                 | — ADACT<3:0> |        |             |          |        | 231                 |  |  |

| CLCxSELy | _                                    | —                                    | _                 |              |        | LCxDyS<4:0> | >        |        | 363                 |  |  |

| CWG1ISM  | _                                    | —                                    | _                 | —            |        | IS<         | 3:0>     |        | 352                 |  |  |

### TABLE 28-5: SUMMARY OF REGISTERS ASSOCIATED WITH CCPx

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the CCP module.

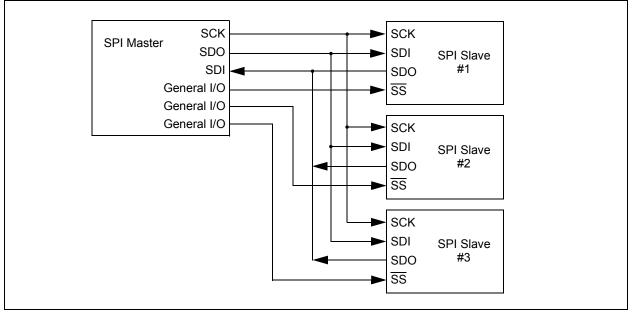

### FIGURE 32-4: SPI MASTER AND MULTIPLE SLAVE CONNECTION

### 32.2.1 SPI MODE REGISTERS

The MSSP module has five registers for SPI mode operation. These are:

- MSSP STATUS register (SSPxSTAT)

- MSSP Control register 1 (SSPxCON1)

- MSSP Control register 3 (SSPxCON3)

- MSSP Data Buffer register (SSPxBUF)

- MSSP Address register (SSPxADD)

- MSSP Shift register (SSPxSR) (Not directly accessible)

SSPxCON1 and SSPxSTAT are the control and status registers in SPI mode operation. The SSPxCON1 register is readable and writable. The lower six bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write.

In one SPI master mode, SSPxADD can be loaded with a value used in the Baud Rate Generator. More information on the Baud Rate Generator is available in **Section 32.7 "Baud Rate Generator"**.

SSPxSR is the shift register used for shifting data in and out. SSPxBUF provides indirect access to the SSPxSR register. SSPxBUF is the buffer register to which data bytes are written, and from which data bytes are read.

In receive operations, SSPxSR and SSPxBUF together create a buffered receiver. When SSPxSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set.

During transmission, the SSPxBUF is not buffered. A write to SSPxBUF will write to both SSPxBUF and SSPxSR.

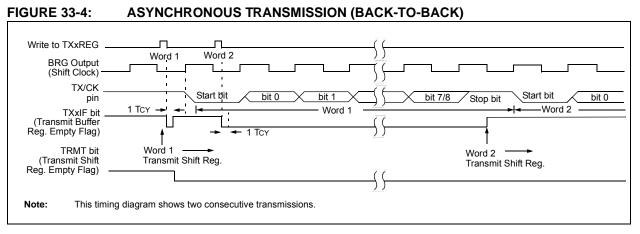

### 33.1.2 EUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 33-2. The data is received on the RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the EUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCxREG register.

### 33.1.2.1 Enabling the Receiver

The EUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCxSTA register enables the receiver circuitry of the EUSART. Clearing the SYNC bit of the TXxSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCxSTA register enables the EUSART. The programmer must set the corresponding TRIS bit to configure the RX/DT I/O pin as an input.

**Note:** If the RX/DT function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

### 33.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. See Section 33.1.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the EUSART receive FIFO and the RXxIF interrupt flag bit of the PIR3 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCxREG register.

Note: If the receive FIFO is overrun, no additional characters will be received until the overrun condition is cleared. See Section 33.1.2.5 "Receive Overrun Error" for more information on overrun errors.

### TABLE 33-3: BAUD RATE FORMULAS

| C    | Configuration Bi | ts |                     | Baud Rate Formula |  |  |  |

|------|------------------|----|---------------------|-------------------|--|--|--|

| SYNC | SYNC BRG16 BRGH  |    | BRG/EUSART Mode     | Daug Rate Formula |  |  |  |

| 0    | 0                | 0  | 8-bit/Asynchronous  | Fosc/[64 (n+1)]   |  |  |  |

| 0    | 0                | 1  | 8-bit/Asynchronous  |                   |  |  |  |

| 0    | 1                | 0  | 16-bit/Asynchronous | Fosc/[16 (n+1)]   |  |  |  |

| 0    | 1                | 1  | 16-bit/Asynchronous |                   |  |  |  |

| 1    | 0                | х  | 8-bit/Synchronous   | Fosc/[4 (n+1)]    |  |  |  |

| 1    | 1                | х  | 16-bit/Synchronous  |                   |  |  |  |

**Legend:** x = Don't care, n = value of SPxBRGH, SPxBRGL register pair.

### TABLE 33-4: BAUD RATE FOR ASYNCHRONOUS MODES

|        |                   | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                   |            |                             |                   |            |                             |                    |            |                             |  |

|--------|-------------------|-------------------------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|--|

| BAUD   | Fosc = 32.000 MHz |                               |                             | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |  |

| RATE   | Actual<br>Rate    | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 300    |                   | _                             | _                           | _                 | _          | _                           | _                 | _          | _                           | _                  | _          | _                           |  |

| 1200   | —                 | —                             | —                           | 1221              | 1.73       | 255                         | 1200              | 0.00       | 239                         | 1200               | 0.00       | 143                         |  |

| 2400   | 2404              | 0.16                          | 207                         | 2404              | 0.16       | 129                         | 2400              | 0.00       | 119                         | 2400               | 0.00       | 71                          |  |

| 9600   | 9615              | 0.16                          | 51                          | 9470              | -1.36      | 32                          | 9600              | 0.00       | 29                          | 9600               | 0.00       | 17                          |  |

| 10417  | 10417             | 0.00                          | 47                          | 10417             | 0.00       | 29                          | 10286             | -1.26      | 27                          | 10165              | -2.42      | 16                          |  |

| 19.2k  | 19.23k            | 0.16                          | 25                          | 19.53k            | 1.73       | 15                          | 19.20k            | 0.00       | 14                          | 19.20k             | 0.00       | 8                           |  |

| 57.6k  | 55.55k            | -3.55                         | 3                           | —                 | _          | _                           | 57.60k            | 0.00       | 7                           | 57.60k             | 0.00       | 2                           |  |

| 115.2k | —                 | _                             | —                           | —                 | _          | —                           | _                 |            | —                           |                    | _          | —                           |  |

|        | <b>SYNC</b> = 0, <b>BRGH</b> = 0, <b>BRG16</b> = 0 |            |                             |                  |            |                             |                   |            |                             |                  |            |                             |

|--------|----------------------------------------------------|------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz                                   |            |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate                                     | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    |                                                    | _          | _                           | 300              | 0.16       | 207                         | 300               | 0.00       | 191                         | 300              | 0.16       | 51                          |

| 1200   | 1202                                               | 0.16       | 103                         | 1202             | 0.16       | 51                          | 1200              | 0.00       | 47                          | 1202             | 0.16       | 12                          |

| 2400   | 2404                                               | 0.16       | 51                          | 2404             | 0.16       | 25                          | 2400              | 0.00       | 23                          | —                | —          | —                           |

| 9600   | 9615                                               | 0.16       | 12                          | _                | _          | _                           | 9600              | 0.00       | 5                           | —                | _          | _                           |

| 10417  | 10417                                              | 0.00       | 11                          | 10417            | 0.00       | 5                           | _                 | _          | _                           | _                | _          | _                           |

| 19.2k  | —                                                  | _          | _                           | —                | _          | _                           | 19.20k            | 0.00       | 2                           | —                | _          | _                           |

| 57.6k  | —                                                  | _          | —                           | —                | —          | —                           | 57.60k            | 0.00       | 0                           | —                | _          |                             |

| 115.2k | —                                                  | —          | _                           | —                | —          | —                           | —                 | _          | —                           | —                | _          | —                           |

### 39.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 39.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradeable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

### 39.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

### 39.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

### 39.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

### 39.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

### 39.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase