#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 224 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15354-i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F15354/55

### TABLE 2: PACKAGES

| Device         | (S)PDIP | SOIC | SSOP | UQFN (4x4) | UQFN (6x6) |

|----------------|---------|------|------|------------|------------|

| PIC16(L)F15354 | •       | •    | •    | •          | •          |

| PIC16(L)F15355 | •       | •    | •    | •          | •          |

## 2.5 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to Section 9.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for details).

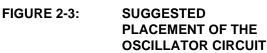

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-3. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins, and other signals in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times, and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

# 2.6 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

| Address | Name                                                                                   | Bit 7                                    | Bit 6      | Bit 5   | Bit 4         | Bit 3             | Bit 2     | Bit 1      | Bit 0     | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |  |

|---------|----------------------------------------------------------------------------------------|------------------------------------------|------------|---------|---------------|-------------------|-----------|------------|-----------|-----------------------|----------------------------|--|

| Bank 11 |                                                                                        |                                          |            |         |               |                   |           |            |           |                       |                            |  |

|         |                                                                                        |                                          |            | CPU COF | RE REGISTERS; | see Table 4-3 for | specifics |            |           |                       |                            |  |

| 58Ch    | n NCO1ACCL NCO1ACC<7:0>                                                                |                                          |            |         |               |                   |           |            |           |                       |                            |  |

| 58Dh    | NCO1ACCH                                                                               |                                          |            |         | NCO1AC        | C<15:8>           |           |            |           | 0000 0000             | 0000 0000                  |  |

| 58Eh    | NCO1ACCU                                                                               | _                                        | _          | —       | _             |                   | NCO1      | ACC<19:16> |           | 0000                  | 0000                       |  |

| 58Fh    | NCO1INCL                                                                               |                                          |            |         | NCO1IN        | C<7:0>            |           |            |           | 0000 0001             | 0000 0001                  |  |

| 590h    |                                                                                        |                                          |            |         |               |                   |           |            |           | 0000 0000             | 0000 0000                  |  |

| 591h    | NCO1INCU                                                                               | _                                        | _          | _       |               |                   | NCO1      | INC<19:16> |           | 0000                  | 0000                       |  |

| 592h    | NCO1CON                                                                                | N1EN                                     | _          | N1OUT   | N1POL         | _                 | _         | _          | N1PFM     | 0-000                 | 0-000                      |  |

| 593h    | NCO1CLK                                                                                |                                          | N1PWS<2:0> |         | _             | —                 |           | N1CKS<2:0> | >         | 000000                | 000000                     |  |

| 594h    | —                                                                                      |                                          |            |         | Unimpler      | nented            |           |            |           |                       |                            |  |

| 595h    | —                                                                                      |                                          |            |         | Unimpler      | mented            |           |            |           |                       |                            |  |

| 596h    | —                                                                                      |                                          |            |         | Unimpler      | mented            |           |            |           |                       |                            |  |

| 597h    | —                                                                                      |                                          |            |         | Unimpler      | mented            |           |            |           |                       |                            |  |

| 598h    | —                                                                                      |                                          |            |         | Unimpler      | mented            |           |            |           |                       |                            |  |

| 599h    | —                                                                                      |                                          |            |         | Unimpler      | mented            |           |            |           |                       |                            |  |

| 59Ah    | —                                                                                      |                                          |            |         | Unimpler      | mented            |           |            |           |                       |                            |  |

| 59Bh    | DBh — Unimplemented                                                                    |                                          |            |         |               |                   |           |            |           |                       |                            |  |

| 59Ch    | i9Ch TMR0L Holding Register for the Least Significant Byte of the 16-bit TMR0 Register |                                          |            |         |               |                   |           |            | 0000 0000 | 0000 0000             |                            |  |

| 59Dh    | 9Dh TMR0H Holding Register for the Most Significant Byte of the 16-bit TMR0 Register   |                                          |            |         |               |                   |           |            | 1111 1111 | 1111 1111             |                            |  |

| 59Eh    | T0CON0                                                                                 | TOCONO TOEN — TOOUT TO16BIT TOOUTPS<3:0> |            |         |               |                   |           |            | 0-00 0000 | 0-00 0000             |                            |  |

| 59Fh    | T0CON1                                                                                 |                                          | T0CS<2:0>  |         | TOASYNC       |                   | TOC       | KPS<3:0>   |           | 0000 0000             | 0000 0000                  |  |

## TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

# 6.0 DEVICE INFORMATION AREA

The Device Information Area (DIA) is a dedicated region in the program memory space; it is a new feature in the PIC16(L)F15354/55 family of devices. The DIA contains the calibration data for the internal temperature indicator module, stores the Microchip Unique Identifier words and the Fixed Voltage Reference voltage readings measured in mV.

The complete DIA table is shown in Table 6-1: Device Information Area, followed by a description of each region and its functionality. The data is mapped from 8100h to 811Fh in the PIC16(L)F15354/55 family. These locations are read-only and cannot be erased or modified. The data is programmed into the device during manufacturing.

| Address Range | Name of Region        | Standard Device Information                           |  |  |  |  |  |

|---------------|-----------------------|-------------------------------------------------------|--|--|--|--|--|

|               | MUI0                  |                                                       |  |  |  |  |  |

|               | MUI1                  |                                                       |  |  |  |  |  |

|               | MUI2                  |                                                       |  |  |  |  |  |

|               | MUI3                  | Microchip Unique Identifier (9 Words)                 |  |  |  |  |  |

| 8100h-8108h   | MUI4                  |                                                       |  |  |  |  |  |

|               | MUI5                  |                                                       |  |  |  |  |  |

|               | MUI6                  |                                                       |  |  |  |  |  |

|               | MUI7                  |                                                       |  |  |  |  |  |

|               | MUI8                  |                                                       |  |  |  |  |  |

| 8109h         | MUI9                  | 1 Word Reserved                                       |  |  |  |  |  |

|               | EUI0                  |                                                       |  |  |  |  |  |

|               | EUI1                  |                                                       |  |  |  |  |  |

|               | EUI2                  |                                                       |  |  |  |  |  |

| 310Ah-8111h - | EUI3                  |                                                       |  |  |  |  |  |

|               | EUI4                  | Unused (8 Words)                                      |  |  |  |  |  |

|               | EUI5                  |                                                       |  |  |  |  |  |

|               | EUI6                  |                                                       |  |  |  |  |  |

|               | EUI7                  |                                                       |  |  |  |  |  |

| 8112h         | TSLR1                 | Temperature Sensor (low range setting)                |  |  |  |  |  |

| 8113h         | TSLR2                 | @ 30°C and @ 90°C (2 Words)                           |  |  |  |  |  |

| 8114h         | TSLR3                 | Unused (1 word)                                       |  |  |  |  |  |

| 8115h         | TSHR1                 | Temperature Sensor (high range setting)               |  |  |  |  |  |

| 8116h         | TSHR2                 | @ 30°C and @ 90°C (2 Words)                           |  |  |  |  |  |

| 8117h         | TSHR3                 | Unused (1 Word)                                       |  |  |  |  |  |

| 8118h         | FVRA1X                | ADC FVR1 Output voltage for 1x setting (in mV)        |  |  |  |  |  |

| 8119h         | FVRA2X                | ADC FVR1 Output Voltage for 2x setting (in mV)        |  |  |  |  |  |

| 811Ah         | FVRA4X <sup>(1)</sup> | ADC FVR1 Output Voltage for 4x setting (in mV)        |  |  |  |  |  |

| 811Bh         | FVRC1X                | Comparator FVR2 output voltage for 1x setting (in mV) |  |  |  |  |  |

| 811Ch         | FVRC2X                | Comparator FVR2 output voltage for 2x setting (in mV) |  |  |  |  |  |

| 811Dh         | FVRC4X <sup>(1)</sup> | Comparator FVR2 output voltage for 4x setting (in mV) |  |  |  |  |  |

| 811Eh-811Fh   |                       | Unused (1 Word)                                       |  |  |  |  |  |

**Note 1:** Value not present on LF devices.

### 8.12 Memory Execution Violation

A Memory Execution Violation Reset occurs if executing an instruction being fetched from outside the valid execution area. The different valid execution areas are defined as follows:

- Flash Memory: Table 4-1 shows the addresses available on the PIC16(L)F15354/55 devices based on user flash size. Execution outside this region generates a memory execution violation.

- Storage Area Flash (SAF): If Storage Area Flash (SAF) is enabled (Section 4.2.3 "Storage Area Flash"), the SAF area (Table 4-2) is not a valid execution area.

Prefetched instructions that are not executed do not cause memory execution violations. For example, a GOTO instruction in the last memory location will prefetch from an invalid location; this is not an error. If an instruction from an invalid location tries to execute, the memory violation is generated immediately, and any concurrent interrupt requests are ignored. When a memory execution violation is generated, the device is reset and flag MEMV is cleared in PCON1 (Register 8-3) to signal the cause. The flag needs to be set in code after a memory execution violation

| R/W-0/0          | R/W-0/0        | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|------------------|------------------|--------------|

| RC2IE            | TX2IE          | RC1IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TX1IE          | BCL2IE           | SSP2IE           | BCL1IE           | SSP1IE       |

| bit 7            |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |                  |                  |                  | bit 0        |

|                  |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |                  |                  |                  |              |

| Legend:          |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |                  |                  |                  |              |

| R = Readable     |                | W = Writable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit            | U = Unimpler     | mented bit, read | l as '0'         |              |

| u = Bit is unch  | anged          | x = Bit is unkr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                | -n/n = Value a   | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is set |                | '0' = Bit is clea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ared           |                  |                  |                  |              |

|                  |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |                  |                  |                  |              |

| bit 7            |                | RT Receive Inte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •              | bit              |                  |                  |              |

|                  |                | the USART rec<br>the USART rec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |                  |                  |                  |              |

| bit 6            |                | RT Transmit Inte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •              | bit              |                  |                  |              |

|                  |                | the USART tra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | •              |                  |                  |                  |              |

|                  | 0 = Disables   | the USART tra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | nsmit interrup | ot               |                  |                  |              |

| bit 5            | RC1IE: USAF    | RT Receive Inte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | errupt Enable  | bit              |                  |                  |              |

|                  |                | the USART rec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | •              |                  |                  |                  |              |

| bit 4            |                | the USART rec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | •              | hit              |                  |                  |              |

| DIL 4            |                | RT Transmit Intention the USART training the USART training the training term of the training term of the training term of the training term of the term of te |                |                  |                  |                  |              |

|                  |                | the USART tra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |                  |                  |                  |              |

| bit 3            | BCL2IE: MSS    | SP2 Bus Collisi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | on Interrupt E | nable bit        |                  |                  |              |

|                  |                | us Collision inte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |                  |                  |                  |              |

|                  |                | us Collision inte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | •              |                  |                  |                  |              |

| bit 2            |                | chronous Seria                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                | 2) Interrupt Ena | able bit         |                  |              |

|                  |                | us collision Inte<br>the MSSP Inte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |                  |                  |                  |              |

| bit 1            |                | SP1 Bus Collisi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •              | nable bit        |                  |                  |              |

|                  |                | us collision inte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |                  |                  |                  |              |

|                  | 0 = MSSP bu    | us collision inte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | rrupt disabled |                  |                  |                  |              |