Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Dectano                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 224 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15354-i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See **Section 10.5 "Automatic Context Saving"** for more information.

## 3.2 16-Level Stack with Overflow and Underflow

These devices have a hardware stack memory 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON register, and if enabled, will cause a software Reset. See **Section 4.5 "Stack**" for more details.

## 3.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers and program memory, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. See **Section 4.6** "**Indirect Addressing**" for more details.

## 3.4 Instruction Set

There are 48 instructions for the enhanced mid-range CPU to support the features of the CPU. See **Section 36.0 "Instruction Set Summary**" for more details.

## 4.1.1 READING PROGRAM MEMORY AS DATA

There are three methods of accessing constants in program memory. The first method is to use tables of RETLW instructions. The second method is to set an FSR to point to the program memory. The third method is to use the NVMREG interface to access the program memory. For an example of NVREG interface use, reference Section 13.3, NVMREG Access.

### 4.1.1.1 RETLW Instruction

The RETLW instruction can be used to provide access to tables of constants. The recommended way to create such a table is shown in Example 4-1.

EXAMPLE 4-1: RETLW INSTRUCTION

| ;Add Index in W to |

|--------------------|

| program counter to |

| ;select data       |

| ;Index0 data       |

| ;Index1 data       |

|                    |

|                    |

|                    |

|                    |

|                    |

|                    |

| EX                 |

|                    |

| IN W               |

|                    |

The BRW instruction makes this type of table very simple to implement.

### 4.1.1.2 Indirect Read with FSR

The program memory can be accessed as data by setting bit 7 of an FSRxH register and reading the matching INDFx register. The MOVIW instruction will place the lower eight bits of the addressed word in the W register. Writes to the program memory cannot be performed via the INDF registers. Instructions that read the program memory via the FSR require one extra instruction cycle to complete. Example 4-2 demonstrates reading the program memory via an FSR.

The High directive will set bit 7 if a label points to a location in the program memory.

#### EXAMPLE 4-2: ACCESSING PROGRAM MEMORY VIA FSR

| constants |                 |             |

|-----------|-----------------|-------------|

| RETLW     | DATAO ; I       | Index0 data |

| RETLW     | DATA1 ;I        | Index1 data |

| RETLW     | DATA2           |             |

| RETLW     | DATA3           |             |

| my_functi | on              |             |

| ; LO      | TS OF CODE      |             |

| MOVLW     | LOW constants   | 5           |

| MOVWF     | FSR1L           |             |

| MOVLW     | HIGH constant   | ts          |

| MOVWF     | FSR1H           |             |

| MOVIW     | 0[FSR1]         |             |

| ;THE PROG | RAM MEMORY IS I | EN W        |

|           |                 |             |

| Address    | Name                | Bit 7         | Bit 6         | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|------------|---------------------|---------------|---------------|---------|---------|---------|---------|---------|---------|-----------------------|----------------------------|

| Bank 62 (C | Bank 62 (Continued) |               |               |         |         |         |         |         |         |                       |                            |

| 1F38h      | ANSELA              | ANSA7         | ANSA6         | ANSA5   | ANSA4   | ANSA3   | ANSA2   | ANSA1   | ANSA0   | 1111 1111             | 1111 1111                  |

| 1F39h      | WPUA                | WPUA7         | WPUA6         | WPUA5   | WPUA4   | WPUA3   | WPUA2   | WPUA1   | WPUA0   | 0000 0000             | 0000 0000                  |

| 1F3Ah      | ODCONA              | ODCA7         | ODCA6         | ODCA5   | ODCA4   | ODCA3   | ODCA2   | ODCA1   | ODCA0   | 0000 0000             | 0000 0000                  |

| 1F3Bh      | SLRCONA             | SLRA7         | SLRA6         | SLRA5   | SLRA4   | SLRA3   | SLRA2   | SLRA1   | SLRA0   | 1111 1111             | 1111 1111                  |

| 1F3Ch      | INLVLA              | INLVLA7       | INLVLA6       | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 1111 1111             | 1111 1111                  |

| 1F3Dh      | IOCAP               | IOCAP7        | IOCAP6        | IOCAP5  | IOCAP4  | IOCAP3  | IOCAP2  | IOCAP1  | IOCAP0  | 0000 0000             | 0000 0000                  |

| 1F3Eh      | IOCAN               | IOCAN7        | IOCAN6        | IOCAN5  | IOCAN4  | IOCAN3  | IOCAN2  | IOCAN1  | IOCAN0  | 0000 0000             | 0000 0000                  |

| 1F3Fh      | IOCAF               | IOCAF7        | IOCAF6        | IOCAF5  | IOCAF4  | IOCAF3  | IOCAF2  | IOCAF1  | IOCAF0  | 0000 0000             | 0000 0000                  |

| 1F40h      | _                   |               |               |         | Unimple | mented  |         |         |         | —                     | —                          |

| 1F41h      | _                   |               |               |         | Unimple | mented  |         |         |         | —                     | —                          |

| 1F42h      | —                   |               |               |         | Unimple | mented  |         |         |         | _                     | _                          |

| 1F43h      | ANSELB              | ANSB7         | ANSB6         | ANSB5   | ANSB4   | ANSB3   | ANSB2   | ANSB1   | ANSB0   | 1111 1111             | 1111 1111                  |

| 1F44h      | WPUB                | WPUB7         | WPUB6         | WPUB5   | WPUB4   | WPUB3   | WPUB2   | WPUB1   | WPUB0   | 0000 0000             | 0000 0000                  |

| 1F45h      | ODCONB              | ODCB7         | ODCB6         | ODCB5   | ODCB4   | ODCB3   | ODCB2   | ODCB1   | ODCB0   | 0000 0000             | 0000 0000                  |

| 1F46h      | SLRCONB             | SLRB7         | SLRB6         | SLRB5   | SLRB4   | SLRB3   | SLRB2   | SLRB1   | SLRB0   | 1111 1111             | 1111 1111                  |

| 1F47h      | INLVLB              | INLVLB7       | INLVLB6       | INLVLB5 | INLVLB4 | INLVLB3 | INLVLB2 | INLVLB1 | INLVLB0 | 1111 1111             | 1111 1111                  |

| 1F48h      | IOCBP               | IOCBP7        | IOCBP6        | IOCBP5  | IOCBP4  | IOCBP3  | IOCBP2  | IOCBP1  | IOCBP0  | 0000 0000             | 0000 0000                  |

| 1F49h      | IOCBN               | IOCBN7        | IOCBN6        | IOCBN5  | IOCBN4  | IOCBN3  | IOCBN2  | IOCBN1  | IOCBN0  | 0000 0000             | 0000 0000                  |

| 1F4Ah      | IOCBF               | IOCBF7        | IOCBF6        | IOCBF5  | IOCBF4  | IOCBF3  | IOCBF2  | IOCBF1  | IOCBF0  | 0000 0000             | 0000 0000                  |

| 1F4Bh      | —                   |               | Unimplemented |         |         |         |         |         |         |                       | —                          |

| 1F4Ch      | _                   |               |               |         | Unimple | mented  |         |         |         | —                     | —                          |

| 1F4Dh      | _                   |               |               |         | Unimple | mented  |         |         |         | —                     | —                          |

| 1F4Eh      | ANSELC              | ANSC7         | ANSC6         | ANSC5   | ANSC4   | ANSC3   | ANSC2   | ANSC1   | ANSC0   | 1111 1111             | 1111 1111                  |

| 1F4Fh      | WPUC                | WPUC7         | WPUC6         | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   | 0000 0000             | 0000 0000                  |

| 1F50h      | ODCONC              | ODCC7         | ODCC6         | ODCC5   | ODCC4   | ODCC3   | ODCC2   | ODCC1   | ODCC0   | 0000 0000             | 0000 0000                  |

| 1F51h      | SLRCONC             | SLRC7         | SLRC6         | SLRC5   | SLRC4   | SLRC3   | SLRC2   | SLRC1   | SLRC0   | 1111 1111             | 1111 1111                  |

| 1F52h      | INLVLC              | INLVLC7       | INLVLC6       | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 | 1111 1111             | 1111 1111                  |

| 1F53h      | IOCCP               | IOCCP7        | IOCCP6        | IOCCP5  | IOCCP4  | IOCCP3  | IOCCP2  | IOCCP1  | IOCCP0  | 0000 0000             | 0000 0000                  |

| 1F54h      | IOCCN               | IOCCN7        | IOCCN6        | IOCCN5  | IOCCN4  | IOCCN3  | IOCCN2  | IOCCN1  | IOCCN0  | 0000 0000             | 0000 0000                  |

| 1F55h      | IOCCF               | IOCCF7        | IOCCF6        | IOCCF5  | IOCCF4  | IOCCF3  | IOCCF2  | IOCCF1  | IOCCF0  | 0000 0000             | 0000 0000                  |

| 1F56h      |                     | Unimplemented |               |         |         |         |         |         |         |                       |                            |

| <br>1F64h  | —                   |               |               |         |         |         |         |         | _       | _                     |                            |

| 1F65h      | WPUE                | —             | _             |         |         | WPUE3   |         |         | —       | 0                     | u                          |

| 1F66h      | —                   |               |               |         | Unimple | mented  |         |         |         | —                     | -                          |

| 1F67h      | _                   |               |               |         | Unimple | mented  |         |         |         | _                     | _                          |

### TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

| REGISTER              | 5-4: CON                                                                                                                                       | FIGURATION                                                                  | WORD 4: M                                                                                    | EMORY                                                                                    |                                |                                                   |                              |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------|---------------------------------------------------|------------------------------|--|

|                       |                                                                                                                                                | R/W-1                                                                       | U-1                                                                                          | R/W-1                                                                                    | U-1                            | R/W-1                                             | R/W-1                        |  |

|                       |                                                                                                                                                | LVP                                                                         |                                                                                              | WRTSAF <sup>(1)</sup>                                                                    |                                | WRTC <sup>(1)</sup>                               | WRTB <sup>(1)</sup>          |  |

|                       |                                                                                                                                                | bit 13                                                                      | 12                                                                                           | 11                                                                                       | 10                             | 9                                                 | bit 8                        |  |

| R/W-1                 | U-1                                                                                                                                            | U-1                                                                         | R/W-1                                                                                        | R/W-1                                                                                    | R/W-1                          | R/W-1                                             | R/W-1                        |  |

| WRTAPP <sup>(1)</sup> | 0-1                                                                                                                                            | 0-1                                                                         | SAFEN <sup>(1)</sup>                                                                         | BBEN <sup>(1)</sup>                                                                      | BBSIZE2                        | BBSIZE1                                           | BBSIZE0                      |  |

| bit 7                 | 6                                                                                                                                              | 5                                                                           | <u> 3AFEN 7</u><br>4                                                                         | 3                                                                                        | 2                              | 1                                                 | bbSIZEU<br>bit C             |  |

|                       | 0                                                                                                                                              | 5                                                                           | 4                                                                                            | 3                                                                                        | 2                              | I                                                 | DILC                         |  |

| Legend:               |                                                                                                                                                |                                                                             |                                                                                              |                                                                                          |                                |                                                   |                              |  |

| R = Readable          | e bit                                                                                                                                          | P = Programr                                                                | mable bit                                                                                    | x = Bit is unkr                                                                          | nown                           | U = Unimplen<br>read as '1'                       | nented bit,                  |  |

| '0' = Bit is cle      | ared                                                                                                                                           | '1' = Bit is set                                                            |                                                                                              | W = Writable                                                                             | bit                            | n = Value whe<br>after Bulk Era                   |                              |  |

| bit 13                | $1 = Low volignored0 = HV on \overline{N}$<br>The LVP bit of<br>purpose of th<br>mode, or acc                                                  | MCLR/VPP mus<br>cannot be writte<br>is rule is to prev<br>identally elimina | ing enabled. M<br>t be used for p<br>n (to zero) whil<br>/ent the user fro<br>ating LVP mode | CLR/VPP pin fu<br>rogramming.<br>le operating froi<br>om dropping ou<br>e from the confi | m the LVP pro<br>t of LVP mode | R. MCLRE Con<br>gramming interf<br>while programn | ace. The                     |  |

|                       | -                                                                                                                                              | tioned (erased)                                                             |                                                                                              | oit is critical.                                                                         |                                |                                                   |                              |  |

| bit 12                |                                                                                                                                                | ted: Read as "                                                              |                                                                                              |                                                                                          |                                |                                                   |                              |  |

| bit 11                |                                                                                                                                                | orage Area Fla                                                              |                                                                                              | ction bit                                                                                |                                |                                                   |                              |  |

|                       | 0 = SAF writ                                                                                                                                   |                                                                             |                                                                                              | the device fami                                                                          | ilv and only ap                | plicable if SAFE                                  | $\overline{\mathbf{N}} = 0.$ |  |

| bit 10                |                                                                                                                                                | ted: Read as "                                                              |                                                                                              |                                                                                          | , ,                            | •                                                 |                              |  |

| bit 9                 |                                                                                                                                                | iguration Regis                                                             |                                                                                              | ction bit                                                                                |                                |                                                   |                              |  |

|                       | 1 = Configu                                                                                                                                    | ration Register                                                             | NOT write-pro                                                                                | tected                                                                                   |                                |                                                   |                              |  |

| bit 8                 | <ul> <li><u>0</u> = Configuration Register write-protected</li> <li>WRTB: Boot Block Write Protection bit</li> </ul>                           |                                                                             |                                                                                              |                                                                                          |                                |                                                   |                              |  |

|                       | 1 = Boot Blo                                                                                                                                   | ock NOT write-                                                              | protected                                                                                    |                                                                                          |                                |                                                   |                              |  |

|                       | 0 = Boot Blo                                                                                                                                   | ock write-proted                                                            | cted                                                                                         |                                                                                          |                                |                                                   |                              |  |

|                       |                                                                                                                                                | ble if $\overline{BBEN} = 0$                                                |                                                                                              |                                                                                          |                                |                                                   |                              |  |

| bit 7                 | WRTAPP: Application Block Write Protection bit         1 = Application Block NOT write-protected         0 = Application Block write-protected |                                                                             |                                                                                              |                                                                                          |                                |                                                   |                              |  |

| bit 6-5               |                                                                                                                                                |                                                                             |                                                                                              |                                                                                          |                                |                                                   |                              |  |

| bit 4                 | Unimplemented: Read as '1'. SAFEN: SAF Enable bit                                                                                              |                                                                             |                                                                                              |                                                                                          |                                |                                                   |                              |  |

| 511 4                 | 1 = SAF disa<br>0 = SAF ena                                                                                                                    | abled                                                                       |                                                                                              |                                                                                          |                                |                                                   |                              |  |

| bit 3                 | BBEN: Boot                                                                                                                                     | Block Enable b<br>ock disabled<br>ock enabled                               | it                                                                                           |                                                                                          |                                |                                                   |                              |  |

| bit 2-0               | BBSIZE[2:0]:<br>BBSIZE is us                                                                                                                   | Boot Block Size                                                             | BBEN = 0                                                                                     | = 1; after BBEI                                                                          | N = 0, BBSIZ i                 | s write-protecte                                  | d.                           |  |

| Note 1: Bit           | ts are impleme                                                                                                                                 | nted as sticky b                                                            | oits. Once prote                                                                             | ection is enable                                                                         | d. it can only b               | e reset through                                   | a Bulk Erase                 |  |

**Note 1:** Bits are implemented as sticky bits. Once protection is enabled, it can only be reset through a Bulk Erase.

## 9.2 Clock Source Types

Clock sources can be classified as external or internal.

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (ECH, ECM, ECL mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes).

Internal clock sources are contained within the oscillator module. The internal oscillator block has two internal oscillators and a dedicated Phase Lock Loop (PLL) that are used to generate internal system clock sources. The High-Frequency Internal Oscillator (HFINTOSC) can produce a range from 1 to 32 MHz. The Low-Frequency Internal Oscillator (LFINTOSC) generates a 31 kHz frequency. The external oscillator block can also be used with the PLL. See **Section 9.2.1.4 "4x PLL"** for more details.

The system clock can be selected between external or internal clock sources via the NOSC bits in the OSCCON1 register. See **Section 9.3** "**Clock Switching**" for additional information.

### 9.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the RSTOSC<2:0> bits in the Configuration Words to select an external clock source that will be used as the default system clock upon a device Reset

- Write the NOSC<2:0> and NDIV<4:0> bits in the OSCCON1 register to switch the system clock source

See **Section 9.3** "Clock Switching" for more information.

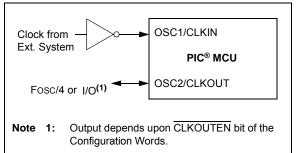

### 9.2.1.1 EC Mode

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. Figure 9-2 shows the pin connections for EC mode.

EC mode has three power modes to select from through Configuration Words:

- ECH High power, 0-32 MHz

- ECM Medium power, 0-8 MHz

- ECL Low power, 0-0.5 MHz

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### EXTERNAL CLOCK (EC) MODE OPERATION

## 9.2.1.2 LP, XT, HS Modes

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 9-3). The three modes select a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive crystals and resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 9-3 and Figure 9-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

## 12.1 Independent Clock Source

The WDT can derive its time base from either the 31 kHz LFINTOSC or 31.25 kHz MFINTOSC internal oscillators, depending on the value of either the WDTCCS<2:0> Configuration bits or the WDTCS<2:0> bits of WDTCON1. Time intervals in this chapter are based on a minimum nominal interval of 1 ms. See **Section 37.0 "Electrical Specifications"** for LFINTOSC and MFINTOSC tolerances.

## 12.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 12-1.

#### 12.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always on.

WDT protection is active during Sleep.

#### 12.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

#### 12.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON0 register.

### 12.2.4 WDT IS OFF

When the WDTE bits of the Configuration Word are set to '00', the WDT is always OFF.

WDT protection is unchanged by Sleep. See Table 12-1 for more details.

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |

|-----------|--------|----------------|-------------|

| 11        | Х      | Х              | Active      |

| 10        | 37     | Awake          | Active      |

| 10        | Х      | Sleep          | Disabled    |

| 0.1       | 1      | Х              | Active      |

| 01        | 0      | Х              | Disabled    |

| 00        | х      | Х              | Disabled    |

## 12.3 Time-Out Period

The WDTPS bits of the WDTCON0 register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

## 12.4 Watchdog Window

The Watchdog Timer has an optional Windowed mode that is controlled by the WDTCWS<2:0> Configuration bits and WINDOW<2:0> bits of the WDTCON1 register. In the Windowed mode, the CLRWDT instruction must occur within the allowed window of the WDT period. Any CLRWDT instruction that occurs outside of this window will trigger a window violation and will cause a WDT Reset, similar to a WDT time out. See Figure 12-2 for an example.

The window size is controlled by the WDTCWS<2:0> Configuration bits, or the WINDOW<2:0> bits of WDTCON1, if WDTCWS<2:0> = 111.

In the event of a <u>window violation</u>, a Reset will be generated and the WDTWV bit of the PCON register will be cleared. This bit is set by a POR or can be set in firmware.

## 12.5 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- · Any Reset

- Valid CLRWDT instruction is executed

- · Device enters Sleep

- Device wakes up from Sleep

- WDT is disabled

- Oscillator Start-up Timer (OST) is running

- Any write to the WDTCON0 or WDTCON1 registers

### 12.5.1 CLRWDT CONSIDERATIONS (WINDOWED MODE)

When in Windowed mode, the WDT must be armed before a CLRWDT instruction will clear the timer. This is performed by reading the WDTCON0 register. Executing a CLRWDT instruction without performing such an arming action will trigger a window violation.

See Table 12-2 for more information.

## 12.6 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting. When the device exits Sleep, the WDT is cleared again.

The WDT remains clear until the OST, if enabled, completes. See Section 9.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The TO and PD bits in the STATUS register are changed to indicate the event. The RWDT bit in the PCON register can also be used. See Section 4.3.2.1 "STATUS Register" for more information.

## 13.3.4 NVMREG WRITE TO PFM

Program memory is programmed using the following steps:

- 1. Load the address of the row to be programmed into NVMADRH:NVMADRL.

- 2. Load each write latch with data.

- 3. Initiate a programming operation.

- 4. Repeat steps 1 through 3 until all data is written.

Before writing to program memory, the word(s) to be written must be erased or previously unwritten. Program memory can only be erased one row at a time. No automatic erase occurs upon the initiation of the write.

Program memory can be written one or more words at a time. The maximum number of words written at one time is equal to the number of write latches. See Figure 13-4 (row writes to program memory with 32 write latches) for more details.

The write latches are aligned to the Flash row address boundary defined by the upper ten bits of NVMADRH:NVMADRL, (NVMADRH<6:0>:NVMADRL<7:5>) with the lower five bits of NVMADRL, (NVMADRL<7:5>) determining the write latch being loaded. Write operations do not cross these boundaries. At the completion of a program memory write operation, the data in the write latches is reset to contain 0x3FFF. The following steps should be completed to load the write latches and program a row of program memory. These steps are divided into two parts. First, each write latch is loaded with data from the NVMDATH:NVMDATL using the unlock sequence with LWLO = 1. When the last word to be loaded into the write latch is ready, the LWLO bit is cleared and the unlock sequence executed. This initiates the programming operation, writing all the latches into Flash program memory.

- Note: The special unlock sequence is required to load a write latch with data or initiate a Flash programming operation. If the unlock sequence is interrupted, writing to the latches or program memory will not be initiated.

- 1. Set the WREN bit of the NVMCON1 register.

- Clear the NVMREGS bit of the NVMCON1 register.

- Set the LWLO bit of the NVMCON1 register. When the LWLO bit of the NVMCON1 register is '1', the write sequence will only load the write latches and will not initiate the write to Flash program memory.

- 4. Load the NVMADRH:NVMADRL register pair with the address of the location to be written.

- 5. Load the NVMDATH:NVMDATL register pair with the program memory data to be written.

- Execute the unlock sequence (Section 13.3.2 "NVM Unlock Sequence"). The write latch is now loaded.

- 7. Increment the NVMADRH:NVMADRL register pair to point to the next location.

- 8. Repeat steps 5 through 7 until all but the last write latch has been loaded.

- Clear the LWLO bit of the NVMCON1 register. When the LWLO bit of the NVMCON1 register is '0', the write sequence will initiate the write to Flash program memory.

- 10. Load the NVMDATH:NVMDATL register pair with the program memory data to be written.

- Execute the unlock sequence (Section 13.3.2 "NVM Unlock Sequence"). The entire program memory latch content is now written to Flash program memory.

- **Note:** The program memory write latches are reset to the blank state (0x3FFF) at the completion of every write or erase operation. As a result, it is not necessary to load all the program memory write latches. Unloaded latches will remain in the blank state.

An example of the complete write sequence is shown in Example 13-4. The initial address is loaded into the NVMADRH:NVMADRL register pair; the data is loaded using indirect addressing.

| Legend: |         |         |         |         |         |         |         |

|---------|---------|---------|---------|---------|---------|---------|---------|

| bit 7   |         |         |         |         |         |         | bit 0   |

| ANSC7   | ANSC6   | ANSC5   | ANSC4   | ANSC3   | ANSC2   | ANSC1   | ANSC0   |

| R/W-1/1 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

|                      |                      |                                                       |

ANSC<7:0>: Analog Select between Analog or Digital Function on Pins RC<7:0>, respectively<sup>(1)</sup> bit 7-0 0 = Digital I/O. Pin is assigned to port or digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

Note 1: When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

#### **REGISTER 14-21: WPUC: WEAK PULL-UP PORTC REGISTER**

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| WPUC7   | WPUC6   | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

WPUC<7:0>: Weak Pull-up Register bits bit 7-0

1 = Pull-up enabled 0 = Pull-up disabled

| VALUES            |                                              |  |  |

|-------------------|----------------------------------------------|--|--|

| Desired Input Pin | Value to Write to<br>Register <sup>(1)</sup> |  |  |

| RA0               | 0x00                                         |  |  |

| RA1               | 0x01                                         |  |  |

| RA2               | 0x02                                         |  |  |

| RA3               | 0x03                                         |  |  |

| RA4               | 0x04                                         |  |  |

| RA5               | 0x05                                         |  |  |

| RA6               | 0x06                                         |  |  |

| RA7               | 0x07                                         |  |  |

| RB0               | 0x08                                         |  |  |

| RB1               | 0x09                                         |  |  |

| RB2               | 0x0A                                         |  |  |

| RB3               | 0x0B                                         |  |  |

| RB4               | 0x0C                                         |  |  |

| RB5               | 0x0D                                         |  |  |

| RB6               | 0x0E                                         |  |  |

| RB7               | 0x0F                                         |  |  |

| RC0               | 0x10                                         |  |  |

| RC1               | 0x11                                         |  |  |

| RC2               | 0x12                                         |  |  |

| RC3               | 0x13                                         |  |  |

| RC4               | 0x14                                         |  |  |

| RC5               | 0x15                                         |  |  |

| RC6               | 0x16                                         |  |  |

| RC7               | 0x17                                         |  |  |

### TABLE 15-2: PPS INPUT REGISTER VALUES

Note 1: Only a few of the values in this column are valid for any given signal. For example, since the INT signal can only be mapped to PORTA or PORTB pins, only the register values 0x00-0x0F (corresponding to RA<7:0> and RB<7:0>) are valid values to write to the INTPPS register.

## 24.7 Operation During Sleep

The ZCD current sources and interrupts are unaffected by Sleep.

## 24.8 Effects of a Reset

The ZCD circuit can be configured to default to the active or inactive state on Power-on-Reset (POR). When the ZCDDIS Configuration bit is cleared, the ZCD circuit will be active at POR. When the ZCD Configuration bit is set, the EN bit of the ZCDxCON register must be set to enable the ZCD module.

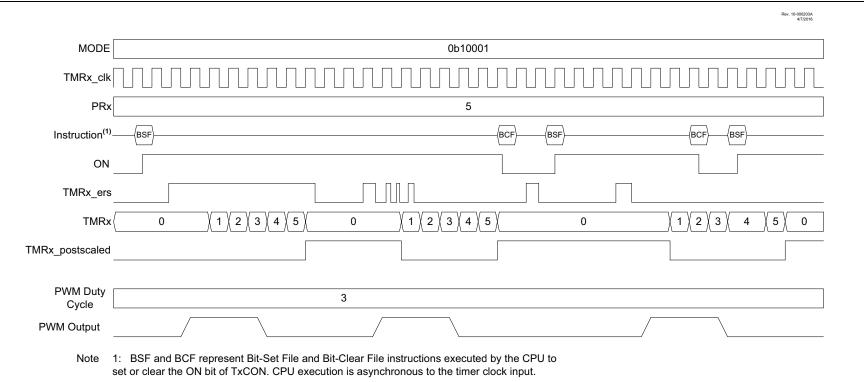

## FIGURE 27-12: RISING EDGE-TRIGGERED MONOSTABLE MODE TIMING DIAGRAM (MODE = 10001)

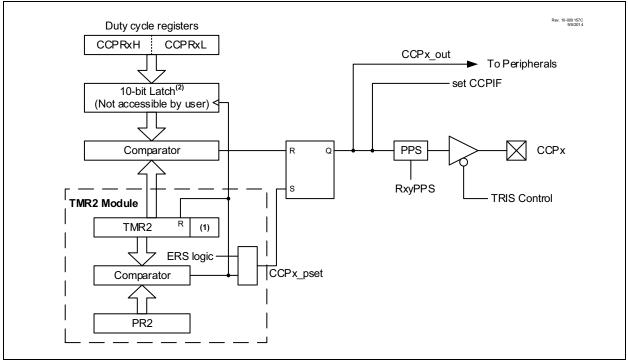

## FIGURE 28-4: SIMPLIFIED PWM BLOCK DIAGRAM

## 28.3.2 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for standard PWM operation:

- Use the desired output pin RxyPPS control to select CCPx as the source and disable the CCPx pin output driver by setting the associated TRIS bit.

- 2. Load the PR2 register with the PWM period value.

- Configure the CCP module for the PWM mode by loading the CCPxCON register with the appropriate values.

- Load the CCPRxL register, and the CCPRxH register with the PWM duty cycle value and configure the CCPxFMT bit of the CCPxCON register to set the proper register alignment.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR4 register. See Note below.

- Configure the CKPS bits of the T2CON register with the Timer prescale value.

- Enable the Timer by setting the Timer2 ON bit of the T2CON register.

- 6. Enable PWM output pin:

- Wait until the Timer overflows and the TMR2IF bit of the PIR4 register is set. See Note below.

- Enable the CCPx pin output driver by clearing the associated TRIS bit.

- **Note:** In order to send a complete duty cycle and period on the first PWM output, the above steps must be included in the setup sequence. If it is not critical to start with a complete PWM signal on the first output, then step 6 may be ignored.

## 28.3.3 CCP/PWM CLOCK SELECTION

The PIC16(L)F15354/55 allows each individual CCP and PWM module to select the timer source that controls the module. Each module has an independent selection.

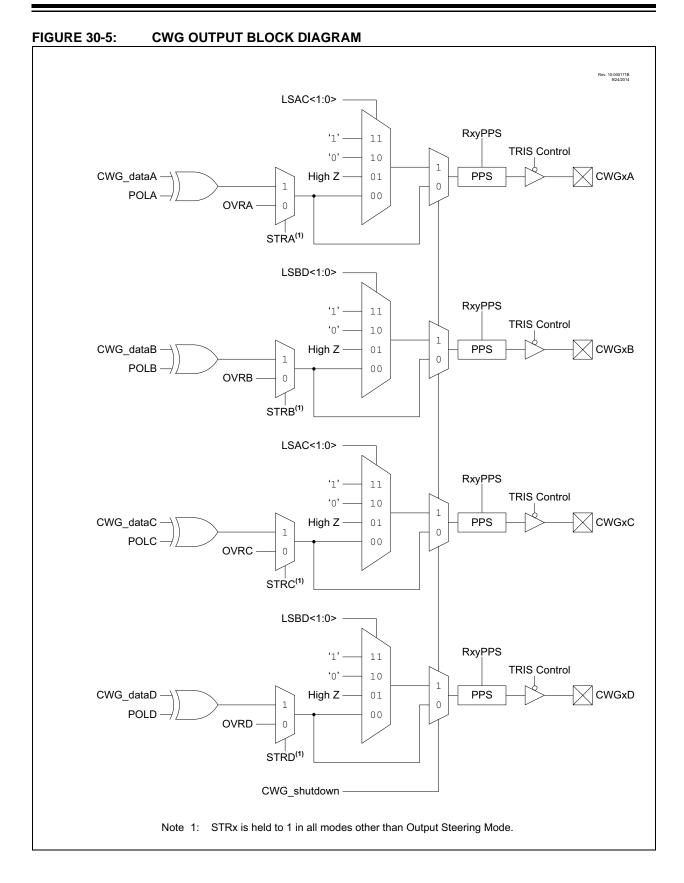

## REGISTER 30-3: CWG1DBR: CWG1 RISING DEAD-BAND COUNTER REGISTER

| U-0              | U-0   | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |

|------------------|-------|-------------------|---------|----------------|------------------|------------------|-------------|

|                  | —     |                   |         | DBR            | <5:0>            |                  |             |

| bit 7            |       |                   |         |                |                  |                  | bit 0       |

|                  |       |                   |         |                |                  |                  |             |

| Legend:          |       |                   |         |                |                  |                  |             |

| R = Readable I   | bit   | W = Writable      | bit     | U = Unimplen   | nented bit, read | as '0'           |             |

| u = Bit is uncha | anged | x = Bit is unkr   | nown    | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set |       | '0' = Bit is clea | ared    | q = Value dep  | ends on condit   | ion              |             |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 DBR<5:0>: Rising Event Dead-Band Value for Counter bits

## REGISTER 30-4: CWG1DBF: CWG1 FALLING DEAD-BAND COUNTER REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   |         |         | DBF     | <5:0>   |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

|       |     |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 DBF<5:0>: Falling Event Dead-Band Value for Counter bits

## © 2016 Microchip Technology Inc.

## 33.4.1.6 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

| Note: | If the device is configured as a slave and  |

|-------|---------------------------------------------|

|       | the TX/CK function is on an analog pin, the |

|       | corresponding ANSEL bit must be cleared.    |

### 33.4.1.7 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCxREG is read to access the FIFO. When this happens the OERR bit of the RCxSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCxREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCxSTA register or by clearing the SPEN bit which resets the EUSART.

### 33.4.1.8 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCxSTA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCxSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCxREG.

## 33.4.1.9 Synchronous Master Reception Set-up:

- 1. Initialize the SPxBRGH, SPxBRGL register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 4. Ensure bits CREN and SREN are clear.

- 5. If interrupts are desired, set the RXxIE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- 6. If 9-bit reception is desired, set bit RX9.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- Interrupt flag bit RXxIF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RXxIE was set.

- 9. Read the RCxSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCxREG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCxSTA register or by clearing the SPEN bit which resets the EUSART.

| RX/DT<br>pin                  | bit 0 bit 1 bit 2 bit 3 bit 4 bit 5 bit 6 bit 7                         |            |

|-------------------------------|-------------------------------------------------------------------------|------------|

| TX/CK pin<br>(SCKP = 0)       |                                                                         |            |

| TX/CK pin<br>(SCKP = 1)       |                                                                         |            |

| Write to<br>bit SREN          |                                                                         |            |

| SREN bit                      |                                                                         |            |

| CREN bit                      |                                                                         | <u>'0'</u> |

| RXxIF bit<br>(Interrupt) ———— |                                                                         | <b>~</b>   |

| Read<br>RCxREG ———            |                                                                         | 1          |

| Note: Timing dia              | agram demonstrates Sync Master mode with bit SREN = 1 and bit BRGH = 0. |            |

### FIGURE 33-12: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

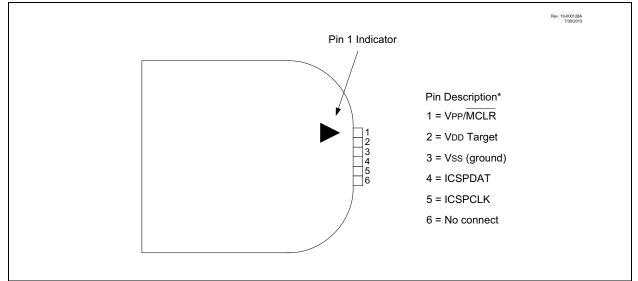

## FIGURE 35-2: PICkit<sup>™</sup> PROGRAMMER STYLE CONNECTOR INTERFACE

| ΜΟΥΨΙ      | Move W to INDFn                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:    | [ <i>label</i> ] MOVWI ++FSRn<br>[ <i>label</i> ] MOVWIFSRn<br>[ <i>label</i> ] MOVWI FSRn++<br>[ <i>label</i> ] MOVWI FSRn<br>[ <i>label</i> ] MOVWI k[FSRn]                                                                                                                                                                                                                                                    |

| Operands:  | $\begin{array}{l} n \in [0,1] \\ mm \in [00,01,10,11] \\ -32 \leq k \leq 31 \end{array}$                                                                                                                                                                                                                                                                                                                         |

| Operation: | $\label{eq:states} \begin{array}{l} W \rightarrow INDFn \\ \text{Effective address is determined by} \\ \bullet \ FSR + 1 \ (preincrement) \\ \bullet \ FSR + 1 \ (predecrement) \\ \bullet \ FSR + k \ (relative offset) \\ \text{After the Move, the FSR value will be} \\ \text{either:} \\ \bullet \ FSR + 1 \ (all \ increments) \\ \bullet \ FSR + 1 \ (all \ increments) \\ \text{Unchanged} \end{array}$ |

Status Affected:

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

None

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

**Note:** The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h-FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap-around.

The increment/decrement operation on FSRn WILL NOT affect any Status bits.

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

| RESET            | Software Reset                                                                |

|------------------|-------------------------------------------------------------------------------|

| Syntax:          | [label] RESET                                                                 |

| Operands:        | None                                                                          |

| Operation:       | Execute a device Reset. Resets the $\overline{RI}$ flag of the PCON register. |

| Status Affected: | None                                                                          |

| Description:     | This instruction provides a way to execute a hardware Reset by software.      |

| RETFIE           | Return from Interrupt                                                                                                                                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] RETFIE k                                                                                                                                                                                              |

| Operands:        | None                                                                                                                                                                                                            |

| Operation:       | $TOS \rightarrow PC, \\ 1 \rightarrow GIE$                                                                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | Return from Interrupt. Stack is POPed<br>and Top-of-Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by<br>setting Global Interrupt Enable bit,<br>GIE (INTCON<7>). This is a 2-cycle<br>instruction. |

| Words:           | 1                                                                                                                                                                                                               |

| Cycles:          | 2                                                                                                                                                                                                               |

| Example:         | RETFIE                                                                                                                                                                                                          |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                          |

| TRIS             | Load TRIS Register with W                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] TRIS f                                                                                                                              |

| Operands:        | $5 \leq f \leq 7$                                                                                                                                    |

| Operation:       | (W) $\rightarrow$ TRIS register 'f'                                                                                                                  |

| Status Affected: | None                                                                                                                                                 |

| Description:     | Move data from W register to TRIS<br>register.<br>When 'f' = 5, TRISA is loaded.<br>When 'f' = 6, TRISB is loaded.<br>When 'f' = 7, TRISC is loaded. |

| XORLW            | Exclusive OR literal with W                                                                                   |

|------------------|---------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] XORLW k                                                                                               |

| Operands:        | $0 \leq k \leq 255$                                                                                           |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                 |

| Status Affected: | Z                                                                                                             |

| Description:     | The contents of the W register are XOR'ed with the 8-bit literal 'k'. The result is placed in the W register. |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] XORWF f,d                                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                               |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |

| Status Affected: | Z                                                                                                                                                                               |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |

## **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

China - Nanjing Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

China - Xiamen Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

Korea - Daegu Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

06/23/16