Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

÷ХГ

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 25                                                                           |

| Program Memory Size        | 7KB (4K x 14)                                                                |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 224 x 8                                                                      |

| RAM Size                   | 512 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-UFQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-UQFN (4x4)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15354t-i-mv |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1-2: PIC16(L)F15354/55 PINOUT DESCRIPTION (CONTINUED)

| Name                                                                                          | Function              | Input<br>Type    | Output Type | Description                                                                                 |

|-----------------------------------------------------------------------------------------------|-----------------------|------------------|-------------|---------------------------------------------------------------------------------------------|

| RA6/ANA6/OSC2/CLKOUT/IOCA6                                                                    | RA6                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                        |

|                                                                                               | ANA6                  | AN               | _           | ADC Channel A6 input.                                                                       |

|                                                                                               | OSC2                  | _                | XTAL        | External Crystal/Resonator (LP, XT, HS modes) driver out-<br>put.                           |

|                                                                                               | CLKOUT                | —                | CMOS/OD     | Fosc/4 digital output (in non-crystal/resonator modes).                                     |

|                                                                                               | IOCA6                 | TTL/ST           | -           | Interrupt-on-change input.                                                                  |

| RA7/ANA7/OSC1/CLKIN/IOCA7                                                                     | RA7                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                        |

|                                                                                               | ANA7                  | AN               | _           | ADC Channel A7 input.                                                                       |

|                                                                                               | OSC1                  | XTAL             | _           | External Crystal/Resonator (LP, XT, HS modes) driver input                                  |

|                                                                                               | CLKIN                 | TTL/ST           | _           | External digital clock input.                                                               |

|                                                                                               | IOCA7                 | TTL/ST           | _           | Interrupt-on-change input.                                                                  |

| RB0/ANB0/C2IN1+/ZCD1/SS2 <sup>(1)</sup> /<br>CWG1IN <sup>(1)</sup> /INT <sup>(1)</sup> /IOCB0 | RB0                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                        |

| CWGTINC/JINTC/JIOCBU                                                                          | ANB0                  | AN               | _           | ADC Channel B0 input.                                                                       |

|                                                                                               | C2IN1+                | AN               | _           | Comparator 2 positive input.                                                                |

|                                                                                               | ZCD1                  | AN               | AN          | Zero-cross detect input pin (with constant current sink/ source).                           |

|                                                                                               | SS2 <sup>(1)</sup>    | TTL/ST           | -           | MSSP2 SPI slave select input.                                                               |

|                                                                                               | CWG1IN <sup>(1)</sup> | TTL/ST           | _           | Complementary Waveform Generator 1 input.                                                   |

|                                                                                               | INT <sup>(1)</sup>    | TTL/ST           | -           | External interrupt request input.                                                           |

|                                                                                               | IOCB0                 | TTL/ST           | -           | Interrupt-on-change input.                                                                  |

| RB1/ANB1/C1IN3-/C2IN3-/SCL2 <sup>(3,4)</sup> /<br>SCK2 <sup>(1)</sup> /IOCB1                  | RB1                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                        |

| SCR2. MOCDI                                                                                   | ANB1                  | AN               | -           | ADC Channel B1 input.                                                                       |

|                                                                                               | C1IN3-                | AN               | _           | Comparator 1 negative input.                                                                |

|                                                                                               | C2IN3-                | AN               | _           | Comparator 2 negative input.                                                                |

|                                                                                               | SCL2 <sup>(3,4)</sup> | l <sup>2</sup> C | OD          | MSSP2 I <sup>2</sup> C clock input/output.                                                  |

|                                                                                               | SCK2 <sup>(1)</sup>   | TTL/ST           | CMOS/OD     | MSSP2 SPI serial clock (default input location, SCK2 is a PPS remappable input and output). |

|                                                                                               | IOCB1                 | TTL/ST           | -           | Interrupt-on-change input.                                                                  |

| RB2/ANB2/SDA2 <sup>(3,4)</sup> /SDI2 <sup>(1)</sup> /IOCB2                                    | RB2                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                        |

|                                                                                               | ANB2                  | AN               | _           | ADC Channel B2 input.                                                                       |

|                                                                                               | SDA2 <sup>(3,4)</sup> | l <sup>2</sup> C | OD          | MSSP2 I <sup>2</sup> C serial data input/output.                                            |

|                                                                                               | SDI2 <sup>(1)</sup>   | TTL/ST           | _           | MSSP2 SPI serial data input.                                                                |

|                                                                                               | IOCB2                 | TTL/ST           | _           | Interrupt-on-change input.                                                                  |

HV = High Voltage XTAL = Crystal levels

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 15-2 for details on which PORT pins may be used for this signal.

2: All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 15-3.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

### TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

| Address                                         | Name | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |  |

|-------------------------------------------------|------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|----------------------------|--|

| Bank 8-10                                       |      |       |       |       |       |       |       |       |       |                       |                            |  |

| CPU CORE REGISTERS; see Table 4-3 for specifics |      |       |       |       |       |       |       |       |       |                       |                            |  |

| x0Ch/<br>x8Ch<br>Unimplemented<br>x1Fh/<br>x9Fh |      |       |       |       |       |       |       |       |       |                       |                            |  |

## 8.15 Register Definitions: Power Control

### REGISTER 8-2: PCON0: POWER CONTROL REGISTER 0

| R/W/HS-0/q | R/W/HS-0/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|------------|------------|------------|------------|------------|------------|------------|------------|

| STKOVF     | STKUNF     | WDTWV      | RWDT       | RMCLR      | RI         | POR        | BOR        |

| bit 7      | •          |            |            |            |            |            | bit 0      |

|            |            |            |            |            |            |            |            |

| Legend:          |                                                                                                                                                                                                                                           |                                                                            |                                                                         |  |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|--|--|--|--|

| HC = Bit is cle  | ared by hardw                                                                                                                                                                                                                             | are                                                                        | HS = Bit is set by hardware                                             |  |  |  |  |  |  |  |

| R = Readable     | bit                                                                                                                                                                                                                                       | W = Writable bit                                                           | U = Unimplemented bit, read as '0'                                      |  |  |  |  |  |  |  |

| u = Bit is unch  | anged                                                                                                                                                                                                                                     | x = Bit is unknown                                                         | -m/n = Value at POR/Value at all other Resets                           |  |  |  |  |  |  |  |

| '1' = Bit is set |                                                                                                                                                                                                                                           | '0' = Bit is cleared                                                       | q = Value depends on condition                                          |  |  |  |  |  |  |  |

| bit 7            | 1 = A Stack                                                                                                                                                                                                                               | ack Overflow Flag bit<br>Overflow occurred<br>Overflow has not occurre     | ed or cleared by firmware                                               |  |  |  |  |  |  |  |

| bit 6            | <ul> <li>0 = A Stack Overflow has not occurred or cleared by firmware</li> <li>STKUNF: Stack Underflow Flag bit</li> <li>1 = A Stack Underflow occurred</li> <li>0 = A Stack Underflow has not occurred or cleared by firmware</li> </ul> |                                                                            |                                                                         |  |  |  |  |  |  |  |

| bit 5            |                                                                                                                                                                                                                                           |                                                                            |                                                                         |  |  |  |  |  |  |  |

| bit 4            | 1 = A Watch                                                                                                                                                                                                                               |                                                                            | it<br>occurred or set to '1' by firmware<br>urred (cleared by hardware) |  |  |  |  |  |  |  |

| bit 3            | 1 = A MCLR                                                                                                                                                                                                                                | CLR Reset Flag bit<br>Reset has not occurred o<br>Reset has occurred (clea |                                                                         |  |  |  |  |  |  |  |

| bit 2            | 1 <b>= A</b> reset                                                                                                                                                                                                                        |                                                                            | executed or set to '1' by firmware<br>ecuted (cleared by hardware)      |  |  |  |  |  |  |  |

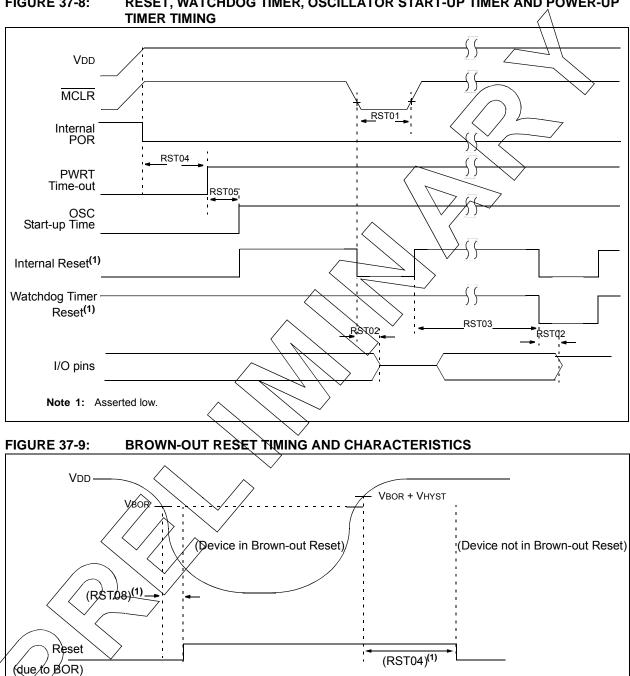

| bit 1            | 1 = No Powe                                                                                                                                                                                                                               | -on Reset Status bit<br>er-on Reset occurred<br>-on Reset occurred (must   | t be set in software after a Power-on Reset occurs)                     |  |  |  |  |  |  |  |

| bit 0            | 1 = No Brow                                                                                                                                                                                                                               | -out Reset Status bit<br>n-out Reset occurred<br>-out Reset occurred (mus  | t be set in software after a Power-on Reset or Brown-out Reset          |  |  |  |  |  |  |  |

| U-0                                                                                        | R/W-0/0             | U-0                            | U-0           | U-0             | U-0              | R/W-0/0  | R/W-0/0 |  |  |  |

|--------------------------------------------------------------------------------------------|---------------------|--------------------------------|---------------|-----------------|------------------|----------|---------|--|--|--|

| _                                                                                          | ZCDIE               | _                              | _             | _               | _                | C2IE     | C1IE    |  |  |  |

| bit 7                                                                                      |                     |                                |               |                 |                  |          | bit 0   |  |  |  |

| Legend:                                                                                    |                     |                                |               |                 |                  |          |         |  |  |  |

| R = Reada                                                                                  | ble bit             | W = Writable                   | bit           | U = Unimpler    | nented bit, read | l as '0' |         |  |  |  |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Res |                     |                                |               |                 |                  |          |         |  |  |  |

| '1' = Bit is set '0' = Bit is cleared                                                      |                     |                                |               |                 |                  |          |         |  |  |  |

|                                                                                            |                     |                                |               |                 |                  |          |         |  |  |  |

| bit 7 Unimplemented: Read as '0'                                                           |                     |                                |               |                 |                  |          |         |  |  |  |

| bit 6                                                                                      | ZCDIE: Zero-        | -Cross Detectio                | n (ZCD) Inter | rupt Enable bit |                  |          |         |  |  |  |

|                                                                                            |                     | the ZCD interru                |               |                 |                  |          |         |  |  |  |

|                                                                                            | 0 = Disables        | the ZCD interr                 | upt           |                 |                  |          |         |  |  |  |

| bit 5-2                                                                                    | Unimplemen          | nted: Read as '                | )'            |                 |                  |          |         |  |  |  |

| bit 1                                                                                      |                     | arator C2 Interru              |               |                 |                  |          |         |  |  |  |

|                                                                                            |                     | the Comparato<br>the Comparato |               |                 |                  |          |         |  |  |  |

| bit 0                                                                                      |                     | arator C1 Interru              |               |                 |                  |          |         |  |  |  |

|                                                                                            | •                   | the Comparato                  | •             |                 |                  |          |         |  |  |  |

|                                                                                            |                     | the Comparato                  |               |                 |                  |          |         |  |  |  |

|                                                                                            |                     | -                              |               |                 |                  |          |         |  |  |  |

| Note:                                                                                      | Bit PEIE of the IN  | ITCON register                 | must be       |                 |                  |          |         |  |  |  |

|                                                                                            | set to enable a     |                                |               |                 |                  |          |         |  |  |  |

|                                                                                            | controlled by regis |                                |               |                 |                  |          |         |  |  |  |

### REGISTER 10-4: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

| Name    | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1     | Bit 0  | Register<br>on Page |

|---------|--------|--------|--------|--------|------------|--------|-----------|--------|---------------------|

| INTCON  | GIE    | PEIE   | _      | _      | —          | —      | —         | INTEDG | 119                 |

| PIE0    | _      | —      | TMR0IE | IOCIE  | —          | _      | —         | INTE   | 120                 |

| PIE1    | OSFIE  | CSWIE  | _      | _      | —          | —      | —         | ADIE   | 121                 |

| PIE2    | _      | ZCDIE  | _      | _      | _          | _      | C2IE      | C1IE   | 122                 |

| PIE3    | RC2IE  | TX2IE  | RC1IE  | TX1IE  | BCL2IE     | SSP2IE | BCL1IE    | SSP1IE | 123                 |

| PIE4    | _      | —      | _      | -      | —          | —      | TMR2IE    | TMR1IE | 124                 |

| PIR0    | _      | —      | TMR0IF | IOCIF  | —          | —      | —         | INTF   | 128                 |

| PIR1    | OSFIF  | CSWIF  | _      | _      | _          | _      | _         | ADIF   | 129                 |

| PIR2    | _      | ZCDIF  | _      | _      | —          | _      | C2IF      | C1IF   | 130                 |

| PIR3    | RC2IF  | TX2IF  | RC1IF  | TX1IF  | BCL2IF     | SSP2IF | BCL1IF    | SSP1IF | 131                 |

| PIR4    | _      | _      | _      | _      | _          | _      | TMR2IF    | TMR1IF | 132                 |

| IOCAP   | IOCAP7 | IOCAP6 | IOCAP5 | IOCAP4 | IOCAP3     | IOCAP2 | IOCAP1    | IOCAP0 | 209                 |

| IOCAN   | IOCAN7 | IOCAN6 | IOCAN5 | IOCAN4 | IOCAN3     | IOCAN2 | IOCAN1    | IOCAN0 | 209                 |

| IOCAF   | IOCAF7 | IOCAF6 | IOCAF5 | IOCAF4 | IOCAF3     | IOCAF2 | IOCAF1    | IOCAF0 | 209                 |

| IOCBP   | IOCBP7 | IOCBP6 | IOCBP5 | IOCBP4 | IOCBP3     | IOCBP2 | IOCBP1    | IOCBP0 | 210                 |

| IOCBN   | IOCBN7 | IOCBN6 | IOCBN5 | IOCBN4 | IOCBN3     | IOCBN2 | IOCBN1    | IOCBN0 | 210                 |

| IOCBF   | IOCBF7 | IOCBF6 | IOCBF5 | IOCBF4 | IOCBF3     | IOCBF2 | IOCBF1    | IOCBF0 | 210                 |

| IOCCP   | IOCCP7 | IOCCP6 | IOCCP5 | IOCCP4 | IOCCP3     | IOCCP2 | IOCCP1    | IOCCP0 | 211                 |

| IOCCN   | IOCCN7 | IOCCN6 | IOCCN5 | IOCCN4 | IOCCN3     | IOCCN2 | IOCCN1    | IOCCN0 | 211                 |

| IOCCF   | IOCCF7 | IOCCF6 | IOCCF5 | IOCCF4 | IOCCF3     | IOCCF2 | IOCCF1    | IOCCF0 | 211                 |

| IOCEP   |        | —      |        |        | IOCEP3     | —      | —         | _      | 212                 |

| IOCEN   |        | —      |        |        | IOCEN3     | _      | —         | _      | 212                 |

| IOCEF   |        |        |        |        | IOCEF3     | —      | —         |        | 213                 |

| STATUS  | _      | _      | _      | TO     | PD         | Z      | DC        | С      | 29                  |

| VREGCON |        | —      | _      | _      | —          | —      | VREGPM    | _      | 141                 |

| CPUDOZE | IDLEN  | DOZEN  | ROI    | DOE    | _          |        | DOZE<2:0> |        | 142                 |

| WDTCON0 | _      | _      |        | ١      | NDTPS<4:0> | >      |           | SWDTEN | 148                 |

### TABLE 11-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

Legend: — = unimplemented location, read as '0'. Shaded cells are not used in Power-Down mode.

| R/W-1/1                                 | R/W-1/1                           | R/W-1/1 | R/W-1/1 | R/W-1/1                                               | R/W-1/1 | R/W-1/1 | R/W-1/1 |  |  |  |

|-----------------------------------------|-----------------------------------|---------|---------|-------------------------------------------------------|---------|---------|---------|--|--|--|

| SLRA7                                   | SLRA6                             | SLRA5   | SLRA4   | SLRA3                                                 | SLRA2   | SLRA1   | SLRA0   |  |  |  |

| bit 7 bit 0                             |                                   |         |         |                                                       |         |         |         |  |  |  |

|                                         |                                   |         |         |                                                       |         |         |         |  |  |  |

| Legend:                                 |                                   |         |         |                                                       |         |         |         |  |  |  |

| R = Readable                            | R = Readable bit W = Writable bit |         |         | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |  |

| u = Bit is unchanged x = Bit is unknown |                                   |         |         | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |  |

### REGISTER 14-7: SLRCONA: PORTA SLEW RATE CONTROL REGISTER

bit 7-0 SLRA<7:0>: PORTA Slew Rate Enable bits For RA<7:0> pins, respectively 1 = Port pin slew rate is limited

'1' = Bit is set

0 = Port pin slews at maximum rate

### **REGISTER 14-8: INLVLA: PORTA INPUT LEVEL CONTROL REGISTER**

'0' = Bit is cleared

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| INLVLA7 | INLVLA6 | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 INLVLA<7:0>: PORTA Input Level Select bits For RA<7:0> pins, respectively 1 = ST input used for PORT reads and interrupt-on-change 0 = TTL input used for PORT reads and interrupt-on-change

### TABLE 14-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| PORTA   | RA7     | RA6     | RA5     | RA4     | RA3     | RA2     | RA1     | RA0     | 173                 |

| TRISA   | TRISA7  | TRISA6  | TRISA5  | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  | 173                 |

| LATA    | LATA7   | LATA6   | LATA5   | LATA4   | LATA3   | LATA2   | LATA1   | LATA0   | 174                 |

| ANSELA  | ANSA7   | ANSA6   | ANSA5   | ANSA4   | ANSA3   | ANSA2   | ANSA1   | ANSA0   | 174                 |

| WPUA    | WPUA7   | WPUA6   | WPUA5   | WPUA4   | WPUA3   | WPUA2   | WPUA1   | WPUA0   | 175                 |

| ODCONA  | ODCA7   | ODCA6   | ODCA5   | ODCA4   | ODCA3   | ODCA2   | ODCA1   | ODCA0   | 175                 |

| SLRCONA | SLRA7   | SLRA6   | SLRA5   | SLRA4   | SLRA3   | SLRA2   | SLRA1   | SLRA0   | 176                 |

| INLVLA  | INLVLA7 | INLVLA6 | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 176                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

Note 1: Unimplemented, read as '1'.

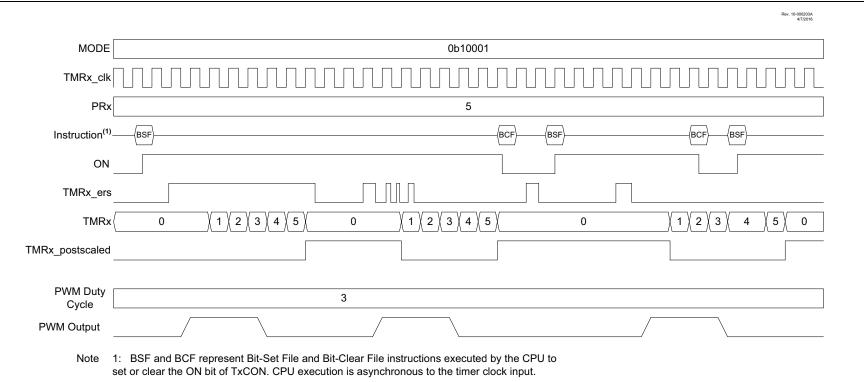

### FIGURE 27-12: RISING EDGE-TRIGGERED MONOSTABLE MODE TIMING DIAGRAM (MODE = 10001)

| Name     | Bit 7       | Bit 6           | Bit 5        | Bit 4       | Bit 3                   | Bit 2     | Bit 1  | Bit 0  | Register<br>on Page |

|----------|-------------|-----------------|--------------|-------------|-------------------------|-----------|--------|--------|---------------------|

| CCP1CON  | EN          | _               | OUT          | FMT         |                         | MODE      | <3:0>  |        | 317                 |

| CCP2CON  | EN          | _               | OUT          | FMT         |                         |           | 317    |        |                     |

| CCPTMRS0 | —           | _               | —            | —           | C2TSEL<1:0> C1TSEL<1:0> |           |        |        | 320                 |

| CCPTMRS1 | —           | _               | —            | —           | P2TSE                   | L<1:0>    | C1TSE  | L<1:0> | 321                 |

| INTCON   | GIE         | PEIE            | —            | —           | —                       | —         |        | INTEDG | 119                 |

| PIE1     | OSFIE       | CSWIE           | —            | —           | —                       | _         | _      | ADIE   | 121                 |

| PIR1     | OSFIF       | CSWIF           | —            | —           | —                       | —         | _      | ADIF   | 129                 |

| PR2      | Timer2 Modu | ule Period Re   | gister       |             |                         |           |        |        |                     |

| TMR2     | Holding Reg | ister for the 8 | -bit TMR2 Re | gister      |                         |           |        |        |                     |

| T2CON    | ON          |                 | CKPS<2:0>    |             |                         | OUTP      | S<3:0> |        | 306                 |

| T2CLKCON | _           | _               | _            | _           |                         | CS<       | 3:0>   |        | 305                 |

| T2RST    | _           | _               | _            | — RSEL<3:0> |                         |           |        |        |                     |

| T2HLT    | PSYNC       | CKPOL           | CKSYNC       |             |                         | MODE<4:0> |        |        | 307                 |

| TABLE 27-2: | SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2 |

|-------------|---------------------------------------------|

|-------------|---------------------------------------------|

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for Timer2 module.

\* Page provides register information.

### REGISTER 28-4: CCPRxH REGISTER: CCPx REGISTER HIGH BYTE

| R/W-x/x  | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x |

|----------|---------|---------|---------|---------|---------|---------|---------|

|          |         |         | CCPRx   | <15:8>  |         |         |         |

| bit 7    |         |         |         |         |         |         | bit 0   |

|          |         |         |         |         |         |         |         |

| l egend: |         |         |         |         |         |         |         |

| Legend:              |                      |                                                      |

|----------------------|----------------------|------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                   |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Reset |

| '1' = Bit is set     | '0' = Bit is cleared |                                                      |

bit 7-0

CCPxMODE = Capture mode

CCPRxH<7:0>: Captured value of TMR1H

CCPxMODE = Compare mode

CCPRxH<7:0>: MS Byte compared to TMR1H

CCPxMODE = PWM modes when CCPxFMT = 0:

CCPRxH<7:2>: Not used

CCPRxH<1:0>: Pulse-width Most Significant two bits

CCPxMODE = PWM modes when CCPxFMT = 1:

CCPRxH<7:0>: Pulse-width Most Significant eight bits

### REGISTER 28-5: CCPTMRS0: CCP TIMERS CONTROL 0 REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-1/1 | R/W-0/0 | R/W-1/1 |

|-------|-----|-----|-----|---------|---------|---------|---------|

| —     | —   | —   | —   | C2TSE   | EL<1:0> | C1TSE   | L<1:0>  |

| bit 7 |     |     |     |         |         |         | bit 0   |

| Legend:              |                      |                                                      |

|----------------------|----------------------|------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                   |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Reset |

| '1' = Bit is set     | '0' = Bit is cleared |                                                      |

| bit 7-4 | Unimplemented: Read as '0'                                                                                                                                                                                                                       |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3-2 | <b>C2TSEL&lt;1:0&gt;:</b> CCP2 Timer Selection<br>11 = CCP2 based on TMR1 (Capture/Compare) or TMR2 (PWM)<br>10 = CCP2 based on TMR1 (Capture/Compare) or TMR2 (PWM)<br>01 = CCP2 based on TMR1 (Capture/Compare) or TMR2 (PWM)<br>00 = Reserved |

| bit 1-0 | C1TSEL<1:0>: CCP2 Timer Selection<br>11 = CCP1 based on TMR1 (Capture/Compare) or TMR2 (PWM)<br>10 = CCP1 based on TMR1 (Capture/Compare) or TMR2 (PWM)<br>01 = CCP1 based on TMR1 (Capture/Compare) or TMR2 (PWM)<br>00 = Reserved              |

### REGISTER 30-3: CWG1DBR: CWG1 RISING DEAD-BAND COUNTER REGISTER

| U-0              | U-0   | R/W-x/u           | R/W-x/u                                                                  | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |

|------------------|-------|-------------------|--------------------------------------------------------------------------|---------|---------|---------|---------|--|

| —                | —     |                   | DBR<5:0>                                                                 |         |         |         |         |  |

| bit 7            |       |                   |                                                                          |         |         |         | bit 0   |  |

|                  |       |                   |                                                                          |         |         |         |         |  |

| Legend:          |       |                   |                                                                          |         |         |         |         |  |

| R = Readable     | bit   | W = Writable      | W = Writable bit U = Unimplemented bit, read as '0'                      |         |         |         |         |  |

| u = Bit is uncha | anged | x = Bit is unkr   | x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |         |  |

| '1' = Bit is set |       | '0' = Bit is clea | '0' = Bit is cleared q = Value depends on condition                      |         |         |         |         |  |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 DBR<5:0>: Rising Event Dead-Band Value for Counter bits

### REGISTER 30-4: CWG1DBF: CWG1 FALLING DEAD-BAND COUNTER REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   |         |         | DBF     | <5:0>   |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

|       |     |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 DBF<5:0>: Falling Event Dead-Band Value for Counter bits

# PIC16(L)F15354/55

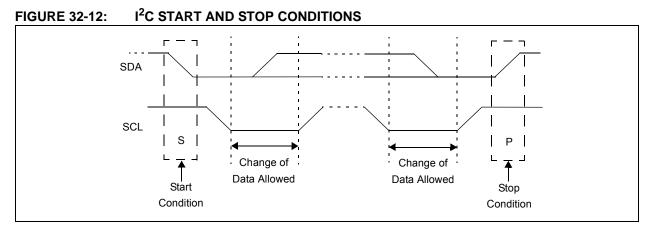

### 32.4.9 ACKNOWLEDGE SEQUENCE

The 9th SCL pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDA line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge (ACK) is an active-low signal, pulling the SDA line low indicates to the transmitter that the device has received the transmitted data and is ready to receive more.

The result of an  $\overline{\text{ACK}}$  is placed in the ACKSTAT bit of the SSPxCON2 register.

Slave software, when the AHEN and DHEN bits are set, allow the user to set the  $\overline{ACK}$  value sent back to the transmitter. The ACKDT bit of the SSPxCON2 register is set/cleared to determine the response.

There are certain conditions where an ACK will not be sent by the slave. If the BF bit of the SSPxSTAT register or the SSPOV bit of the SSPxCON1 register are set when a byte is received.

When the module is addressed, after the eighth falling edge of SCL on the bus, the ACKTIM bit of the SSPxCON3 register is set. The ACKTIM bit indicates the acknowledge time of the active bus. The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is enabled.

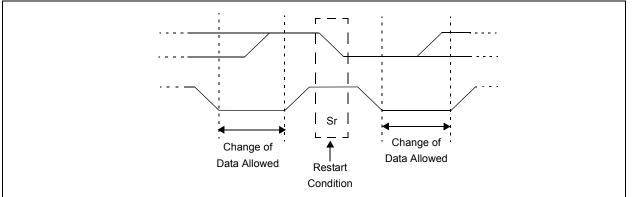

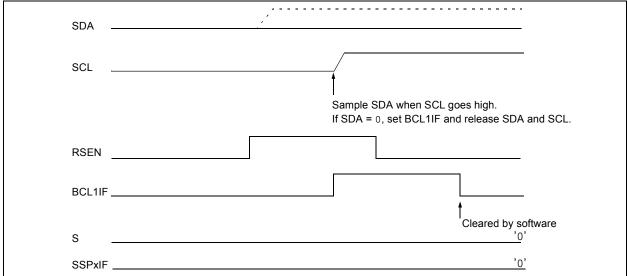

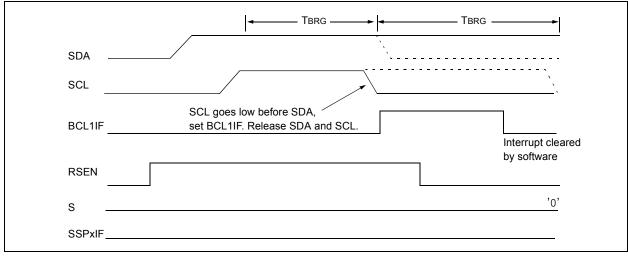

## 32.6.13.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level (Case 1).

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1' (Case 2).

When the user releases SDA and the pin is allowed to float high, the BRG is loaded with SSPxADD and counts down to zero. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 32-36). If SDA is sampled high, the BRG is reloaded and begins

counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, see Figure 32-37.

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

### FIGURE 32-36: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

### 33.3 EUSART Baud Rate Generator (BRG)

The Baud Rate Generator (BRG) is an 8-bit or 16-bit timer that is dedicated to the support of both the asynchronous and synchronous EUSART operation. By default, the BRG operates in 8-bit mode. Setting the BRG16 bit of the BAUDxCON register selects 16-bit mode.

The SPxBRGH, SPxBRGL register pair determines the period of the free running baud rate timer. In Asynchronous mode the multiplier of the baud rate period is determined by both the BRGH bit of the TXxSTA register and the BRG16 bit of the BAUDxCON register. In Synchronous mode, the BRGH bit is ignored.

Table 33-1 contains the formulas for determining the baud rate. Example 33-1 provides a sample calculation for determining the baud rate and baud rate error.

Typical baud rates and error values for various Asynchronous modes have been computed for your convenience and are shown in Table 33-3. It may be advantageous to use the high baud rate (BRGH = 1), or the 16-bit BRG (BRG16 = 1) to reduce the baud rate error. The 16-bit BRG mode is used to achieve slow baud rates for fast oscillator frequencies.

Writing a new value to the SPxBRGH, SPxBRGL register pair causes the BRG timer to be reset (or cleared). This ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

If the system clock is changed during an active receive operation, a receive error or data loss may result. To avoid this problem, check the status of the RCIDL bit to make sure that the receive operation is idle before changing the system clock.

### EXAMPLE 33-1: CALCULATING BAUD RATE ERROR

For a device with Fosc of 16 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG:

Desired Baud Rate =  $\frac{FOSC}{64([SPBRGH:SPBRGL] + 1)}$

Solving for SPxBRGH:SPxBRGL:

| $X = \frac{Fosc}{\frac{Desired Baud Rate}{64} - 1}$                     |

|-------------------------------------------------------------------------|

| $= \frac{\frac{16000000}{9600}}{64} - 1$                                |

| = [25.042] = 25                                                         |

| $Calculated Baud Rate = \frac{16000000}{64(25+1)}$                      |

| = 9615                                                                  |

| Error = $\frac{Calc. Baud Rate - Desired Baud Rate}{Desired Baud Rate}$ |

| $=\frac{(9615-9600)}{9600} = 0.16\%$                                    |

### 33.4.1.6 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

| Note: | If the device is configured as a slave and  |

|-------|---------------------------------------------|

|       | the TX/CK function is on an analog pin, the |

|       | corresponding ANSEL bit must be cleared.    |

### 33.4.1.7 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCxREG is read to access the FIFO. When this happens the OERR bit of the RCxSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCxREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCxSTA register or by clearing the SPEN bit which resets the EUSART.

### 33.4.1.8 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCxSTA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCxSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCxREG.

## 33.4.1.9 Synchronous Master Reception Set-up:

- 1. Initialize the SPxBRGH, SPxBRGL register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 4. Ensure bits CREN and SREN are clear.

- 5. If interrupts are desired, set the RXxIE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- 6. If 9-bit reception is desired, set bit RX9.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- Interrupt flag bit RXxIF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RXxIE was set.

- 9. Read the RCxSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCxREG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCxSTA register or by clearing the SPEN bit which resets the EUSART.

| RX/DT<br>pin                  | bit 0 bit 1 bit 2 bit 3 bit 4 bit 5 bit 6 bit 7                         |            |

|-------------------------------|-------------------------------------------------------------------------|------------|

| TX/CK pin<br>(SCKP = 0)       |                                                                         |            |

| TX/CK pin<br>(SCKP = 1)       |                                                                         |            |

| Write to<br>bit SREN          |                                                                         |            |

| SREN bit                      |                                                                         |            |

| CREN bit                      |                                                                         | <u>'0'</u> |

| RXxIF bit<br>(Interrupt) ———— |                                                                         | <b>~</b>   |

| Read<br>RCxREG ———            |                                                                         | 1          |

| Note: Timing dia              | agram demonstrates Sync Master mode with bit SREN = 1 and bit BRGH = 0. |            |

### FIGURE 33-12: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

| R/W-0/0              | R/W-0/0                                                                                                                                     | R/W-0/0                                                                 | R/W-0/0        | R/W-0/0                            | R-0/0             | R-0/0         | R-0/0    |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------|------------------------------------|-------------------|---------------|----------|--|--|

| SPEN <sup>(1)</sup>  | RX9                                                                                                                                         | SREN                                                                    | CREN           | ADDEN                              | FERR              | OERR          | RX9D     |  |  |

| bit 7                |                                                                                                                                             |                                                                         |                |                                    |                   |               | bit 0    |  |  |

|                      |                                                                                                                                             |                                                                         |                |                                    |                   |               |          |  |  |

| Legend:              |                                                                                                                                             |                                                                         |                |                                    |                   | (2)           |          |  |  |

| R = Readable bit     |                                                                                                                                             | W = Writable                                                            |                | U = Unimplemented bit, read as '0' |                   |               |          |  |  |

| u = Bit is unchanged |                                                                                                                                             | x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Reset |                |                                    |                   |               |          |  |  |

| '1' = Bit is set     |                                                                                                                                             | '0' = Bit is cle                                                        | ared           |                                    |                   |               |          |  |  |

| bit 7                | SPEN: Serial                                                                                                                                | Port Enable bi                                                          | it(1)          |                                    |                   |               |          |  |  |

|                      | 1 = Serial port enabled                                                                                                                     |                                                                         |                |                                    |                   |               |          |  |  |

|                      |                                                                                                                                             | rt disabled (he                                                         | ld in Reset)   |                                    |                   |               |          |  |  |

| bit 6                | <b>RX9:</b> 9-Bit Re                                                                                                                        | eceive Enable I                                                         | oit            |                                    |                   |               |          |  |  |

|                      | 1 = Selects 9-bit reception                                                                                                                 |                                                                         |                |                                    |                   |               |          |  |  |

|                      | 0 = Selects 8                                                                                                                               | •                                                                       | -1             |                                    |                   |               |          |  |  |

| bit 5                | SREN: Single Receive Enable bit                                                                                                             |                                                                         |                |                                    |                   |               |          |  |  |

|                      | <u>Asynchronous mode</u> :<br>Unused in this mode – value ignored                                                                           |                                                                         |                |                                    |                   |               |          |  |  |

|                      | Synchronous mode – Master:                                                                                                                  |                                                                         |                |                                    |                   |               |          |  |  |

|                      | 1 = Enables single receive                                                                                                                  |                                                                         |                |                                    |                   |               |          |  |  |

|                      | 0 = Disables single receive                                                                                                                 |                                                                         |                |                                    |                   |               |          |  |  |

|                      | This bit is cleared after reception is complete.<br><u>Synchronous mode – Slave</u>                                                         |                                                                         |                |                                    |                   |               |          |  |  |

|                      |                                                                                                                                             | s mode – value                                                          |                |                                    |                   |               |          |  |  |

| bit 4                | CREN: Continuous Receive Enable bit                                                                                                         |                                                                         |                |                                    |                   |               |          |  |  |

|                      | Asynchronous mode:                                                                                                                          |                                                                         |                |                                    |                   |               |          |  |  |

|                      | 1 = Enables continuous receive until enable bit CREN is cleared                                                                             |                                                                         |                |                                    |                   |               |          |  |  |

|                      | 0 = Disables continuous receive<br>Svnchronous mode:                                                                                        |                                                                         |                |                                    |                   |               |          |  |  |

|                      | 1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)                                                       |                                                                         |                |                                    |                   |               |          |  |  |

|                      |                                                                                                                                             | continuous red                                                          |                |                                    |                   |               | ,        |  |  |

| bit 3                | ADDEN: Add                                                                                                                                  | ress Detect Er                                                          | able bit       |                                    |                   |               |          |  |  |

|                      | Asynchronous mode 9-bit (RX9 = 1):                                                                                                          |                                                                         |                |                                    |                   |               |          |  |  |

|                      | 1 = Enables address detection – enable interrupt and load of the receive buffer when the ninth bit in                                       |                                                                         |                |                                    |                   |               |          |  |  |

|                      | the receive buffer is set<br>0 = Disables address detection, all bytes are received and ninth bit can be used as parity bit                 |                                                                         |                |                                    |                   |               |          |  |  |

|                      | Asynchronous mode 8-bit ( $RX9 = 0$ ):                                                                                                      |                                                                         |                |                                    |                   |               |          |  |  |

|                      | Unused in this                                                                                                                              | s mode – value                                                          | e ignored      |                                    |                   |               |          |  |  |

| bit 2                | FERR: Framing Error bit                                                                                                                     |                                                                         |                |                                    |                   |               |          |  |  |

|                      | <ul> <li>1 = Framing error (can be updated by reading RCxREG register and receive next valid byte)</li> <li>0 = No framing error</li> </ul> |                                                                         |                |                                    |                   |               |          |  |  |

| bit 1                | OERR: Overr                                                                                                                                 | un Error bit                                                            |                |                                    |                   |               |          |  |  |

|                      | 1 = Overrun<br>0 = No overr                                                                                                                 |                                                                         | leared by clea | aring bit CREN                     | )                 |               |          |  |  |

| bit 0                |                                                                                                                                             | bit of Received                                                         |                |                                    |                   |               |          |  |  |

|                      | This can be address/data bit or a parity bit and must be calculated by user firmware.                                                       |                                                                         |                |                                    |                   |               |          |  |  |

|                      | e EUSART mod<br>sociated TRIS b                                                                                                             |                                                                         |                |                                    | state to drive as | needed. Confi | gure the |  |  |

### REGISTER 33-2: RCxSTA: RECEIVE STATUS AND CONTROL REGISTER

'1' = Bit is set

## **REGISTER 33-7:** SPxBRGH<sup>(1, 2)</sup>: BAUD RATE GENERATOR HIGH REGISTER

| R/W-0                                                                                      | R/W-0 | R/W-0          | R/W-0 | R/W-0        | R/W-0            | R/W-0  | R/W-0 |

|--------------------------------------------------------------------------------------------|-------|----------------|-------|--------------|------------------|--------|-------|

|                                                                                            |       |                | SPxBF | RG<15:8>     |                  |        |       |

| bit 7                                                                                      |       |                |       |              |                  |        | bit 0 |

|                                                                                            |       |                |       |              |                  |        |       |

| Legend:                                                                                    |       |                |       |              |                  |        |       |

| R = Readable b                                                                             | bit   | W = Writable b | oit   | U = Unimplen | nented bit, read | as '0' |       |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Res |       |                |       |              | ther Resets      |        |       |

bit 7 SPxBRG<15:8>: Upper eight bits of the Baud Rate Generator

'0' = Bit is cleared

Note 1: SPxBRGH value is ignored for all modes unless BAUDxCON<BRG16> is active.

**2:** Writing to SPxBRGH resets the BRG counter.

## 37.2 Standard Operating Conditions

| 37.2 Standard Operating Conditions                                 | Λ                 |

|--------------------------------------------------------------------|-------------------|

| The standard operating conditions for any device are defined as:   | $\langle \rangle$ |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$               |                   |

| VDD — Operating Supply Voltage <sup>(1)</sup>                      | $\sim$            |

| PIC16LF15354/55                                                    |                   |

| VDDMIN (Fosc $\leq$ 16 MHz)                                        |                   |

| VDDMIN (Fosc $\leq$ 32 MHz)                                        | +2.5V             |

| VDDMAX                                                             | +3.6V             |

| PIC16F15354/55                                                     | $\sim$            |

| VDDMIN (Fosc $\leq$ 16 MHz)                                        | +2.3V             |

| VDDMIN (Fosc $\leq$ 32 MHz)                                        | +2.5V             |

| VDDMAX                                                             |                   |

| TA — Operating Ambient Temperature Range                           | $\langle \rangle$ |

| Industrial Temperature                                             |                   |

| TA_MIN                                                             | -40°C             |

|                                                                    | +85°C             |

| Extended Temperature                                               | $\geq$            |

| TA_MIN                                                             | ~40°C             |

|                                                                    |                   |

| Note 1: See Parameter Supply Voltage, DS Characteristics: Supply V | /oltage.          |

## **FIGURE 37-8:** RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP

# PIC16(L)F15354/55

### TABLE 37-25: I<sup>2</sup>C BUS DATA REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) |                 |                            |              |            |      |       |                                             |

|---------------------------------------------------------|-----------------|----------------------------|--------------|------------|------|-------|---------------------------------------------|

| Param.<br>No.                                           | Symbol<br>Thigh | Characteristic             |              | Min.       | Max. | Units | Conditions                                  |

| SP100*                                                  |                 | Clock high time            | 100 kHz mode | 4.0        | —    | μS    | Device must operate at a minimum of 1.5 MHz |

|                                                         |                 |                            | 400 kHz mode | 0.6        | _    | μS    | Device must operate at a minimum of 10 MHz  |

|                                                         |                 |                            | SSP module   | 1.5Tcy     |      |       |                                             |

| SP101* TLOW                                             | TLOW            | Clock low time             | 100 kHz mode | 4.7        | —    | μS    | Device must operate at a minimum of 1.5 MHz |

|                                                         |                 |                            | 400 kHz mode | 1.3        | —    | μS    | Device must operate at a minimum of 10 MHz  |

|                                                         |                 |                            | SSP module   | 1.5Tcy     |      |       |                                             |

| SP102* Tr                                               | TR              | SDA and SCL rise<br>time   | 100 kHz mode | —          | 1000 | ns    |                                             |

|                                                         |                 |                            | 400 kHz mode | 20 + 0.1CB | 300  | ns    | CB is specified to be from 10-400 pF        |

| SP103* T                                                | TF              | SDA and SCL fall time      | 100 kHz mode | —          | 250  | ns    |                                             |

|                                                         |                 |                            | 400 kHz mode | 20 + 0.1CB | 250  | ns    | CB is specified to be from 10-400 pF        |

| SP106* 1                                                | THD:DAT         | Data input hold time       | 100 kHz mode | 0          |      | ns    |                                             |

|                                                         |                 |                            | 400 kHz mode | 0          | 0.9  | μS    | ]                                           |

| SP107*                                                  | TSU:DAT         | Data input setup time      | 100 kHz mode | 250        | _    | ns    | (Note 2)                                    |

|                                                         |                 |                            | 400 kHz mode | 100        | _    | ns    |                                             |

| SP109*                                                  | ΤΑΑ             | Output valid from<br>clock | 100 kHz mode | —          | 3500 | ns    | (Note 1)                                    |

|                                                         |                 |                            | 400 kHz mode | —          | _    | ns    |                                             |

| SP110*                                                  | TBUF            | Bus free time              | 100 kHz mode | 4.7        | _    | μS    | Time the bus must be free                   |

|                                                         |                 |                            | 400 kHz mode | 1.3        | —    | μs    | before a new transmission<br>can start      |

| SP111                                                   | Св              | Bus capacitive loading     |              | _          | 400  | pF    |                                             |

\* These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

2: A Fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement TsU:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line TR max. + TSU:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.