Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 224 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15355-e-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

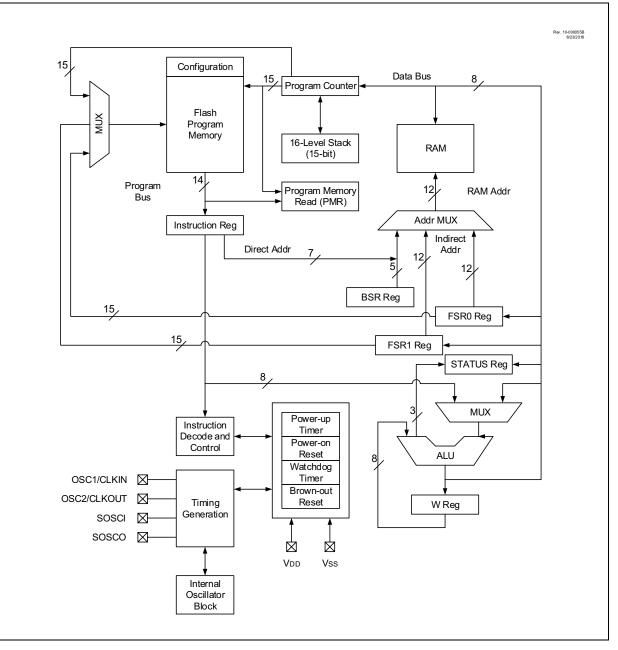

# 1.0 DEVICE OVERVIEW

The PIC16(L)F15354/55 are described within this data sheet. The PIC16(L)F15354/55 devices are available in 28-pin SPDIP, SSOP, SOIC, and UQFN packages. Figure 1-1 shows a block diagram of the PIC16(L)F15354/55 devices. Table 1-2 shows the pinout descriptions.

Reference Table 1-1 for peripherals available per device.

#### TABLE 1-1: DEVICE PERIPHERAL SUMMARY

| Peripheral                                                                                 |            | PIC16(L)F15354/55 |  |  |  |

|--------------------------------------------------------------------------------------------|------------|-------------------|--|--|--|

| Analog-to-Digital Converter                                                                |            | •                 |  |  |  |

| Digital-to-Analog Converter (DAC1)                                                         |            | •                 |  |  |  |

| Fixed Voltage Reference (FVR)                                                              |            | •                 |  |  |  |

| Enhanced Universal Synchronous/Asynchronous Receiver/<br>Transmitter (EUSART1 and EUSART2) |            | •                 |  |  |  |

| Numerically Controlled Oscillator (NCO1)                                                   |            | •                 |  |  |  |

| Temperature Indicator Module (TIM)                                                         |            | •                 |  |  |  |

| Zero-Cross Detect (ZCD1)                                                                   |            |                   |  |  |  |

| Capture/Compare/PWM Modules (CCP)                                                          |            |                   |  |  |  |

| 00                                                                                         | CP1        | •                 |  |  |  |

| 00                                                                                         | CP2        | •                 |  |  |  |

| Comparator Module (Cx)                                                                     |            |                   |  |  |  |

|                                                                                            | C1         | •                 |  |  |  |

|                                                                                            | C2         | •                 |  |  |  |

| Configurable Logic Cell (CLC)                                                              |            |                   |  |  |  |

|                                                                                            | _C1        | •                 |  |  |  |

|                                                                                            | _C2        | •                 |  |  |  |

|                                                                                            | _C3        | •                 |  |  |  |

|                                                                                            | _C4        | •                 |  |  |  |

| Complementary Waveform Generator (CWG)                                                     |            |                   |  |  |  |

|                                                                                            | /G1        | •                 |  |  |  |

| Master Synchronous Serial Ports (MSSP)                                                     |            |                   |  |  |  |

| MSS                                                                                        |            | •                 |  |  |  |

| MSS<br>Dules Width Meduleter (DWA)                                                         | 5P2        | •                 |  |  |  |

| Pulse-Width Modulator (PWM)                                                                | /M3        |                   |  |  |  |

|                                                                                            | /M3<br>/M4 | •                 |  |  |  |

|                                                                                            | /M4<br>/M5 | •                 |  |  |  |

|                                                                                            | /M6        | •                 |  |  |  |

| Timers                                                                                     |            | -                 |  |  |  |

|                                                                                            | ier0       | •                 |  |  |  |

| Tim                                                                                        |            | •                 |  |  |  |

|                                                                                            | -          | •                 |  |  |  |

## 3.0 ENHANCED MID-RANGE CPU

This family of devices contains an enhanced mid-range 8-bit CPU core. The CPU has 48 instructions. Interrupt capability includes automatic context saving.

FIGURE 3-1: CORE DATA PATH DIAGRAM

The hardware stack is 16-levels deep and has

Overflow and Underflow Reset capability. Direct,

Indirect, and Relative Addressing modes are available.

Two File Select Registers (FSRs) provide the ability to

read program and data memory.

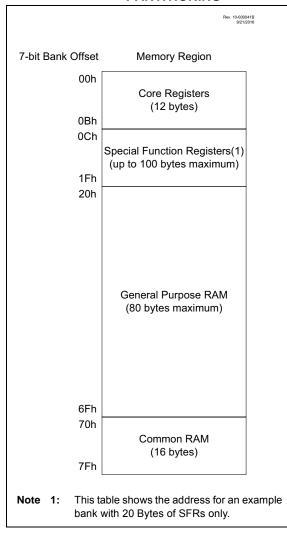

#### 4.3 Data Memory Organization

The data memory is partitioned into 64 memory banks with 128 bytes in each bank.

#### FIGURE 4-3: BANKED MEMORY PARTITIONING

Each bank consists of:

- · 12 core registers

- Up to 100 Special Function Registers (SFR)

- Up to 80 bytes of General Purpose RAM (GPR)

- · 16 bytes of common RAM

#### 4.3.1 BANK SELECTION

The active bank is selected by writing the bank number into the Bank Select Register (BSR). Unimplemented memory will read as '0'. All data memory can be accessed either directly (via instructions that use the file registers) or indirectly via the two File Select Registers (FSR). See **Section 4.6 "Indirect Addressing**" for more information.

Data memory uses a 13-bit address. The upper six bits of the address define the Bank address and the lower seven bits select the registers/RAM in that bank.

#### 4.3.2 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation. The core registers occupy the first 12 addresses of every data memory bank (addresses x00h/x08h through x0Bh/x8Bh). These registers are listed below in Table 4-3.

TABLE 4-3: CORE REGISTERS

| Addresses    | BANKx  |

|--------------|--------|

| x00h or x80h | INDF0  |

| x01h or x81h | INDF1  |

| x02h or x82h | PCL    |

| x03h or x83h | STATUS |

| x04h or x84h | FSR0L  |

| x05h or x85h | FSR0H  |

| x06h or x86h | FSR1L  |

| x07h or x87h | FSR1H  |

| x08h or x88h | BSR    |

| x09h or x89h | WREG   |

| x0Ah or x8Ah | PCLATH |

| x0Bh or x8Bh | INTCON |

| Address | Name                                                                                  | Bit 7                    | Bit 6               | Bit 5              | Bit 4         | Bit 3             | Bit 2          | Bit 1      | Bit 0     | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------|---------------------------------------------------------------------------------------|--------------------------|---------------------|--------------------|---------------|-------------------|----------------|------------|-----------|-----------------------|----------------------------|

| Bank 11 |                                                                                       |                          |                     |                    |               |                   |                |            |           |                       |                            |

|         |                                                                                       |                          |                     | CPU COF            | RE REGISTERS; | see Table 4-3 for | specifics      |            |           |                       |                            |

| 58Ch    | Ch NCO1ACCL NCO1ACC<7:0>                                                              |                          |                     |                    |               |                   |                |            |           | 0000 0000             | 0000 0000                  |

| 58Dh    | NCO1ACCH                                                                              |                          |                     |                    | NCO1AC        | C<15:8>           |                |            |           | 0000 0000             | 0000 0000                  |

| 58Eh    | NCO1ACCU                                                                              | _                        | _                   | —                  | _             |                   | NCO1           | ACC<19:16> |           | 0000                  | 0000                       |

| 58Fh    | NCO1INCL                                                                              |                          |                     |                    | NCO1IN        | C<7:0>            |                |            |           | 0000 0001             | 0000 0001                  |

| 590h    | NCO1INCH                                                                              |                          |                     |                    | NCO1INC       | C<15:8>           |                |            |           | 0000 0000             | 0000 0000                  |

| 591h    | NCO1INCU                                                                              | _                        | _                   | _                  |               |                   | NCO1INC<19:16> |            |           |                       | 0000                       |

| 592h    | NCO1CON                                                                               | N1EN                     | _                   | N1OUT              | N1POL         | _                 | _              | _          | N1PFM     | 0-000                 | 0-000                      |

| 593h    | NCO1CLK                                                                               |                          | N1PWS<2:0>          |                    | _             | —                 |                | N1CKS<2:0> | >         | 000000                | 000000                     |

| 594h    | —                                                                                     |                          |                     |                    | Unimpler      | nented            |                |            |           |                       |                            |

| 595h    | —                                                                                     |                          |                     |                    | Unimpler      | mented            |                |            |           |                       |                            |

| 596h    | —                                                                                     |                          |                     |                    | Unimpler      | mented            |                |            |           |                       |                            |

| 597h    | —                                                                                     |                          |                     |                    | Unimpler      | mented            |                |            |           |                       |                            |

| 598h    | —                                                                                     |                          |                     |                    | Unimpler      | mented            |                |            |           |                       |                            |

| 599h    | —                                                                                     |                          | Unimplemented       |                    |               |                   |                |            |           |                       |                            |

| 59Ah    | —                                                                                     |                          |                     |                    | Unimpler      | mented            |                |            |           |                       |                            |

| 59Bh    | —                                                                                     | Unimplemented            |                     |                    |               |                   |                |            |           |                       |                            |

| 59Ch    | 9Ch TMR0L Holding Register for the Least Significant Byte of the 16-bit TMR0 Register |                          |                     |                    |               |                   |                | 0000 0000  | 0000 0000 |                       |                            |

| 59Dh    | TMR0H                                                                                 | Holding Register for the | he Most Significant | Byte of the 16-bit | TMR0 Register |                   |                |            |           | 1111 1111             | 1111 1111                  |

| 59Eh    | T0CON0                                                                                | TOEN                     | _                   | T0OUT              | T016BIT       |                   | TOOL           | JTPS<3:0>  |           | 0-00 0000             | 0-00 0000                  |

| 59Fh    | T0CON1                                                                                |                          | T0CS<2:0>           |                    | TOASYNC       |                   | TOC            | KPS<3:0>   |           | 0000 0000             | 0000 0000                  |

#### TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

| Address   | Name   | Bit 7         | Bit 6 | Bit 5   | Bit 4         | Bit 3            | Bit 2       | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|-----------|--------|---------------|-------|---------|---------------|------------------|-------------|-------|-------|-----------------------|----------------------------|

| Bank 62   |        |               |       |         |               |                  |             |       |       |                       |                            |

|           |        |               |       | CPU COF | RE REGISTERS; | see Table 4-3 fo | r specifics |       |       |                       |                            |

| 1F0Ch     | _      |               |       |         | Unimple       | mented           |             |       |       |                       |                            |

| 1F0Dh     | _      | Unimplemented |       |         |               |                  |             |       |       |                       |                            |

| 1F0Eh     | _      | Unimplemented |       |         |               |                  |             |       |       |                       |                            |

| 1F0Fh     | _      |               |       |         | Unimple       | mented           |             |       |       |                       |                            |

| 1F10h     | RA0PPS | —             | —     | —       |               |                  | RA0PPS<4:0  | >     |       | 00 0000               | uu uuuu                    |

| 1F11h     | RA1PPS | —             | —     | —       |               |                  | RA1PPS<4:0  | >     |       | 00 0000               | uu uuuu                    |

| 1F12h     | RA2PPS | —             | _     | —       |               |                  | RA2PPS<4:0  | >     |       | 00 0000               | uu uuuu                    |

| 1F13h     | RA3PPS | —             | _     | —       |               |                  | RA3PPS<4:0  | >     |       | 00 0000               | uu uuuu                    |

| 1F14h     | RA4PPS | -             | -     | —       |               |                  | RA4PPS<4:0  | >     |       | 00 0000               | uu uuuu                    |

| 1F15h     | RA5PPS | —             | _     | _       |               |                  | RA5PPS<4:0  | >     |       | 00 0000               | uu uuuu                    |

| 1F16h     | RA6PPS | —             | _     | _       |               | RA6PPS<4:0>      |             |       |       |                       | uu uuuu                    |

| 1F17h     | RA7PPS | _             | _     | _       |               | RA7PPS<4:0>      |             |       |       |                       | uu uuuu                    |

| 1F18h     | RB0PPS | _             | _     | _       |               | RB0PPS<4:0>      |             |       |       |                       | uu uuuu                    |

| 1F19h     | RB1PPS | _             | _     | _       |               | RB1PPS<4:0>      |             |       |       |                       | uu uuuu                    |

| 1F1Ah     | RB2PPS | _             | _     | _       |               |                  | RB2PPS<4:0  | >     |       | 00 0000               | uu uuuu                    |

| 1F1Bh     | RB3PPS | _             | _     | _       |               |                  | RB3PPS<4:0  | >     |       | 00 0000               | uu uuuu                    |

| 1F1Ch     | RB4PPS | _             | _     | _       |               |                  | RB4PPS<4:0  | >     |       | 00 0000               | uu uuuu                    |

| 1F1Dh     | RB5PPS | _             | _     | _       |               |                  | RB5PPS<4:0  | >     |       | 00 0000               | uu uuuu                    |

| 1F1Eh     | RB6PPS | _             | _     | _       |               |                  | RB6PPS<4:0  | >     |       | 00 0000               | uu uuuu                    |

| 1F1Fh     | RB7PPS | _             | _     | _       |               |                  | RB7PPS<4:0  | >     |       | 00 0000               | uu uuuu                    |

| 1F20h     | RC0PPS | _             | _     | _       |               |                  | RC0PPS<4:0  | >     |       | 00 0000               | uu uuuu                    |

| 1F21h     | RC1PPS | _             | _     | _       |               |                  | RC1PPS<4:0  | >     |       | 00 0000               | uu uuuu                    |

| 1F22h     | RC2PPS | —             | _     | —       |               |                  | RC2PPS<4:0  | >     |       | 00 0000               | uu uuuu                    |

| 1F23h     | RC3PPS | —             | _     | —       |               |                  | RC3PPS<4:0  | >     |       | 00 0000               | uu uuuu                    |

| 1F24h     | RC4PPS | —             | _     | —       |               |                  | RC4PPS<4:0  | >     |       | 00 0000               | uu uuuu                    |

| 1F25h     | RC5PPS | —             | _     | —       |               |                  | RC5PPS<4:0  | >     |       | 00 0000               | uu uuuu                    |

| 1F26h     | RC6PPS | —             | _     | —       |               |                  | RC6PPS<4:0  | >     |       | 00 0000               | uu uuuu                    |

| 1F27h     | RC7PPS | —             | _     | —       |               |                  | RC7PPS<4:0  | >     |       | 00 0000               | uu uuuu                    |

| 1F28h<br> | _      | Unimplemented |       |         |               |                  |             |       | -     | _                     |                            |

#### TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

# PIC16(L)F15354/55

#### 6.1 Microchip Unique identifier (MUI)

The PIC16(L)F15354/55 devices are individually encoded during final manufacturing with a Microchip Unique Identifier, or MUI. The MUI cannot be erased by a Bulk Erase command or any other user-accessible means. This feature allows for manufacturing traceability of Microchip Technology devices in applications where this is a required. It may also be used by the application manufacturer for a number of functions that require unverified unique identification, such as:

- Tracking the device

- Unique serial number

The MUI consists of nine program words. When taken together, these fields form a unique identifier. The MUI is stored in nine read-only locations, located between 8100h to 8109h in the DIA space. Table 6-1 lists the addresses of the identifier words.

| Note: | For applications that require verified unique |

|-------|-----------------------------------------------|

|       | identification, contact your Microchip Tech-  |

|       | nology sales office to create a Serialized    |

|       | Quick Turn Programming option.                |

#### 6.2 External Unique Identifier (EUI)

The EUI data is stored at locations 810Ah to 8111h in the program memory region. This region is an optional space for placing application specific information. The data is coded per customer requirements during manufacturing. The EUI cannot be erased by a Bulk erase command.

Note: Data is stored in this address range on receiving a request from the customer. The customer may contact the local sales representative, or Field Applications Engineer, and provide them the unique identifier information that is required to be stored in this region.

#### 6.3 Analog-to-Digital Conversion Data of the Temperature Sensor

The purpose of the temperature sensor module is to provide a temperature-dependent voltage that can be measured by an analog module. **Section 19.0 "Temperature Indicator Module**" explains the operation of the Temperature Indicator module and defines terms such as the low range and high range settings of the sensor.

The DIA table contains the internal ADC measurement values of the temperature sensor for low and high range at fixed points of reference. The values are measured during test and are unique to each device. The right-justified ADC readings are stored in the DIA memory region. The calibration data can be used to plot the approximate sensor output voltage, VTSENSE vs. Temperature curve without having to make calibration measurements in the application.

- **TSLR<3:1>**: Address 8112h to 8114h store the measurements for the low range setting of the temperature sensor at VDD = 3V.

- TSHR<3:1>: Address 8115h to 8117h store the measurements for the high range setting of the temperature sensor at VDD = 3V.

The stored measurements are made by the device ADC using the internal VREF = 2.048V.

#### 6.4 Fixed Voltage Reference Data

The Fixed Voltage Reference, or FVR, is a stable voltage reference, independent of VDD, with 1.024V, 2.048V or 4.096V selectable output levels. The output of the FVR can be configured to supply a reference voltage to the following:

- · ADC input channel

- ADC positive reference

- Comparator positive input

- Digital-to-Analog Converter

For more information on the FVR, refer to **Section 18.0 "Fixed Voltage Reference (FVR)"**.

The DIA stores measured FVR voltages for this device in mV for the different buffer settings of 1x, 2x or 4x at program memory locations 8118h to 811Dh.

- FVRA1X stores the value of ADC FVR1 Output voltage for 1x setting (in mV)

- FVRA2X stores the value of ADC FVR1 Output Voltage for 2x setting (in mV)

- FVRA4X stores the value of ADC FVR1 Output Voltage for 4x setting (in mV)

- FVRC1X stores the value of Comparator FVR2 output voltage for 2x setting (in mV)

- FVRC2X stores the value of Comparator FVR2 output voltage for 2x setting (in mV)

- FVRC4X stores the value of Comparator FVR2 output voltage for 4x setting (in mV)

| U-0            | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W/HS-0/0                               | R-0           | U-0                | U-0                | U-0              | R/W/HS-0/0          |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|---------------|--------------------|--------------------|------------------|---------------------|--|

| _              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | TMR0IF                                   | IOCIF         | _                  | _                  | _                | INTF <sup>(1)</sup> |  |

| bit 7          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          |               |                    |                    |                  | bit 0               |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          |               |                    |                    |                  |                     |  |

| Legend:        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          |               |                    |                    |                  |                     |  |

| R = Reada      | ble bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | W = Writable b                           | bit           | U = Unimpler       | nented bit, read   | as '0'           |                     |  |

| u = Bit is u   | nchanged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | x = Bit is unkn                          | own           | -n/n = Value a     | at POR and BO      | R/Value at all c | other Resets        |  |

| '1' = Bit is s | set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | '0' = Bit is clea                        | red           | HS= Hardwa         | re Set             |                  |                     |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          |               |                    |                    |                  |                     |  |

| bit 7-6        | Unimpleme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | nted: Read as '0                         | ,             |                    |                    |                  |                     |  |

| bit 5          | 5 TMR0IF: Timer0 Overflow Interrupt Flag bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                          |               |                    |                    |                  |                     |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | register has over<br>register did not    |               | st be cleared in   | software)          |                  |                     |  |

| bit 4          | IOCIF: Interr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | rupt-on-Change I                         | nterrupt Flag | g bit (read-only)  | (2)                |                  |                     |  |

|                | 1 = One or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | more of the IOC                          | AF-IOCEF re   | egister bits are o | currently set, ind | icating an enal  | bled edge was       |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ed by the IOC mo                         |               |                    |                    |                  |                     |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | of the IOCAF-IOC                         | -             | bits are current   | ly set             |                  |                     |  |

| bit 3-1        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | nted: Read as '0                         |               |                    |                    |                  |                     |  |

| bit 0          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | xternal Interrupt                        | -             |                    |                    |                  |                     |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | T external interru<br>T external interru |               |                    | ed in software)    |                  |                     |  |

| N              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          |               |                    |                    |                  |                     |  |

|                | The External Inter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | • •                                      |               |                    | ,                  |                  | 9                   |  |

|                | The IOCIF bit is the application firmware application for the second sec |                                          |               |                    |                    |                  | nag,                |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          |               |                    |                    |                  |                     |  |