Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| 2000                       |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 224 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15355-e-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F15354/55

### TABLE 2: PACKAGES

| Device         | (S)PDIP | SOIC | SSOP | UQFN (4x4) | UQFN (6x6) |

|----------------|---------|------|------|------------|------------|

| PIC16(L)F15354 | •       | •    | •    | •          | •          |

| PIC16(L)F15355 | •       | •    | •    | •          | •          |

| Name                                                    | Function              | Input<br>Type | Output Type | Description                                       |

|---------------------------------------------------------|-----------------------|---------------|-------------|---------------------------------------------------|

| RA0/ANA0/C1IN0-/C2IN0-/CLCIN0 <sup>(1)</sup> /          | RA0                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

| IOCA0                                                   | ANA0                  | AN            | _           | ADC Channel A0 input.                             |

|                                                         | C1IN0-                | AN            | _           | Comparator 1 negative input.                      |

|                                                         | C2IN0-                | AN            | _           | Comparator 2 negative input.                      |

|                                                         | CLCIN0 <sup>(1)</sup> | TTL/ST        | -           | Configurable Logic Cell source input.             |

|                                                         | IOCA0                 | TTL/ST        | _           | Interrupt-on-change input.                        |

| RA1/ANA1/C1IN1-/C2IN1-/CLCIN1 <sup>(1)</sup> /<br>IOCA1 | RA1                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

| IUCAT                                                   | ANA1                  | AN            | _           | ADC Channel A1 input.                             |

|                                                         | C1IN1-                | AN            | _           | Comparator 1 negative input.                      |

|                                                         | C2IN1-                | AN            | -           | Comparator 2 negative input.                      |

|                                                         | CLCIN1 <sup>(1)</sup> | TTL/ST        | -           | Configurable Logic Cell source input.             |

|                                                         | IOCA1                 | TTL/ST        | _           | Interrupt-on-change input.                        |

| RA2/ANA2/C1IN0+/C2IN0+/VREF-/<br>DAC1OUT1/IOCA2         | RA2                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

| DACTOUTINOCAZ                                           | ANA2                  | AN            | -           | ADC Channel A2 input.                             |

|                                                         | C1IN0+                | AN            | I           | Comparator 2 positive input.                      |

|                                                         | C2IN0+                | AN            | -           | Comparator 2 positive input.                      |

|                                                         | DAC1OUT1              | —             | AN          | Digital-to-Analog Converter output.               |

|                                                         | IOCA2                 | TTL/ST        | -           | Interrupt-on-change input.                        |

| RA3/ANA3/C1IN1+/VREF+/IOCA3/<br>DAC1REF+                | RA3                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

| DAGIREFT                                                | ANA3                  | AN            | -           | ADC Channel A3 input.                             |

|                                                         | C1IN1+                | AN            | I           | Comparator 1 positive input.                      |

|                                                         | VREF+                 | AN            | I           | External ADC and/or DAC positive reference input. |

|                                                         | IOCA3                 | TTL/ST        | -           | Interrupt-on-change input.                        |

|                                                         | DAC1REF+              | TTL/ST        | AN          | DAC positive reference.                           |

| RA4/ANA4/T0CKI <sup>(1)</sup> /IOCA4                    | RA4                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

|                                                         | ANA4                  | AN            | _           | ADC Channel A4 input.                             |

|                                                         | тоскі <sup>(1)</sup>  | TTL/ST        | _           | Timer0 clock input.                               |

|                                                         | IOCA4                 | TTL/ST        | _           | Interrupt-on-change input.                        |

| RA5/ANA5/SS1 <sup>(1)</sup> /IOCA5                      | RA5                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

|                                                         | ANA5                  | AN            | _           | ADC Channel A5 input.                             |

|                                                         | SS1 <sup>(1)</sup>    | TTL/ST        | _           | MSSP1 SPI slave select input.                     |

|                                                         | IOCA5                 | TTL/ST        | —           | Interrupt-on-change input.                        |

TABLE 1-2: PIC16(L)F15354/55 PINOUT DESCRIPTION

Legend:AN= Analog input or output<br/>TTLCMOS= CMOS compatible input or output<br/>STOD= Open-Drain<br/>I^2CHV= High VoltageXTAL= Crystal levelsI2C= Schmitt Trigger input with I2C

Note 1

This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 15-2 for details on which PORT pins may be used for this signal.

All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin

All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTX pin options as described in Table 15-3.

The several PORTX pin the several port of the several port

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

| Address   | Name   | Bit 7 | Bit 6           | Bit 5   | Bit 4         | Bit 3            | Bit 2       | Bit 1   | Bit 0   | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|-----------|--------|-------|-----------------|---------|---------------|------------------|-------------|---------|---------|-----------------------|----------------------------|

| Bank 62   |        |       |                 |         |               |                  |             |         |         |                       |                            |

|           |        |       |                 | CPU COF | RE REGISTERS; | see Table 4-3 fo | r specifics |         |         |                       |                            |

| 1F0Ch     | _      |       |                 |         | Unimple       | mented           |             |         |         |                       |                            |

| 1F0Dh     | _      |       |                 |         | Unimple       | mented           |             |         |         |                       |                            |

| 1F0Eh     | _      |       |                 |         | Unimple       | mented           |             |         |         |                       |                            |

| 1F0Fh     | _      |       |                 |         | Unimple       | mented           |             |         |         |                       |                            |

| 1F10h     | RA0PPS | —     | —               | —       |               |                  | RA0PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F11h     | RA1PPS | —     | —               | —       |               |                  | RA1PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F12h     | RA2PPS | —     | _               | —       |               |                  | RA2PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F13h     | RA3PPS | —     | _               | —       |               |                  | RA3PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F14h     | RA4PPS | -     | -               | —       |               |                  | RA4PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F15h     | RA5PPS | —     | _               | _       |               |                  | RA5PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F16h     | RA6PPS | —     | _               | _       |               |                  | RA6PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F17h     | RA7PPS | _     | _               | _       |               |                  | RA7PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F18h     | RB0PPS | _     | _               | _       |               |                  | RB0PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F19h     | RB1PPS | _     | _               | _       |               |                  | RB1PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F1Ah     | RB2PPS | _     | _               | _       |               |                  | RB2PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F1Bh     | RB3PPS | _     | _               | _       |               |                  | RB3PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F1Ch     | RB4PPS | _     | _               | _       |               |                  | RB4PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F1Dh     | RB5PPS | _     | _               | _       |               |                  | RB5PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F1Eh     | RB6PPS | _     | _               | _       |               |                  | RB6PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F1Fh     | RB7PPS | _     | _               | _       |               |                  | RB7PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F20h     | RC0PPS | _     | _               | _       |               |                  | RC0PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F21h     | RC1PPS | _     | _               | _       |               |                  | RC1PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F22h     | RC2PPS | —     | _               | —       |               |                  | RC2PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F23h     | RC3PPS | —     | _               | —       |               |                  | RC3PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F24h     | RC4PPS | —     | _               | —       | RC4PPS<4:0>   |                  |             | 00 0000 | uu uuuu |                       |                            |

| 1F25h     | RC5PPS | —     | _               | —       | RC5PPS<4:0>   |                  |             | 00 0000 | uu uuuu |                       |                            |

| 1F26h     | RC6PPS | —     | _               | —       | RC6PPS<4:0> - |                  |             |         | 00 0000 | uu uuuu               |                            |

| 1F27h     | RC7PPS | —     | _               | —       |               |                  | RC7PPS<4:0  | >       |         | 00 0000               | uu uuuu                    |

| 1F28h<br> | _      |       | Unimplemented — |         |               |                  |             |         | _       |                       |                            |

### TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

# PIC16(L)F15354/55

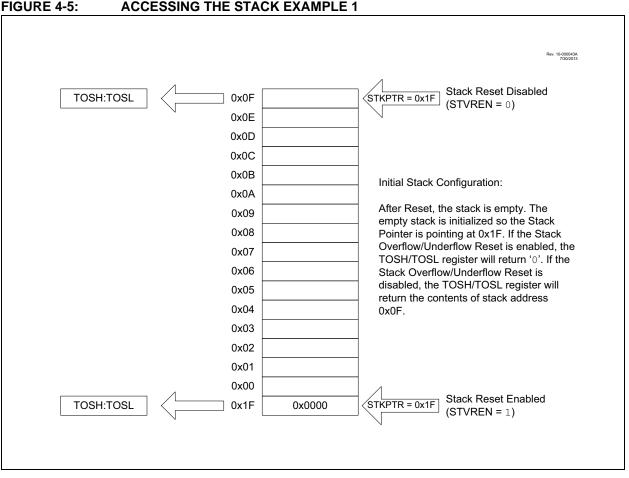

### 4.5 Stack

All devices have a 16-level x 15-bit wide hardware stack (refer to Figure 4-5 through Figure 4-8). The stack space is not part of either program or data space. The PC is PUSHed onto the stack when CALL or CALLW instructions are executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer if the STVREN bit is programmed to '0' (Configuration Words). This means that after the stack has been PUSHed sixteen times, the seventeenth PUSH overwrites the value that was stored from the first PUSH. The eighteenth PUSH overwrites the second PUSH (and so on). The STKOVF and STKUNF flag bits will be set on an Overflow/Underflow, regardless of whether the Reset is enabled.

Note 1: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, CALLW, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

### 4.5.1 ACCESSING THE STACK

The stack is accessible through the TOSH, TOSL and STKPTR registers. STKPTR is the current value of the Stack Pointer. TOSH:TOSL register pair points to the TOP of the stack. Both registers are read/writable. TOS is split into TOSH and TOSL due to the 15-bit size of the PC. To access the stack, adjust the value of STKPTR, which will position TOSH:TOSL, then read/write to TOSH:TOSL. STKPTR is five bits to allow detection of overflow and underflow.

| Note: | Care should be taken when modifying the |

|-------|-----------------------------------------|

|       | STKPTR while interrupts are enabled.    |

During normal program operation, CALL, CALLW and interrupts will increment STKPTR while RETLW, RETURN, and RETFIE will decrement STKPTR. STKPTR can be monitored to obtain to value of stack memory left at any given time. The STKPTR always points at the currently used place on the stack. Therefore, a CALL or CALLW will increment the STKPTR and then write the PC, and a return will unload the PC value from the stack and then decrement the STKPTR.

Reference Figure 4-5 through Figure 4-8 for examples of accessing the stack.

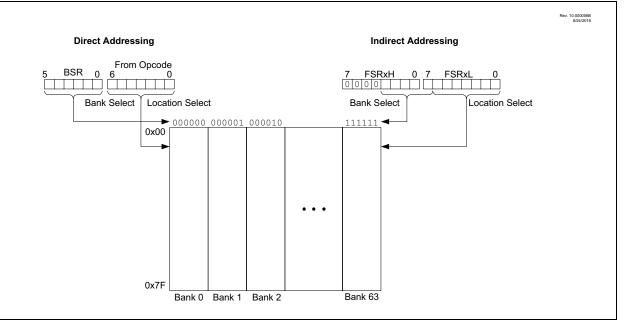

### 4.6.1 TRADITIONAL/BANKED DATA MEMORY

The traditional or banked data memory is a region from FSR address 0x000 to FSR address 0xFFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

### FIGURE 4-11: TRADITIONAL/BANKED DATA MEMORY MAP

| REGIST  | ER 5-7:      | REVIS       | REVISIONID: REVISION ID REGISTER |   |   |           |        |             |         |          |     |   |       |

|---------|--------------|-------------|----------------------------------|---|---|-----------|--------|-------------|---------|----------|-----|---|-------|

| R       | R            | R           | R                                | R | R | R         | R      | R           | R       | R        | R   | R | R     |

| 1       | 0            | MJRREV<5:0> |                                  |   |   |           |        | MNRREV<5:0> |         |          |     |   |       |

| bit 13  |              |             |                                  |   |   |           |        |             |         |          |     |   | bit 0 |

|         |              |             |                                  |   |   |           |        |             |         |          |     |   |       |

| Legend: |              |             |                                  |   |   |           |        |             |         |          |     |   |       |

|         | R = Read     | able bit    |                                  |   |   |           |        |             |         |          |     |   |       |

|         | '0' = Bit is | cleared     |                                  |   |   | '1' = Bit | is set |             | x = Bit | is unkno | own |   |       |

bit 13-12 **Fixed Value**: Read-only bits These bits are fixed with value '10' for all devices included in this data sheet.

bit 11-6MJRREV<5:0>: Major Revision ID bits<br/>These bits are used to identify a major revision.bit 5-0MNRREV<5:0>: Minor Revision ID bits<br/>These bits are used to identify a minor revision.

© 2016 Microchip Technology Inc.

# 8.15 Register Definitions: Power Control

### REGISTER 8-2: PCON0: POWER CONTROL REGISTER 0

| R/W/HS-0/q | R/W/HS-0/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|------------|------------|------------|------------|------------|------------|------------|------------|

| STKOVF     | STKUNF     | WDTWV      | RWDT       | RMCLR      | RI         | POR        | BOR        |

| bit 7      | •          |            |            |            |            |            | bit 0      |

|            |            |            |            |            |            |            |            |

| Legend:                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                        |                                                                            |                                                                         |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|

| HC = Bit is cle                                                                                                                                                                                                                                                                                                           | ared by hardw                                                                                                                                                          | are                                                                        | HS = Bit is set by hardware                                             |  |  |

| R = Readable                                                                                                                                                                                                                                                                                                              | bit                                                                                                                                                                    | W = Writable bit                                                           | U = Unimplemented bit, read as '0'                                      |  |  |

| u = Bit is unch                                                                                                                                                                                                                                                                                                           | anged                                                                                                                                                                  | x = Bit is unknown                                                         | -m/n = Value at POR/Value at all other Resets                           |  |  |

| '1' = Bit is set                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                        | '0' = Bit is cleared                                                       | q = Value depends on condition                                          |  |  |

| bit 7                                                                                                                                                                                                                                                                                                                     | 1 = A Stack                                                                                                                                                            | ack Overflow Flag bit<br>Overflow occurred<br>Overflow has not occurre     | ed or cleared by firmware                                               |  |  |

| bit 6                                                                                                                                                                                                                                                                                                                     | STKUNF: Stack                                                                                                                                                          | ack Underflow Flag bit<br>Underflow occurred                               | red or cleared by firmware                                              |  |  |

| <ul> <li>bit 5</li> <li>WDTWV: WDT Window Violation Flag bit</li> <li>1 = A WDT Window Violation Reset has not occurred or set to '1' by firmware</li> <li>0 = A WDT Window Violation Reset has occurred (a CLRWDT instruction was executed eith arming the window or outside the window (cleared by hardware)</li> </ul> |                                                                                                                                                                        |                                                                            |                                                                         |  |  |

| bit 4                                                                                                                                                                                                                                                                                                                     | 1 = A Watch                                                                                                                                                            |                                                                            | it<br>occurred or set to '1' by firmware<br>urred (cleared by hardware) |  |  |

| bit 3                                                                                                                                                                                                                                                                                                                     | 1 = A MCLR                                                                                                                                                             | CLR Reset Flag bit<br>Reset has not occurred o<br>Reset has occurred (clea |                                                                         |  |  |

| bit 2                                                                                                                                                                                                                                                                                                                     | 1 <b>= A</b> reset                                                                                                                                                     |                                                                            | executed or set to '1' by firmware<br>ecuted (cleared by hardware)      |  |  |

| bit 1                                                                                                                                                                                                                                                                                                                     | bit 1 <b>POR:</b> Power-on Reset Status bit<br>1 = No Power-on Reset occurred<br>0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs) |                                                                            |                                                                         |  |  |

| bit 0 BOR: Brown-out Reset Status bit 1 = No Brown-out Reset occurred 0 = A Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out R occurs)                                                                                                                                               |                                                                                                                                                                        |                                                                            |                                                                         |  |  |

# PIC16(L)F15354/55

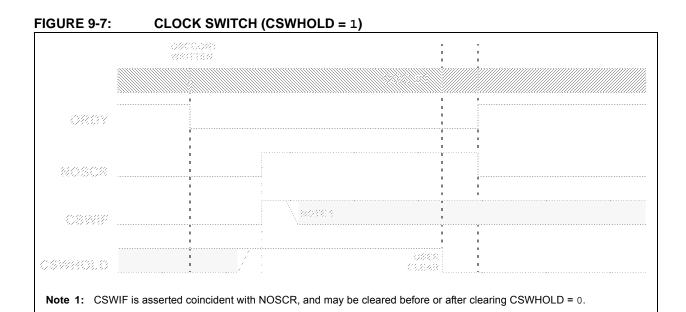

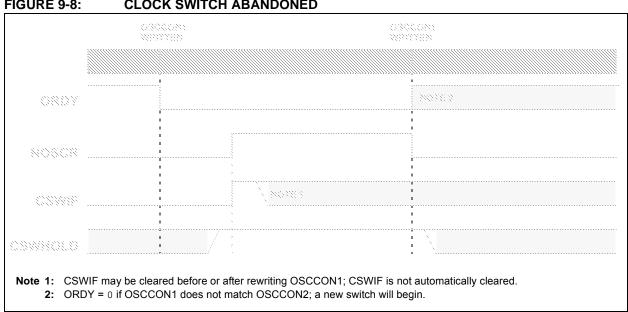

### **FIGURE 9-8: CLOCK SWITCH ABANDONED**

### 9.5 Register Definitions: Oscillator Control

### REGISTER 9-1: OSCCON1: OSCILLATOR CONTROL REGISTER1

| U-0   | R/W-f/f <sup>(1)</sup> | R/W-f/f <sup>(1)</sup>    | R/W-f/f <sup>(1)</sup> | R/W-q/q | R/W-q/q | R/W-q/q            | R/W-q/q |

|-------|------------------------|---------------------------|------------------------|---------|---------|--------------------|---------|

| —     | 1                      | NOSC<2:0> <sup>(2,3</sup> | 3)                     |         | NDIV<3  | :0> <b>(2,3,4)</b> |         |

| bit 7 |                        |                           |                        |         |         |                    | bit 0   |

|       |                        |                           |                        |         |         |                    |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | f = determined by fuse setting                        |

bit 7 Unimplemented: Read as '0'

bit 6-4

NOSC<2:0>: New Oscillator Source Request bits

The setting requests a source oscillator and PLL combination per Table 9-1.

POR value = RSTOSC (Register 5-1).

bit 3-0

NDIV<3:0>: New Divider Selection Request bits

The setting determines the new postscaler division ratio per Table 9-1.

Note 1: The default value (f/f) is set equal to the RSTOSC Configuration bits.

- 2: If NOSC is written with a reserved value (Table 9-1), the operation is ignored and neither NOSC nor NDIV is written.

- 3: When CSWEN = 0, this register is read-only and cannot be changed from the POR value.

- 4: When NOSC = 110 (HFINTOSC 4 MHz), the NDIV bits will default to '0010' upon Reset; for all other NOSC settings the NDIV bits will default to '0000' upon Reset.

### REGISTER 9-2: OSCCON2: OSCILLATOR CONTROL REGISTER 2

| U-0   | R-n/n <sup>(2)</sup> |

|-------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| —     |                      | COSC<2:0>            |                      |                      | CDIV                 | <3:0>                |                      |

| bit 7 |                      |                      |                      |                      |                      |                      | bit 0                |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 Unimplemented: Read as '0'

bit 6-4 COSC<2:0>: Current Oscillator Source Select bits (read-only)

Indicates the current source oscillator and PLL combination per Table 9-1.

bit 3-0 **CDIV<3:0>:** Current Divider Select bits (read-only) Indicates the current postscaler division ratio per Table 9-1.

**Note 1:** The POR value is the value present when user code execution begins.

**2:** The Reset value (n/n) is the same as the NOSC/NDIV bits.

# 14.0 I/O PORTS

### TABLE 14-1: PORT AVAILABILITY PER DEVICE

| Device            | PORTA | PORTB | PORTC | PORTE |

|-------------------|-------|-------|-------|-------|

| PIC16(L)F15354/55 | ٠     | ٠     | ٠     | ٠     |

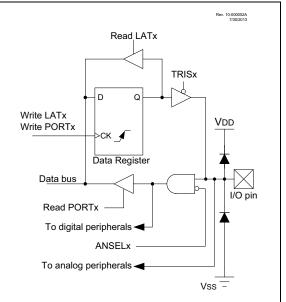

Each port has ten standard registers for its operation. These registers are:

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

- TRISx registers (data direction)

- ANSELx registers (analog select)

- WPUx registers (weak pull-up)

- INLVLx (input level control)

- SLRCONx registers (slew rate)

- ODCONx registers (open-drain)

Most port pins share functions with device peripherals, both analog and digital. In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output; however, the pin can still be read.

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports that support analog inputs have an associated ANSELx register. When an ANSEL bit is set, the digital input buffer associated with that bit is disabled.

Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 14-1.

### FIGURE 14-1: GENERIC I/O PORT OPERATION

## 14.1 I/O Priorities

Each pin defaults to the PORT data latch after Reset. Other functions are selected with the peripheral pin select logic. See **Section 15.0** "**Peripheral Pin Select** (**PPS**) **Module**" for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx register. Digital output functions may continue to control the pin when it is in Analog mode.

Analog outputs, when enabled, take priority over the digital outputs and force the digital output driver to the high-impedance state.

| Name       | Bit 7 | Bit 6 | Bit 5 | Bit 4         | Bit 3 | Bit 2      | Bit 1 | Bit 0     | Register<br>on page |  |

|------------|-------|-------|-------|---------------|-------|------------|-------|-----------|---------------------|--|

| PPSLOCK    | _     | —     | —     | _             | —     | _          | —     | PPSLOCKED | 197                 |  |

| INTPPS     | _     | _     |       |               | INT   | PPS<5:0>   |       |           | 196                 |  |

| TOCKIPPS   | _     | _     |       |               | TOCK  | (IPPS<5:0> |       |           | 196                 |  |

| T1CKIPPS   | —     | _     |       |               | T1CK  | (IPPS<5:0> |       |           | 196                 |  |

| T1GPPS     | _     | _     |       |               | T1G   | PPS<5:0>   |       |           | 196                 |  |

| T2AINPPS   |       |       |       |               | T2AII | NPPS<5:0>  |       |           | 196                 |  |

| CCP1PPS    | —     | _     |       |               | CCP   | 1PPS<5:0>  |       |           | 196                 |  |

| CCP2PPS    | _     | _     |       |               | CCP   | 2PPS<5:0>  |       |           | 196                 |  |

| CWG1PPS    | _     | _     |       |               | CWG   | 1PPS<5:0>  |       |           | 196                 |  |

| SSP1CLKPPS | —     | _     |       |               | SSP1C | LKPPS<5:0  | >     |           | 196                 |  |

| SSP1DATPPS | —     | _     |       |               | SSP1D | ATPPS<5:0  | >     |           | 196                 |  |

| SSP1SSPPS  | —     | _     |       |               | SSP18 | SSPPS<5:0> | •     |           | 196                 |  |

| SSP2CLKPPS | _     | _     |       |               | SSP2C | LKPPS<5:0  | >     |           | 196                 |  |

| SSP2DATPPS | _     | _     |       |               | SSP2D | ATPPS<5:0  | >     |           | 196                 |  |

| SSP2SSPPS  | _     | _     |       |               | SSP28 | SSPPS<5:0> | •     |           | 196                 |  |

| RX1PPS     | _     | _     |       |               | RXI   | PPS<5:0>   |       |           | 197                 |  |

| TX1PPS     | _     | _     |       |               | TXF   | PPS<5:0>   |       |           | 196                 |  |

| CLCIN0PPS  | _     | _     |       |               | CLCIN | 10PPS<5:0> |       |           | 196                 |  |

| CLCIN1PPS  | _     | _     |       |               | CLCIN | 1PPS<5:0>  |       |           | 196                 |  |

| CLCIN2PPS  | _     | _     |       |               | CLCIN | 12PPS<5:0> |       |           | 196                 |  |

| CLCIN3PPS  | _     | _     |       |               | CLCIN | 13PPS<5:0> |       |           | 196                 |  |

| RX2PPS     | _     | _     |       |               | RX2   | PPS<5:0>   |       |           | 196                 |  |

| TX2PPS     | _     | _     |       |               | TX2   | PPS<5:0>   |       |           | 196                 |  |

| ADACTPPS   | _     | _     |       |               | ADAC  | TPPS<5:0>  |       |           | 196                 |  |

| RA0PPS     |       |       |       |               |       | RA0PPS<    | 4:0>  |           | 197                 |  |

| RA1PPS     | _     | _     |       |               |       | RA1PPS<    | 4:0>  |           | 197                 |  |

| RA2PPS     | _     | _     | _     |               |       | RA2PPS<    | 4:0>  |           | 197                 |  |

| RA3PPS     | _     | _     | _     |               |       | RA3PPS<    | 4:0>  |           | 197                 |  |

| RA4PPS     | _     | _     |       |               |       | RA4PPS<    | 4:0>  |           | 197                 |  |

| RA5PPS     | _     | _     |       |               |       | RA5PPS<    | 4:0>  |           | 197                 |  |

| RA6PPS     |       |       |       |               |       | RA6PPS<    |       |           | 197                 |  |

| RA7PPS     | _     | _     | —     |               |       | RA7PPS<    | 4:0>  |           | 197                 |  |

| RB0PPS     | _     | _     | —     |               |       | RB0PPS<    | 4:0>  |           | 197                 |  |

| RB1PPS     | —     | _     | —     |               |       | RB1PPS<    | 4:0>  |           | 197                 |  |

| RB2PPS     | _     | _     | _     |               |       | RB2PPS<    | 4:0>  |           | 197                 |  |

| RB3PPS     | _     | _     | _     |               |       | RB3PPS<    | 4:0>  |           | 197                 |  |

| RB4PPS     | _     | _     | _     | — RB4PPS<4:0> |       |            |       |           |                     |  |

| RB5PPS     | _     | _     | _     |               |       | RB5PPS<    |       |           | 197<br>197          |  |

| RB6PPS     | _     | _     | _     | — RB6PPS<4:0> |       |            |       |           |                     |  |

| RB7PPS     | _     | _     | _     |               |       | RB7PPS<    |       |           | 197<br>197          |  |

| RC0PPS     |       |       |       |               |       | RC0PPS<    |       |           | 197                 |  |

### TABLE 15-4: SUMMARY OF REGISTERS ASSOCIATED WITH THE PPS MODULE

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the PPS module.

# PIC16(L)F15354/55

### REGISTER 23-3: CMxNSEL: COMPARATOR Cx NEGATIVE INPUT SELECT REGISTER

| U-0      | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|----------|-----|-----|-----|-----|---------|----------|---------|

| —        | —   | —   | —   | —   |         | NCH<2:0> |         |

| bit 7    |     |     |     |     |         |          | bit 0   |

|          |     |     |     |     |         |          |         |

| l egend: |     |     |     |     |         |          |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-2 | Unimplemented: Read as '0'                              |

|---------|---------------------------------------------------------|

| bit 2-0 | NCH<2:0>: Comparator Negative Input Channel Select bits |

|         | 111 = CxVN connects to AVss                             |

|         | 110 = CxVN connects to FVR Buffer 2                     |

|         | 101 = CxVN unconnected                                  |

|         | 100 = CxVN unconnected                                  |

|         | 011 = CxVN connects to CxIN3- pin                       |

|         | 010 = CxVN connects to CxIN2- pin                       |

|         | 001 = CxVN connects to CxIN1- pin                       |

|         | 000 = CxVN connects to CxIN0- pin                       |

### REGISTER 23-4: CMxPSEL: COMPARATOR Cx POSITIVE INPUT SELECT REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|----------|---------|

| _     | —   | _   | _   | _   |         | PCH<2:0> |         |

| bit 7 | •   |     |     |     |         |          | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-2 Unimplemented: Read as '0'

bit 5-3 PCH<2:0>: Comparator Positive Input Channel Select bits

- 111 = CxVP connects to AVss

- 110 = CxVP connects to FVR Buffer 2

- 101 = CxVP connects to DAC output

- 100 = CxVP unconnected

- 011 = CxVP unconnected

- 010 = CxVP unconnected

- 001 = CxVP connects to CxIN1+ pin

- 000 = CxVP connects to CxIN0+ pin

| Marila            | MODE   | <4:0>        | Output                            | Onenetien                                                 | Timer Control              |                       |                                 |  |

|-------------------|--------|--------------|-----------------------------------|-----------------------------------------------------------|----------------------------|-----------------------|---------------------------------|--|

| Mode              | <4:3>  | <2:0>        | Operation                         | Operation                                                 | Start                      | Reset                 | Stop                            |  |

|                   |        | 000          |                                   | Software gate (Figure 27-4) ON = 1                        |                            | _                     | ON = 0                          |  |

|                   |        | 001          | Period<br>Pulse                   | Hardware gate, active-high<br>(Figure 27-5)               | ON = 1 and<br>TMRx_ers = 1 | _                     | ON = 0 or<br>TMRx_ers = 0       |  |

|                   |        | 010          | Fuise                             | Hardware gate, active-low                                 | ON = 1 and<br>TMRx_ers = 0 | _                     | ON = 0 or<br>TMRx_ers = 1       |  |

| Free              | 0.0    | 011          |                                   | Rising or falling edge Reset                              |                            | TMRx_ers              |                                 |  |

| Running<br>Period | 00     | 100          | Period                            | Rising edge Reset (Figure 27-6)                           |                            | TMRx_ers ↑            | <b>ON =</b> 0                   |  |

|                   |        | 101          | Pulse                             | Falling edge Reset                                        |                            | TMRx_ers ↓            |                                 |  |

|                   |        | 110          | with<br>Hardware                  | Low level Reset                                           | ON = 1                     | TMRx_ers = 0          | ON = 0 or<br>TMRx_ers = 0       |  |

|                   |        | 111          | Reset                             | High level Reset (Figure 27-7)                            |                            | TMRx_ers = 1          | ON = 0 or<br>TMRx_ers = 1       |  |

|                   |        | 000          | One-shot                          | Software start (Figure 27-8)                              | ON = 1                     | _                     |                                 |  |

|                   |        | 001          | Edge                              | Rising edge start (Figure 27-9)                           | ON = 1 and<br>TMRx_ers ↑   | _                     |                                 |  |

|                   |        | 010          | triggered<br>start                | Falling edge start                                        | ON = 1 and<br>TMRx_ers ↓   | _                     |                                 |  |

|                   |        | 011          | (Note 1)                          | Any edge start                                            | ON = 1 and<br>TMRx_ers     | _                     | ON = 0<br>or<br>Next clock      |  |

| One-shot          | 01 100 | 100          | Edge                              | Rising edge start and<br>Rising edge Reset (Figure 27-10) | ON = 1 and<br>TMRx_ers ↑   | TMRx_ers ↑            | after<br>TMRx = PRx             |  |

|                   |        | 101          | triggered<br>start<br>and         | Falling edge start and<br>Falling edge Reset              | ON = 1 and<br>TMRx_ers ↓   | TMRx_ers $\downarrow$ | (Note 2)                        |  |

|                   |        | 110          | hardware<br>Reset                 | Rising edge start and<br>Low level Reset (Figure 27-11)   | ON = 1 and<br>TMRx_ers ↑   | TMRx_ers = 0          |                                 |  |

|                   |        | 111          | (Note 1)                          | Falling edge start and<br>High level Reset                | ON = 1 and<br>TMRx_ers ↓   | TMRx_ers = 1          |                                 |  |

|                   |        | 000          |                                   | Rese                                                      | rved                       |                       |                                 |  |

|                   |        | 001          | Edge                              | Rising edge start<br>(Figure 27-12)                       | ON = 1 and<br>TMRx_ers ↑   | _                     | ON = 0<br>or                    |  |

| Mono-stable       |        | 010          | triggered<br>start                | Falling edge start                                        | ON = 1 and<br>TMRx_ers ↓   | _                     | Next clock<br>after             |  |

|                   |        | 011          | (Note 1)                          | Any edge start                                            | ON = 1 and<br>TMRx_ers     | _                     | TMRx = PRx<br>( <b>Note 3</b> ) |  |

| Reserved          | 10     | 100          |                                   | Rese                                                      | rved                       |                       |                                 |  |

| Reserved          |        | 101          |                                   | Rese                                                      | rved                       |                       |                                 |  |

|                   |        | 110          | Level<br>triggered                | High level start and<br>Low level Reset (Figure 27-13)    | ON = 1 and<br>TMRx_ers = 1 | TMRx_ers = 0          | ON = 0 or                       |  |

| One-shot          |        | 111          | start<br>and<br>hardware<br>Reset | Low level start &<br>High level Reset                     | ON = 1 and<br>TMRx_ers = 0 | TMRx_ers = 1          | Held in Reset                   |  |

| Reserved          | 11     | xxx Reserved |                                   |                                                           |                            |                       |                                 |  |

### TABLE 27-1: TIMER2 OPERATING MODES

**Note** 1: If ON = 0 then an edge is required to restart the timer after ON = 1.

2: When TMRx = PRx then the next clock clears ON and stops TMRx at 00h.

3: When TMRx = PRx then the next clock stops TMRx at 00h but does not clear ON.

### 27.5.8 LEVEL RESET, EDGE-TRIGGERED HARDWARE LIMIT ONE-SHOT MODES

In Level -Triggered One-Shot mode the timer count is reset on the external signal level and starts counting on the rising/falling edge of the transition from Reset level to the active level while the ON bit is set. Reset levels are selected as follows:

- Low Reset level (MODE<4:0> = 01110)

- High Reset level (MODE<4:0> = 01111)

When the timer count matches the PRx period count, the timer is reset and the ON bit is cleared. When the ON bit is cleared by either a PRx match or by software control a new external signal edge is required after the ON bit is set to start the counter.

When Level-Triggered Reset One-Shot mode is used in conjunction with the CCP PWM operation the PWM drive goes active with the external signal edge that starts the timer. The PWM drive goes inactive when the timer count equals the CCPRx pulse width count. The PWM drive does not go active when the timer count clears at the PRx period count match.

| Name     | Bit 7       | Bit 6       | Bit 5          | Bit 4 | Bit 3  | Bit 2       | Bit 1    | Bit 0  | Register<br>on Page |

|----------|-------------|-------------|----------------|-------|--------|-------------|----------|--------|---------------------|

| INTCON   | GIE         | PEIE        | _              | —     | —      | _           | —        | INTEDG | 119                 |

| PIR4     | —           | _           | _              | _     | —      | _           | TMR2IF   | TMR1IF | 132                 |

| PIE4     | —           | —           | _              | _     | _      | _           | TMR2IE   | TMR1IE | 124                 |

| CCP1CON  | EN          | —           | OUT            | FMT   |        | MODE        | =<3:0>   |        | 317                 |

| CCP1CAP  | _           |             |                |       |        |             | CTS<2:0> |        | 319                 |

| CCPR1L   | Capture/Con | npare/PWM F | Register 1 (LS | B)    |        |             |          |        | 319                 |

| CCPR1H   | Capture/Con | npare/PWM F | Register 1 (MS | SB)   |        |             |          |        | 320                 |

| CCP2CON  | EN          | —           | OUT            | FMT   |        | MODE        | =<3:0>   |        | 317                 |

| CCP2CAP  | _           | _           | _              | _     | _      |             | CTS<2:0> |        | 319                 |

| CCPR2L   | Capture/Con | npare/PWM F | Register 1 (LS | B)    |        |             |          |        | 319                 |

| CCPR2H   | Capture/Con | npare/PWM F | Register 1 (MS | SB)   |        |             |          |        | 319                 |

| CCPTMRS0 | _           | _           | _              | _     | C2TSE  | L<1:0>      | C1TSE    | L<1:0> | 320                 |

| CCPTMRS1 | _           | _           | _              | _     | P2TSE  | L<1:0>      | C1TSE    | L<1:0> | 321                 |

| CCP1PPS  | _           | _           |                |       | CCP1PI | PS<5:0>     |          |        | 196                 |

| CCP2PPS  | _           | _           |                |       | CCP2PI | PS<5:0>     |          |        | 196                 |

| RxyPPS   | —           | —           | —              |       |        | RxyPPS<4:0> | >        |        | 197                 |

| ADACT    | —           | —           | _              | —     |        | ADAC        | T<3:0>   |        | 231                 |

| CLCxSELy | _           | —           | _              |       |        | LCxDyS<4:0> | >        |        | 363                 |

| CWG1ISM  | —           | —           | _              | —     |        | IS<         | 3:0>     |        | 352                 |

### TABLE 28-5: SUMMARY OF REGISTERS ASSOCIATED WITH CCPx

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the CCP module.

### TABLE 31-4: SUMMARY OF REGISTERS ASSOCIATED WITH CLCx

| Name     | Bit 7  | Bit 6  | Bit 5    | Bit 4    | Bit 3          | Bit 2    | Bit 1        | Bit 0    | Register<br>on Page |

|----------|--------|--------|----------|----------|----------------|----------|--------------|----------|---------------------|

| INTCON   | GIE    | PEIE   | _        | _        | _              | _        | _            | INTEDG   | 119                 |

| PIR5     | CLC4IF | CLC3IF | CLC2IF   | CLC1IF   | _              | _        | _            | TMR1GIF  | 133                 |

| PIE5     | CLC4IE | CLC4IE | CLC2IE   | CLC1IE   | _              | _        | _            | TMR1GIE  | 125                 |

| CLC1CON  | LC1EN  | _      | LC10UT   | LC1INTP  | LC1INTN        |          | LC1MODE<2:0  | >        | 361                 |

| CLC1POL  | LC1POL | _      | _        | _        | LC1G4POL       | LC1G3POL | LC1G2POL     | LC1G1POL | 362                 |

| CLC1SEL0 | _      | _      |          |          | LC1D           | 1S<5:0>  | 1            | 1        | 363                 |

| CLC1SEL1 | _      |        |          |          | LC1D           | 2S<5:0>  |              |          | 363                 |

| CLC1SEL2 | _      | _      |          |          | LC1D           | 3S<5:0>  |              |          | 363                 |

| CLC1SEL3 | _      | _      |          |          | LC1D           | 4S<5:0>  |              |          | 363                 |

| CLC1GLS0 | _      | _      | LC1G1D3T | LC1G1D3N | LC1G1D2T       | LC1G1D2N | LC1G1D1T     | LC1G1D1N | 364                 |

| CLC1GLS1 | _      | _      | LC1G2D3T | LC1G2D3N | LC1G2D2T       | LC1G2D2N | LC1G2D1T     | LC1G2D1N | 365                 |

| CLC1GLS2 | _      | _      | LC1G3D3T | LC1G3D3N | LC1G3D2T       | LC1G3D2N | LC1G3D1T     | LC1G3D1N | 366                 |

| CLC1GLS3 | _      | _      | LC1G4D3T | LC1G4D3N | LC1G4D2T       | LC1G4D2N | LC1G4D1T     | LC1G4D1N | 367                 |

| CLC2CON  | LC2EN  | _      | LC2OUT   | LC2INTP  | LC2INTN        |          | LC2MODE<2:0  | >        | 361                 |

| CLC2POL  | LC2POL | _      | _        | —        | LC2G4POL       | LC2G3POL | LC2G2POL     | LC2G1POL | 362                 |

| CLC2SEL0 | _      | _      |          | L        | LC2D           | 1S<5:0>  |              |          | 363                 |

| CLC2SEL1 | _      | _      |          |          | LC2D           | 2S<5:0>  |              |          | 363                 |

| CLC2SEL2 | _      | _      |          |          | LC2D           | 3S<5:0>  |              |          | 363                 |

| CLC2SEL3 | _      | _      |          |          | LC2D           | 4S<5:0>  |              |          | 363                 |

| CLC2GLS0 | _      | _      | LC2G1D3T | LC2G1D3N | LC2G1D2T       | LC2G1D2N | LC2G1D1T     | LC2G1D1N | 364                 |

| CLC2GLS1 | —      | _      | LC2G2D3T | LC2G2D3N | LC2G2D2T       | LC2G2D2N | LC2G2D1T     | LC2G2D1N | 365                 |

| CLC2GLS2 | —      | _      | LC2G3D3T | LC2G3D3N | LC2G3D2T       | LC2G3D2N | LC2G3D1T     | LC2G3D1N | 366                 |

| CLC2GLS3 | _      | _      | LC2G4D3T | LC2G4D3N | LC2G4D2T       | LC2G4D2N | LC2G4D1T     | LC2G4D1N | 367                 |

| CLC3CON  | LC3EN  | _      | LC3OUT   | LC3INTP  | <b>LC3INTN</b> |          | LC3MODE<2:0  | >        | 361                 |

| CLC3POL  | LC3POL | _      | _        | —        | LC3G4POL       | LC3G3POL | LC3G2POL     | LC3G1POL | 362                 |

| CLC3SEL0 | —      | _      |          |          | LC3D           | 1S<5:0>  |              |          | 363                 |

| CLC3SEL1 | _      | _      |          |          | LC3D           | 2S<5:0>  |              |          | 363                 |

| CLC3SEL2 | _      | _      |          |          | LC3D           | 3S<5:0>  |              |          | 363                 |

| CLC3SEL3 | —      | _      |          |          | LC3D           | 4S<5:0>  |              |          | 363                 |

| CLC3GLS0 | _      | _      | LC3G1D3T | LC3G1D3N | LC3G1D2T       | LC3G1D2N | LC3G1D1T     | LC3G1D1N | 364                 |

| CLC3GLS1 | _      | _      | LC3G2D3T | LC3G2D3N | LC3G2D2T       | LC3G2D2N | LC3G2D1T     | LC3G2D1N | 365                 |

| CLC3GLS2 | _      | _      | LC3G3D3T | LC3G3D3N | LC3G3D2T       | LC3G3D2N | LC3G3D1T     | LC3G3D1N | 366                 |

| CLC3GLS3 | _      | _      | LC3G4D3T | LC3G4D3N | LC3G4D2T       | LC3G4D2N | LC3G4D1T     | LC3G4D1N | 367                 |

| CLC4CON  | LC4EN  | _      | LC4OUT   | LC4INTP  | LC4INTN        |          | LC4MODE<2:0> | >        | 361                 |

| CLC4POL  | LC4POL | _      | _        | _        | LC4G4POL       | LC4G3POL | LC4G2POL     | LC4G1POL | 362                 |

| CLC4SEL0 | _      | _      |          |          | LC4D           | 1S<5:0>  |              | 1        | 363                 |

| CLC4SEL1 | _      | _      |          |          | LC4D           | 2S<5:0>  |              |          | 363                 |

| CLC4SEL2 | _      | _      |          |          | LC4D           | 3S<5:0>  |              |          | 363                 |

| CLC4SEL3 | _      | _      |          |          | LC4D           | 4S<5:0>  |              |          | 363                 |

| CLC4GLS0 | _      | _      | LC4G1D3T | LC4G1D3N | LC4G1D2T       | LC4G1D2N | LC4G1D1T     | LC4G1D1N | 364                 |

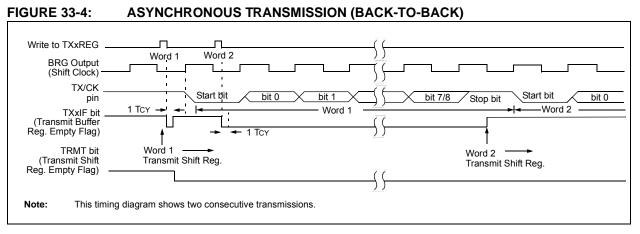

### 33.1.2 EUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 33-2. The data is received on the RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the EUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCxREG register.

### 33.1.2.1 Enabling the Receiver

The EUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCxSTA register enables the receiver circuitry of the EUSART. Clearing the SYNC bit of the TXxSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCxSTA register enables the EUSART. The programmer must set the corresponding TRIS bit to configure the RX/DT I/O pin as an input.

**Note:** If the RX/DT function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

## 33.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. See Section 33.1.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the EUSART receive FIFO and the RXxIF interrupt flag bit of the PIR3 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCxREG register.

Note: If the receive FIFO is overrun, no additional characters will be received until the overrun condition is cleared. See Section 33.1.2.5 "Receive Overrun Error" for more information on overrun errors.

# 36.3 Instruction Descriptions

| ADDFSR           | Add Literal to FSRn                                                                              |

|------------------|--------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ADDFSR FSRn, k                                                                         |

| Operands:        | $-32 \le k \le 31$<br>n $\in$ [ 0, 1]                                                            |

| Operation:       | $FSR(n) + k \rightarrow FSR(n)$                                                                  |

| Status Affected: | None                                                                                             |

| Description:     | The signed 6-bit literal 'k' is added to<br>the contents of the FSRnH:FSRnL<br>register pair.    |

|                  | FSRn is limited to the range<br>0000h-FFFFh. Moving beyond these<br>bounds will cause the FSR to |

| ANDLW            | AND literal with W                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                        |

| Operands:        | $0 \leq k \leq 255$                                                                                             |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                 |

| Status Affected: | Z                                                                                                               |

| Description:     | The contents of W register are<br>AND'ed with the 8-bit literal 'k'. The<br>result is placed in the W register. |

| ADDLW            | Add literal and W                                                                                             |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                      |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                           |  |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                             |  |  |  |

| Status Affected: | C, DC, Z                                                                                                      |  |  |  |

| Description:     | The contents of the W register are added to the 8-bit literal 'k' and the result is placed in the W register. |  |  |  |

wrap-around.

| ANDWF            | AND W with f                                                                                                                                                    |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                      |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                 |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |  |  |  |

| Status Affected: | Z                                                                                                                                                               |  |  |  |

| Description:     | AND the W register with register 'f'. If<br>'d' is '0', the result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f'. |  |  |  |

| ADDWF            | Add W and f                                                                                                                                                                     |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                               |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                               |  |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                           |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                        |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the result is<br>stored in the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |  |  |  |  |

| ASRF             | Arithmetic Right Shift                                                                                                                                                                                                              |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ASRF f {,d}                                                                                                                                                                                                        |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                   |

| Operation:       | (f<7>)→ dest<7><br>(f<7:1>) → dest<6:0>,<br>(f<0>) → C,                                                                                                                                                                             |

| Status Affected: | C, Z                                                                                                                                                                                                                                |

| Description:     | The contents of register 'f' are shifted<br>one bit to the right through the Carry<br>flag. The MSb remains unchanged. If<br>'d' is '0', the result is placed in W. If 'd'<br>is '1', the result is stored back in<br>register 'f'. |

### ADDWFC ADD W and CARRY bit to f

| Syntax:          | [ <i>label</i> ] ADDWFC f {,d}                                                                                                                                            |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                         |  |  |  |

| Operation:       | $(W) + (f) + (C) \rightarrow dest$                                                                                                                                        |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                  |  |  |  |

| Description:     | Add W, the Carry flag and data mem-<br>ory location 'f'. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed in data memory location 'f'. |  |  |  |

The following sections give the technical details of the packages.

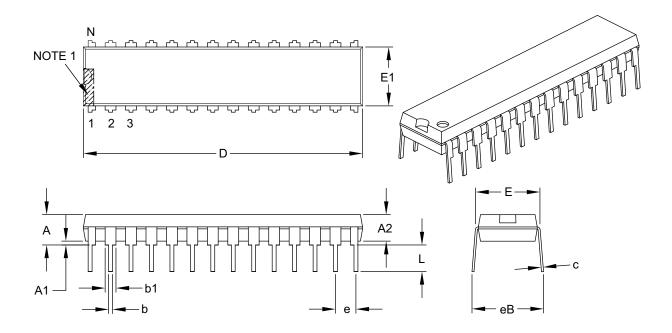

### 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | INCHES |          |       |       |

|----------------------------|--------|----------|-------|-------|

| Dimension Limits           |        | MIN      | NOM   | MAX   |

| Number of Pins             | Ν      | 28       |       |       |

| Pitch                      | е      | .100 BSC |       |       |

| Top to Seating Plane       | Α      | -        | -     | .200  |

| Molded Package Thickness   | A2     | .120     | .135  | .150  |

| Base to Seating Plane      | A1     | .015     | -     | -     |

| Shoulder to Shoulder Width | Е      | .290     | .310  | .335  |

| Molded Package Width       | E1     | .240     | .285  | .295  |

| Overall Length             | D      | 1.345    | 1.365 | 1.400 |

| Tip to Seating Plane       | L      | .110     | .130  | .150  |

| Lead Thickness             | С      | .008     | .010  | .015  |

| Upper Lead Width           | b1     | .040     | .050  | .070  |

| Lower Lead Width           | b      | .014     | .018  | .022  |

| Overall Row Spacing §      | eB     | -        | -     | .430  |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

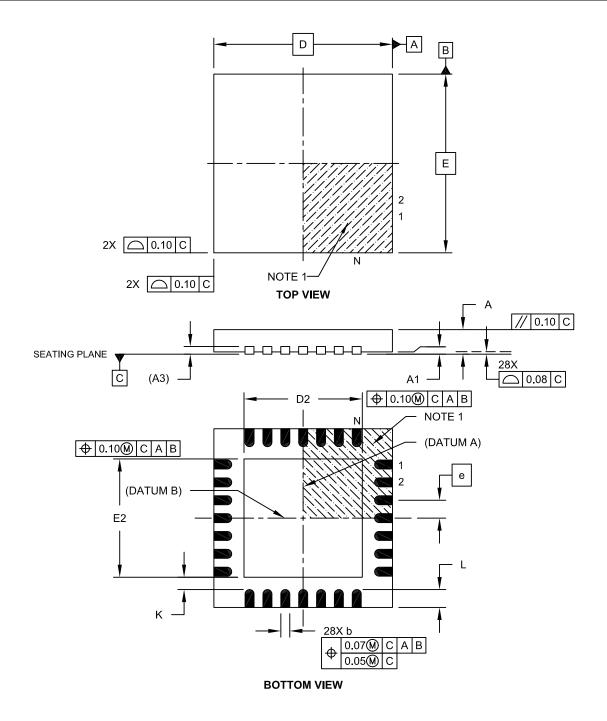

28-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-152A Sheet 1 of 2