Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 224 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

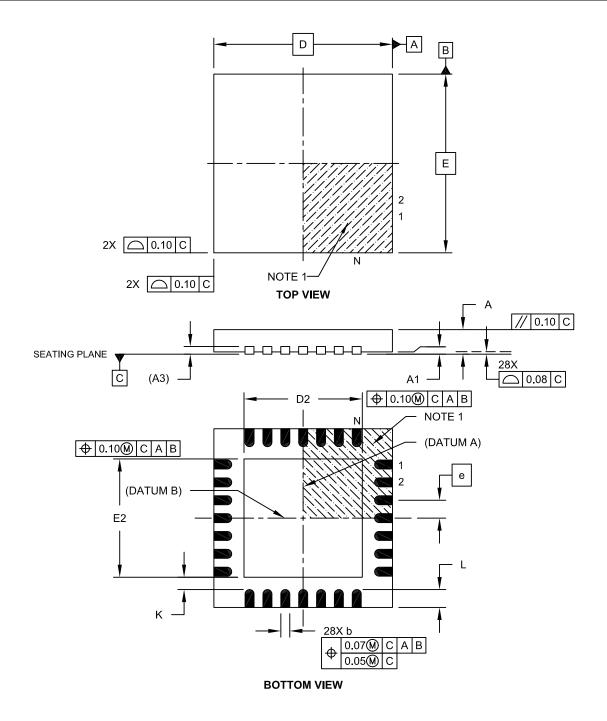

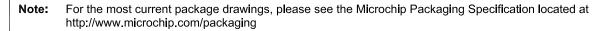

| Package / Case             | 28-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15355-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F15354/55

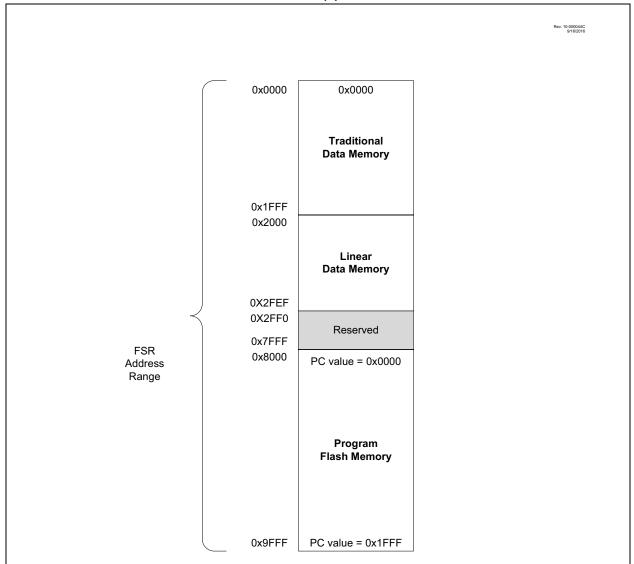

FIGURE 4-10: INDIRECT ADDRESSING PIC16(L)F15355

DS40001853B-page 99

| R/W-0/0          | R/W-0/0                                                                                                                                                                                                                                      | R/W-0/0                                             | R/W-0/0       | R/W-0/0          | R/W-0/0              | U-0              | U-0          |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------|------------------|----------------------|------------------|--------------|--|

| EXTOEN           | HFOEN                                                                                                                                                                                                                                        | MFOEN                                               | LFOEN         | SOSCEN           | ADOEN                | —                | —            |  |

| bit 7            |                                                                                                                                                                                                                                              |                                                     |               |                  |                      |                  | bit 0        |  |

|                  |                                                                                                                                                                                                                                              |                                                     |               |                  |                      |                  |              |  |

| Legend:          |                                                                                                                                                                                                                                              |                                                     |               |                  |                      |                  |              |  |

| R = Readable     | bit                                                                                                                                                                                                                                          | W = Writable                                        | bit           | U = Unimpler     | nented bit, read     | d as '0'         |              |  |

| u = Bit is unch  | anged                                                                                                                                                                                                                                        | x = Bit is unkr                                     | nown          | -n/n = Value a   | at POR and BO        | R/Value at all o | other Resets |  |

| '1' = Bit is set |                                                                                                                                                                                                                                              | '0' = Bit is clea                                   | ared          |                  |                      |                  |              |  |

| bit 7            | bit 7 <b>EXTOEN:</b> External Oscillator Manual Request Enable bit <sup>(1)</sup><br>1 = EXTOSC is explicitly enabled, operating as specified by FEXTOSC<br>0 = EXTOSC could be enabled by some modules                                      |                                                     |               |                  |                      |                  |              |  |

| bit 6            | 1 = HFINTO                                                                                                                                                                                                                                   | NTOSC Oscilla<br>SC is explicitly<br>SC could be e  | enabled, oper | rating as specif | bit<br>fied by OSCFR | Q                |              |  |

| bit 5            | 1 = MFINTOS                                                                                                                                                                                                                                  | NTOSC Oscilla<br>SC is explicitly of SC could be en | enabled       |                  | bit                  |                  |              |  |

| bit 4            | LFOEN: LFINTOSC (31 kHz) Oscillator Manual Request Enable bit<br>1 = LFINTOSC is explicitly enabled<br>0 = LFINTOSC could be enabled by another module                                                                                       |                                                     |               |                  |                      |                  |              |  |

| bit 3            | <ul> <li>SOSCEN: Secondary (Timer1) Oscillator Manual Request bit</li> <li>1 = Secondary oscillator is explicitly enabled, operating as specified by SOSCPWR</li> <li>0 = Secondary oscillator could be enabled by another module</li> </ul> |                                                     |               |                  |                      |                  |              |  |

| bit 2            | ADOEN: FRC Oscillator Manual Request Enable bit<br>1 = FRC is explicitly enabled<br>0 = FRC could be enabled by another module                                                                                                               |                                                     |               |                  |                      |                  |              |  |

| bit 1-0          | Unimplemen                                                                                                                                                                                                                                   | tad. Dood os '                                      | o'            |                  |                      |                  |              |  |

# REGISTER 9-5: OSCEN: OSCILLATOR MANUAL ENABLE REGISTER

| U-0            | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W/HS-0/0                               | R-0           | U-0                | U-0                | U-0              | R/W/HS-0/0          |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|---------------|--------------------|--------------------|------------------|---------------------|--|

| _              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | TMR0IF                                   | IOCIF         | _                  | _                  | _                | INTF <sup>(1)</sup> |  |

| bit 7          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          |               |                    |                    |                  | bit 0               |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          |               |                    |                    |                  |                     |  |

| Legend:        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          |               |                    |                    |                  |                     |  |

| R = Reada      | ble bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | W = Writable b                           | bit           | U = Unimpler       | nented bit, read   | as '0'           |                     |  |

| u = Bit is u   | nchanged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | x = Bit is unkn                          | own           | -n/n = Value a     | at POR and BO      | R/Value at all c | other Resets        |  |

| '1' = Bit is s | set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | '0' = Bit is clea                        | red           | HS= Hardwa         | re Set             |                  |                     |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          |               |                    |                    |                  |                     |  |

| bit 7-6        | Unimpleme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | nted: Read as '0                         | ,             |                    |                    |                  |                     |  |

| bit 5          | bit 5 TMR0IF: Timer0 Overflow Interrupt Flag bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                          |               |                    |                    |                  |                     |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | register has over<br>register did not    |               | st be cleared in   | software)          |                  |                     |  |

| bit 4          | IOCIF: Interr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | rupt-on-Change I                         | nterrupt Flag | g bit (read-only)  | (2)                |                  |                     |  |

|                | 1 = One or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | more of the IOC                          | AF-IOCEF re   | egister bits are o | currently set, ind | icating an enal  | bled edge was       |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ed by the IOC mo                         |               |                    |                    |                  |                     |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | of the IOCAF-IOC                         | -             | bits are current   | ly set             |                  |                     |  |

| bit 3-1        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | nted: Read as '0                         |               |                    |                    |                  |                     |  |

| bit 0          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | xternal Interrupt                        | -             |                    |                    |                  |                     |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | T external interru<br>T external interru |               |                    | ed in software)    |                  |                     |  |

| N              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          |               |                    |                    |                  |                     |  |

|                | The External Inter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | • •                                      |               |                    | ,                  |                  | 9                   |  |

|                | The IOCIF bit is the application firmware application for the second sec |                                          |               |                    |                    |                  | nag,                |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          |               |                    |                    |                  |                     |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          |               |                    |                    |                  |                     |  |

# REGISTER 10-10: PIR0: PERIPHERAL INTERRUPT STATUS REGISTER 0

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# PIC16(L)F15354/55

#### EXAMPLE 13-1: PFM PROGRAM MEMORY READ

```

* This code block will read 1 word of program

* memory at the memory address:

PROG_ADDR_HI : PROG_ADDR_LO

*

data will be returned in the variables;

*

PROG_DATA_HI, PROG_DATA_LO

BANKSEL NVMADRL ; Select Bank for NVMCON registers

MOVLW PROG_ADDR_LO ;

MOVWF NVMADRL ; Store LSB of address

MOVLW PROG_ADDR_HI ;

MOVWF NVMADRU

; Store MSB of address

MOVWF NVMADRH

BCF

NVMCON1,NVMREGS ; Do not select Configuration Space

BSF

NVMCON1, RD

; Initiate read

MOVF

NVMDATL,W

; Get LSB of word

NVMDAIL,W, Get LSB of wordPROG_DATA_LO; Store in user locationNVMDATH,W; Get MSB of wordPROG_DATA_HI; Store in user location

MOVWF

MOVF

MOVWF

```

| U-0     | U-0 | U-0 | R/W-0/u | R/W-0/u | R/W-0/u     | R/W-0/u | R/W-0/u |

|---------|-----|-----|---------|---------|-------------|---------|---------|

| —       | —   | —   |         |         | RxyPPS<4:0> |         |         |

| bit 7   |     |     |         |         |             |         | bit 0   |

|         |     |     |         |         |             |         |         |

| Legend: |     |     |         |         |             |         |         |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-5 | Unimplemented: Read as '0'                                                     |

|---------|--------------------------------------------------------------------------------|

| bit 4-0 | <b>RxyPPS&lt;5:0&gt;:</b> Pin Rxy Output Source Selection bits See Table 15-3. |

**Note 1:** TRIS control is overridden by the peripheral as required.

### REGISTER 15-3: PPSLOCK: PPS LOCK REGISTER

| U-0         | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0   |  |  |

|-------------|-----|-----|-----|-----|-----|-----|-----------|--|--|

| —           | —   | —   | —   | —   | —   | —   | PPSLOCKED |  |  |

| bit 7 bit 0 |     |     |     |     |     |     |           |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-1 Unimplemented: Read as '0'

bit 0 PPSLOCKED: PPS Locked bit

$\ensuremath{\texttt{1=PPS}}$  is locked. PPS selections can not be changed.

0= PPS is not locked. PPS selections can be changed.

# 20.3 ADC Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 20-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 20-4. The maximum recommended impedance for analog sources is 10 k $\Omega$  As the

source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an ADC acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 20-1 may be used. This equation assumes that 1/2 LSb error is used (1,024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

### EQUATION 20-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature =

$$50^{\circ}C$$

and external impedance of  $10k\Omega 5.0V$  VDD

$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$

$= TAMP + TC + TCOFF$

$= 2\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$

*The value for TC can be approximated with the following equations:*

$$V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) = V_{CHOLD} \qquad ;[1] V_{CHOLD} charged to within 1/2 lsb$$

$$V_{APPLIED}\left(1 - e^{\frac{-Tc}{RC}}\right) = V_{CHOLD} \qquad ;[2] V_{CHOLD} charge response to V_{APPLIED} V_{APPLIED}\left(1 - e^{\frac{-Tc}{RC}}\right) = V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) \qquad ;combining [1] and [2]$$

Note: Where n = number of bits of the ADC.

Solving for TC:

ł

$$Tc = -C_{HOLD}(RIC + RSS + RS) \ln(1/2047)$$

=  $-10pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.0004885)$

=  $1.37\mu s$

Therefore:

$$TACQ = 2\mu s + 1.37 + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 4.62\mu s

**Note 1:** The VAPPLIED has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is  $10 \text{ k}\Omega$ . This is required to meet the pin leakage specification.

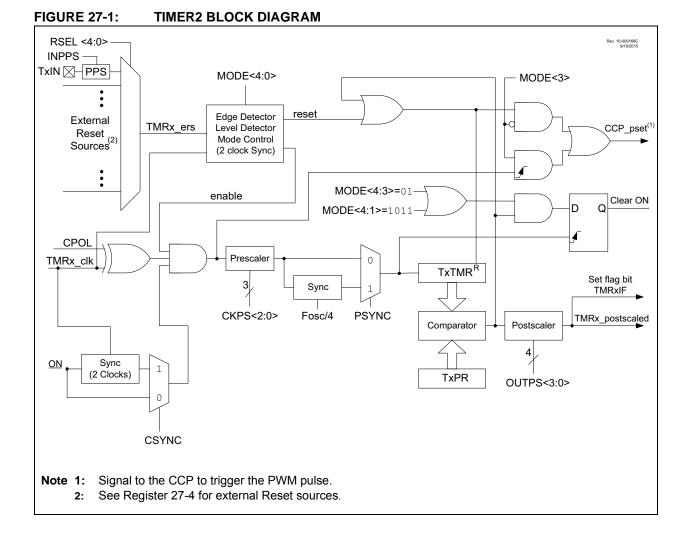

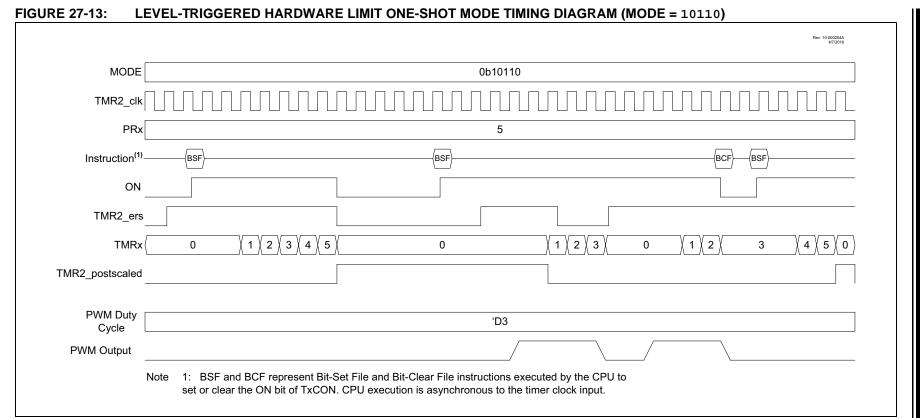

# 27.0 TIMER2 MODULE WITH HARDWARE LIMIT TIMER (HLT)

The Timer2 modules are 8-bit timers that can operate as free-running period counters or in conjunction with external signals that control start, run, freeze, and reset operation in One-Shot and Monostable modes of operation. Sophisticated waveform control such as pulse density modulation are possible by combining the operation of these timers with other internal peripherals such as the comparators and CCP modules. Features of the timer include:

- 8-bit timer register

- · 8-bit period register

- · Selectable external hardware timer Resets

- Programmable prescaler (1:1 to 1:128)

- Programmable postscaler (1:1 to 1:16)

- · Selectable synchronous/asynchronous operation

- · Alternate clock sources

- · Interrupt-on-period

- · Three modes of operation:

- Free Running Period

- One-shot

- Monostable

See Figure 27-1 for a block diagram of Timer2. See Figure 27-2 for the clock source block diagram.

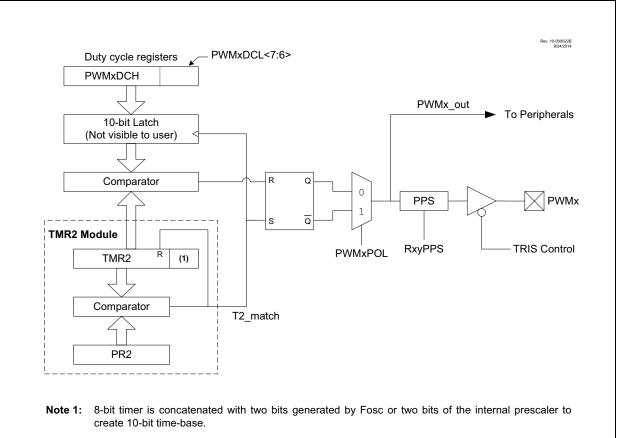

### 29.1 Standard PWM Mode

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the PWMx pin with up to ten bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- TMR2 register

- PR2 register

- PWMxCON registers

- PWMxDCH registers

- PWMxDCL registers

Figure 29-2 shows a simplified block diagram of PWM operation.

If PWMPOL = 0, the default state of the output is '0'. If PWMPOL = 1, the default state is '1'. If PWMEN = 0, the output will be the default state.

Note: The corresponding TRIS bit must be cleared to enable the PWM output on the PWMx pin

### FIGURE 29-2: SIMPLIFIED PWM BLOCK DIAGRAM

| U-0                                                                  | U-0        | R-x                                    | U-0        | R/W-0/0        | R/W-0/0         | R/W-0/0          | R/W-0/0     |  |  |

|----------------------------------------------------------------------|------------|----------------------------------------|------------|----------------|-----------------|------------------|-------------|--|--|

| _                                                                    | _          | IN                                     | _          | POLD           | POLC            | POLB             | POLA        |  |  |

| bit 7                                                                | ·          |                                        |            | · ·            |                 | •                | bit 0       |  |  |

| Legend:                                                              |            |                                        |            |                |                 |                  |             |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |            |                                        |            |                |                 |                  |             |  |  |

| u = Bit is un                                                        | changed    | x = Bit is unkr                        | nown       | -n/n = Value a | at POR and BO   | R/Value at all c | ther Resets |  |  |

| '1' = Bit is se                                                      | et         | '0' = Bit is cle                       | ared       | q = Value dep  | pends on condit | ion              |             |  |  |

| bit 7-6                                                              | Unimpleme  | ented: Read as '                       | o'         |                |                 |                  |             |  |  |

| bit 5                                                                | •          | put Value bit                          | 0          |                |                 |                  |             |  |  |

| bit 4                                                                |            | ented: Read as '                       | 0'         |                |                 |                  |             |  |  |

| bit 3                                                                | •          | G1D Output Pola                        |            |                |                 |                  |             |  |  |

|                                                                      | 1 = Signal | output is inverted                     | l polarity |                |                 |                  |             |  |  |

| bit 2                                                                | POLC: CW   | POLC: CWG1C Output Polarity bit        |            |                |                 |                  |             |  |  |

|                                                                      | 0          | output is inverted<br>output is normal |            |                |                 |                  |             |  |  |

| bit 1                                                                | POLB: CW   | G1B Output Pola                        | rity bit   |                |                 |                  |             |  |  |

|                                                                      |            | output is inverted<br>output is normal |            |                |                 |                  |             |  |  |

| bit 0                                                                | POLA: CW   | POLA: CWG1A Output Polarity bit        |            |                |                 |                  |             |  |  |

|                                                                      | 0          | output is inverted<br>output is normal |            |                |                 |                  |             |  |  |

# REGISTER 30-2: CWG1CON1: CWG1 CONTROL REGISTER 1

# PIC16(L)F15354/55

E.

| U-1              | U-1                                 | U-1                                      | R/W-0/0     | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |  |

|------------------|-------------------------------------|------------------------------------------|-------------|----------------|------------------|------------------|--------------|--|--|--|

| _                | _                                   | —                                        | AS4E        | AS3E           | AS2E             | AS1E             | AS0E         |  |  |  |

| bit 7            |                                     |                                          |             |                |                  |                  | bit 0        |  |  |  |

|                  |                                     |                                          |             |                |                  |                  |              |  |  |  |

| Legend:          |                                     |                                          |             |                |                  |                  |              |  |  |  |

| R = Readable     | bit                                 | W = Writable                             | bit         | U = Unimpler   | mented bit, read | l as '0'         |              |  |  |  |

| u = Bit is unch  | anged                               | x = Bit is unkr                          | iown        | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |  |  |  |

| '1' = Bit is set |                                     | '0' = Bit is clea                        | ared        | q = Value der  | pends on condit  | ion              |              |  |  |  |

|                  |                                     |                                          |             |                |                  |                  |              |  |  |  |

| bit 7-5          | Unimplemen                          | ted: Read as '                           | כי          |                |                  |                  |              |  |  |  |

| bit 4            | AS4E: CLC2                          | Output bit                               |             |                |                  |                  |              |  |  |  |

|                  | 1 = LC2_out shut-down is enabled    |                                          |             |                |                  |                  |              |  |  |  |

|                  | 0 = LC2_out shut-down is disabled   |                                          |             |                |                  |                  |              |  |  |  |

| bit 3            | AS3E: Compa                         | E: Comparator C2 Output bit              |             |                |                  |                  |              |  |  |  |

|                  | 1 = C2 output shut-down is enabled  |                                          |             |                |                  |                  |              |  |  |  |

|                  | 0 = C2 output shut-down is disabled |                                          |             |                |                  |                  |              |  |  |  |

| bit 2            | AS2E: Compa                         | arator C1 Outp                           | ut bit      |                |                  |                  |              |  |  |  |

|                  |                                     | 1 = C1 output shut-down is enabled       |             |                |                  |                  |              |  |  |  |

|                  | 0 = C1 output shut-down is disabled |                                          |             |                |                  |                  |              |  |  |  |

| bit 2            | AS1E: TMR2                          | Postscale Out                            | put bit     |                |                  |                  |              |  |  |  |