Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XF

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 25                                                                           |

| Program Memory Size        | 14KB (8K x 14)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 224 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 28-QFN (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15355t-i-ml |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See **Section 10.5 "Automatic Context Saving"** for more information.

#### 3.2 16-Level Stack with Overflow and Underflow

These devices have a hardware stack memory 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON register, and if enabled, will cause a software Reset. See **Section 4.5 "Stack**" for more details.

### 3.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers and program memory, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. See **Section 4.6** "**Indirect Addressing**" for more details.

### 3.4 Instruction Set

There are 48 instructions for the enhanced mid-range CPU to support the features of the CPU. See **Section 36.0 "Instruction Set Summary**" for more details.

#### 4.3.3 SPECIAL FUNCTION REGISTER

The Special Function Registers are registers used by the application to control the desired operation of peripheral functions in the device. The Special Function Registers occupy the 20 bytes of the data banks 0-59 and 100 bytes of the data banks 60-63, after the core registers.

The SFRs associated with the operation of the peripherals are described in the appropriate peripheral chapter of this data sheet.

#### 4.3.4 GENERAL PURPOSE RAM

There are up to 80 bytes of GPR in each data memory bank.

#### 4.3.4.1 Linear Access to GPR

The general purpose RAM can be accessed in a non-banked method via the FSRs. This can simplify access to large memory structures. See **Section 4.6.2** "**Linear Data Memory**" for more information.

#### 4.3.5 COMMON RAM

There are 16 bytes of common RAM accessible from all banks.

#### 4.3.6 DEVICE MEMORY MAPS

The memory maps are as shown in Table 4-4 through Table 4-9.

| <b>TABLE 4-10:</b> | SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED) |  |

|--------------------|----------------------------------------------------------|--|

|                    |                                                          |  |

| Address | Name                                            | Bit 7                        | Bit 6       | Bit 5 | Bit 4  | Bit 3   | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------|-------------------------------------------------|------------------------------|-------------|-------|--------|---------|-------|-------|-------|-----------------------|----------------------------|

| Bank 2  | ank 2                                           |                              |             |       |        |         |       |       |       |                       |                            |

|         | CPU CORE REGISTERS; see Table 4-3 for specifics |                              |             |       |        |         |       |       |       |                       |                            |

| 10Ch    |                                                 |                              |             |       |        |         |       |       | -     | _                     |                            |

| 119h    | RC1REG                                          | EUSART Receive Data Register |             |       |        |         |       |       |       | 0000 0000             | 0000 0000                  |

| 11Ah    | TX1REG                                          | EUSART Transmit Da           | ta Register |       |        |         |       |       |       | 0000 0000             | 0000 0000                  |

| 11Bh    | SP1BRGL                                         |                              |             |       | SP1BR0 | G<7:0>  |       |       |       | 0000 0000             | 0000 0000                  |

| 11Ch    | SP1BRGH                                         |                              |             |       | SP1BRG | i<15:8> |       |       |       | 0000 0000             | 0000 0000                  |

| 11Dh    | RC1STA                                          | SPEN                         | RX9         | SREN  | CREN   | ADDEN   | FERR  | OERR  | RX9D  | 0000 0000             | 0000 0000                  |

| 11Eh    | TX1STA                                          | CSRC                         | TX9         | TXEN  | SYNC   | SENDB   | BRGH  | TRMT  | TX9D  | 0000 0010             | 0000 0010                  |

| 11Fh    | BAUD1CON                                        | ABDOVF                       | RCIDL       | _     | SCKP   | BRG16   | _     | WUE   | ABDEN | 01-0 0-00             | 01-0 0-00                  |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

#### TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

| Address                                         | Name             | Bit 7                | Bit 7     Bit 6     Bit 5     Bit 4     Bit 3     Bit 2     Bit 1     Bit 0     Value on:<br>POR, BOR     Value on:<br>MCLR |                   |                    |                  |                  |                  |             |  | V <u>alue o</u> n:<br>MCLR |

|-------------------------------------------------|------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------|------------------|------------------|------------------|-------------|--|----------------------------|

| Bank 21-59                                      | Jank 21-59       |                      |                                                                                                                             |                   |                    |                  |                  |                  |             |  |                            |

| CPU CORE REGISTERS; see Table 4-3 for specifics |                  |                      |                                                                                                                             |                   |                    |                  |                  |                  |             |  |                            |

| x0Ch/<br>x8Ch<br>                               |                  |                      |                                                                                                                             |                   |                    |                  |                  |                  |             |  |                            |

| Legend:                                         | x = unknown, u : | = unchanged, q = dep | ends on conditior                                                                                                           | ı, - = unimplemer | nted, read as '0', | r = reserved. Sh | aded locations u | inimplemented, r | ead as '0'. |  |                            |

#### 7.0 DEVICE CONFIGURATION INFORMATION

The Device Configuration Information (DCI) is a dedicated region in the Program Flash Memory mapped from 8200h to 821Fh. The data stored in the DCI memory is hard-coded into the device during manufacturing.

Refer to Table 7-1: Device Configuration Information for PIC16(L)F15354/55 Devices for the complete DCI table address and description. The DCI holds information about the device which is useful for programming and bootloader applications. These locations are read-only and cannot be erased or modified.

| ADDRESS      | Name  | DESCRIPTION             | VAI            | UNITS          |         |

|--------------|-------|-------------------------|----------------|----------------|---------|

| ADDRESS Name |       | DESCRIPTION             | PIC16(L)F15354 | PIC16(L)F15355 | UNITS   |

| 8200h        | ERSIZ | Erase Row Size          | 32             | 32             | Words   |

| 8201h        | WLSIZ | Number of write latches | 32             | 32             | Latches |

| 8202h        | URSIZ | Number of User Rows     | 128            | 256            | Rows    |

| 8203h        | EESIZ | EE Data memory size     | 0              | 0              | Bytes   |

| 8204h        | PCNT  | Pin Count               | 28             | 28             | Pins    |

#### TABLE 7-1: DEVICE CONFIGURATION INFORMATION FOR PIC16(L)F15354/55 DEVICES

#### 7.1 DIA and DCI Access

The DIA and DCI data are read-only and cannot be erased or modified. See **13.3.6** "NVMREG Access to Device Information Area, Device Configuration Area, User ID, Device ID and Configuration Words" for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the DIA and DCI regions, similar to the Device ID and Revision ID.

| R/W-0/0                                                                                                                                                                                                                   | R/W-0/0                                                                                                                                                                                      | R/W-0/0                                             | R/W-0/0 | R/W-0/0        | R/W-0/0          | U-0              | U-0          |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------|----------------|------------------|------------------|--------------|--|

| EXTOEN                                                                                                                                                                                                                    | HFOEN                                                                                                                                                                                        | MFOEN                                               | LFOEN   | SOSCEN         | ADOEN            | —                | —            |  |

| bit 7                                                                                                                                                                                                                     |                                                                                                                                                                                              |                                                     |         |                |                  |                  | bit 0        |  |

|                                                                                                                                                                                                                           |                                                                                                                                                                                              |                                                     |         |                |                  |                  |              |  |

| Legend:                                                                                                                                                                                                                   |                                                                                                                                                                                              |                                                     |         |                |                  |                  |              |  |

| R = Readable                                                                                                                                                                                                              | bit                                                                                                                                                                                          | W = Writable                                        | bit     | U = Unimpler   | nented bit, read | d as '0'         |              |  |

| u = Bit is unch                                                                                                                                                                                                           | anged                                                                                                                                                                                        | x = Bit is unkr                                     | nown    | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |  |

| '1' = Bit is set                                                                                                                                                                                                          |                                                                                                                                                                                              | '0' = Bit is clea                                   | ared    |                |                  |                  |              |  |

| bit 7 <b>EXTOEN:</b> External Oscillator Manual Request Enable bit <sup>(1)</sup><br>1 = EXTOSC is explicitly enabled, operating as specified by FEXTOSC<br>0 = EXTOSC could be enabled by some modules                   |                                                                                                                                                                                              |                                                     |         |                |                  |                  |              |  |

| bit 6                                                                                                                                                                                                                     | bit 6 <b>HFOEN:</b> HFINTOSC Oscillator Manual Request Enable bit<br>1 = HFINTOSC is explicitly enabled, operating as specified by OSCFRQ<br>0 = HFINTOSC could be enabled by another module |                                                     |         |                |                  |                  |              |  |

| bit 5                                                                                                                                                                                                                     | 1 = MFINTOS                                                                                                                                                                                  | NTOSC Oscilla<br>SC is explicitly of SC could be en | enabled |                | bit              |                  |              |  |

| bit 4                                                                                                                                                                                                                     | 1 = LFINTO                                                                                                                                                                                   | ITOSC (31 kHz<br>SC is explicitly<br>SC could be er | enabled |                | Enable bit       |                  |              |  |

| bit 3 <b>SOSCEN:</b> Secondary (Timer1) Oscillator Manual Request bit<br>1 = Secondary oscillator is explicitly enabled, operating as specified by SOSCPWR<br>0 = Secondary oscillator could be enabled by another module |                                                                                                                                                                                              |                                                     |         |                |                  |                  |              |  |

| bit 2                                                                                                                                                                                                                     | 2 ADOEN: FRC Oscillator Manual Request Enable bit<br>1 = FRC is explicitly enabled<br>0 = FRC could be enabled by another module                                                             |                                                     |         |                |                  |                  |              |  |

| bit 1-0                                                                                                                                                                                                                   |                                                                                                                                                                                              |                                                     |         |                |                  |                  |              |  |

#### REGISTER 9-5: OSCEN: OSCILLATOR MANUAL ENABLE REGISTER

| R/W/HS-0/                             | 0 R/W/HS-0/0                                                             | R/W/HS-0/0                                                                                                                                             | R/W/HS-0/0      | R/W/HS-0/0       | R/W/HS-0/0                         | R/W/HS-0/0         | R/W/HS-0/0     |  |

|---------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|------------------------------------|--------------------|----------------|--|

| RC2IF                                 | TX2IF                                                                    | RC1IF                                                                                                                                                  | TX1IF           | BCL2IF           | SSP2IF                             | BCL1IF             | SSP1IF         |  |

| bit 7                                 |                                                                          |                                                                                                                                                        |                 |                  |                                    |                    | bit (          |  |

| Legend:                               |                                                                          |                                                                                                                                                        |                 |                  |                                    |                    |                |  |

| R = Readab                            | le bit                                                                   | W = Writable                                                                                                                                           | bit             | U = Unimpler     | nented bit, read                   | as '0'             |                |  |

| u = Bit is un                         | changed                                                                  | x = Bit is unkr                                                                                                                                        | nown            | •                | at POR and BO                      |                    | ther Resets    |  |

| '1' = Bit is set '0' = Bit is cleared |                                                                          |                                                                                                                                                        |                 | HS = Hardwa      | re clearable                       |                    |                |  |

| bit 7                                 |                                                                          | ART2 Receive I                                                                                                                                         | nterrunt Enab   | le hit           |                                    |                    |                |  |

|                                       |                                                                          |                                                                                                                                                        |                 |                  | at least one by                    | te)                |                |  |

|                                       |                                                                          | ART2 receive                                                                                                                                           |                 |                  |                                    | ,                  |                |  |

| bit 6                                 | TX2IF: EUSA                                                              | RT2 Transmit I                                                                                                                                         | Interrupt Enab  | le bit           |                                    |                    |                |  |

|                                       |                                                                          |                                                                                                                                                        |                 |                  | unoccupied spa                     |                    |                |  |

|                                       | 0 = The EUS<br>TXxREG                                                    |                                                                                                                                                        | it buffer is cu | rrently full. Th | e application f                    | rmware should      | d not write to |  |

| bit 5                                 | RC1IF: EUSA                                                              | ART1 Receive I                                                                                                                                         | nterrupt Flag   | (read-only) bit  | (1)                                |                    |                |  |

|                                       | 1 = The EUSART1 receive buffer is not empty (contains at least one byte) |                                                                                                                                                        |                 |                  |                                    |                    |                |  |

|                                       | 0 = The EUSART1 receive buffer is empty                                  |                                                                                                                                                        |                 |                  |                                    |                    |                |  |

| bit 4                                 |                                                                          | <b>TX1IF:</b> EUSART1 Transmit Interrupt Flag (read-only) bit <sup>(2)</sup><br>1 = The EUSART1 transmit buffer contains at least one unoccupied space |                 |                  |                                    |                    |                |  |

|                                       |                                                                          |                                                                                                                                                        |                 |                  | ne application f                   |                    | d not write to |  |

|                                       |                                                                          |                                                                                                                                                        |                 |                  | in the transmit                    |                    |                |  |

| bit 3                                 | BCL2IF: MSS                                                              | SP2 Bus Collisi                                                                                                                                        | on Interrupt FI | ag bit           |                                    |                    |                |  |

|                                       |                                                                          | ision was dete                                                                                                                                         | •               | cleared in soft  | ware)                              |                    |                |  |

| bit 2                                 |                                                                          | ollision was det                                                                                                                                       |                 | ) Interrupt Elev | a hit                              |                    |                |  |

| DIL Z                                 | -                                                                        | chronous Seria                                                                                                                                         | -               | -                | lete (must be cl                   | eared in softwa    | are)           |  |

|                                       |                                                                          | or the Transmis                                                                                                                                        | •               |                  | •                                  |                    | 10)            |  |

| bit 1                                 | BCL1IF: MSS                                                              | SP1 Bus Collisi                                                                                                                                        | on Interrupt Fl | ag bit           |                                    |                    |                |  |

|                                       |                                                                          | llision was dete                                                                                                                                       |                 | cleared in sof   | ťware)                             |                    |                |  |

|                                       |                                                                          | ollision was de                                                                                                                                        |                 |                  |                                    |                    |                |  |

| bit 0                                 |                                                                          | chronous Seria                                                                                                                                         | •               | <i>,</i> , ,     | •                                  |                    |                |  |

|                                       |                                                                          | or the Transmis                                                                                                                                        |                 |                  | lete (must be cl<br>on in progress | eared in soltwa    | ire)           |  |

|                                       | The RC1IF flag is a imes to remove al                                    |                                                                                                                                                        |                 |                  | firmware must                      | read from RCx      | REG enough     |  |

|                                       | he TX1IF flag is a                                                       | -                                                                                                                                                      |                 |                  | the transmit but                   | ffer. To clear the | e TX1IF flag,  |  |

|                                       | he firmware must<br>X1IF flag does no                                    |                                                                                                                                                        |                 |                  |                                    |                    | ouffer. The    |  |

|                                       |                                                                          |                                                                                                                                                        |                 |                  |                                    |                    |                |  |

|                                       | nterrupt flag bits a                                                     |                                                                                                                                                        |                 |                  |                                    |                    |                |  |

|                                       | condition occurs, re<br>ts corresponding e                               |                                                                                                                                                        |                 |                  |                                    |                    |                |  |

|                                       | Enable bit, GIE, o                                                       |                                                                                                                                                        |                 |                  |                                    |                    |                |  |

|                                       | Jser software                                                            |                                                                                                                                                        | -               |                  |                                    |                    |                |  |

© 2016 Microchip Technology Inc.

appropriate interrupt flag bits are clear

prior to enabling an interrupt.

| R/W-1/1                                 | R/W-1/1 | R/W-1/1 | R/W-1/1                                               | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-----------------------------------------|---------|---------|-------------------------------------------------------|---------|---------|---------|---------|

| SLRA7                                   | SLRA6   | SLRA5   | SLRA4                                                 | SLRA3   | SLRA2   | SLRA1   | SLRA0   |

| bit 7                                   |         |         |                                                       |         |         |         | bit 0   |

|                                         |         |         |                                                       |         |         |         |         |

| Legend:                                 |         |         |                                                       |         |         |         |         |

| R = Readable bit W = Writable bit       |         |         | U = Unimplemented bit, read as '0'                    |         |         |         |         |

| u = Bit is unchanged x = Bit is unknown |         |         | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |         |

#### REGISTER 14-7: SLRCONA: PORTA SLEW RATE CONTROL REGISTER

bit 7-0 SLRA<7:0>: PORTA Slew Rate Enable bits For RA<7:0> pins, respectively 1 = Port pin slew rate is limited

'1' = Bit is set

0 = Port pin slews at maximum rate

#### **REGISTER 14-8: INLVLA: PORTA INPUT LEVEL CONTROL REGISTER**

'0' = Bit is cleared

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| INLVLA7 | INLVLA6 | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 INLVLA<7:0>: PORTA Input Level Select bits For RA<7:0> pins, respectively 1 = ST input used for PORT reads and interrupt-on-change 0 = TTL input used for PORT reads and interrupt-on-change

#### TABLE 14-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| PORTA   | RA7     | RA6     | RA5     | RA4     | RA3     | RA2     | RA1     | RA0     | 173                 |

| TRISA   | TRISA7  | TRISA6  | TRISA5  | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  | 173                 |

| LATA    | LATA7   | LATA6   | LATA5   | LATA4   | LATA3   | LATA2   | LATA1   | LATA0   | 174                 |

| ANSELA  | ANSA7   | ANSA6   | ANSA5   | ANSA4   | ANSA3   | ANSA2   | ANSA1   | ANSA0   | 174                 |

| WPUA    | WPUA7   | WPUA6   | WPUA5   | WPUA4   | WPUA3   | WPUA2   | WPUA1   | WPUA0   | 175                 |

| ODCONA  | ODCA7   | ODCA6   | ODCA5   | ODCA4   | ODCA3   | ODCA2   | ODCA1   | ODCA0   | 175                 |

| SLRCONA | SLRA7   | SLRA6   | SLRA5   | SLRA4   | SLRA3   | SLRA2   | SLRA1   | SLRA0   | 176                 |

| INLVLA  | INLVLA7 | INLVLA6 | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 176                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

Note 1: Unimplemented, read as '1'.

#### 23.2 Comparator Control

Each comparator has two control registers: CMxCON0 and CMxCON1.

The CMxCON0 register (see Register 23-1) contains Control and Status bits for the following:

- Enable

- Output

- Output polarity

- · Hysteresis enable

- Timer1 output synchronization

The CMxCON1 register (see Register 23-2) contains Control bits for the following:

- · Interrupt on positive/negative edge enables

- The CMxNSEL and CMxPSEL (Register 23-3 and Register 23-4) contain control bits for the following:

- Positive input channel selection

- Negative input channel selection

#### 23.2.1 COMPARATOR ENABLE

Setting the CxON bit of the CMxCON0 register enables the comparator for operation. Clearing the CxON bit disables the comparator resulting in minimum current consumption.

#### 23.2.2 COMPARATOR OUTPUT

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the MCxOUT bit of the CMOUT register.

The comparator output can also be routed to an external pin through the RxyPPS register (Register 15-2). The corresponding TRIS bit must be clear to enable the pin as an output.

Note 1: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

#### 23.2.3 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the CxPOL bit of the CMxCON0 register. Clearing the CxPOL bit results in a non-inverted output.

Table 23-2 shows the output state versus input conditions, including polarity control.

#### TABLE 23-2: COMPARATOR OUTPUT STATE VS. INPUT CONDITIONS

| Input Condition | CxPOL | CxOUT |

|-----------------|-------|-------|

| CxVN > CxVP     | 0     | 0     |

| CxVN < CxVP     | 0     | 1     |

| CxVN > CxVP     | 1     | 1     |

| CxVN < CxVP     | 1     | 0     |

| REGISTER 23-2: | CMxCON1: COMPARATOR Cx CONTROL REGISTER 1 |

|----------------|-------------------------------------------|

|----------------|-------------------------------------------|

| U-0                                                                                        | U-0 | U-0               | U-0  | U-0          | U-0              | R/W-0/0  | R/W-0/0 |

|--------------------------------------------------------------------------------------------|-----|-------------------|------|--------------|------------------|----------|---------|

| —                                                                                          | —   | —                 | —    | —            |                  | INTP     | INTN    |

| bit 7                                                                                      |     |                   |      |              |                  |          | bit 0   |

|                                                                                            |     |                   |      |              |                  |          |         |

| Legend:                                                                                    |     |                   |      |              |                  |          |         |

| R = Readable                                                                               | bit | W = Writable      | bit  | U = Unimplen | nented bit, read | l as '0' |         |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Res |     |                   |      |              | other Resets     |          |         |

| '1' = Bit is set                                                                           |     | '0' = Bit is clea | ared |              |                  |          |         |

| bit 7-2<br>bit 1 | Unimplemented: Read as '0'<br>INTP: Comparator Interrupt on Positive-Going Edge Enable bits                                                                                                                                                                         |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | <ul> <li>1 = The CxIF interrupt flag will be set upon a positive-going edge of the CxOUT bit</li> <li>0 = No interrupt flag will be set on a positive-going edge of the CxOUT bit</li> </ul>                                                                        |

| bit 0            | <ul> <li>INTN: Comparator Interrupt on Negative-Going Edge Enable bits</li> <li>1 = The CxIF interrupt flag will be set upon a negative-going edge of the CxOUT bit</li> <li>0 = No interrupt flag will be set on a negative-going edge of the CxOUT bit</li> </ul> |

| R/W-0/0          | R/W-0/0                                                                                                                                                         | R/W-0/0                                   | R/W-0/0    | R/W-0/0             | R/W-0/0             | R/W-0/0             | R/W-0/0             |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------|---------------------|---------------------|---------------------|---------------------|--|--|

| OVRD             | OVRC                                                                                                                                                            | OVRB                                      | OVRA       | STRD <sup>(2)</sup> | STRC <sup>(2)</sup> | STRB <sup>(2)</sup> | STRA <sup>(2)</sup> |  |  |

| bit 7            |                                                                                                                                                                 |                                           | •          |                     |                     | •                   | bit 0               |  |  |

|                  |                                                                                                                                                                 |                                           |            |                     |                     |                     |                     |  |  |

| Legend:          |                                                                                                                                                                 |                                           |            |                     |                     |                     |                     |  |  |

| R = Readable     |                                                                                                                                                                 | W = Writable                              |            |                     | nented bit, read    |                     |                     |  |  |

| u = Bit is unch  | anged                                                                                                                                                           | x = Bit is unkr                           | nown       | -n/n = Value a      | at POR and BO       | R/Value at all o    | ther Resets         |  |  |

| '1' = Bit is set |                                                                                                                                                                 | '0' = Bit is clea                         | ared       | q = Value dep       | pends on condit     | ion                 |                     |  |  |

|                  |                                                                                                                                                                 |                                           |            |                     |                     |                     |                     |  |  |

| bit 7            |                                                                                                                                                                 | ing Data D bit                            |            |                     |                     |                     |                     |  |  |

| bit 6            | OVRC: Steer                                                                                                                                                     | ing Data C bit                            |            |                     |                     |                     |                     |  |  |

| bit 5            | OVRB: Steer                                                                                                                                                     | ing Data B bit                            |            |                     |                     |                     |                     |  |  |

| bit 4            | OVRA: Steer                                                                                                                                                     | OVRA: Steering Data A bit                 |            |                     |                     |                     |                     |  |  |

| bit 3            | STRD: Steeri                                                                                                                                                    | TRD: Steering Enable D bit <sup>(2)</sup> |            |                     |                     |                     |                     |  |  |

|                  |                                                                                                                                                                 | output has the output is assig            |            |                     | polarity control    | from POLD bit       |                     |  |  |

| bit 2            | STRC: Steering Enable C bit <sup>(2)</sup>                                                                                                                      |                                           |            |                     |                     |                     |                     |  |  |

|                  | <ul> <li>1 = CWG1C output has the CWG1_data waveform with polarity control from POLC bit</li> <li>0 = CWG1C output is assigned the value of OVRC bit</li> </ul> |                                           |            |                     |                     |                     |                     |  |  |

| bit 1            | STRB: Steeri                                                                                                                                                    | ng Enable B bi                            | t(2)       |                     |                     |                     |                     |  |  |

|                  | <ul> <li>1 = CWG1B output has the CWG1_data waveform with polarity control from POLB bit</li> <li>0 = CWG1B output is assigned the value of OVRB bit</li> </ul> |                                           |            |                     |                     |                     |                     |  |  |

| bit 0            | STRA: Steeri                                                                                                                                                    | ng Enable A bi                            | t(2)       |                     |                     |                     |                     |  |  |

|                  | 1 = CWG1A                                                                                                                                                       |                                           | CWG1_data  |                     | polarity control    | from POLA bit       |                     |  |  |

| Note 1: Th       | e bits in this re                                                                                                                                               | gister apply onl                          | y when MOD | E<2:0> = 00x.       |                     |                     |                     |  |  |

### REGISTER 30-7: CWG1STR: CWG1 STEERING CONTROL REGISTER<sup>(1)</sup>

**2:** This bit is effectively double-buffered when MODE<2:0> = 001.

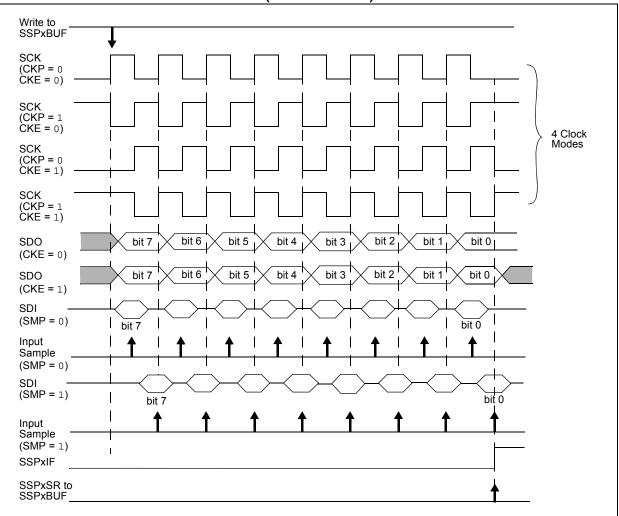

#### 32.2.3 SPI MASTER MODE

The master can initiate the data transfer at any time because it controls the SCK line. The master determines when the slave (Processor 2, Figure 32-5) is to broadcast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPxBUF register is written to. If the SPI is only going to receive, the SDO output could be disabled (programmed as an input). The SSPxSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPxBUF register as if a normal received byte (interrupts and Status bits appropriately set). The clock polarity is selected by appropriately programming the CKP bit of the SSPxCON1 register and the CKE bit of the SSPxSTAT register. This then, would give waveforms for SPI communication as shown in Figure 32-6, Figure 32-8, Figure 32-9 and Figure 32-10, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 \* Tcy)

- Fosc/64 (or 16 \* Tcy)

- Timer2 output/2

- Fosc/(4 \* (SSPxADD + 1))

Figure 32-6 shows the waveforms for Master mode.

When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPxBUF is loaded with the received data is shown.

FIGURE 32-6: SPI MODE WAVEFORM (MASTER MODE)

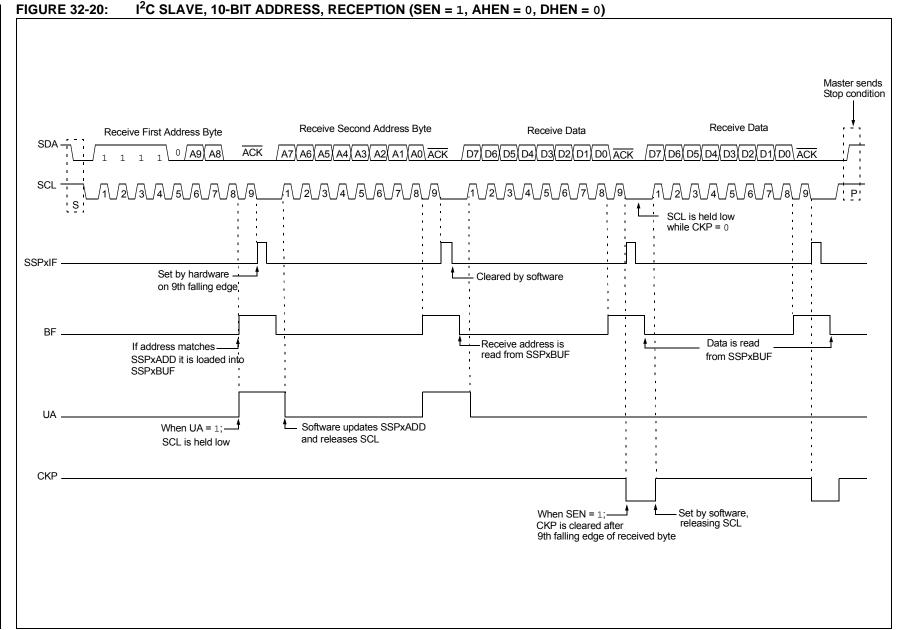

### **FIGURE 32-20:**

PIC16(L)F15354/55

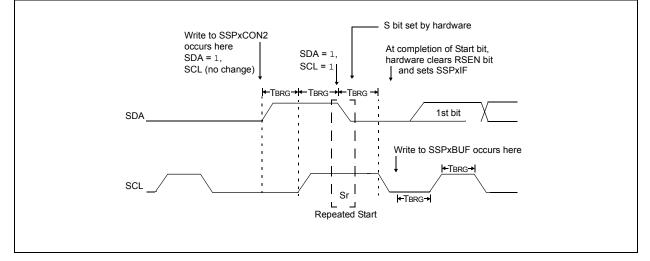

## 32.6.5 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition (Figure 32-27) occurs when the RSEN bit of the SSPxCON2 register is programmed high and the master state machine is no longer active. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. SCL is asserted low. Following this, the RSEN bit of the SSPxCON2 register will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit of the SSPxSTAT register will be set. The SSPxIF bit will not be set until the Baud Rate Generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

#### FIGURE 32-27: REPEATED START CONDITION WAVEFORM

| MOVIW            | Move INDFn to W                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVIW ++FSRn<br>[ <i>label</i> ] MOVIWFSRn<br>[ <i>label</i> ] MOVIW FSRn++<br>[ <i>label</i> ] MOVIW FSRn<br>[ <i>label</i> ] MOVIW k[FSRn]                                                                                                                                                                                                                                                                                           |

| Operands:        | n ∈ [0,1]<br>mm ∈ [00,01, 10, 11]<br>-32 ≤ k ≤ 31                                                                                                                                                                                                                                                                                                                                                                                                       |

| Operation:       | $\begin{split} &\text{INDFn} \rightarrow W \\ &\text{Effective address is determined by} \\ &\text{•} \ &\text{FSR + 1 (preincrement)} \\ &\text{•} \ &\text{FSR - 1 (predecrement)} \\ &\text{•} \ &\text{FSR + k (relative offset)} \\ &\text{After the Move, the FSR value will be} \\ &\text{either:} \\ &\text{•} \ &\text{FSR + 1 (all increments)} \\ &\text{•} \ &\text{FSR - 1 (all decrements)} \\ &\text{•} \ &\text{Unchanged} \end{split}$ |

| Status Affected: | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

**Note:** The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h -FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap-around.

#### MOVLB Move literal to BSR

| Syntax:          | [ label ] MOVLB k                                                    |

|------------------|----------------------------------------------------------------------|

| Operands:        | $0 \le k \le$                                                        |

| Operation:       | $k \rightarrow BSR$                                                  |

| Status Affected: | None                                                                 |

| Description:     | The 6-bit literal 'k' is loaded into the Bank Select Register (BSR). |

| MOVLP            | Move literal to PCLATH                                                                         |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLP k                                                                       |  |  |  |  |

| Operands:        | $0 \le k \le 127$                                                                              |  |  |  |  |

| Operation:       | $k \rightarrow PCLATH$                                                                         |  |  |  |  |

| Status Affected: | None                                                                                           |  |  |  |  |

| Description:     | The 7-bit literal 'k' is loaded into the PCLATH register.                                      |  |  |  |  |

| MOVLW            | Move literal to W                                                                              |  |  |  |  |

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                       |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                            |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                            |  |  |  |  |

| Status Affected: | None                                                                                           |  |  |  |  |

| Description:     | The 8-bit literal 'k' is loaded into W reg-<br>ister. The "don't cares" will assemble as '0's. |  |  |  |  |

| Words:           | 1                                                                                              |  |  |  |  |

| Cycles:          | 1                                                                                              |  |  |  |  |

| Example:         | MOVLW 0x5A                                                                                     |  |  |  |  |

|                  | After Instruction<br>W = 0x5A                                                                  |  |  |  |  |

| MOVWF            | Move W to f                                                                                    |  |  |  |  |

| Syntax:          | [ <i>label</i> ] MOVWF f                                                                       |  |  |  |  |

| Operands:        | $0 \leq f \leq 127$                                                                            |  |  |  |  |

| Operation:       | $(W) \to (f)$                                                                                  |  |  |  |  |

| Status Affected: | None                                                                                           |  |  |  |  |

| Description:     | Move data from W register to register 'f'.                                                     |  |  |  |  |

| Words:           | 1                                                                                              |  |  |  |  |

| Cycles:          | 1                                                                                              |  |  |  |  |

| Example:         | MOVWF LATA                                                                                     |  |  |  |  |

|                  | Before Instruction<br>LATA = 0xFF                                                              |  |  |  |  |

|                  | W = 0x4F                                                                                       |  |  |  |  |

W = 0x4F After Instruction LATA = 0x4F W = 0x4F

### 37.2 Standard Operating Conditions

| 37.2 Standard Operating Conditions                               | $\wedge$                  |

|------------------------------------------------------------------|---------------------------|

| The standard operating conditions for any device are defined as: | $\langle \rangle$         |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$             |                           |

| VDD — Operating Supply Voltage <sup>(1)</sup>                    |                           |

| PIC16LF15354/55                                                  |                           |

| VDDMIN (Fosc $\leq$ 16 MHz)                                      |                           |

| VDDMIN (Fosc $\leq$ 32 MHz)                                      |                           |

| VDDMAX                                                           | +3.6V                     |

| PIC16F15354/55                                                   | $\sim$                    |

| VDDMIN (Fosc $\leq$ 16 MHz)                                      | +2.3V                     |

| VDDMIN (Fosc $\leq$ 32 MHz)                                      |                           |

| VDDMAX                                                           |                           |

| TA — Operating Ambient Temperature Range                         | $\langle \rangle \rangle$ |

| Industrial Temperature                                           |                           |

| TA_MIN                                                           | -40°C                     |

| Та_мах                                                           |                           |

| Extended Temperature                                             | $\searrow$                |

|                                                                  | 40°C                      |

| Та_мах                                                           | ∕<br>+125°C               |

| Note 1: See Parameter Supply Voltage, DS Characteristics: Suppl  | y Voltage.                |

#### **TABLE 37-6:** THERMAL CHARACTERISTICS

| Standar       | Standard Operating Conditions (unless otherwise stated) |                                        |              |       |                                                                                |  |  |

|---------------|---------------------------------------------------------|----------------------------------------|--------------|-------|--------------------------------------------------------------------------------|--|--|

| Param.<br>No. | Sym.                                                    | Characteristic                         | Тур.         | Units | Conditions                                                                     |  |  |

| TH01          | θJA                                                     | Thermal Resistance Junction to Ambient | 60           | °C/W  | 28-pin SPDIP package                                                           |  |  |

|               |                                                         |                                        | 80           | °C/W  | 28-pin SO/C package                                                            |  |  |

|               |                                                         |                                        | 90           | °C/W  | 28-pin SSOP pa¢kage                                                            |  |  |

|               |                                                         |                                        | 48           | °C/W  | 28-pin UQFN 4x4mm package                                                      |  |  |

| TH02          | θJC                                                     | Thermal Resistance Junction to Case    | 31.4         | °C/W  | 28-pin SPQIP package                                                           |  |  |

|               |                                                         |                                        | 24           | °C/W  | 28-pin SOIC package                                                            |  |  |

|               |                                                         |                                        | 24           | °C/W  | 28-pin-SSOP package                                                            |  |  |

|               |                                                         |                                        | 12           | °C/W  | 28-pin, UQFN 4x4mm package                                                     |  |  |

| TH03          | Тјмах                                                   | Maximum Junction Temperature           | 150          | °C /  |                                                                                |  |  |

| TH04          | PD                                                      | Power Dissipation                      | _            | ∕ w   | RD = PINTERNAL + PI/O                                                          |  |  |

| TH05          | PINTERNAL                                               | Internal Power Dissipation             | _            | W     | PINTERNAL = IDD x VDD <sup>(1)</sup>                                           |  |  |

| TH06          | Pı/o                                                    | I/O Power Dissipation                  | 7            | W \   | $PI/O \neq \Sigma$ (IOL * VOL) + $\Sigma$ (IOH * (VDD - VOH))                  |  |  |

| TH07          | Pder                                                    | Derated Power                          | $\leftarrow$ | Ŵ     | P <sub>DER</sub> = PDmax (T <sub>J</sub> - T <sub>A</sub> )/θja <sup>(2)</sup> |  |  |

Note 1: IDD is current to run the chip alone without driving any load on the output pins.

2: TA = Ambient Temperature, TJ = Junction Temperature

© 2016 Microchip Technology Inc.

#### TABLE 37-18: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

|               | rd Operating ( | •                         | nless otherwis<br>≤ +125°C             | e stated)                     |                            |                     |                               |       |                        |

|---------------|----------------|---------------------------|----------------------------------------|-------------------------------|----------------------------|---------------------|-------------------------------|-------|------------------------|

| Param.<br>No. | Sym.           |                           | Characteristic                         |                               | Min.                       | Тур†                | Max.                          | Units | Conditions             |

| 40*           | Тт0Н           | T0CKI High F              | Pulse Width                            | No Prescaler                  | 0.5 Tcy + 20               | _                   | _                             | ns    |                        |

|               |                |                           |                                        | With Prescaler                | 10                         | _                   | _                             | ns    | $\frown$               |

| 41*           | TT0L           | T0CKI Low F               | ulse Width                             | No Prescaler                  | 0.5 Tcy + 20               | _                   | _                             | /ns / |                        |

|               |                |                           |                                        | With Prescaler                | 10                         | _                   | _                             | ns    |                        |

| 42*           | TT0P           | T0CKI Period              | ł                                      |                               | Greater of:                | _                   | _                             | ns    | N = prescale value     |

|               |                |                           |                                        |                               |                            |                     | $\bigwedge$                   | /     |                        |

| 45*           | T⊤1H           | T1CKI High                | Synchronous, N                         | No Prescaler                  | 0.5 Tcy + 20               | —                   | 1-1                           | ns    | $\searrow$             |

|               |                | Time                      | Synchronous, v                         | vith Prescaler                | 15                         | —                   | +/                            | / ns  | $\checkmark$           |

|               |                |                           | Asynchronous                           |                               | 30                         | $\overline{}$       |                               | ns    |                        |

| 46*           | TT1L           | T1CKI Low<br>Time         | Synchronous, N                         | No Prescaler                  | 0.5 Tcy + 20               | $\langle - \rangle$ | $\overline{)} - \overline{)}$ | \ns   |                        |

|               |                |                           | Synchronous, with Prescaler            |                               | 15                         |                     |                               | ns    |                        |

|               |                |                           | Asynchronous                           |                               | 30 <                       | 1                   | Z                             | ns    |                        |

| 47*           | TT1P           | T1CKI Input               | Synchronous                            |                               | Greater of.                | 1                   |                               | ns    | N = prescale value     |

|               |                | Period                    |                                        |                               | 30 or <u>TCX + 40</u><br>N |                     | >                             |       |                        |

|               |                |                           | Asynchronous                           | /                             | 60                         | $\langle - \rangle$ |                               | ns    |                        |

| 48            | F⊤1            | -                         | scillator Input Fr<br>abled by setting | equency Range<br>bit T1OSCEN) | 32.4                       | 32.768              | 33.1                          | kHz   |                        |

| 49*           | TCKEZTMR1      | Delay from E<br>Increment | xternal Clock Ec                       | lge to Timer                  | 2 Vosc                     | _                   | 7 Tosc                        | _     | Timers in Sync<br>mode |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.