Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 25                                                                           |

| Program Memory Size        | 14KB (8K x 14)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 224 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 28-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15355t-i-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0  | Device Overview                                                           |  |

|------|---------------------------------------------------------------------------|--|

| 2.0  | Guidelines for Getting Started with PIC16(L)F15354/55 Microcontrollers    |  |

| 3.0  | Enhanced Mid-Range CPU                                                    |  |

| 4.0  | Memory Organization                                                       |  |

| 5.0  | Device Configuration                                                      |  |

| 6.0  | Device Information Area                                                   |  |

| 7.0  | Device Configuration Information                                          |  |

| 8.0  | Resets                                                                    |  |

| 9.0  | Oscillator Module (with Fail-Safe Clock Monitor)                          |  |

| 10.0 | Interrupts                                                                |  |

| 11.0 | Power-Saving Operation Modes                                              |  |

| 12.0 | Windowed Watchdog Timer (WWDT)                                            |  |

|      | Nonvolatile Memory (NVM) Control                                          |  |

| 14.0 | I/O Ports                                                                 |  |

| 15.0 | Peripheral Pin Select (PPS) Module                                        |  |

| 16.0 | Peripheral Module Disable                                                 |  |

| 17.0 | Interrupt-On-Change                                                       |  |

| 18.0 | Fixed Voltage Reference (FVR)                                             |  |

| 19.0 | Temperature Indicator Module                                              |  |

| 20.0 | Analog-to-Digital Converter (ADC) Module                                  |  |

| 21.0 | 5-Bit Digital-to-Analog Converter (DAC1) Module                           |  |

|      | Numerically Controlled Oscillator (NCO) Module                            |  |

|      | Comparator Module                                                         |  |

|      | Zero-Cross Detection (ZCD) Module                                         |  |

|      | Timer0 Module                                                             |  |

|      | Timer1 Module with Gate Control                                           |  |

| 27.0 | Timer2 Module With Hardware Limit Timer (HLT)                             |  |

| 28.0 |                                                                           |  |

|      | Pulse-Width Modulation (PWM)                                              |  |

| 30.0 | Complementary Waveform Generator (CWG) Module                             |  |

| 31.0 | Configurable Logic Cell (CLC)                                             |  |

|      | Master Synchronous Serial Port (MSSP) Modules                             |  |

|      | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) |  |

|      | Reference Clock Output Module                                             |  |

| 35.0 |                                                                           |  |

| 36.0 |                                                                           |  |

| 37.0 |                                                                           |  |

| 38.0 |                                                                           |  |

| 39.0 | Development Support                                                       |  |

| 40.0 | Packaging Information                                                     |  |

## TABLE 4-5:PIC16(L)F15354/55 MEMORY MAP, BANKS 8-15

|      | BANK 8                  |      | BANK 9                  |      | BANK 10                 |      | BANK 11                 |      | BANK 12                 |      | BANK 13       |      | BANK 14       |      | BANK 15       |

|------|-------------------------|------|-------------------------|------|-------------------------|------|-------------------------|------|-------------------------|------|---------------|------|---------------|------|---------------|

| 400h |                         | 480h |                         | 500h |                         | 580h |                         | 600h |                         | 680h |               | 700h |               | 780h |               |

|      | Core Register           |      | Core Register |      | Core Register |      | Core Register |

|      | (Table 4-3)             |      | (Table 4-3)   |      | (Table 4-3)   |      | (Table 4-3)   |

| 40Bh |                         | 48Bh |                         | 50Bh |                         | 58Bh |                         | 60Bh |                         | 68Bh |               | 70Bh |               | 78Bh |               |

| 40Ch | —                       | 48Ch | —                       | 50Ch | —                       | 58Ch | NCO1ACCL                | 60Ch | CWG1CLK                 | 68Ch | —             | 70Ch | PIR0          | 78Ch |               |

| 40Dh | _                       | 48Dh | _                       | 50Dh | _                       | 58Dh | NCO1ACCH                | 60Dh | CWG1DAT                 | 68Dh |               | 70Dh | PIR1          | 78Dh |               |

| 40Eh | —                       | 48Eh | _                       | 50Eh | —                       | 58Eh | NCO1ACCU                | 60Eh | CWG1DBR                 | 68Eh | _             | 70Eh | PIR2          | 78Eh |               |

| 40Fh | —                       | 48Fh | _                       | 50Fh | —                       | 58Fh | NCO1INCL                | 60Fh | CWG1DBF                 | 68Fh | _             | 70Fh | PIR3          | 78Fh |               |

| 410h | —                       | 490h | —                       | 510h | —                       | 590h | NCO1INCH                | 610h | CWG1CON0                | 690h | _             | 710h | PIR4          | 790h | _             |

| 411h | —                       | 491h | _                       | 511h | —                       | 591h | NCO1INCU                | 611h | CWG1CON1                | 691h | _             | 711h | PIR5          | 791h | _             |

| 412h | —                       | 492h | —                       | 512h | —                       | 592h | NCO1CON                 | 612h | CWG1AS0                 | 692h | —             | 712h | PIR6          | 792h | _             |

| 413h | —                       | 493h | —                       | 513h | —                       | 593h | NCO1CLK                 | 613h | CWG1AS1                 | 693h | —             | 713h | PIR7          | 793h | —             |

| 414h | —                       | 494h | —                       | 514h | —                       | 594h | —                       | 614h | CWG1STR                 | 694h | _             | 714h | _             | 794h | —             |

| 415h | —                       | 495h | —                       | 515h | —                       | 595h | _                       | 615h | —                       | 695h | _             | 715h | —             | 795h | _             |

| 416h | —                       | 496h | _                       | 516h | —                       | 596h | _                       | 616h | —                       | 696h | _             | 716h | PIE0          | 796h | PMD0          |

| 417h | —                       | 497h | _                       | 517h | —                       | 597h | _                       | 617h | —                       | 697h | _             | 717h | PIE1          | 797h | PMD1          |

| 418h | _                       | 498h | _                       | 518h | _                       | 598h | _                       | 618h | _                       | 698h | —             | 718h | PIE2          | 798h | PMD2          |

| 419h | _                       | 499h | _                       | 519h | _                       | 599h | _                       | 619h | _                       | 699h | —             | 719h | PIE3          | 799h | PMD3          |

| 41Ah | —                       | 49Ah | _                       | 51Ah | —                       | 59Ah |                         | 61Ah | —                       | 69Ah | _             | 71Ah | PIE4          | 79Ah | PMD4          |

| 41Bh | _                       | 49Bh | _                       | 51Bh | _                       | 59Bh | _                       | 61Bh | _                       | 69Bh |               | 71Bh | PIE5          | 79Bh | PMD5          |

| 41Ch |                         | 49Ch | _                       | 51Ch | _                       | 59Ch | TMR0                    | 61Ch | _                       | 69Ch | _             | 71Ch | PIE6          | 79Ch |               |

| 41Dh |                         | 49Dh | _                       | 51Dh | _                       | 59Dh | PR0                     | 61Dh | _                       | 69Dh | _             | 71Dh | PIE7          | 79Dh |               |

| 41Eh | _                       | 49Eh | _                       | 51Eh | _                       | 59Eh | TMR0CON0                | 61Eh | _                       | 69Eh | _             | 71Eh | —             | 79Eh |               |

| 41Fh | —                       | 49Fh | —                       | 51Fh | —                       | 59Fh | TMR0CON1                | 61Fh | —                       | 69Fh | —             | 71Fh | —             | 79Fh | _             |

| 420h |                         | 4A0h |                         | 520h |                         | 5A0h |                         | 620h |                         | 6A0h |               | 720h |               | 7A0h |               |

|      | General                 |      |               |      |               |      |               |

|      | Purpose                 |      | Unimplemented |      | Unimplemented |      | Unimplemented |

|      | Register                |      | Read as '0'   |      | Read as '0'   |      | Read as '0'   |

|      | 80 Bytes <sup>(2)</sup> |      |               |      |               |      |               |

| 46Fh |                         | 4EFh |                         | 56Fh |                         | 5EFh |                         | 66Fh |                         | 6EFh |               | 76Fh |               | 7EFh |               |

| 470h | Common RAM              | 4F0h | Common RAM              | 570h | Common RAM              | 5F0h | Common RAM              | 670h | Common RAM              | 6F0h | Common RAM    | 770h | Common RAM    | 7F0h | Common RAM    |

|      | Accesses                |      | Accesses      |      | Accesses      |      | Accesses      |

| 47Fh | 70h-7Fh                 | 4FFh | 70h-7Fh                 | 57Fh | 70h-7Fh                 | 5FFh | 70h-7Fh                 | 67Fh | 70h-7Fh                 | 6FFh | 70h-7Fh       | 77Fh | 70h-7Fh       | 7FFh | 70h-7Fh       |

Note 1: Unimplemented locations read as '0'.

2: Present only in PIC16(L)F15355.

### TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

| Address      | Name                                            | Bit 7                 | Bit 6             | Bit 5            | Bit 4              | Bit 3            | Bit 2            | Bit 1            | Bit 0       | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |  |  |  |

|--------------|-------------------------------------------------|-----------------------|-------------------|------------------|--------------------|------------------|------------------|------------------|-------------|-----------------------|----------------------------|--|--|--|

| Bank 13      | ank 13                                          |                       |                   |                  |                    |                  |                  |                  |             |                       |                            |  |  |  |

|              | CPU CORE REGISTERS; see Table 4-3 for specifics |                       |                   |                  |                    |                  |                  |                  |             |                       |                            |  |  |  |

| 68Ch<br>69Fh | Unimplemented — — —                             |                       |                   |                  |                    |                  |                  |                  |             |                       |                            |  |  |  |

| Legend:      | x = unknown, u =                                | = unchanged, ਕੁ = dep | ends on condition | , - = unimplemen | ited, read as '0', | r = reserved. Sh | aded locations u | inimplemented, r | ead as '0'. | •                     |                            |  |  |  |

#### 10.3 Interrupts During Sleep

Interrupts can be used to wake from Sleep. To wake from Sleep, the peripheral must be able to operate without the system clock. The interrupt source must have the appropriate Interrupt Enable bit(s) set prior to entering Sleep.

On waking from Sleep, if the GIE bit is also set, the processor will branch to the interrupt vector. Otherwise, the processor will continue executing instructions after the SLEEP instruction. The instruction directly after the SLEEP instruction will always be executed before branching to the ISR. Refer to **Section 11.0 "Power-Saving Operation Modes"** for more details.

#### 10.4 INT Pin

The INT pin can be used to generate an asynchronous edge-triggered interrupt. Refer to Figure 10-3. This interrupt is enabled by setting the INTE bit of the PIE0 register. The INTEDG bit of the INTCON register determines on which edge the interrupt will occur. When the INTEDG bit is set, the rising edge will cause the interrupt. When the INTEDG bit is clear, the falling edge will cause the interrupt. The INTF bit of the PIR0 register will be set when a valid edge appears on the INT pin. If the GIE and INTE bits are also set, the processor will redirect program execution to the interrupt vector.

#### 10.5 Automatic Context Saving

Upon entering an interrupt, the return PC address is saved on the stack. Additionally, the following registers are automatically saved in the shadow registers:

- W register

- STATUS register (except for TO and PD)

- BSR register

- · FSR registers

- PCLATH register

Upon exiting the Interrupt Service Routine, these registers are automatically restored. Any modifications to these registers during the ISR will be lost. If modifications to any of these registers are desired, the corresponding shadow register should be modified and the value will be restored when exiting the ISR. The shadow registers are available in Bank 31 and are readable and writable. Depending on the user's application, other registers may also need to be saved.

| U-0              | U-0               | R/W-0/0                        | R/W-0/0       | U-0            | U-0              | U-0              | R/W-0/0     |

|------------------|-------------------|--------------------------------|---------------|----------------|------------------|------------------|-------------|

| —                | —                 | TMR0IE                         | IOCIE         | —              | -                | —                | INTE        |

| bit 7            |                   |                                |               |                |                  |                  | bit 0       |

|                  |                   |                                |               |                |                  |                  |             |

| Legend:          |                   |                                |               |                |                  |                  |             |

| R = Readable     | bit               | W = Writable                   | bit           | U = Unimpler   | mented bit, read | as '0'           |             |

| u = Bit is unch  | anged             | x = Bit is unkr                | nown          | -n/n = Value a | at POR and BOF   | R/Value at all o | ther Resets |

| '1' = Bit is set |                   | '0' = Bit is clea              | ared          | HS = Hardwa    | are set          |                  |             |

|                  |                   |                                |               |                |                  |                  |             |

| bit 7-6          | Unimplemen        | ted: Read as '                 | כי            |                |                  |                  |             |

| bit 5            | TMROIE: Time      | er0 Overflow Ir                | terrupt Enabl | e bit          |                  |                  |             |

|                  |                   | the Timer0 int                 |               |                |                  |                  |             |

|                  |                   | the Timer0 inf                 |               |                |                  |                  |             |

| bit 4            |                   | pt-on-Change<br>the IOC change | •             | ble bit        |                  |                  |             |

|                  |                   | the IOC changes the IOC chan   |               |                |                  |                  |             |

| bit 3-1          |                   | ted: Read as '                 |               |                |                  |                  |             |

| bit 0            | -                 | ternal Interrupt               |               |                |                  |                  |             |

|                  |                   | the INT extern                 | •             |                |                  |                  |             |

|                  | 0 = Disables      | s the INT extern               | nal interrupt |                |                  |                  |             |

| Note 1: The      | e External Interr | upt GPIO pin i                 | s selected by | INTPPS (Regi   | ster 15-1).      |                  |             |

## REGISTER 10-2: PIE0: PERIPHERAL INTERRUPT ENABLE REGISTER 0

| Note: | Bit PEIE of the INTCON register must be    |

|-------|--------------------------------------------|

|       | set to enable any peripheral interrupt     |

|       | controlled by PIE1-PIE7. Interrupt sources |

|       | controlled by the PIE0 register do not     |

|       | require PEIE to be set in order to allow   |

|       | interrupt vectoring (when GIE is set).     |

### 14.6 PORTC Registers

#### 14.6.1 DATA REGISTER

PORTC is an 8-bit wide bidirectional port. The corresponding data direction register is TRISC (Register 14-18). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Figure 14-1 shows how to initialize an I/O port.

Reading the PORTC register (Register 14-17) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATC).

The PORT data latch LATC (Register 14-19) holds the output port data, and contains the latest value of a LATC or PORTC write.

#### 14.6.2 DIRECTION CONTROL

The TRISC register (Register 14-18) controls the PORTC pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISC register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

#### 14.6.3 OPEN-DRAIN CONTROL

The ODCONC register (Register 14-22) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONC bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONC bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

| Note: | It is not necessary to set open-drain control when using the pin for I <sup>2</sup> C; the I <sup>2</sup> C |

|-------|-------------------------------------------------------------------------------------------------------------|

|       | module controls the pin and makes the pin open-drain.                                                       |

#### 14.6.4 SLEW RATE CONTROL

The SLRCONC register (Register 14-23) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONC bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONC bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

#### 14.6.5 INPUT THRESHOLD CONTROL

The INLVLC register (Register 14-24) controls the input voltage threshold for each of the available PORTC input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTC register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 37-4 for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

### 14.6.6 ANALOG CONTROL

The ANSELC register (Register 14-20) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELC bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELC bits has no effect on digital output functions. A pin with TRIS clear and ANSELC set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

#### 14.6.7 WEAK PULL-UP CONTROL

The WPUC register (Register 14-21) controls the individual weak pull-ups for each port pin.

#### 14.6.8 PORTC FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after Reset. Other output functions are selected with the peripheral pin select logic. See **Section 15.0 "Peripheral Pin Select (PPS) Module"** for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. Digital output functions may continue to control the pin when it is in Analog mode.

Note: The ANSELC bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

#### 14.8 PORTE Registers

#### 14.8.1 DATA REGISTER

PORTE is a single bit wide port. The corresponding data direction register is TRISE (Register 14-25). Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., disable the output driver). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Figure 14-1 shows how to initialize PORTE.

Reading the PORTE register (Register 14-25) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATE).

#### 14.8.2 DIRECTION CONTROL

The TRISE register (Register 14-26) controls the PORTE pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISE register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

| Note: | The TRISE3 bit is a read-only bit and it |

|-------|------------------------------------------|

|       | always reads a '1'.                      |

#### 14.8.3 INPUT THRESHOLD CONTROL

The INLVLE register (Register 14-28) controls the input voltage threshold for each of the available PORTE input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTE register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 37-4 for more information on threshold levels.

| Note: | Changing the input threshold selection<br>should be performed while all peripheral<br>modules are disabled. Changing the<br>threshold level during the time a module is |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | active may inadvertently generate a<br>transition associated with an input pin,<br>regardless of the actual voltage level on<br>that pin.                               |

#### 14.8.4 WEAK PULL-UP CONTROL

The WPUE register (Register 14-27) controls the individual weak pull-ups for each port pin.

#### 14.8.5 PORTE FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after Reset. Other output functions are selected with the peripheral pin select logic. See **Section 15.0 "Peripheral Pin Select (PPS) Module"** for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. Digital output functions may continue to control the pin when it is in Analog mode.

# PIC16(L)F15354/55

| REGISTER 1                                           | 6-5: PMD4:                                                                                                                                                                                  | PMD CONT                                                                                                                                                                                                                                                                                                             | ROL REGIST                                    | ER 4            |                  |                |              |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------|------------------|----------------|--------------|

| R/W-0/0                                              | R/W-0/0                                                                                                                                                                                     | R/W-0/0                                                                                                                                                                                                                                                                                                              | R/W-0/0                                       | U-0             | U-0              | U-0            | R/W-0/0      |

| UART2MD                                              | UART1MD                                                                                                                                                                                     | MSSP2MD                                                                                                                                                                                                                                                                                                              | MSSP1MD                                       | —               | —                | _              | CWG1MD       |

| bit 7                                                |                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                      |                                               |                 |                  |                | bit 0        |

|                                                      |                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                      |                                               |                 |                  |                |              |

| Legend:                                              |                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                      |                                               |                 |                  |                |              |

| R = Readable                                         | bit                                                                                                                                                                                         | W = Writable I                                                                                                                                                                                                                                                                                                       | oit                                           | U = Unimplem    | ented bit, read  | as '0'         |              |

| u = Bit is unch                                      | nanged                                                                                                                                                                                      | x = Bit is unkn                                                                                                                                                                                                                                                                                                      | own                                           | -n/n = Value at | t POR and BOF    | R/Value at all | other Resets |

| '1' = Bit is set                                     |                                                                                                                                                                                             | '0' = Bit is clea                                                                                                                                                                                                                                                                                                    | ared                                          | q = Value depe  | ends on conditio | on             |              |

| bit 7<br>bit 6<br>bit 5<br>bit 4<br>bit 3-1<br>bit 0 | 1 = EUSART2<br>0 = EUSART2<br>UART1MD: D<br>1 = EUSART2<br>0 = EUSART2<br>MSSP2MD: D<br>1 = MSSP2 m<br>0 = MSSP2 m<br>MSSP1MD: D<br>1 = MSSP1 m<br>0 = MSSP1 m<br>0 = MSSP1 m<br>1 = CWG1 m | isable EUSAR <sup>2</sup><br>2 module disab<br>2 module enable<br>2 module enable<br>isable EUSAR <sup>2</sup><br>1 module disable<br>1 module disable<br>isable MSSP2<br>module enabled<br>isable MSSP1<br>module disabled<br>nodule enabled<br>ted: Read as 'C<br>sable CWG1 bi<br>odule disabled<br>odule enabled | led<br>ed<br>F1 bit<br>led<br>bit<br>l<br>bit |                 |                  |                |              |

## 18.3 Register Definitions: FVR Control

#### REGISTER 18-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0/0         | R-q/q                                                                 | R/W-0/0                                                                                                                               | R/W-0/0              | R/W-0/0                    | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |  |  |

|-----------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------------|------------------|------------------|--------------|--|--|--|--|

| FVREN           | FVRRDY <sup>(1)</sup>                                                 | TSEN <sup>(3)</sup>                                                                                                                   | TSRNG <sup>(3)</sup> | CDAF                       | VR<1:0>          | ADFVI            | R<1:0>       |  |  |  |  |

| bit 7           |                                                                       |                                                                                                                                       |                      |                            |                  |                  | bit          |  |  |  |  |

|                 |                                                                       |                                                                                                                                       |                      |                            |                  |                  |              |  |  |  |  |

| Legend:         |                                                                       |                                                                                                                                       |                      |                            |                  |                  |              |  |  |  |  |

| R = Readabl     | e bit                                                                 | W = Writable                                                                                                                          | bit                  |                            | mented bit, read |                  |              |  |  |  |  |

| u = Bit is und  | changed                                                               | x = Bit is unk                                                                                                                        | nown                 | -n/n = Value               | at POR and BO    | R/Value at all c | other Resets |  |  |  |  |

| '1' = Bit is se | t                                                                     | '0' = Bit is cle                                                                                                                      | ared                 | q = Value de               | pends on condit  | tion             |              |  |  |  |  |

| bit 7           |                                                                       | d Voltage Refe                                                                                                                        |                      | bit                        |                  |                  |              |  |  |  |  |

|                 |                                                                       | Itage Referenc<br>Itage Referenc                                                                                                      |                      |                            |                  |                  |              |  |  |  |  |

| bit 6           | FVRRDY: Fix                                                           | ed Voltage Re                                                                                                                         | ference Ready        | / Flag bit <sup>(1)</sup>  |                  |                  |              |  |  |  |  |

|                 |                                                                       | Itage Reference<br>Itage Reference                                                                                                    |                      |                            | enabled          |                  |              |  |  |  |  |

| bit 5           |                                                                       | erature Indicate                                                                                                                      | -                    | -                          |                  |                  |              |  |  |  |  |

|                 |                                                                       | ture Indicator i                                                                                                                      |                      |                            |                  |                  |              |  |  |  |  |

|                 | •                                                                     | ture Indicator i                                                                                                                      |                      | <i>(</i> -)                |                  |                  |              |  |  |  |  |

| bit 4           |                                                                       | perature Indica                                                                                                                       |                      | lection bit <sup>(3)</sup> |                  |                  |              |  |  |  |  |

|                 | 1 = Vout = Vdd - 4Vt (High Range)<br>0 = Vout = Vdd - 2Vt (Low Range) |                                                                                                                                       |                      |                            |                  |                  |              |  |  |  |  |

| bit 3-2         |                                                                       | •                                                                                                                                     | •                    | Gain Selection             | bits             |                  |              |  |  |  |  |

|                 | 11 = Compar                                                           | <b>CDAFVR&lt;1:0&gt;:</b> Comparator FVR Buffer Gain Selection bits<br>11 = Comparator FVR Buffer Gain is 4x, (4.096V) <sup>(2)</sup> |                      |                            |                  |                  |              |  |  |  |  |

|                 |                                                                       | ator FVR Buffe                                                                                                                        |                      | ,                          |                  |                  |              |  |  |  |  |

|                 |                                                                       | 01 = Comparator FVR Buffer Gain is 1x, (1.024V)<br>00 = Comparator FVR Buffer is off                                                  |                      |                            |                  |                  |              |  |  |  |  |

| bit 1-0         |                                                                       | ADC FVR Build                                                                                                                         |                      | ction bit                  |                  |                  |              |  |  |  |  |

| DIL 1-0         |                                                                       | 'R Buffer Gain                                                                                                                        |                      |                            |                  |                  |              |  |  |  |  |

|                 |                                                                       | 'R Buffer Gain                                                                                                                        |                      |                            |                  |                  |              |  |  |  |  |

|                 |                                                                       | 'R Buffer Gain                                                                                                                        | is 1x, (1.024V       | )                          |                  |                  |              |  |  |  |  |

|                 | 00 <b>= ADC FV</b>                                                    | 'R Buffer is off                                                                                                                      |                      |                            |                  |                  |              |  |  |  |  |

| Note 1: F       | VRRDY is always                                                       | s '1' for PIC16                                                                                                                       | (L)F15354/55 (       | devices only.              |                  |                  |              |  |  |  |  |

| 2: Fi           | xed Voltage Refe                                                      | erence output o                                                                                                                       | cannot exceed        | VDD.                       |                  |                  |              |  |  |  |  |

- 2: Fixed Voltage Reference output cannot exceed VDD.

- 3: See Section 19.0 "Temperature Indicator Module" for additional information.

| R/W-0/       | 0 R/W-0/0                                       | R/W-0/0                                                                                                | R/W-0/0                        | U-0            | U-0              | R/W-0/0             | R/W-0/0      |

|--------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------|----------------|------------------|---------------------|--------------|

| ADFN         | 1                                               | ADCS<2:0>                                                                                              |                                | —              | —                | ADPRE               | EF<1:0>      |

| bit 7        |                                                 |                                                                                                        |                                |                |                  |                     | bit          |

| Legend:      |                                                 |                                                                                                        |                                |                |                  |                     |              |

| R = Read     | able bit                                        | W = Writable b                                                                                         | bit                            | U = Unimpler   | mented bit, read | 1 as '0'            |              |

| u = Bit is u | unchanged                                       | x = Bit is unkn                                                                                        | own                            | -n/n = Value a | at POR and BO    | R/Value at all      | other Resets |

| '1' = Bit is | set                                             | '0' = Bit is clea                                                                                      | red                            |                |                  |                     |              |

| bit 7        | 1 = Right<br>loade                              | ustified. Six Least                                                                                    | Significant bi                 |                |                  |                     |              |

| bit 6-4      | 111 = AD<br>110 = Fos<br>101 = Fos<br>100 = Fos | sc/16<br>sc/4<br>CRC (dedicated R<br>sc/32<br>sc/8                                                     | C oscillator)                  | ct bits        |                  |                     |              |

| bit 3-2      | Unimplem                                        | nented: Read as '0                                                                                     | ,                              |                |                  |                     |              |

| bit 1-0      | 11 = VREF<br>10 = VREF<br>01 = Rese             | <b>:1:0&gt;:</b> ADC Positiv<br>+ is connected to i<br>+ is connected to<br>erved<br>+ is connected to | nternal Fixed<br>external VREF | Voltage Refere |                  | dule <sup>(1)</sup> |              |

| Note 1:      | -                                               | the VREF+ pin as<br>tists. See Table 37                                                                |                                |                | erence, be awa   | are that a minin    | num voltage  |

#### REGISTER 20-2: ADCON1: ADC CONTROL REGISTER 1

| U-0                               | U-0 | U-0               | R/W-0/0          | R/W-0/0        | R/W-0/0       | R/W-0/0          | R/W-0/0      |

|-----------------------------------|-----|-------------------|------------------|----------------|---------------|------------------|--------------|

| —                                 | —   | —                 |                  |                | ADAC1         | 「<3:0>           |              |

| bit 7                             |     |                   |                  |                |               |                  | bit 0        |

|                                   |     |                   |                  |                |               |                  |              |

| Legend:                           |     |                   |                  |                |               |                  |              |

| R = Readable bit W = Writable bit |     | U = Unimplen      | nented bit, read | 1 as '0'       |               |                  |              |

| u = Bit is unchanged x = Bit is   |     | x = Bit is unkr   | iown             | -n/n = Value a | at POR and BO | R/Value at all o | other Resets |

| '1' = Bit is set                  |     | '0' = Bit is clea | ared             |                |               |                  |              |

#### REGISTER 20-3: ADACT: A/D AUTO-CONVERSION TRIGGER

bit 7-4 Unimplemented: Read as '0'

bit 3-0 ADACT<3:0>: Auto-Conversion Trigger Selection bits<sup>(1)</sup> (see Table 20-2)

**Note 1:** This is a rising edge sensitive input for all sources.

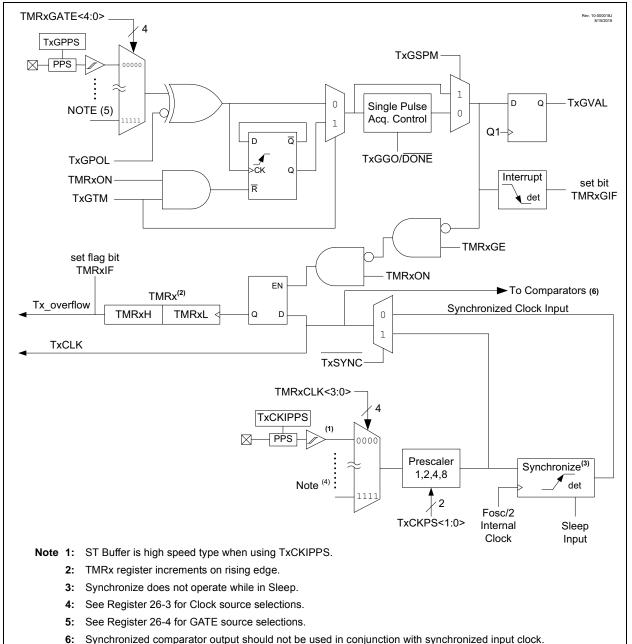

## 26.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is 16-bit timer/counters with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- · Programmable internal or external clock source

- · 2-bit prescaler

- Clock source for optional comparator synchronization

- Multiple Timer1 gate (count enable) sources

- · Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- · Time base for the Capture/Compare function

- Auto-conversion Trigger (with CCP)

- · Selectable Gate Source Polarity

- Gate Toggle mode

- · Gate Single-Pulse mode

- · Gate Value Status

- · Gate Event Interrupt

Figure 26-1 is a block diagram of the Timer1 module.

This device has one instance of Timer1 type modules.

#### FIGURE 26-1: TIMER1 BLOCK DIAGRAM

#### REGISTER 28-1: CCPxCON: CCPx CONTROL REGISTER (CONTINUED)

- bit 3-0 MODE<3:0>: CCPx Mode Select bits<sup>(1)</sup>

- 1111 = PWM mode

- 1110 = Reserved

- 1101 = Reserved

- 1100 = Reserved

- 1011 = Compare mode: output will pulse 0-1-0; Clears TMR1

- 1010 = Compare mode: output will pulse 0-1-0

- 1001 = Compare mode: clear output on compare match

- 1000 = Compare mode: set output on compare match

- 0111 = Capture mode: every 16th rising edge of CCPx input

- 0110 = Capture mode: every 4th rising edge of CCPx input

- 0101 = Capture mode: every rising edge of CCPx input

- 0100 = Capture mode: every falling edge of CCPx input

- 0011 = Capture mode: every edge of CCPx input

- 0010 = Compare mode: toggle output on match

- 0001 = Compare mode: toggle output on match; clear TMR1

- 0000 = Capture/Compare/PWM off (resets CCPx module)

- **Note 1:** All modes will set the CCPxIF bit, and will trigger an ADC conversion if CCPx is selected as the ADC trigger source.

## PIC16(L)F15354/55

#### REGISTER 30-8: CWG1CLK: CWG1 CLOCK SELECTION REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 |

|-------|-----|-----|-----|-----|-----|-----|---------|

| —     | —   |     |     | —   | —   |     | CS      |

| bit 7 |     |     |     |     |     |     | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

#### bit 7-1 Unimplemented: Read as '0'

bit 0

bit 3-0

CS: CWG1 Clock Selection bit

- 1 = HFINTOSC 16 MHz is selected

- 0 = Fosc is selected

#### REGISTER 30-9: CWG1ISM: CWG1 INPUT SELECTION REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|---------|---------|

| —     | —   | —   | —   |         | IS<     | 3:0>    |         |

| bit 7 |     |     |     |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

#### bit 7-4 Unimplemented: Read as '0'

| IS<3:0>: | CWG1 Input Selection bits       |

|----------|---------------------------------|

| 1111 =   | Reserved. No channel connected. |

| 1110 =   | Reserved. No channel connected. |

| 1101 =   | LC4_out.                        |

| 1100 =   | LC3_out.                        |

| 1011 =   | LC2_out.                        |

| 1010 =   | LC1_out                         |

| 1001 =   | Comparator C2 out               |

| 1000 =   | Comparator C1 out.              |

| 0111 =   | NCO1 output.                    |

| 0110 =   | PWM6_out                        |

| 0101 =   | PWM5_out                        |

|          | PWM4_out                        |

| 0011 =   | PWM3_out                        |

| 0010 =   | CCP2_out                        |

| 0001 =   | CCP1_out                        |

| 0000 =   | CWG11CLK                        |

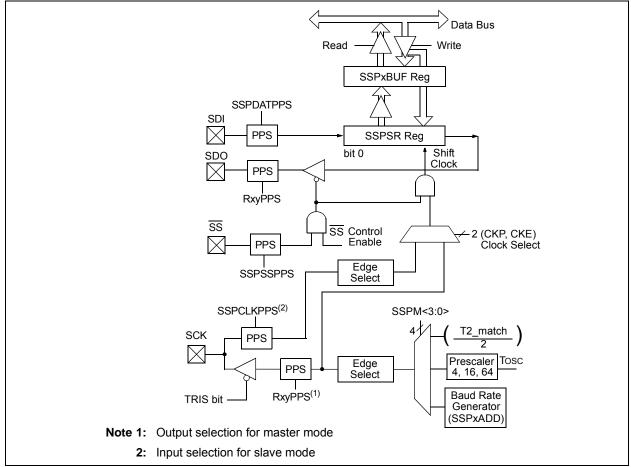

## 32.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULES

### 32.1 MSSP Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

The SPI interface supports the following modes and features:

- Master mode

- Slave mode

- Clock Parity

- Slave Select Synchronization (Slave mode only)

- · Daisy-chain connection of slave devices

Figure 32-1 is a block diagram of the SPI interface module.

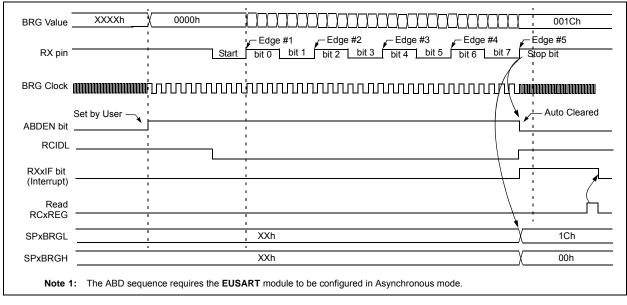

#### 33.3.1 AUTO-BAUD DETECT

The EUSART module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUDxCON register starts the auto-baud calibration sequence. While the ABD sequence takes place, the EUSART state machine is held in Idle. On the first rising edge of the receive line, after the Start bit, the SPxBRG begins counting up using the BRG counter clock as shown in Figure 33-6. The fifth rising edge will occur on the RX pin at the end of the eighth bit period. At that time, an accumulated value totaling the proper BRG period is left in the SPxBRGH, SPxBRGL register pair, the ABDEN bit is automatically cleared and the RXxIF interrupt flag is set. The value in the RCxREG needs to be read to clear the RXxIF interrupt. RCxREG content should be discarded. When calibrating for modes that do not use the SPxBRGH register the user can verify that the SPxBRGL register did not overflow by checking for 00h in the SPxBRGH register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table 33-1. During ABD, both the SPxBRGH and SPxBRGL registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SPxBRGH and SPxBRGL registers are clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

- Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte following the Break character (see Section 33.3.3 "Auto-Wake-up on Break").

- It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible.

- 3: During the auto-baud process, the auto-baud counter starts counting at one. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract 1 from the SPxBRGH:SPxBRGL register pair.

|  | TABLE 33-1: | BRG COUNTER CLOCK RATES |

|--|-------------|-------------------------|

|--|-------------|-------------------------|

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |

|-------|------|-------------------|------------------|

| 0     | 0    | Fosc/64           | Fosc/512         |

| 0     | 1    | Fosc/16           | Fosc/128         |

| 1     | 0    | Fosc/16           | Fosc/128         |

| 1     | 1    | Fosc/4            | Fosc/32          |

**Note:** During the ABD sequence, SPxBRGL and SPxBRGH registers are both used as a 16-bit counter, independent of the BRG16 setting.

#### FIGURE 33-6: AUTOMATIC BAUD RATE CALIBRATION

## 34.0 REFERENCE CLOCK OUTPUT MODULE

The reference clock output module provides the ability to send a clock signal to the clock reference output pin (CLKR).

The reference clock output module has the following features:

- Selectable input clock

- Programmable clock divider

- Selectable duty cycle

## 34.1 CLOCK SOURCE

The reference clock output module has a selectable clock source. The CLKRCLK register (Register 34-2) controls which input is used.

#### 34.1.1 CLOCK SYNCHRONIZATION

Once the reference clock enable (CLKREN) is set, the module is ensured to be glitch-free at start-up.

When the reference clock output is disabled, the output signal will be disabled immediately.

Clock dividers and clock duty cycles can be changed while the module is enabled, but glitches may occur on the output. To avoid possible glitches, clock dividers and clock duty cycles should be changed only when the CLKREN is clear.

#### 34.2 PROGRAMMABLE CLOCK DIVIDER

The module takes the system clock input and divides it based on the value of the CLKRDIV<2:0> bits of the CLKRCON register (Register 34-1).

The following configurations can be made based on the CLKRDIV<2:0> bits:

- Base Fosc value

- Fosc divided by 2

- Fosc divided by 4

- Fosc divided by 8

- Fosc divided by 16

- Fosc divided by 32

- Fosc divided by 64

- Fosc divided by 128

The clock divider values can be changed while the module is enabled; however, in order to prevent glitches on the output, the CLKRDIV<2:0> bits should only be changed when the module is disabled (CLKREN = 0).

## 34.3 SELECTABLE DUTY CYCLE

The CLKRDC<1:0> bits of the CLKRCON register can be used to modify the duty cycle of the output clock. A duty cycle of 25%, 50%, or 75% can be selected for all clock rates, with the exception of the undivided base Fosc value.

The duty cycle can be changed while the module is enabled; however, in order to prevent glitches on the output, the CLKRDC<1:0> bits should only be changed when the module is disabled (CLKREN = 0).

Note: The CLKRDC1 bit is reset to '1'. This makes the default duty cycle 50% and not 0%.

## 34.4 OPERATION IN SLEEP MODE

The reference clock output module clock is based on the system clock. When the device goes to Sleep, the module outputs will remain in their current state. This will have a direct effect on peripherals using the reference clock output as an input signal.

# PIC16(L)F15354/55

| TRIS             | Load TRIS Register with W                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] TRIS f                                                                                                                              |

| Operands:        | $5 \leq f \leq 7$                                                                                                                                    |

| Operation:       | (W) $\rightarrow$ TRIS register 'f'                                                                                                                  |

| Status Affected: | None                                                                                                                                                 |

| Description:     | Move data from W register to TRIS<br>register.<br>When 'f' = 5, TRISA is loaded.<br>When 'f' = 6, TRISB is loaded.<br>When 'f' = 7, TRISC is loaded. |

| XORLW            | Exclusive OR literal with W                                                                                   |

|------------------|---------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] XORLW k                                                                                               |

| Operands:        | $0 \leq k \leq 255$                                                                                           |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                 |

| Status Affected: | Z                                                                                                             |

| Description:     | The contents of the W register are XOR'ed with the 8-bit literal 'k'. The result is placed in the W register. |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] XORWF f,d                                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                               |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |

| Status Affected: | Z                                                                                                                                                                               |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |

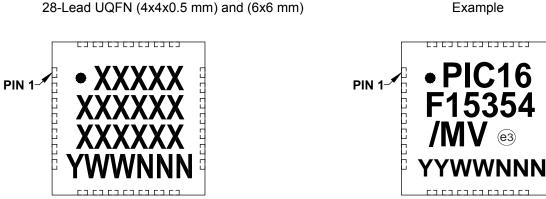

#### Package Marking Information (Continued) 40.1

| Legend | : XXX                                                                                                                                                                                                   | Customer-specific information                                                                                      |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

|        | Y                                                                                                                                                                                                       | Year code (last digit of calendar year)                                                                            |

|        | ΥY                                                                                                                                                                                                      | Year code (last 2 digits of calendar year)                                                                         |

|        | WW                                                                                                                                                                                                      | Week code (week of January 1 is week '01')                                                                         |

|        | NNN Alphanumeric traceability code<br>Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)                                                                                                          |                                                                                                                    |

|        | *                                                                                                                                                                                                       | This package is Pb-free. The Pb-free JEDEC designator ((e3)) can be found on the outer packaging for this package. |

| Note:  | In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information. |                                                                                                                    |

28-Lead UQFN (4x4x0.5 mm) and (6x6 mm)

## THE MICROCHIP WEBSITE

Microchip provides online support via our website at www.microchip.com. This website is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the website contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip website at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the website at: http://www.microchip.com/support