### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 25                                                                           |

| Program Memory Size        | 14KB (8K x 14)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 224 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 28-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15355t-i-ss |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **TABLE 1-2:** PIC16(L)F15354/55 PINOUT DESCRIPTION (CONTINUED)

| Name                                                                       | Function              | Input<br>Type    | Output Type | Description                                                                                       |

|----------------------------------------------------------------------------|-----------------------|------------------|-------------|---------------------------------------------------------------------------------------------------|

| RC1/ANC1/CCP2 <sup>(1)</sup> /IOCC1/SOSCI                                  | RC1                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                              |

|                                                                            | ANC1                  | AN               | _           | ADC Channel C1 input.                                                                             |

|                                                                            | CCP2 <sup>(1)</sup>   | TTL/ST           | CMOS/OD     | CCP2 Capture Input.                                                                               |

|                                                                            | IOCC1                 | TTL/ST           | _           | Interrupt-on-change input.                                                                        |

|                                                                            | SOSCI                 | AN               | _           | 32.768 kHz secondary oscillator crystal driver input.                                             |

| RC2/ANC2/CCP1 <sup>(1)</sup> /IOCC2                                        | RC2                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                              |

|                                                                            | ANC2                  | AN               | _           | ADC Channel C2 input.                                                                             |

|                                                                            | CCP1 <sup>(1)</sup>   | TTL/ST           | CMOS/OD     | CCP1 Capture Input.                                                                               |

|                                                                            | IOCC2                 | TTL/ST           | _           | Interrupt-on-change input.                                                                        |

| RC3/ANC3/SCL1 <sup>(3,4)</sup> /SCK1 <sup>(1)</sup> /T2IN <sup>(1)</sup> / | RC3                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                              |

| IOCC3                                                                      | ANC3                  | AN               | _           | ADC Channel C3 input.                                                                             |

|                                                                            | SCL1 <sup>(3,4)</sup> | l <sup>2</sup> C | OD          | MSSP1 I <sup>2</sup> C input/output.                                                              |

|                                                                            | SCK1 <sup>(1)</sup>   | TTL/ST           | CMOS/OD     | MSSP1 SPI clock input/output (default input location, SCK? is a PPS remappable input and output). |

|                                                                            | T2IN <sup>(1)</sup>   | TTL/ST           | —           | Timer2 external input.                                                                            |

|                                                                            | IOCC3                 | TTL/ST           | _           | Interrupt-on-change input.                                                                        |

| RC4/ANC4/SDA1 <sup>(3,4)</sup> /SDI1 <sup>(1)</sup> /IOCC4                 | RC4                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                              |

|                                                                            | ANC4                  | AN               | _           | ADC Channel C4 input.                                                                             |

|                                                                            | SDA1 <sup>(3,4)</sup> | I <sup>2</sup> C | OD          | MSSP1 I <sup>2</sup> C serial data input/output.                                                  |

|                                                                            | SDI1 <sup>(1)</sup>   | TTL/ST           | _           | MSSP1 SPI serial data input.                                                                      |

|                                                                            | IOCC4                 | TTL/ST           | _           | Interrupt-on-change input.                                                                        |

| RC5/ANC5/IOCC5                                                             | RC5                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                              |

|                                                                            | ANC5                  | AN               | _           | ADC Channel C5 input.                                                                             |

|                                                                            | IOCC5                 | TTL/ST           | _           | Interrupt-on-change input.                                                                        |

| RC6/ANC6/TX1/CK1 <sup>(1)</sup> /IOCC6                                     | RC6                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                              |

|                                                                            | ANC6                  | AN               | _           | ADC Channel C6 input.                                                                             |

|                                                                            | TX1                   | _                | CMOS        | EUSART1 asynchronous transmit.                                                                    |

|                                                                            | CK1 <sup>(1)</sup>    | TTL/ST           | CMOS/OD     | EUSART 1 synchronous mode clock input/output.                                                     |

|                                                                            | IOCC6                 | TTL/ST           | _           | Interrupt-on-change input.                                                                        |

| RC7/ANC7/RX1/DT1 <sup>(3)</sup> /IOCC7                                     | RC7                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                              |

|                                                                            | ANC7                  | AN               |             | ADC Channel C7 input.                                                                             |

|                                                                            | RX1                   | TTL/ST           | —           | EUSART1 Asynchronous mode receiver data input.                                                    |

|                                                                            | DT1 <sup>(3)</sup>    | TTL/ST           | CMOS/OD     | EUSART1 Synchronous mode data input/output.                                                       |

|                                                                            | IOCC7                 | TTL/ST           | _           | Interrupt-on-change input.                                                                        |

All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 15-3. This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx 1:

2:

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and 3: PPS output registers.

These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS 4: assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

Note

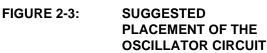

### 2.5 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to Section 9.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-3. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins, and other signals in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times, and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

### 2.6 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

| Address   | Name                 | Bit 7         | Bit 6 | Bit 5         | Bit 4         | Bit 3               | Bit 2     | Bit 1 | Bit 0     | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |  |  |  |

|-----------|----------------------|---------------|-------|---------------|---------------|---------------------|-----------|-------|-----------|-----------------------|----------------------------|--|--|--|

| Bank 61   |                      |               |       |               | •             |                     |           |       | •         |                       | •                          |  |  |  |

|           |                      |               |       | CPU COP       | RE REGISTERS  | ; see Table 4-3 for | specifics |       |           |                       |                            |  |  |  |

| 1E8Ch     | E8Ch — Unimplemented |               |       |               |               |                     |           |       |           |                       |                            |  |  |  |

| 1E8Dh     | —                    |               |       |               | Unimple       | emented             |           |       |           |                       |                            |  |  |  |

| 1E8Eh     | —                    |               |       |               | Unimple       | emented             |           |       |           |                       |                            |  |  |  |

| 1E8Fh     | PPSLOCK              |               | —     | _             | —             | —                   | -         | —     | PPSLOCKED | 0                     | 0                          |  |  |  |

| 1E90h     | INTPPS               |               | —     |               |               | INTP                | PS<5:0>   |       |           | 00 1000               | uu uuuu                    |  |  |  |

| 1E91h     | <b>T0CKIPPS</b>      | —             | —     |               |               | TOCKI               | PPS<5:0>  |       |           | 00 0100               | uu uuuu                    |  |  |  |

| 1E92h     | T1CKIPPS             |               | —     |               |               | T1CKI               | PPS<5:0>  |       |           | 01 0000               | uu uuuu                    |  |  |  |

| 1E93h     | T1GPPS               |               | —     |               |               | T1GF                | PPS<5:0>  |       |           | 00 1101               | uu uuuu                    |  |  |  |

| 1E94h     |                      |               |       |               | Linimolo      | montod              |           |       |           |                       |                            |  |  |  |

| 1E9Bh     | —                    |               |       | Unimplemented |               |                     |           |       |           |                       | _                          |  |  |  |

| 1E9Ch     | T2INPPS              | —             | -     | T2INPPS<5:0>  |               |                     |           |       |           |                       | uu uuuu                    |  |  |  |

| 1E9Dh     |                      | Unimplemented |       |               |               |                     |           |       |           |                       |                            |  |  |  |

| 1EA0h     | —                    |               |       |               | Unimple       | ementeu             |           |       |           | _                     | _                          |  |  |  |

| 1EA1h     | CCP1PPS              | _             | -     |               |               | CCP1                | PPS<5:0>  |       |           | 01 0010               | uu uuuu                    |  |  |  |

| 1EA2h     | CCP2PPS              | —             | —     |               |               | CCP2                | PPS<5:0>  |       |           | 01 0001               | uu uuuu                    |  |  |  |

| 1EA3h     |                      |               |       |               | l lucius a la | and a stand         |           |       |           |                       |                            |  |  |  |

| 1EB0h     | —                    |               |       |               | Unimple       | ementeu             |           |       |           | _                     | _                          |  |  |  |

| 1EB1h     | CWG1PPS              | _             | -     |               |               | CWG1                | PPS<5:0>  |       |           | 00 1000               | uu uuuu                    |  |  |  |

| 1EB2h     |                      |               |       |               | Induced -     | montod              |           |       |           |                       |                            |  |  |  |

| <br>1EBAh | _                    |               |       |               | Unimple       | ementea             |           |       |           | _                     | _                          |  |  |  |

| 1EBBh     | <b>CLCIN0PPS</b>     | _             | _     |               |               | CLCIN               | )PPS<5:0> |       |           | 00 0000               | uu uuuu                    |  |  |  |

| 1EBCh     | CLCIN1PPS            | _             | _     |               |               | CLCIN               | 1PPS<5:0> |       |           | 00 0001               | uu uuuu                    |  |  |  |

| 1EBDh     | CLCIN2PPS            | _             | _     |               |               | CLCIN               | 2PPS<5:0> |       |           | 00 1110               | uu uuuu                    |  |  |  |

| 1EBEh     | CLCIN3PPS            | _             | _     |               |               | CLCIN               | 3PPS<5:0> |       |           | 00 1111               | uu uuuu                    |  |  |  |

| 1EBFh     |                      |               |       |               |               |                     |           |       |           |                       |                            |  |  |  |

| <br>1EC2h | -                    |               |       |               | Unimple       | emented             |           |       |           | _                     | _                          |  |  |  |

| 1EC3h     | ADACTPPS             | _             | _     |               |               | CLCIN               | 3PPS<5:0> |       |           | 001100                | uuuuuu                     |  |  |  |

| 1EC4h     | _                    |               | ·     | •             | Unimple       |                     |           |       |           |                       |                            |  |  |  |

### TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

# PIC16(L)F15354/55

### 5.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Program memory protection and data memory are controlled independently. Internal access to the program memory is unaffected by any code protection setting.

### 5.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Self-writing the program memory is dependent upon the write protection setting. See **Section 5.4** "Write **Protection**" for more information.

### 5.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as boot loader software, can be protected while allowing other regions of the program memory to be modified.

The WRTAPP, WRTSAF, WRTB, WRTC bits in Configuration Words (Register 5-4) define whether the corresponding region of the program memory block is protected or not.

### 5.5 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See Section 13.3.6 "NVMREG Access to Device Information Area, Device Configuration Area, User ID, Device ID and Configuration Words" for more information on accessing these memory locations. For more information on checksum calculation, see the "PIC16(L)F153xx Memory Programming Specification" (DS40001838).

# PIC16(L)F15354/55

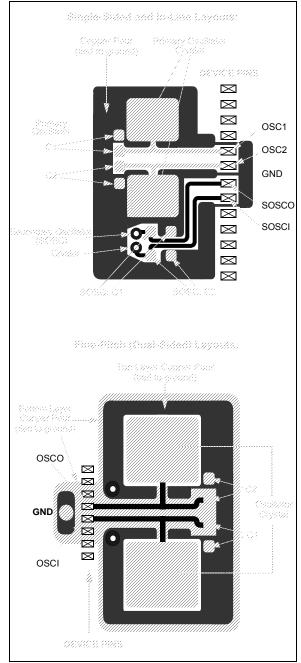

### 13.3.5 MODIFYING FLASH PROGRAM MEMORY

When modifying existing data in a program memory row, and data within that row must be preserved, it must first be read and saved in a RAM image. Program memory is modified using the following steps:

- 1. Load the starting address of the row to be modified.

- 2. Read the existing data from the row into a RAM image.

- 3. Modify the RAM image to contain the new data to be written into program memory.

- 4. Load the starting address of the row to be rewritten.

- 5. Erase the program memory row.

- 6. Load the write latches with data from the RAM image.

- 7. Initiate a programming operation.

### FIGURE 13-6:

### FLASH PROGRAM MEMORY MODIFY

### 14.7 Register Definitions: PORTC

### **REGISTER 14-17: PORTC: PORTC REGISTER**

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u      |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|--------------|

| RC7              | RC6     | RC5               | RC4     | RC3            | RC2              | RC1              | RC0          |

| bit 7            |         |                   |         |                |                  |                  | bit 0        |

|                  |         |                   |         |                |                  |                  |              |

| Legend:          |         |                   |         |                |                  |                  |              |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | mented bit, read | l as '0'         |              |

| u = Bit is uncha | anged   | x = Bit is unkn   | iown    | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |              |

bit 7-0 RC<7:0>: PORTC General Purpose I/O Pin bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

**Note 1:** Writes to PORTC are actually written to corresponding LATC register. The actual I/O pin values are read from the PORTC register.

### REGISTER 14-18: TRISC: PORTC TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISC7  | TRISC6  | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

**TRISC<7:0>:** PORTC Tri-State Control bits 1 = PORTC pin configured as an input (tri-stated)

= PORTC pin configured as an input (in-state) = PORTC pin configured as an output

0 = PORTC pin configured as an output

### REGISTER 14-19: LATC: PORTC DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATC7   | LATC6   | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

### bit 7-0 LATC<7:0>: PORTC Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register returns actual I/O pin values.

### 18.3 Register Definitions: FVR Control

### REGISTER 18-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0/0         | R-q/q                 | R/W-0/0                            | R/W-0/0              | R/W-0/0                    | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|-----------------|-----------------------|------------------------------------|----------------------|----------------------------|------------------|------------------|--------------|

| FVREN           | FVRRDY <sup>(1)</sup> | TSEN <sup>(3)</sup>                | TSRNG <sup>(3)</sup> | CDAF                       | VR<1:0>          | ADFVI            | R<1:0>       |

| bit 7           |                       |                                    |                      |                            |                  |                  | bit          |

|                 |                       |                                    |                      |                            |                  |                  |              |

| Legend:         |                       |                                    |                      |                            |                  |                  |              |

| R = Readabl     | e bit                 | W = Writable                       | bit                  |                            | mented bit, read |                  |              |

| u = Bit is und  | hanged                | x = Bit is unk                     | nown                 | -n/n = Value               | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is se | t                     | '0' = Bit is cle                   | ared                 | q = Value de               | pends on condit  | tion             |              |

| bit 7           |                       | d Voltage Refe                     |                      | bit                        |                  |                  |              |

|                 |                       | Itage Referenc<br>Itage Referenc   |                      |                            |                  |                  |              |

| bit 6           | FVRRDY: Fix           | ed Voltage Re                      | ference Ready        | / Flag bit <sup>(1)</sup>  |                  |                  |              |

|                 |                       | Itage Reference<br>Itage Reference |                      |                            | enabled          |                  |              |

| bit 5           |                       | erature Indicate                   | -                    | -                          |                  |                  |              |

|                 |                       | ture Indicator i                   |                      |                            |                  |                  |              |

|                 | •                     | ture Indicator i                   |                      | <i>(</i> -)                |                  |                  |              |

| bit 4           |                       | perature Indica                    |                      | lection bit <sup>(3)</sup> |                  |                  |              |

|                 |                       | ′оо - 4Vт (Higł<br>′оо - 2Vт (Low  | 0,                   |                            |                  |                  |              |

| bit 3-2         |                       | <b>D&gt;:</b> Comparato            | •                    | Gain Selection             | bits             |                  |              |

|                 | 11 = Compar           | ator FVR Buffe                     | er Gain is 4x, (4    | 4.096V) <sup>(2)</sup>     |                  |                  |              |

|                 |                       | ator FVR Buffe                     |                      | ,                          |                  |                  |              |

|                 |                       | ator FVR Buffe<br>ator FVR Buffe   |                      | 1.024V)                    |                  |                  |              |

| bit 1-0         |                       | ADC FVR Build                      |                      | ction bit                  |                  |                  |              |

| DIL 1-0         |                       | 'R Buffer Gain                     |                      |                            |                  |                  |              |

|                 |                       | 'R Buffer Gain                     |                      |                            |                  |                  |              |

|                 |                       | 'R Buffer Gain                     | is 1x, (1.024V       | )                          |                  |                  |              |

|                 | 00 <b>= ADC FV</b>    | 'R Buffer is off                   |                      |                            |                  |                  |              |

| Note 1: F       | VRRDY is always       | s '1' for PIC16                    | (L)F15354/55 (       | devices only.              |                  |                  |              |

| 2: Fi           | xed Voltage Refe      | erence output o                    | cannot exceed        | VDD.                       |                  |                  |              |

- 2: Fixed Voltage Reference output cannot exceed VDD.

- 3: See Section 19.0 "Temperature Indicator Module" for additional information.

### 22.0 NUMERICALLY CONTROLLED OSCILLATOR (NCO) MODULE

The Numerically Controlled Oscillator (NCO) module is a timer that uses overflow from the addition of an increment value to divide the input frequency. The advantage of the addition method over simple counter driven timer is that the output frequency resolution does not vary with the divider value. The NCO is most useful for application that requires frequency accuracy and fine resolution at a fixed duty cycle.

Features of the NCO include:

- 20-bit Increment Function

- Fixed Duty Cycle mode (FDC) mode

- Pulse Frequency (PF) mode

- Output Pulse Width Control

- Multiple Clock Input Sources

- Output Polarity Control

- Interrupt Capability

Figure 22-1 is a simplified block diagram of the NCO module.

### 23.2 Comparator Control

Each comparator has two control registers: CMxCON0 and CMxCON1.

The CMxCON0 register (see Register 23-1) contains Control and Status bits for the following:

- Enable

- Output

- Output polarity

- · Hysteresis enable

- Timer1 output synchronization

The CMxCON1 register (see Register 23-2) contains Control bits for the following:

- · Interrupt on positive/negative edge enables

- The CMxNSEL and CMxPSEL (Register 23-3 and Register 23-4) contain control bits for the following:

- Positive input channel selection

- Negative input channel selection

### 23.2.1 COMPARATOR ENABLE

Setting the CxON bit of the CMxCON0 register enables the comparator for operation. Clearing the CxON bit disables the comparator resulting in minimum current consumption.

### 23.2.2 COMPARATOR OUTPUT

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the MCxOUT bit of the CMOUT register.

The comparator output can also be routed to an external pin through the RxyPPS register (Register 15-2). The corresponding TRIS bit must be clear to enable the pin as an output.

Note 1: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

### 23.2.3 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the CxPOL bit of the CMxCON0 register. Clearing the CxPOL bit results in a non-inverted output.

Table 23-2 shows the output state versus input conditions, including polarity control.

### TABLE 23-2: COMPARATOR OUTPUT STATE VS. INPUT CONDITIONS

| Input Condition | CxPOL | CxOUT |

|-----------------|-------|-------|

| CxVN > CxVP     | 0     | 0     |

| CxVN < CxVP     | 0     | 1     |

| CxVN > CxVP     | 1     | 1     |

| CxVN < CxVP     | 1     | 0     |

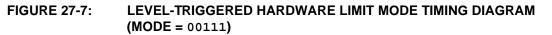

### 27.5.4 LEVEL-TRIGGERED HARDWARE LIMIT MODE

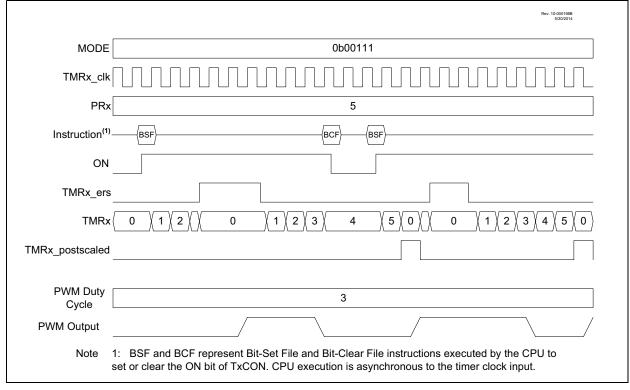

In the Level-Triggered Hardware Limit Timer modes the counter is reset by high or low levels of the external signal TMRx\_ers, as shown in Figure 27-7. Selecting MODE<4:0> = 00110 will cause the timer to reset on a low level external signal. Selecting MODE<4:0> = 00111 will cause the timer to reset on a high level external signal. In the example, the counter is reset while TMRx\_ers = 1. ON is controlled by BSF and BCF instructions. When ON = 0 the external signal is ignored.

When the CCP uses the timer as the PWM time base then the PWM output will be set high when the timer starts counting and then set low only when the timer count matches the CCPRx value. The timer is reset when either the timer count matches the PRx value or two clock periods after the external Reset signal goes true and stays true.

The timer starts counting, and the PWM output is set high, on either the clock following the PRx match or two clocks after the external Reset signal relinquishes the Reset. The PWM output will remain high until the timer counts up to match the CCPRx pulse width value. If the external Reset signal goes true while the PWM output is high then the PWM output will remain high until the Reset signal is released allowing the timer to count up to match the CCPRx value.

# © 2016 Microchip Technology Inc.

Preliminary

### 27.5.10 LEVEL-TRIGGERED HARDWARE LIMIT ONE-SHOT MODES

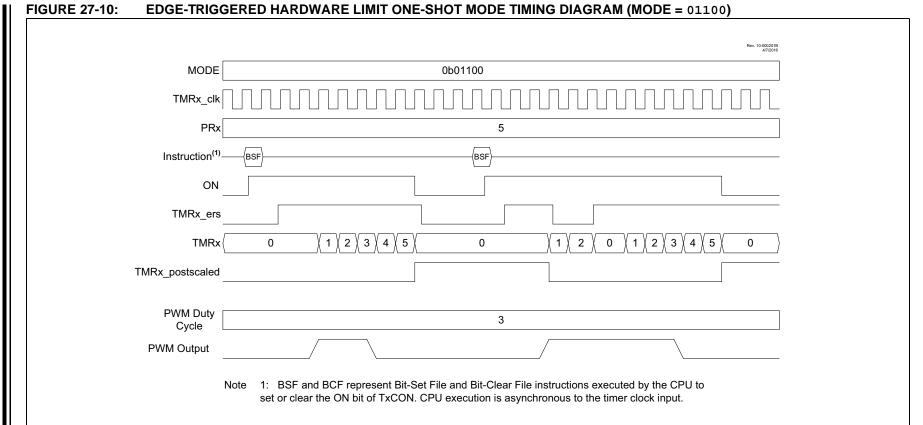

The Level-Triggered Hardware Limit One-Shot modes hold the timer in Reset on an external Reset level and start counting when both the ON bit is set and the external signal is not at the Reset level. If one of either the external signal is not in Reset or the ON bit is set then the other signal being set/made active will start the timer. Reset levels are selected as follows:

- Low Reset level (MODE<4:0> = 10110)

- High Reset level (MODE<4:0> = 10111)

When the timer count matches the PRx period count, the timer is reset and the ON bit is cleared. When the ON bit is cleared by either a PRx match or by software control the timer will stay in Reset until both the ON bit is set and the external signal is not at the Reset level.

When Level-Triggered Hardware Limit One-Shot modes are used in conjunction with the CCP PWM operation the PWM drive goes active with either the external signal edge or the setting of the ON bit, which-ever of the two starts the timer.

| R/W/HC-0/0        | R/W-0/0                                          | R/W-0/0            | R/W-0/0         | R/W-0/0          | R/W-0/0          | R/W-0/0        | R/W-0/0      |  |  |  |  |

|-------------------|--------------------------------------------------|--------------------|-----------------|------------------|------------------|----------------|--------------|--|--|--|--|

| ON <sup>(1)</sup> |                                                  | CKPS<2:0>          |                 |                  | OUTP             | S<3:0>         |              |  |  |  |  |

| bit 7             |                                                  |                    |                 | -                |                  |                | bit (        |  |  |  |  |

| Legend:           |                                                  |                    |                 |                  |                  |                |              |  |  |  |  |

| R = Readable      | bit                                              | W = Writable       | bit             | U = Unimplen     | nented bit, read | d as '0'       |              |  |  |  |  |

| u = Bit is unch   | anged                                            | x = Bit is unkr    | iown            | -n/n = Value a   | at POR and BC    | R/Value at all | other Resets |  |  |  |  |

| '1' = Bit is set  | ·                                                | '0' = Bit is clea  | ared            |                  | eared by hardv   |                |              |  |  |  |  |

|                   |                                                  |                    |                 |                  |                  |                |              |  |  |  |  |

| bit 7             | ON: Timerx                                       | On bit             |                 |                  |                  |                |              |  |  |  |  |

|                   | 1 = Timerx                                       | is on              |                 |                  |                  |                |              |  |  |  |  |

|                   | 0 = Timerx                                       | is off: all counte | rs and state n  | nachines are res | set              |                |              |  |  |  |  |

| bit 6-4           | CKPS<2:0>:                                       | : Timer2-type Cl   | ock Prescale    | Select bits      |                  |                |              |  |  |  |  |

|                   | 111 = 1: <b>128</b>                              | Prescaler          |                 |                  |                  |                |              |  |  |  |  |

|                   | 110 = 1:64 Prescaler                             |                    |                 |                  |                  |                |              |  |  |  |  |

|                   | 101 = 1:32 Prescaler                             |                    |                 |                  |                  |                |              |  |  |  |  |

|                   | 100 = 1:16 Prescaler                             |                    |                 |                  |                  |                |              |  |  |  |  |

|                   | 011 = 1:8 Prescaler                              |                    |                 |                  |                  |                |              |  |  |  |  |

|                   |                                                  | 10 = 1:4 Prescaler |                 |                  |                  |                |              |  |  |  |  |

|                   | 001 = 1:2 P                                      |                    |                 |                  |                  |                |              |  |  |  |  |

|                   | 000 = 1:1 P                                      |                    |                 |                  |                  |                |              |  |  |  |  |

| bit 3-0           |                                                  | >: Timerx Outpu    | It Postscaler S | Select bits      |                  |                |              |  |  |  |  |

|                   | 1111 = 1:16                                      |                    |                 |                  |                  |                |              |  |  |  |  |

|                   | 1110 = 1:15 Postscaler                           |                    |                 |                  |                  |                |              |  |  |  |  |

|                   | 1101 = 1:14 Postscaler                           |                    |                 |                  |                  |                |              |  |  |  |  |

|                   | 1100 = 1:13 Postscaler<br>1011 = 1:12 Postscaler |                    |                 |                  |                  |                |              |  |  |  |  |

|                   |                                                  |                    |                 |                  |                  |                |              |  |  |  |  |

|                   | 1010 = 1:11  Postscaler                          |                    |                 |                  |                  |                |              |  |  |  |  |

|                   | 1001 = 1:10 Postscaler<br>1000 = 1:9 Postscaler  |                    |                 |                  |                  |                |              |  |  |  |  |

|                   | 0111 = 1.8 Postscaler                            |                    |                 |                  |                  |                |              |  |  |  |  |

|                   | 0110 = 1.7 Postscaler                            |                    |                 |                  |                  |                |              |  |  |  |  |

|                   | 0101 = <b>1</b> :6 F                             | Postscaler         |                 |                  |                  |                |              |  |  |  |  |

|                   | 0100 <b>= 1:5</b> F                              | Postscaler         |                 |                  |                  |                |              |  |  |  |  |

|                   | 0011 = <b>1</b> :4 F                             | Postscaler         |                 |                  |                  |                |              |  |  |  |  |

|                   | 0010 = 1:3 F                                     | Postscaler         |                 |                  |                  |                |              |  |  |  |  |

|                   | 0001 = 1:2 F                                     |                    |                 |                  |                  |                |              |  |  |  |  |

|                   | 0000 = 1:1 F                                     | Postscaler         |                 |                  |                  |                |              |  |  |  |  |

### REGISTER 27-2: T2CON: TIMER2 CONTROL REGISTER

Note 1: In certain modes, the ON bit will be auto-cleared by hardware. See Section 27.5 "Operation Examples".

| Name     | Bit 7       | Bit 6           | Bit 5        | Bit 4  | Bit 3 | Bit 2     | Bit 1  | Bit 0  | Register<br>on Page |

|----------|-------------|-----------------|--------------|--------|-------|-----------|--------|--------|---------------------|

| CCP1CON  | EN          | _               | OUT          | FMT    |       | MODE      | <3:0>  |        | 317                 |

| CCP2CON  | EN          | _               | OUT          | FMT    |       | MODE      | <3:0>  |        | 317                 |

| CCPTMRS0 | —           | _               | —            | —      | C2TSE | L<1:0>    | C1TSE  | L<1:0> | 320                 |

| CCPTMRS1 | —           | _               | —            | —      | P2TSE | L<1:0>    | C1TSE  | L<1:0> | 321                 |

| INTCON   | GIE         | PEIE            | —            | —      | —     | —         |        | INTEDG | 119                 |

| PIE1     | OSFIE       | CSWIE           | —            | —      | —     | _         | _      | ADIE   | 121                 |

| PIR1     | OSFIF       | CSWIF           | —            | —      | —     | —         | _      | ADIF   | 129                 |

| PR2      | Timer2 Modu | ule Period Re   | gister       |        |       |           |        |        |                     |

| TMR2     | Holding Reg | ister for the 8 | -bit TMR2 Re | gister |       |           |        |        |                     |

| T2CON    | ON          |                 | CKPS<2:0>    |        |       | OUTP      | S<3:0> |        | 306                 |

| T2CLKCON | _           | _               | _            | _      |       | CS<       | 3:0>   |        | 305                 |

| T2RST    | _           | _               | _            | _      |       | RSEL<3:0> |        |        | 308                 |

| T2HLT    | PSYNC       | CKPOL           | CKSYNC       |        |       | MODE<4:0> |        |        | 307                 |

| TABLE 27-2: | SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2 |

|-------------|---------------------------------------------|

|-------------|---------------------------------------------|

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for Timer2 module.

\* Page provides register information.

### 30.9 CWG Steering Mode

In Steering mode (MODE = 00x), the CWG allows any combination of the CWG1x pins to be the modulated signal. The same signal can be simultaneously available on multiple pins, or a fixed-value output can be presented.

When the respective STRx bit of CWG1OCON0 is '0', the corresponding pin is held at the level defined. When the respective STRx bit of CWG1OCON0 is '1', the pin is driven by the input data signal. The user can assign the input data signal to one, two, three, or all four output pins.

The POLx bits of the CWG1CON1 register control the signal polarity only when STRx = 1.

The CWG auto-shutdown operation also applies in Steering modes as described in **Section 30.10** "**Auto-Shutdown**". An auto-shutdown event will only affect pins that have STRx = 1.

### 30.9.1 STEERING SYNCHRONIZATION

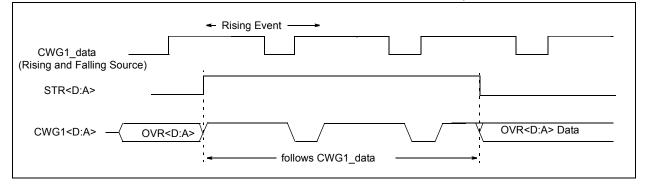

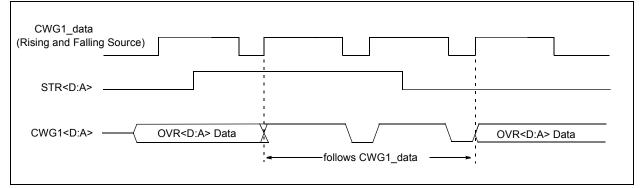

Changing the MODE bits allows for two modes of steering, synchronous and asynchronous.

When MODE = 000, the steering event is asynchronous and will happen at the end of the instruction that writes to STRx (that is, immediately). In this case, the output signal at the output pin may be an incomplete waveform. This can be useful for immediately removing a signal from the pin.

When MODE = 001, the steering update is synchronous and occurs at the beginning of the next rising edge of the input data signal. In this case, steering the output on/off will always produce a complete waveform.

Figure 30-10 and Figure 30-11 illustrate the timing of asynchronous and synchronous steering, respectively.

### FIGURE 30-11: EXAMPLE OF STEERING EVENT (MODE<2:0> = 001)

### 32.5.3.3 7-bit Transmission with Address Hold Enabled

Setting the AHEN bit of the SSPxCON3 register enables additional clock stretching and interrupt generation after the eighth falling edge of a received matching address. Once a matching address has been clocked in, CKP is cleared and the SSPxIF interrupt is set.

Figure 32-19 displays a standard waveform of a 7-bit address slave transmission with AHEN enabled.

- 1. Bus starts Idle.

- Master sends Start condition; the S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Master sends matching address with R/W bit set. After the eighth falling edge of the SCL line the CKP bit is cleared and SSPxIF interrupt is generated.

- 4. Slave software clears SSPxIF.

- 5. Slave software reads ACKTIM bit of SSPxCON3 register, and  $R/\overline{W}$  and  $D/\overline{A}$  of the SSPxSTAT register to determine the source of the interrupt.

- 6. Slave reads the address value from the SSPxBUF register clearing the BF bit.

- 7. Slave software decides from this information if it wishes to ACK or not ACK and sets the ACKDT bit of the SSPxCON2 register accordingly.

- 8. Slave sets the CKP bit releasing SCL.

- 9. Master clocks in the  $\overline{ACK}$  value from the slave.

- 10. Slave hardware automatically clears the CKP bit and sets SSPxIF after the ACK if the R/W bit is set.

- 11. Slave software clears SSPxIF.

- 12. Slave loads value to transmit to the master into SSPxBUF setting the BF bit.

Note: <u>SSPxBUF</u> cannot be loaded until after the <u>ACK</u>.

13. Slave sets the CKP bit releasing the clock.

- 14. Master clocks out the data from the slave and sends an  $\overline{ACK}$  value on the ninth SCL pulse.

- 15. Slave hardware copies the ACK value into the ACKSTAT bit of the SSPxCON2 register.

- 16. Steps 10-15 are repeated for each byte transmitted to the master from the slave.

- 17. If the master sends a not ACK the slave releases the bus allowing the master to send a Stop and end the communication.

**Note:** Master must send a not ACK on the last byte to ensure that the slave releases the SCL line to receive a Stop.

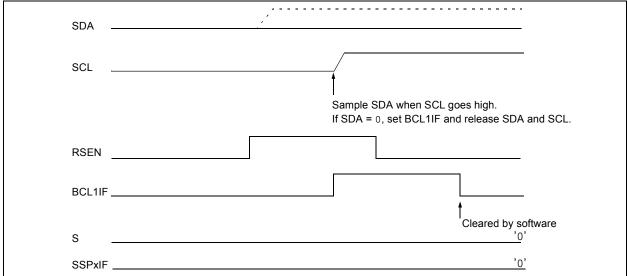

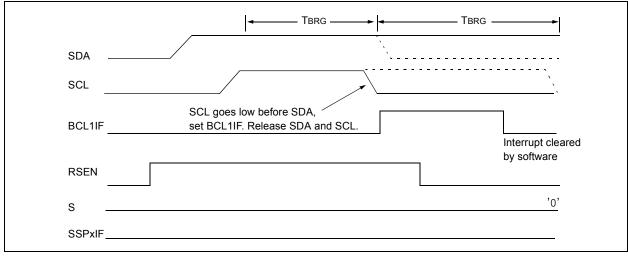

## 32.6.13.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level (Case 1).

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1' (Case 2).

When the user releases SDA and the pin is allowed to float high, the BRG is loaded with SSPxADD and counts down to zero. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 32-36). If SDA is sampled high, the BRG is reloaded and begins

counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, see Figure 32-37.

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

### FIGURE 32-36: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

### REGISTER 32-2: SSPxCON1: SSPx CONTROL REGISTER 1

| R/C/HS-0/0          | R/C/HS-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0/0                                             | R/W-0/0                                | R/W-0/0                                               | R/W-0/0        | R/W-0/0                                 | R/W-0/0   |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------|-------------------------------------------------------|----------------|-----------------------------------------|-----------|--|

| WCOL                | SSPOV <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SSPEN                                               | СКР                                    |                                                       | SSP            | M<3:0>                                  |           |  |

| bit 7               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                     |                                        |                                                       |                |                                         | bit       |  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                     |                                        |                                                       |                |                                         |           |  |

| Legend:             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                     |                                        |                                                       |                |                                         |           |  |

| R = Readable bit    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | W = Writable bit                                    |                                        | U = Unimplement                                       |                |                                         |           |  |

| u = Bit is unchange | d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | x = Bit is unknowr                                  |                                        | -n/n = Value at POR and BOR/Value at all other Resets |                |                                         |           |  |

| '1' = Bit is set    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | '0' = Bit is cleared                                |                                        | HS = Bit is set by                                    | hardware       | C = User cleared                        |           |  |

| bit 7               | WCOL: Write Collision Detect bit (Transmit mode only)<br>1 = The SSPxBUF register is written while it is still transmitting the previous word (must be cleared in software)<br>0 = No collision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                     |                                        |                                                       |                |                                         |           |  |

| bit 6               | <ul> <li>SSPOV: Receive Overflow Indicator bit<sup>(1)</sup>         In SPI mode:         1 = A new byte is received while the SSPxBUF register is still holding the previous data. In case of overflow, the data in SSPxSR is lost.<br/>Overflow can only occur in Slave mode. In Slave mode, the user must read the SSPxBUF, even if only transmitting data, to avoid<br/>setting overflow. In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to the<br/>SSPxBUF register (must be cleared in software).         </li> <li>0 = No overflow         In I<sup>2</sup>C mode:         1 = A byte is received while the SSPxBUF register is still holding the previous byte. SSPOV is a "don't care" in Transmit mode<br/>(must be cleared in software).         </li> <li>0 = No overflow</li> </ul> |                                                     |                                        |                                                       |                |                                         |           |  |

| bit 5               | <ul> <li>SSPEN: Synchronous Serial Port Enable bit</li> <li>In both modes, when enabled, the following pins must be properly configured as input or output<br/>In SPI mode:         <ul> <li>I = Enables serial port and configures SCK, SDO, SDI and SS as the source of the serial port pins<sup>(2)</sup></li> <li>Disables serial port and configures these pins as I/O port pins             </li> <li>I = Enables the serial port and configures the SDA and SCL pins as the source of the serial port pins<sup>(3)</sup></li> <li>Disables serial port and configures these pins as I/O port pins</li> </ul> </li> </ul>                                                                                                                                                                                                                                   |                                                     |                                        |                                                       |                |                                         |           |  |

| bit 4               | CKP: Clock Polarity Select bit<br>In SPI mode:<br>1 = Idle state for clock is a high level<br>0 = Idle state for clock is a low level<br>In I <sup>2</sup> C Slave mode:<br>SCL release control<br>1 = Enable clock<br>0 = Holds clock low (clock stretch). (Used to ensure data setup time.)<br>In I <sup>2</sup> C Master mode:<br>Unused in this mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                     |                                        |                                                       |                |                                         |           |  |

| bit 3-0             | SSPM<3:0>: Synchronous Serial Port Mode Select bits<br>1111 = I <sup>2</sup> C Slave mode, 10-bit address with Start and Stop bit interrupts enabled<br>1110 = I <sup>2</sup> C Slave mode, 7-bit address with Start and Stop bit interrupts enabled<br>1101 = Reserved<br>1010 = Reserved<br>1011 = I <sup>2</sup> C firmware controlled Master mode (slave idle)<br>1010 = SPI Master mode, clock = Fosc/(4 * (SSPxADD+1)) <sup>(5)</sup><br>1001 = Reserved<br>1000 = I <sup>2</sup> C Master mode, clock = Fosc / (4 * (SSPxADD+1)) <sup>(4)</sup><br>0111 = I <sup>2</sup> C Slave mode, 10-bit address<br>0101 = SPI Slave mode, clock = SCK pin, <u>SS</u> pin control disabled, <u>SS</u> can be used as I/O pin<br>0100 = SPI Slave mode, clock = T2_match/2<br>0011 = SPI Master mode, clock = Fosc/16<br>0001 = SPI Master mode, clock = Fosc/16       |                                                     |                                        |                                                       |                |                                         |           |  |

| 2: When<br>RxyF     | aster mode, the ove<br>n enabled, these pi<br>PPS to select the pi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | erflow bit is not set<br>ns must be properly<br>ns. | since each new r<br>/ configured as ii |                                                       | SSPxSSPPS, SSF | by writing to the SS<br>XCLKPPS, SSPxDA | TPPS, and |  |

When enabled, the SDA and SCL pins must be configured as inputs. Use SSPxCLKPPS, SSPxDATPPS, and RxyPPS to select the pins.

SSPxADD values of 0, 1 or 2 are not supported for I<sup>2</sup>C mode.

SSPxADD value of '0' is not supported. Use SSPM = 0000 instead.

### TABLE 37-18: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

|               | rd Operating (                  | •                                                                                                              | nless otherwis<br>≤ +125°C  | e stated)                  |                            |                     |                        |                    |                    |

|---------------|---------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------------|----------------------------|---------------------|------------------------|--------------------|--------------------|

| Param.<br>No. | Sym.                            | Characteristic                                                                                                 |                             |                            | Min.                       | Тур†                | Max.                   | Units              | Conditions         |

| 40*           | Тт0Н                            | T0CKI High Pulse Width                                                                                         |                             | No Prescaler               | 0.5 Tcy + 20               | -                   |                        | ns                 |                    |

|               |                                 | With Prescaler                                                                                                 |                             |                            | 10                         | _                   |                        | ns                 | $\frown$           |

| 41* T⊤0L      | T0CKI Low Pulse Width No Presca |                                                                                                                |                             | 0.5 Tcy + 20               | —                          | _                   | /ns /                  |                    |                    |

|               |                                 | With Prescaler                                                                                                 |                             |                            | 10                         | —                   | _                      | ns                 |                    |

| 42* TT0P      | T0CKI Period                    |                                                                                                                |                             | Greater of:                | —                          | _                   | ns                     | N = prescale value |                    |

|               |                                 |                                                                                                                |                             | 20 or <u>Tcy + 40</u><br>N |                            | $\bigwedge$         |                        |                    |                    |

| 45* T⊤1H      | T⊤1H                            | T1CKI High<br>Time                                                                                             | Synchronous, No Prescaler   |                            | 0.5 Tcy + 20               | —                   | 7-1                    | ns                 | $\searrow$         |

|               |                                 |                                                                                                                | Synchronous, with Prescaler |                            | 15                         | —                   | +/                     | / ŋs               | $\sim$             |

|               |                                 |                                                                                                                | Asynchronous                |                            | 30                         | $\overline{}$       | -                      | ns                 |                    |

| 46* T⊤1L      | TT1L                            | - T1CKI Low<br>Time                                                                                            | Synchronous, N              | No Prescaler               | 0.5 Tcy + 20               | $\langle - \rangle$ | -                      | ns                 |                    |

|               |                                 |                                                                                                                | Synchronous, v              | vith Prescaler             | 15                         | $\sim$              |                        | √ns                |                    |

|               |                                 |                                                                                                                | Asynchronous                |                            | 30 <                       | 1                   | A                      | ns                 |                    |

| 47* TT1P      | TT1P                            | T1P T1CKI Input<br>Period                                                                                      | Synchronous                 |                            | Greater of.                | 1                   |                        | ns                 | N = prescale value |

|               |                                 |                                                                                                                |                             |                            | 30 or <u>TCX + 40</u><br>N |                     | >                      |                    |                    |

|               |                                 |                                                                                                                | Asynchronous                | /                          | 60                         |                     | —                      | ns                 |                    |

| 48            | F⊤1                             | Secondary Oscillator Input Frequency Range 32.4 32.768 33.1 kHz<br>(oscillator enabled by setting bit T1OSCEN) |                             |                            |                            |                     |                        |                    |                    |

| 49*           | TCKEZTMR1                       | Delay from E<br>Increment                                                                                      | 2 Vosc                      | —                          | 7 Tosc                     | —                   | Timers in Sync<br>mode |                    |                    |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### 39.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- MPLAB® XPRESS IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB X SIM Software Simulator

- · Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools