Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | XC800                                                                           |

| Core Size                  | 8-Bit                                                                           |

| Speed                      | 24MHz                                                                           |

| Connectivity               | SSI, UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 34                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1.75К х 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 48-LQFP                                                                         |

| Supplier Device Package    | PG-TQFP-48                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/sal-xc886-8ffa-5v-ac |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 8-Bit Single Chip Microcontroller

## SAL-XC886CLM

# **1** Summary of Features

The SAL-XC886 has the following features:

- High-performance XC800 Core

- compatible with standard 8051 processor

- two clocks per machine cycle architecture (for memory access without wait state)

- two data pointers

- On-chip memory

- 12 Kbytes of Boot ROM

- 256 bytes of RAM

- 1.5 Kbytes of XRAM

- 24/32 Kbytes of Flash

- (includes memory protection strategy)

- I/O port supply at 5.0 V and core logic supply at 2.5 V (generated by embedded voltage regulator)

(more features on next page)

| Flash<br>24K/32K x 8 |                   | On-Chip Debug Support |                    | UART  | UART SSC                   |        | 7-bit Digital V |

|----------------------|-------------------|-----------------------|--------------------|-------|----------------------------|--------|-----------------|

| Boot ROM<br>12K x 8  |                   | XC800 Core            |                    |       | ompare Unit<br>-bit        | Port 1 | 8-bit Digital V |

| XRAM<br>1.5K x 8     |                   | XC800 Core            |                    |       | are Unit<br>-bit           | Port 2 | 8-bit Digital/  |

| RAM<br>256 x 8       | Timer 0<br>16-bit | Timer 1<br>16-bit     | Timer 2<br>16-bit  | 10    | ADC<br>10-bit<br>8-channel |        | 8-bit Digital V |

| MDU                  | CORDIC            | MultiCAN              | Timer 21<br>16-bit | UART1 | Watchdog<br>Timer          | Port 4 | 3-bit Digital V |

#### Summary of Features

#### SAL-XC886 Variant Devices

The SAL-XC886 product family features devices with different configurations and program memory sizes, to offer cost-effective solutions for different application requirements.

The list of SAL-XC886 device configurations are summarized in Table 1.

| Device<br>Type | Sales Type           | Program<br>Memory<br>(Kbytes) | CAN<br>Module | LIN BSL<br>Support | MDU<br>Module |

|----------------|----------------------|-------------------------------|---------------|--------------------|---------------|

| Flash          | SAL-XC886-8FFA 5V    | 32                            | No            | No                 | No            |

| S              | SAL-XC886C-8FFA 5V   | 32                            | Yes           | No                 | No            |

|                | SAL-XC886CM-8FFA 5V  | 32                            | Yes           | No                 | Yes           |

|                | SAL-XC886LM-8FFA 5V  | 32                            | No            | Yes                | Yes           |

|                | SAL-XC886CLM-8FFA 5V | 32                            | Yes           | Yes                | Yes           |

|                | SAL-XC886-6FFA 5V    | 24                            | No            | No                 | No            |

|                | SAL-XC886C-6FFA 5V   | 24                            | Yes           | No                 | No            |

|                | SAL-XC886CM-6FFA 5V  | 24                            | Yes           | No                 | Yes           |

|                | SAL-XC886LM-6FFA 5V  | 24                            | No            | Yes                | Yes           |

|                | SAL-XC886CLM-6FFA 5V | 24                            | Yes           | Yes                | Yes           |

#### Table 1Device Profile

Note: For variants with LIN BSL support, only LIN BSL is available regardless of the availability of the CAN module.

As this document refers to all the derivatives, some description may not apply to a specific product. For simplicity, all versions are referred to by the term SAL-XC886 throughout this document.

#### **Ordering Information**

The ordering code for Infineon Technologies microcontrollers provides an exact reference to the required product. This ordering code identifies:

- The derivative itself, i.e. its function set, the temperature range, and the supply voltage

- The package and the type of delivery

For the available ordering codes for the SAL-XC886, please refer to your responsible sales representative or your local distributor.

## 3.2.2 Special Function Register

The Special Function Registers (SFRs) occupy direct internal data memory space in the range  $80_{H}$  to FF<sub>H</sub>. All registers, except the program counter, reside in the SFR area. The SFRs include pointers and registers that provide an interface between the CPU and the on-chip peripherals. As the 128-SFR range is less than the total number of registers required, address extension mechanisms are required to increase the number of addressable SFRs. The address extension mechanisms include:

- Mapping

- Paging

#### 3.2.2.1 Address Extension by Mapping

Address extension is performed at the system level by mapping. The SFR area is extended into two portions: the standard (non-mapped) SFR area and the mapped SFR area. Each portion supports the same address range  $80_H$  to FF<sub>H</sub>, bringing the number of addressable SFRs to 256. The extended address range is not directly controlled by the CPU instruction itself, but is derived from bit RMAP in the system control register SYSCON0 at address  $8F_H$ . To access SFRs in the mapped area, bit RMAP in SFR SYSCON0 must be set. Alternatively, the SFRs in the standard area can be accessed by clearing bit RMAP. The SFR area can be selected as shown in **Figure 7**.

As long as bit RMAP is set, the mapped SFR area can be accessed. This bit is not cleared automatically by hardware. Thus, before standard/mapped registers are accessed, bit RMAP must be cleared/set, respectively, by software.

## 3.2.3.1 Password Register

# PASSWD

| Password | Reset | Value: 07 <sub>H</sub> |   |   |               |    |    |

|----------|-------|------------------------|---|---|---------------|----|----|

| 7        | 6     | 5                      | 4 | 3 | 2             | 1  | 0  |

|          |       | PASS                   | I | I | PROTECT<br>_S | МС | DE |

|          |       | wh                     |   |   | rh            | r  | W  |

| Field     | Bits  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|-----------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| MODE      | [1:0] | rw   | <ul> <li>Bit Protection Scheme Control Bits</li> <li>Scheme disabled - direct access to the protected bits is allowed.</li> <li>Scheme enabled - the bit field PASS has to be written with the passwords to open and close the access to protected bits. (default)</li> <li>Others:Scheme Enabled.</li> <li>These two bits cannot be written directly. To change he value between 11<sub>B</sub> and 00<sub>B</sub>, the bit field PASS nust be written with 11000<sub>B</sub>; only then, will the MODE[1:0] be registered.</li> </ul> |  |  |  |  |  |  |  |

| PROTECT_S | 2     | rh   | <ul> <li>Bit Protection Signal Status Bit</li> <li>This bit shows the status of the protection.</li> <li>0 Software is able to write to all protected bits.</li> <li>1 Software is unable to write to any protected bits.</li> </ul>                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| PASS      | [7:3] | wh   | Password BitsThe Bit Protection Scheme only recognizes threepatterns. $11000_B$ Enables writing of the bit field MODE. $10011_B$ Opens access to writing of all protected bits. $10101_B$ Closes access to writing of all protected bits                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| Addr            | Register Name              | Bit            | 7    | 6        | 5                                            | 4    | 3   | 2        | 1        | 0        |  |  |

|-----------------|----------------------------|----------------|------|----------|----------------------------------------------|------|-----|----------|----------|----------|--|--|

| вз <sub>Н</sub> | MD1 Reset: 00 <sub>H</sub> | Bit Field      |      | <u> </u> | <u>.                                    </u> | DA   | TA  | <u> </u> | <u> </u> | <u> </u> |  |  |

|                 | MDU Operand Register 1     | Туре           |      |          |                                              | r    | W   |          |          |          |  |  |

| вз <sub>Н</sub> | MR1 Reset: 00 <sub>H</sub> | Bit Field      |      |          |                                              | DA   | ATA |          |          |          |  |  |

|                 | MDU Result Register 1      | Туре           | rh   |          |                                              |      |     |          |          |          |  |  |

| B4 <sub>H</sub> | MD2 Reset: 00 <sub>H</sub> | Bit Field      | DATA |          |                                              |      |     |          |          |          |  |  |

|                 | MDU Operand Register 2     | Туре           |      |          |                                              | r    | w   |          |          |          |  |  |

| B4 <sub>H</sub> | MR2 Reset: 00 <sub>H</sub> | Bit Field      |      |          |                                              | DATA |     |          |          |          |  |  |

|                 | MDU Result Register 2      | Type rh        |      |          |                                              |      |     |          |          |          |  |  |

| в5 <sub>Н</sub> | MD3 Reset: 00 <sub>H</sub> | Bit Field      |      |          |                                              | DA   | ATA |          |          |          |  |  |

|                 | MDU Operand Register 3     | Туре           |      |          |                                              | r    | W   |          |          |          |  |  |

| B5 <sub>H</sub> | MR3 Reset: 00 <sub>H</sub> | Bit Field      |      |          |                                              | DA   | ATA |          |          |          |  |  |

|                 | MDU Result Register 3      | Туре           | rh   |          |                                              |      |     |          |          |          |  |  |

| B6 <sub>H</sub> | MD4 Reset: 00 <sub>H</sub> | Bit Field      |      |          |                                              | DA   | ATA |          |          |          |  |  |

|                 | MDU Operand Register 4     | Туре           |      |          |                                              | r    | W   |          |          |          |  |  |

| B6 <sub>H</sub> | MR4 Reset: 00 <sub>H</sub> | Bit Field      |      |          |                                              | DA   | ATA |          |          |          |  |  |

|                 | MDU Result Register 4      | Туре           | rh   |          |                                              |      |     |          |          |          |  |  |

| в7 <sub>Н</sub> | MD5 Reset: 00 <sub>H</sub> | Bit Field DATA |      |          |                                              |      |     |          |          |          |  |  |

|                 | MDU Operand Register 5     | Туре           |      |          |                                              | r    | W   |          |          |          |  |  |

| в7 <sub>Н</sub> | MR5 Reset: 00 <sub>H</sub> | Bit Field      |      |          |                                              | DA   | ATA |          |          |          |  |  |

|                 | MDU Result Register 5      | Туре           |      |          |                                              | ı    | 'n  |          |          |          |  |  |

#### Table 5MDU Register Overview (cont'd)

# 3.2.4.3 CORDIC Registers

The CORDIC SFRs can be accessed in the mapped memory area (RMAP = 1).

#### Table 6 CORDIC Register Overview

|                                                                  | 5                                |                                        |       |       |   |    |     |   |   |   |  |  |

|------------------------------------------------------------------|----------------------------------|----------------------------------------|-------|-------|---|----|-----|---|---|---|--|--|

| Addr                                                             | Register Name                    | Bit                                    | 7     | 6     | 5 | 4  | 3   | 2 | 1 | 0 |  |  |

| RMAP =                                                           | = 1                              |                                        |       |       |   |    |     |   |   |   |  |  |

| 9A <sub>H</sub>                                                  | CD_CORDXL Reset: 00 <sub>H</sub> | Bit Field                              | DATAL |       |   |    |     |   |   |   |  |  |

|                                                                  | CORDIC X Data Low Byte           | Туре                                   | rw    |       |   |    |     |   |   |   |  |  |

| 9B <sub>H</sub> CD_CORDXH Reset: 00 <sub>H</sub> Bit Field DATAH |                                  |                                        |       |       |   |    |     |   |   |   |  |  |

|                                                                  | CORDIC X Data High Byte          | Туре                                   | rw    |       |   |    |     |   |   |   |  |  |

| 9C <sub>H</sub>                                                  | CD_CORDYL Reset: 00 <sub>H</sub> | Bit Field                              |       | DATAL |   |    |     |   |   |   |  |  |

|                                                                  | CORDIC Y Data Low Byte           | Туре                                   | rw    |       |   |    |     |   |   |   |  |  |

| 9D <sub>H</sub>                                                  | CD_CORDYH Reset: 00 <sub>H</sub> | Bit Field                              |       |       |   | DA | TAH |   |   |   |  |  |

|                                                                  | CORDIC Y Data High Byte          | Туре                                   |       |       |   | r  | w   |   |   |   |  |  |

| 9E <sub>H</sub>                                                  | CD_CORDZL Reset: 00 <sub>H</sub> | Reset: 00 <sub>H</sub> Bit Field DATAL |       |       |   |    |     |   |   |   |  |  |

|                                                                  | CORDIC Z Data Low Byte           | Туре                                   | rw    |       |   |    |     |   |   |   |  |  |

| Table 9Port Register Overview (cont'd) |         |        |     |   |   |   |  |  |

|----------------------------------------|---------|--------|-----|---|---|---|--|--|

| Addr                                   | Registe | r Name | Bit | 7 | 6 | 5 |  |  |

| Addr            | Register Name                                                         | Bit       | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-----------------|-----------------------------------------------------------------------|-----------|----|----|----|----|----|----|----|----|

| 93 <sub>H</sub> | P5_ALTSEL1 Reset: 00 <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P5 Alternate Select 1 Register                                        | Туре      | rw |

| во <sub>Н</sub> | P3_ALTSEL0 Reset: 00 <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P3 Alternate Select 0 Register                                        | Туре      | rw |

| в1 <sub>Н</sub> | P3_ALTSEL1 Reset: 00 <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P3 Alternate Select 1 Register                                        | Туре      | rw |

| C8 <sub>H</sub> | H P4_ALTSEL0 Reset: 00 <sub>H</sub><br>P4 Alternate Select 0 Register | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 |                                                                       | Туре      | rw |

| C9 <sub>H</sub> | P4_ALTSEL1 Reset: 00 <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P4 Alternate Select 1 Register                                        | Туре      | rw |

| RMAP =          | = 0, PAGE 3                                                           |           |    |    |    |    |    |    |    |    |

| 80 <sub>H</sub> | P0_OD Reset: 00 <sub>H</sub>                                          | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P0 Open Drain Control Register                                        | Туре      | rw |

| 90 <sub>H</sub> | P1_OD Reset: 00 <sub>H</sub>                                          | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P1 Open Drain Control Register                                        | Туре      | rw |

| 92 <sub>H</sub> | P5_OD Reset: 00 <sub>H</sub>                                          | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P5 Open Drain Control Register                                        | Туре      | rw |

| в0 <sub>Н</sub> | P3_OD Reset: 00 <sub>H</sub>                                          | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P3 Open Drain Control Register                                        | Туре      | rw |

| C8 <sub>H</sub> | P4_OD Reset: 00 <sub>H</sub>                                          | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P4 Open Drain Control Register                                        | Туре      | rw |

## 3.2.4.7 ADC Registers

The ADC SFRs can be accessed in the standard memory area (RMAP = 0).

| Addr            | Register Name                                                                        | Bit       | 7         | 6         | 5  | 4     | 3    | 2     | 1          | 0     |

|-----------------|--------------------------------------------------------------------------------------|-----------|-----------|-----------|----|-------|------|-------|------------|-------|

| RMAP =          | -                                                                                    | 1         |           | -         | -  |       | -    |       |            |       |

| D1 <sub>H</sub> |                                                                                      |           | C         | P         | ST | NR    | 0    |       | PAGE       |       |

|                 | Page Register                                                                        | Туре      | ١         | V         | ١  | w     |      |       | rw         |       |

| RMAP =          | = 0, PAGE 0                                                                          |           |           |           |    |       |      |       |            |       |

| са <sub>Н</sub> | CA <sub>H</sub> ADC_GLOBCTR Reset: 30 <sub>H</sub>                                   |           | ANON      | DW        | C. | CTC 0 |      |       |            |       |

|                 | Global Control Register                                                              | Туре      | rw        | rw        | r  | w     | r    |       |            |       |

| св <sub>Н</sub> | ADC_GLOBSTR Reset: 00 <sub>H</sub><br>Global Status Register                         | Bit Field | (         | )         |    | CHNR  |      | 0     | SAMP<br>LE | BUSY  |

|                 |                                                                                      | Type r rh |           |           | r  | rh    | rh   |       |            |       |

| cc <sup>H</sup> | CC <sub>H</sub> ADC_PRAR Reset: 00 <sub>H</sub><br>Priority and Arbitration Register |           | ASEN<br>1 | ASEN<br>0 | 0  | ARBM  | CSM1 | PRIO1 | CSM0       | PRIO0 |

|                 |                                                                                      |           | rw        | rw        | r  | rw    | rw   | rw    | rw         | rw    |

#### Table 10ADC Register Overview (cont'd)

| Addr            | Register Name                                                          | Bit       | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |  |

|-----------------|------------------------------------------------------------------------|-----------|------------|------------|------------|------------|------------|------------|------------|------------|--|

| cc <sup>H</sup> | ADC_CHINSR Reset: 00 <sub>H</sub><br>Channel Interrupt Set Register    | Bit Field | CHINS<br>7 | CHINS<br>6 | CHINS<br>5 | CHINS<br>4 | CHINS<br>3 | CHINS<br>2 | CHINS<br>1 | CHINS<br>0 |  |

|                 |                                                                        | Туре      | w          | w          | w          | w          | w          | w          | w          | w          |  |

| CD <sub>H</sub> | ADC_CHINPR Reset: 00 <sub>H</sub><br>Channel Interrupt Node Pointer    | Bit Field | CHINP<br>7 | CHINP<br>6 | CHINP<br>5 | CHINP<br>4 | CHINP<br>3 | CHINP<br>2 | CHINP<br>1 | CHINP<br>0 |  |

|                 | Register                                                               | Туре      | rw         |  |

| Ceh             | ADC_EVINFR Reset: 00 <sub>H</sub><br>Event Interrupt Flag Register     | Bit Field | EVINF<br>7 | EVINF<br>6 | EVINF<br>5 | EVINF<br>4 | (          | )          | EVINF<br>1 | EVINF<br>0 |  |

|                 |                                                                        | Туре      | rh         | rh         | rh         | rh         |            | r          | rh         | rh         |  |

| CF <sub>H</sub> | ADC_EVINCR Reset: 00 <sub>H</sub><br>Event Interrupt Clear Flag        | Bit Field | EVINC<br>7 | EVINC<br>6 | EVINC<br>5 | EVINC<br>4 | (          | D          | EVINC<br>1 | EVINC<br>0 |  |

|                 | Register                                                               | Туре      | w          | w          | w          | w          |            | r          | w          | w          |  |

| D2 <sub>H</sub> | ADC_EVINSR Reset: 00 <sub>H</sub><br>Event Interrupt Set Flag Register | Bit Field | EVINS<br>7 | EVINS<br>6 | EVINS<br>5 | EVINS<br>4 | (          | D          | EVINS<br>1 | EVINS<br>0 |  |

|                 |                                                                        | Туре      | w          | w          | w          | w          |            | r          | w          | w          |  |

| D3 <sub>H</sub> | ADC_EVINPR Reset: 00 <sub>H</sub><br>Event Interrupt Node Pointer      | Bit Field | EVINP<br>7 | EVINP<br>6 | EVINP<br>5 | EVINP<br>4 | (          | 0          | EVINP<br>1 | EVINP<br>0 |  |

|                 | Register                                                               | Туре      | rw         | rw         | rw         | rw         | r rw rv    |            |            |            |  |

| RMAP =          | = 0, PAGE 6                                                            |           |            |            |            |            |            |            |            |            |  |

| CAH             | ADC_CRCR1 Reset: 00 <sub>H</sub>                                       | Bit Field | CH7        | CH6        | CH5        | CH4        |            | 0          |            |            |  |

|                 | Conversion Request Control<br>Register 1                               | Туре      | rwh        | rwh        | rwh        | rwh        |            | I          | r          |            |  |

| св <sub>н</sub> | ADC_CRPR1 Reset: 00 <sub>H</sub>                                       | Bit Field | CHP7       | CHP6       | CHP5       | CHP4       |            | (          | )          |            |  |

|                 | Conversion Request Pending<br>Register 1                               | Туре      | rwh        | rwh        | rwh        | rwh        |            |            | r          |            |  |

| сс <sup>н</sup> | ADC_CRMR1 Reset: 00 <sub>H</sub><br>Conversion Request Mode            | Bit Field | Rsv        | LDEV       | CLRP<br>ND | SCAN       | ENSI       | ENTR       | 0          | ENGT       |  |

|                 | Register 1                                                             | Туре      | r          | W          | w          | rw         | rw         | rw         | r          | rw         |  |

| CD <sub>H</sub> | ADC_QMR0 Reset: 00 <sub>H</sub><br>Queue Mode Register 0               | Bit Field | CEV        | TREV       | FLUS<br>H  | CLRV       | 0          | ENTR       | 0          | ENGT       |  |

|                 |                                                                        | Туре      | w          | w          | w          | w          | r          | rw         | r          | rw         |  |

| Ceh             | ADC_QSR0 Reset: 20 <sub>H</sub><br>Queue Status Register 0             | Bit Field | Rsv        | 0          | EMPT<br>Y  | EV         | (          | D          | FI         | LL         |  |

|                 |                                                                        | Туре      | r          | r          | rh         | rh         |            | r          | r          | h          |  |

| CF <sub>H</sub> | ADC_Q0R0 Reset: 00 <sub>H</sub>                                        | Bit Field | EXTR       | ENSI       | RF         | V          | 0          | F          | REQCHN     | २          |  |

|                 | Queue 0 Register 0                                                     | Туре      | rh         | rh         | rh         | rh         | r          |            | rh         |            |  |

| D2 <sub>H</sub> | ADC_QBUR0 Reset: 00 <sub>H</sub>                                       | Bit Field | EXTR       | ENSI       | RF         | V          | 0          | F          | REQCHN     | २          |  |

|                 | Queue Backup Register 0                                                | Туре      | rh         | rh         | rh         | rh         | r          |            | rh         |            |  |

| D2 <sub>H</sub> | ADC_QINR0 Reset: 00 <sub>H</sub>                                       | Bit Field | EXTR       | ENSI       | RF         | (          | )          | F          | REQCHN     | २          |  |

|                 | Queue Input Register 0                                                 | Туре      | w          | w          | w          |            | r          |            | w          |            |  |

## Table 13 CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                                        | Bit       | 7          | 6          | 5          | 4          | 3          | 2          | 1           | 0           |  |

|-----------------|--------------------------------------------------------------------------------------|-----------|------------|------------|------------|------------|------------|------------|-------------|-------------|--|

| FB <sub>H</sub> | CCU6_CC60RH Reset: 00 <sub>H</sub>                                                   | Bit Field |            |            | <u> </u>   | CC6        | 60VH       |            |             |             |  |

|                 | Capture/Compare Register for<br>Channel CC60 High                                    | Туре      | rh         |            |            |            | h          |            |             |             |  |

| FC <sub>H</sub> | CCU6_CC61RL Reset: 00 <sub>H</sub>                                                   | Bit Field |            |            |            | CCe        | 61VL       |            |             |             |  |

|                 | Capture/Compare Register for<br>Channel CC61 Low                                     | Туре      |            |            |            | r          | h          |            |             |             |  |

| FD <sub>H</sub> | CCU6_CC61RH Reset: 00 <sub>H</sub>                                                   | Bit Field |            |            |            | CC6        | 51VH       |            |             |             |  |

|                 | Capture/Compare Register for<br>Channel CC61 High                                    | Туре      |            |            |            | r          | h          |            |             |             |  |

| Fe <sub>H</sub> | CCU6_CC62RL Reset: 00 <sub>H</sub>                                                   | Bit Field |            |            |            | CCe        | 62VL       |            |             |             |  |

|                 | Capture/Compare Register for<br>Channel CC62 Low                                     | Туре      |            |            |            | r          | h          |            |             |             |  |

| FF <sub>H</sub> | CCU6_CC62RH Reset: 00 <sub>H</sub>                                                   | Bit Field |            |            |            | CC6        | 2VH        |            |             |             |  |

|                 | Capture/Compare Register for<br>Channel CC62 High                                    | Туре      |            |            |            | r          | h          |            |             |             |  |

| RMAP =          | = 0, PAGE 2                                                                          |           |            |            |            |            |            |            |             |             |  |

| 9A <sub>H</sub> | CCU6_T12MSELL Reset: 00 <sub>H</sub><br>T12 Capture/Compare Mode Select              | Bit Field |            | MSI        | EL61       |            |            | MSE        | EL60        |             |  |

|                 | Register Low                                                                         | Туре      |            | r          | W          |            |            | r          | w           |             |  |

| 9B <sub>H</sub> | CCU6_T12MSELH Reset: 00 <sub>H</sub>                                                 | Bit Field | DBYP       |            | HSYNC      |            | MSEL62     |            |             |             |  |

|                 | T12 Capture/Compare Mode Select<br>Register High                                     | Туре      | rw         | rw         |            |            | rw         |            |             |             |  |

| 9CH             | CCU6_IENL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Enable<br>Register Low | Bit Field | ENT1       | ENT1       | ENCC       | ENCC       | ENCC       | ENCC       | ENCC        | ENCC        |  |

|                 |                                                                                      |           | 2<br>PM    | 2<br>OM    | 62F        | 62R        | 61F        | 61R        | 60F         | 60R         |  |

|                 |                                                                                      | Туре      | rw          | rw          |  |

| 9D <sub>H</sub> | CCU6_IENH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Enable                 | Bit Field | EN<br>STR  | EN<br>IDLE | EN<br>WHE  | EN<br>CHE  | 0          | EN<br>TRPF | ENT1<br>3PM | ENT1<br>3CM |  |

|                 | Register High                                                                        | Туре      | rw         | rw         | rw         | rw         | r          | rw         | rw          | rw          |  |

| 9EH             | CCU6_INPL Reset: 40 <sub>H</sub><br>Capture/Compare Interrupt Node                   | Bit Field | INP        | INPCHE IN  |            | INPCC62    |            | INPCC61    |             | INPCC60     |  |

|                 | Pointer Register Low                                                                 | Туре      | r          | w          | r          | w          | rw         |            | rw          |             |  |

| 9F <sub>H</sub> | CCU6_INPH Reset: 39 <sub>H</sub><br>Capture/Compare Interrupt Node                   | Bit Field | (          | 0          | INPT13     |            | INPT12     |            | INPERR      |             |  |

|                 | Pointer Register High                                                                | Туре      |            | r          | r          | w          | r          | w          | r           | w           |  |

| A4 <sub>H</sub> | CCU6_ISSL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status                 | Bit Field | ST12<br>PM | ST12<br>OM | SCC6<br>2F | SCC6<br>2R | SCC6<br>1F | SCC6<br>1R | SCC6<br>0F  | SCC6<br>0R  |  |

|                 | Set Register Low                                                                     | Туре      | w          | w          | w          | w          | w          | w          | w           | w           |  |

| A5 <sub>H</sub> | CCU6_ISSH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status                 | Bit Field | SSTR       | SIDLE      | SWHE       | SCHE       | SWH<br>C   | STRP<br>F  | ST13<br>PM  | ST13<br>CM  |  |

|                 | Set Register High                                                                    | Туре      | w          | w          | w          | w          | w          | w          | w           | w           |  |

| A6 <sub>H</sub> | CCU6_PSLR Reset: 00 <sub>H</sub><br>Passive State Level Register                     | Bit Field | PSL63      | 0          |            |            | P          | SL         |             |             |  |

|                 | , , , , , , , , , , , , , , , , , , ,                                                | Туре      |            |            | vh         |            |            |            |             |             |  |

| <sup>А7</sup> Н | CCU6_MCMCTR Reset: 00 <sub>H</sub><br>Multi-Channel Mode Control Register            | Bit Field |            | 0          | SW         | SYN        | 0          |            | SWSEL       |             |  |

|                 |                                                                                      | Туре      |            | r          | 1          | w          | r          | r rw       |             |             |  |

| FA <sub>H</sub> | CCU6_TCTR2L Reset: 00 <sub>H</sub><br>Timer Control Register 2 Low                   | Bit Field | 0          | T13        | TED        |            | T13TEC     |            | T13<br>SSC  | T12<br>SSC  |  |

|                 |                                                                                      | Туре      | r          | r          | W          |            | rw         |            | rw          | rw          |  |

## 3.2.4.12 SSC Registers

The SSC SFRs can be accessed in the standard memory area (RMAP = 0).

| Addr            | Register Name                             | Bit       | 7             | 6  | 5  | 4    | 3    | 2   | 1   | 0   |  |

|-----------------|-------------------------------------------|-----------|---------------|----|----|------|------|-----|-----|-----|--|

| RMAP =          | = 0                                       |           |               |    |    |      |      |     |     |     |  |

| A9 <sub>H</sub> | SSC_PISEL Reset: 00 <sub>H</sub>          | Bit Field |               |    | 0  |      |      | CIS | SIS | MIS |  |

|                 | Port Input Select Register                | Туре      |               |    | r  |      |      | rw  | rw  | rw  |  |

| AA <sub>H</sub> | SSC_CONL Reset: 00 <sub>H</sub>           | Bit Field | LB            | PO | PH | HB   |      | В   | М   |     |  |

|                 | Control Register Low<br>Programming Mode  | Туре      | rw            | rw | rw | rw   |      | r   | w   |     |  |

| аа <sub>Н</sub> | SSC_CONL Reset: 00 <sub>H</sub>           | Bit Field |               | (  | C  |      |      | В   | C   |     |  |

|                 | Control Register Low<br>Operating Mode    | Туре      |               | r  |    |      | rh   |     |     |     |  |

| ab <sub>h</sub> | SSC_CONH Reset: 00 <sub>H</sub>           | Bit Field | EN            | MS | 0  | AREN | BEN  | PEN | REN | TEN |  |

|                 | Control Register High<br>Programming Mode |           | rw            | rw | r  | rw   | rw   | rw  | rw  | rw  |  |

| ав <sub>Н</sub> | SSC_CONH Reset: 00 <sub>H</sub>           | Bit Field | EN            | MS | 0  | BSY  | BE   | PE  | RE  | TE  |  |

|                 | Control Register High<br>Operating Mode   | Туре      | rw            | rw | r  | rh   | rwh  | rwh | rwh | rwh |  |

| ас <sub>Н</sub> | SSC_TBL Reset: 00 <sub>H</sub>            | Bit Field |               |    |    | TB_V | ALUE |     |     |     |  |

|                 | Transmitter Buffer Register Low           | Туре      |               |    |    | r    | N    |     |     |     |  |

| ad <sub>H</sub> | SSC_RBL Reset: 00 <sub>H</sub>            | Bit Field |               |    |    | RB_V | ALUE |     |     |     |  |

|                 | Receiver Buffer Register Low              | Туре      | rh            |    |    |      |      |     |     |     |  |

| ае <sub>Н</sub> | SSC_BRL Reset: 00 <sub>H</sub>            | Bit Field | Field BR_VALU |    |    |      | ALUE |     |     |     |  |

|                 | Baud Rate Timer Reload<br>Register Low    | Туре      | rw            |    |    |      |      |     |     |     |  |

| AF <sub>H</sub> | SSC_BRH Reset: 00 <sub>H</sub>            | Bit Field |               |    |    | BR_V | ALUE |     |     |     |  |

|                 | Baud Rate Timer Reload<br>Register High   | Туре      |               |    |    | n    | N    |     |     |     |  |

#### Table 15 SSC Register Overview

## 3.2.4.13 MultiCAN Registers

The MultiCAN SFRs can be accessed in the standard memory area (RMAP = 0).

| Table 16 | CAN Register Overview |

|----------|-----------------------|

|----------|-----------------------|

| Addr            | Register Name                        | Bit       | 7   | 6   | 5   | 4   | 3    | 2    | 1    | 0    |

|-----------------|--------------------------------------|-----------|-----|-----|-----|-----|------|------|------|------|

| RMAP =          | 0                                    |           |     |     |     |     |      |      |      |      |

| D8 <sub>H</sub> | ADCON Reset: 00 <sub>H</sub>         | Bit Field | V3  | V2  | V1  | V0  | AU   | AD   | BSY  | RWEN |

|                 | CAN Address/Data Control<br>Register | Туре      | rw  | rw  | rw  | rw  | rw   |      | rh   | rw   |

| D9 <sub>H</sub> | ADL Reset: 00 <sub>H</sub>           | Bit Field | CA9 | CA8 | CA7 | CA6 | CA5  | CA4  | CA3  | CA2  |

|                 | CAN Address Register Low             | Туре      | rwh | rwh | rwh | rwh | rwh  | rwh  | rwh  | rwh  |

| da <sub>H</sub> | ADH Reset: 00 <sub>H</sub>           | Bit Field |     | (   | )   |     | CA13 | CA12 | CA11 | CA10 |

|                 | CAN Address Register High            | Туре      |     | l   | r   |     | rwh  | rwh  | rwh  | rwh  |

## SAL-XC886CLM

#### **Functional Description**

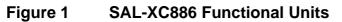

Figure 13 Interrupt Request Sources (Part 1)

## 3.4.3 Interrupt Priority

An interrupt that is currently being serviced can only be interrupted by a higher-priority interrupt, but not by another interrupt of the same or lower priority. Hence, an interrupt of the highest priority cannot be interrupted by any other interrupt request.

If two or more requests of different priority levels are received simultaneously, the request of the highest priority is serviced first. If requests of the same priority are received simultaneously, then an internal polling sequence determines which request is serviced first. Thus, within each priority level, there is a second priority structure determined by the polling sequence shown in **Table 20**.

| Source                                                                                         | Level     |  |  |  |  |  |

|------------------------------------------------------------------------------------------------|-----------|--|--|--|--|--|

| Non-Maskable Interrupt (NMI)                                                                   | (highest) |  |  |  |  |  |

| External Interrupt 0                                                                           | 1         |  |  |  |  |  |

| Timer 0 Interrupt                                                                              | 2         |  |  |  |  |  |

| External Interrupt 1                                                                           | 3         |  |  |  |  |  |

| Timer 1 Interrupt                                                                              | 4         |  |  |  |  |  |

| UART Interrupt                                                                                 | 5         |  |  |  |  |  |

| Timer 2,UART Normal Divider Overflow,<br>MultiCAN, LIN Interrupt                               | 6         |  |  |  |  |  |

| ADC, MultiCAN Interrupt                                                                        | 7         |  |  |  |  |  |

| SSC Interrupt                                                                                  | 8         |  |  |  |  |  |

| External Interrupt 2, Timer 21, UART1, UART1<br>Normal Divider Overflow, MDU, CORDIC Interrupt | 9         |  |  |  |  |  |

| External Interrupt [6:3], MultiCAN Interrupt                                                   | 10        |  |  |  |  |  |

| CCU6 Interrupt Node Pointer 0, MultiCAN interrupt                                              | 11        |  |  |  |  |  |

| CCU6 Interrupt Node Pointer 1, MultiCAN Interrupt                                              | 12        |  |  |  |  |  |

| CCU6 Interrupt Node Pointer 2, MultiCAN Interrupt                                              | 13        |  |  |  |  |  |

| CCU6 Interrupt Node Pointer 3, MultiCAN Interrupt                                              | 14        |  |  |  |  |  |

#### Table 20 Priority Structure within Interrupt Level

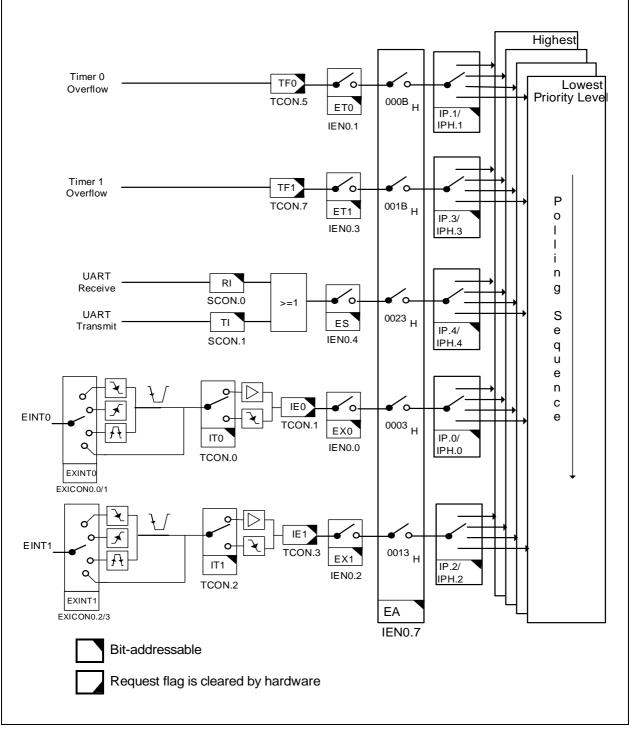

#### Figure 22 $V_{\text{DDP}}$ , $V_{\text{DDC}}$ and $V_{\text{RESET}}$ during Power-on Reset

The second type of reset in SAL-XC886 is the hardware reset. This reset function can be used during normal operation or when the chip is in power-down mode. A reset input pin RESET is provided for the hardware reset.

The Watchdog Timer (WDT) module is also capable of resetting the device if it detects a malfunction in the system.

Another type of reset that needs to be detected is a reset while the device is in power-down mode (wake-up reset). While the contents of the static RAM are undefined after a power-on reset, they are well defined after a wake-up reset from power-down mode.

## 3.11 Multiplication/Division Unit

The Multiplication/Division Unit (MDU) provides fast 16-bit multiplication, 16-bit and 32-bit division as well as shift and normalize features. It has been integrated to support the SAL-XC886 Core in real-time control applications, which require fast mathematical computations.

#### Features

- Fast signed/unsigned 16-bit multiplication

- Fast signed/unsigned 32-bit divide by 16-bit and 16-bit divide by 16-bit operations

- 32-bit unsigned normalize operation

- 32-bit arithmetic/logical shift operations

Table 27 specifies the number of clock cycles used for calculation in various operations.

| Operation                | Result | Remainder | No. of Clock Cycles<br>used for calculation |  |  |  |

|--------------------------|--------|-----------|---------------------------------------------|--|--|--|

| Signed 32-bit/16-bit     | 32-bit | 16-bit    | 33                                          |  |  |  |

| Signed 16-bit/16bit      | 16-bit | 16-bit    | 17                                          |  |  |  |

| Signed 16-bit x 16-bit   | 32-bit | -         | 16                                          |  |  |  |

| Unsigned 32-bit/16-bit   | 32-bit | 16-bit    | 32                                          |  |  |  |

| Unsigned 16-bit/16-bit   | 16-bit | 16-bit    | 16                                          |  |  |  |

| Unsigned 16-bit x 16-bit | 32-bit | -         | 16                                          |  |  |  |

| 32-bit normalize         | -      | -         | No. of shifts + 1 (Max. 32)                 |  |  |  |

| 32-bit shift L/R         | -      | -         | No. of shifts + 1 (Max. 32)                 |  |  |  |

Table 27

MDU Operation Characteristics

| Table 30   | Deviation Error for          | UAR I with Fractio             | nal Divider enal       | bled               |

|------------|------------------------------|--------------------------------|------------------------|--------------------|

| $f_{PCLK}$ | Prescaling Factor<br>(BRPRE) | Reload Value<br>(BR_VALUE + 1) | STEP                   | Deviation<br>Error |

| 20 MHz     | 1                            | 10 (A <sub>H</sub> )           | 230 (E6 <sub>H</sub> ) | +0.03 %            |

| 10 MHz     | 1                            | 5 (5 <sub>H</sub> )            | 230 (E6 <sub>H</sub> ) | +0.03 %            |

| 6.67 MHz   | 1                            | 3 (3 <sub>H</sub> )            | 212 (D4 <sub>H</sub> ) | -0.16 %            |

| 5 MHz      | 1                            | 2 (2 <sub>H</sub> )            | 189 (BD <sub>H</sub> ) | +0.14 %            |

#### war far IIADT with Freetianal Division and blad -61- 20

#### 3.13.2 **Baud Rate Generation using Timer 1**

In UART modes 1 and 3 of UART module, Timer 1 can be used for generating the variable baud rates. In theory, this timer could be used in any of its modes. But in practice, it should be set into auto-reload mode (Timer 1 mode 2), with its high byte set to the appropriate value for the required baud rate. The baud rate is determined by the Timer 1 overflow rate and the value of SMOD as follows:

Mode 1, 3 baud rate =

$$\frac{2^{\text{SMOD}} \times f_{\text{PCLK}}}{32 \times 2 \times (256 - \text{TH1})}$$

(3.7)

#### 3.14 Normal Divider Mode (8-bit Auto-reload Timer)

Setting bit FDM in register FDCON to 1 configures the fractional divider to normal divider mode, while at the same time disables baud rate generation (see Figure 29). Once the fractional divider is enabled (FDEN = 1), it functions as an 8-bit auto-reload timer (with no relation to baud rate generation) and counts up from the reload value with each input clock pulse. Bit field RESULT in register FDRES represents the timer value, while bit field STEP in register FDSTEP defines the reload value. At each timer overflow, an overflow flag (FDCON.NDOV) will be set and an interrupt request generated. This gives an output clock f<sub>MOD</sub> that is 1/n of the input clock f<sub>DIV</sub>, where n is defined by 256 - STEP. The output frequency in normal divider mode is derived as follows:

$$f_{MOD} = f_{DIV} \times \frac{1}{256 - STEP}$$

(3.8)

## SAL-XC886CLM

#### **Functional Description**

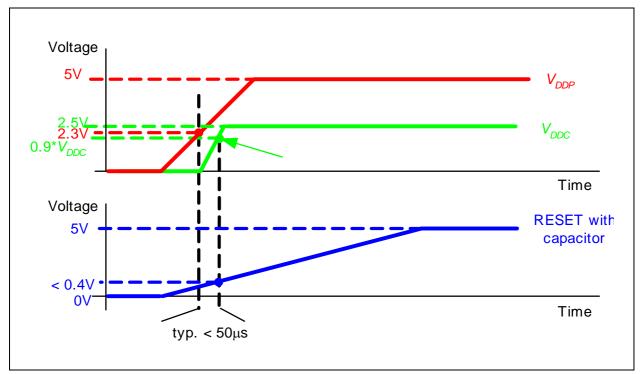

Figure 32 CCU6 Block Diagram

- CAN functionality according to CAN specification V2.0 B active.

- Dedicated control registers are provided for each CAN node.

- A data transfer rate up to 1 MBaud is supported.

- Flexible and powerful message transfer control and error handling capabilities are implemented.

- Advanced CAN bus bit timing analysis and baud rate detection can be performed for each CAN node via the frame counter.

- Full-CAN functionality: A set of 32 message objects can be individually

- allocated (assigned) to any CAN node

- configured as transmit or receive object

- setup to handle frames with 11-bit or 29-bit identifier

- counted or assigned a timestamp via a frame counter

- configured to remote monitoring mode

- Advanced Acceptance Filtering:

- Each message object provides an individual acceptance mask to filter incoming frames.

- A message object can be configured to accept only standard or only extended frames or to accept both standard and extended frames.

- Message objects can be grouped into 4 priority classes.

- The selection of the message to be transmitted first can be performed on the basis of frame identifier, IDE bit and RTR bit according to CAN arbitration rules.

- Advanced Message Object Functionality:

- Message Objects can be combined to build FIFO message buffers of arbitrary size, which is only limited by the total number of message objects.

- Message objects can be linked to form a gateway to automatically transfer frames between 2 different CAN buses. A single gateway can link any two CAN nodes. An arbitrary number of gateways may be defined.

- Advanced Data Management:

- The Message objects are organized in double chained lists.

- List reorganizations may be performed any time, even during full operation of the CAN nodes.

- A powerful, command driven list controller manages the organization of the list structure and ensures consistency of the list.

- Message FIFOs are based on the list structure and can easily be scaled in size during CAN operation.

- Static Allocation Commands offer compatibility with TwinCAN applications, which are not list based.

- Advanced Interrupt Handling:

- Up to 8 interrupt output lines are available. Most interrupt requests can be individually routed to one of the 8 interrupt output lines.

- Message postprocessing notifications can be flexibly aggregated into a dedicated register field of 64 notification bits.

10 MHz. However, it is important to note that the conversion error could increase due to loss of charges on the capacitors, if  $f_{ADC}$  becomes too low during slow-down mode.

#### 3.21.2 ADC Conversion Sequence

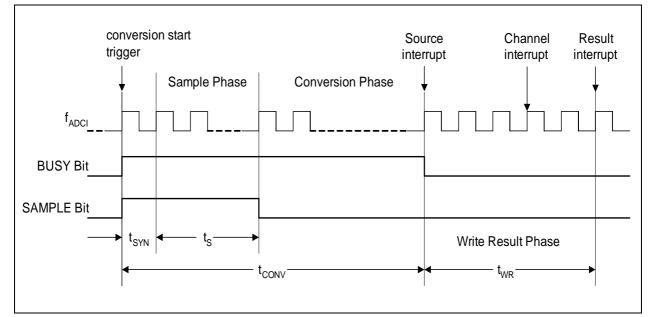

The analog-to-digital conversion procedure consists of the following phases:

- Synchronization phase (t<sub>SYN</sub>)

- Sample phase  $(t_S)$

- Conversion phase

- Write result phase (*t*<sub>WR</sub>)

Figure 35 ADC Conversion Timing

#### **Electrical Parameters**

#### 4.2 DC Parameters

The electrical characteristics of the DC Parameters are detailed in this section.

#### 4.2.1 Input/Output Characteristics

Table 38 provides the characteristics of the input/output pins of the SAL-XC886.

| Table 38 Input/Output Characteristics (Operating Conditions apply) |

|--------------------------------------------------------------------|

|--------------------------------------------------------------------|

| Parameter                                                      | Symbol           |    | Limit                     | Values                 | Unit | Test Conditions                                             |  |  |

|----------------------------------------------------------------|------------------|----|---------------------------|------------------------|------|-------------------------------------------------------------|--|--|

|                                                                |                  |    | min.                      | min. max.              |      |                                                             |  |  |

| V <sub>DDP</sub> = 5 V Range                                   |                  |    |                           |                        |      | •                                                           |  |  |

| Output low voltage                                             | $V_{OL}$         | CC | _                         | 1.0                    | V    | I <sub>OL</sub> = 15 mA                                     |  |  |

|                                                                |                  |    | -                         | 1.0                    | V    | $I_{OL}$ = 5 mA, current into<br>all pins > 60 mA           |  |  |

|                                                                |                  |    | -                         | 0.4                    | V    | $I_{\rm OL}$ = 5 mA, current into all pins $\leq$ 60 mA     |  |  |

| Output high voltage                                            | V <sub>OH</sub>  | CC | V <sub>DDP</sub> -<br>1.0 | _                      | V    | I <sub>OH</sub> = -15 mA                                    |  |  |

|                                                                |                  |    | V <sub>DDP</sub> -<br>1.0 | -                      | V    | $I_{OH}$ = -5 mA, current<br>from all pins > 60 mA          |  |  |

|                                                                |                  |    | V <sub>DDP</sub> -<br>0.4 | -                      | V    | $I_{\rm OH}$ = -5 mA, current<br>from all pins $\leq$ 60 mA |  |  |

| Input low voltage on<br>port pins<br>(all except P0.0 & P0.1)  | V <sub>ILP</sub> | SR | -                         | $0.3 	imes V_{ m DDP}$ | V    | CMOS Mode                                                   |  |  |

| Input low voltage on<br>P0.0 & P0.1                            | $V_{ILP0}$       | SR | -0.2                      | $0.3 	imes V_{ m DDP}$ | V    | CMOS Mode                                                   |  |  |

| Input low voltage on RESET pin                                 | $V_{ILR}$        | SR | -                         | $0.3 	imes V_{ m DDP}$ | V    | CMOS Mode                                                   |  |  |

| Input low voltage on<br>TMS pin                                | $V_{ILT}$        | SR | -                         | $0.3 	imes V_{ m DDP}$ | V    | CMOS Mode                                                   |  |  |

| Input high voltage on<br>port pins<br>(all except P0.0 & P0.1) | V <sub>IHP</sub> | SR | $0.7 	imes V_{ m DDP}$    | -                      | V    | CMOS Mode                                                   |  |  |

| Input high voltage on<br>P0.0 & P0.1                           | $V_{IHP0}$       | SR | $0.7 	imes V_{ m DDP}$    | $V_{DDP}$              | V    | CMOS Mode                                                   |  |  |

#### SAL-XC886CLM

#### **Electrical Parameters**

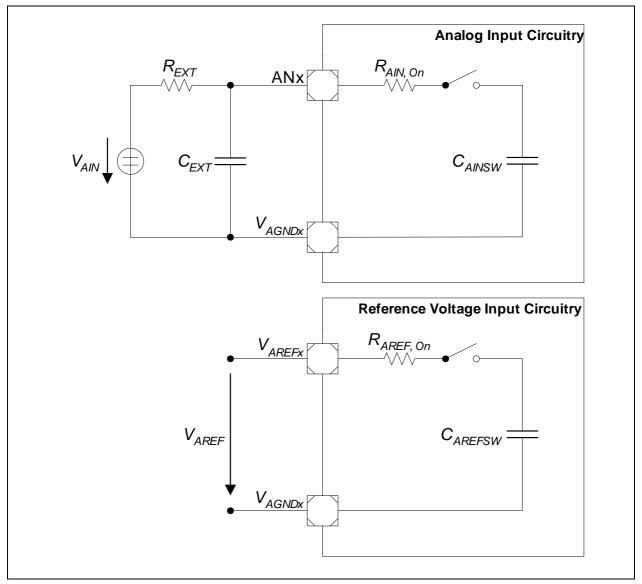

Figure 38 ADC Input Circuits

#### **Electrical Parameters**

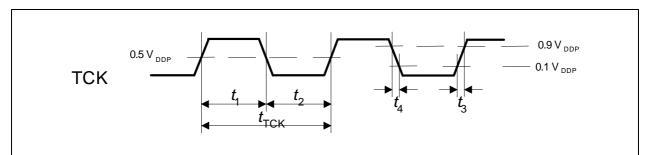

#### 4.3.6 JTAG Timing

Table 47 provides the characteristics of the JTAG timing in the SAL-XC886.

#### Table 47TCK Clock Timing (Operating Conditions apply; CL = 50 pF)

| Parameter           | Sym                   | Symbol |     | nits | Unit | Test Conditions |  |

|---------------------|-----------------------|--------|-----|------|------|-----------------|--|

|                     |                       |        | min | max  |      |                 |  |

| TCK clock period    | t <sub>TCK</sub>      | SR     | 50  | -    | ns   | 1)              |  |

| TCK high time       | <i>t</i> <sub>1</sub> | SR     | 20  | _    | ns   | 1)              |  |

| TCK low time        | <i>t</i> <sub>2</sub> | SR     | 20  | -    | ns   | 1)              |  |

| TCK clock rise time | <i>t</i> <sub>3</sub> | SR     | -   | 4    | ns   | 1)              |  |

| TCK clock fall time | <i>t</i> <sub>4</sub> | SR     | -   | 4    | ns   | 1)              |  |

1) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

Figure 45 TCK Clock Timing

#### Table 48JTAG Timing (Operating Conditions apply; CL = 50 pF)

| Parameter                 | Symbol                |    | Lir | nits | Unit | Test       |  |

|---------------------------|-----------------------|----|-----|------|------|------------|--|

|                           |                       |    | min | max  |      | Conditions |  |

| TMS setup to TCK          | t <sub>1</sub>        | SR | 8   | -    | ns   | 1)         |  |

| TMS hold to TCK           | <i>t</i> <sub>2</sub> | SR | 24  | -    | ns   | 1)         |  |

| TDI setup to TCK          | t <sub>1</sub>        | SR | 11  | -    | ns   | 1)         |  |

| TDI hold to TCK           | <i>t</i> <sub>2</sub> | SR | 24  | -    | ns   | 1)         |  |

| TDO valid output from TCK | <i>t</i> <sub>3</sub> | CC | -   | 27   | ns   | 1)         |  |