Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Discontinued at Digi-Key                                                          |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | XC800                                                                             |

| Core Size                  | 8-Bit                                                                             |

| Speed                      | 24MHz                                                                             |

| Connectivity               | CANbus, LINbus, SSI, UART/USART                                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 34                                                                                |

| Program Memory Size        | 32KB (32K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 1.75K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                       |

| Data Converters            | A/D 8x10b                                                                         |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 48-LQFP                                                                           |

| Supplier Device Package    | PG-TQFP-48                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc886clm8ffa5vaclxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 4.3.3 | Power-on Reset and PLL Timing 11      | 17         |

|-------|---------------------------------------|------------|

| 4.3.4 | On-Chip Oscillator Characteristics 11 | 9          |

| 4.3.5 | External Clock Drive XTAL1 12         | 20         |

| 4.3.6 | JTAG Timing 12                        | 21         |

| 4.3.7 | SSC Master Mode Timing 12             | <u>23</u>  |

| 5     | Package and Quality Declaration 12    | 24         |

| 5.1   | Package Parameters 12                 | <u>2</u> 4 |

| 5.2   | Package Outline                       | 25         |

| 5.3   | Quality Declaration 12                | 26         |

#### **Summary of Features**

Features: (continued)

- Power-on reset generation

- Brownout detection for core logic supply

- On-chip OSC and PLL for clock generation

- PLL loss-of-lock detection

- Power saving modes

- slow-down mode

- idle mode

- power-down mode with wake-up capability via RXD or EXINT0

- clock gating control to each peripheral

- Programmable 16-bit Watchdog Timer (WDT)

- Six ports

- Up to 48 pins as digital I/O

- 8 pins as digital/analog input

- 8-channel, 10-bit ADC

- Four 16-bit timers

- Timer 0 and Timer 1 (T0 and T1)

- Timer 2 and Timer 21 (T2 and T21)

- Multiplication/Division Unit for arithmetic operations (MDU)

- Software libraries to support floating point and MDU calculations

- CORDIC Coprocessor for computation of trigonometric, hyperbolic and linear functions

- MultiCAN with 2 nodes, 32 message objects

- Capture/compare unit for PWM signal generation (CCU6)

- Two full-duplex serial interfaces (UART and UART1)

- Synchronous serial channel (SSC)

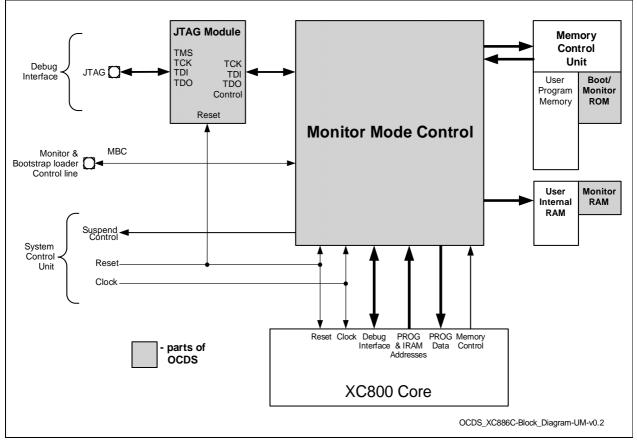

- On-chip debug support

- 1 Kbyte of monitor ROM (part of the 12-Kbyte Boot ROM)

- 64 bytes of monitor RAM

- Package:

- PG-TQFP-48

- Temperature range  $T_A$ :

- SAL (-40 to 150 °C)

## SAL-XC886CLM

## **General Device Information**

| Symbol | Pin Number | Туре | Reset<br>State | Function                                       |                                                                                                                                                              |

|--------|------------|------|----------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1     |            | I/O  |                | I/O port. It ca<br>for the JTAG                | B-bit bidirectional general purpose<br>an be used as alternate functions<br>5, CCU6, UART, Timer 0, Timer 1,<br>1, er 21, MultiCAN and SSC.                  |

| P1.0   | 26         |      | PU             | RXD_0<br>T2EX<br>RXDC0_0                       | UART Receive Data Input<br>Timer 2 External Trigger Input<br>MultiCAN Node 0 Receiver Input                                                                  |

| P1.1   | 27         |      | PU             | EXINT3<br>T0_1<br>TDO_1<br>TXD_0<br>TXDC0_0    | External Interrupt Input 3<br>Timer 0 Input<br>JTAG Serial Data Output<br>UART Transmit Data<br>Output/Clock Output<br>MultiCAN Node 0 Transmitter<br>Output |

| P1.2   | 28         |      | PU             | SCK_0                                          | SSC Clock Input/Output                                                                                                                                       |

| P1.3   | 29         |      | PU             | MTSR_0<br>TXDC1_3                              | SSC Master Transmit<br>Output/Slave Receive Input<br>MultiCAN Node 1 Transmitter<br>Output                                                                   |

| P1.4   | 30         |      | PU             | MRST_0<br>EXINT0_1<br>RXDC1_3                  | SSC Master Receive Input/<br>Slave Transmit Output<br>External Interrupt Input 0<br>MultiCAN Node 1 Receiver Input                                           |

| P1.5   | 31         |      | PU             | CCPOS0_1<br>EXINT5<br>T1_1<br>EXF2_0<br>RXDO_0 | CCU6 Hall Input 0<br>External Interrupt Input 5<br>Timer 1 Input<br>Timer 2 External Flag Output<br>UART Transmit Data Output                                |

## Table 2Pin Definitions and Functions (cont'd)

## **General Device Information**

| Symbol | Pin Number | Туре | Reset<br>State | Function                                                                                                                                                                                                           |                                                                                                                                                                             |  |  |  |

|--------|------------|------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| P2     |            | I    |                | <b>Port 2</b><br>Port 2 is an 8-bit general purpose input-only<br>port. It can be used as alternate functions for<br>the digital inputs of the JTAG and CCU6. It is<br>also used as the analog inputs for the ADC. |                                                                                                                                                                             |  |  |  |

| P2.0   | 14         |      | Hi-Z           | CCPOS0_0<br>EXINT1_0<br>T12HR_2<br>TCK_1<br>CC61_3<br>AN0                                                                                                                                                          | •                                                                                                                                                                           |  |  |  |

| P2.1   | 15         |      | Hi-Z           | CCPOS1_0<br>EXINT2_0<br>T13HR_2<br>TDI_1<br>CC62_3<br>AN1                                                                                                                                                          | CCU6 Hall Input 1<br>External Interrupt Input 2<br>CCU6 Timer 13 Hardware Run<br>Input<br>JTAG Serial Data Input<br>Input of Capture/Compare<br>channel 2<br>Analog Input 1 |  |  |  |

| P2.2   | 16         |      | Hi-Z           | CCPOS2_0<br>CTRAP_1<br>CC60_3<br>AN2                                                                                                                                                                               | CCU6 Hall Input 2<br>CCU6 Trap Input<br>Input of Capture/Compare<br>channel 0<br>Analog Input 2                                                                             |  |  |  |

| P2.3   | 19         |      | Hi-Z           | AN3                                                                                                                                                                                                                | Analog Input 3                                                                                                                                                              |  |  |  |

| P2.4   | 20         |      | Hi-Z           | AN4                                                                                                                                                                                                                | Analog Input 4                                                                                                                                                              |  |  |  |

| P2.5   | 21         |      | Hi-Z           | AN5                                                                                                                                                                                                                | Analog Input 5                                                                                                                                                              |  |  |  |

| P2.6   | 22         |      | Hi-Z           | AN6                                                                                                                                                                                                                | Analog Input 6                                                                                                                                                              |  |  |  |

| P2.7   | 25         |      | Hi-Z           | AN7                                                                                                                                                                                                                | Analog Input 7                                                                                                                                                              |  |  |  |

## Table 2Pin Definitions and Functions (cont'd)

## SAL-XC886CLM

## **General Device Information**

| Symbol | Pin Number | Туре | Reset<br>State | Function            |                                                                                                          |

|--------|------------|------|----------------|---------------------|----------------------------------------------------------------------------------------------------------|

| P4     |            | I/O  |                | I/O port. It ca     | 3-bit bidirectional general purpose<br>an be used as alternate functions<br>mer 0, Timer 1, Timer 21 and |

| P4.0   | 45         |      | Hi-Z           | RXDC0_3<br>CC60_1   | MultiCAN Node 0 Receiver Input<br>Output of Capture/Compare<br>channel 0                                 |

| P4.1   | 46         |      | Hi-Z           | TXDC0_3<br>COUT60_1 | MultiCAN Node 0 Transmitter<br>Output<br>Output of Capture/Compare<br>channel 0                          |

| P4.3   | 32         |      | Hi-Z           | EXF21_1<br>COUT63_2 | Timer 21 External Flag Output<br>Output of Capture/Compare<br>channel 3                                  |

## Table 2Pin Definitions and Functions (cont'd)

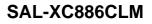

#### Figure 8 Address Extension by Paging

In order to access a register located in a page different from the actual one, the current page must be exited. This is done by reprogramming the bit field PAGE in the page register. Only then can the desired access be performed.

If an interrupt routine is initiated between the page register access and the module register access, and the interrupt needs to access a register located in another page, the current page setting can be saved, the new one programmed and the old page setting restored. This is possible with the storage fields STx (x = 0 - 3) for the save and restore action of the current page setting. By indicating which storage bit field should be used in parallel with the new page value, a single write operation can:

• Save the contents of PAGE in STx before overwriting with the new value (this is done in the beginning of the interrupt routine to save the current page setting and program the new page number); or

| Addr            | Register Name              | Bit       | 7  | 6        | 5                                            | 4  | 3   | 2        | 1        | 0        |

|-----------------|----------------------------|-----------|----|----------|----------------------------------------------|----|-----|----------|----------|----------|

| вз <sub>Н</sub> | MD1 Reset: 00 <sub>H</sub> | Bit Field |    | <u> </u> | <u>.                                    </u> | DA | TA  | <u> </u> | <u> </u> | <u> </u> |

|                 | MDU Operand Register 1     | Туре      | rw |          |                                              |    |     |          |          |          |

| вз <sub>Н</sub> | MR1 Reset: 00 <sub>H</sub> | Bit Field |    |          |                                              | DA | ATA |          |          |          |

|                 | MDU Result Register 1      | Туре      | rh |          |                                              |    |     |          |          |          |

| B4 <sub>H</sub> | MD2 Reset: 00 <sub>H</sub> | Bit Field |    |          |                                              | DA | ATA |          |          |          |

|                 | MDU Operand Register 2     | Туре      |    |          |                                              | r  | w   |          |          |          |

| B4 <sub>H</sub> | MR2 Reset: 00 <sub>H</sub> | Bit Field |    |          |                                              | DA | ATA |          |          |          |

|                 | MDU Result Register 2      | Туре      |    |          |                                              | I  | 'n  |          |          |          |

| в5 <sub>Н</sub> | MD3 Reset: 00 <sub>H</sub> | Bit Field |    |          |                                              | DA | ATA |          |          |          |

|                 | MDU Operand Register 3     | Туре      |    |          |                                              | r  | W   |          |          |          |

| B5 <sub>H</sub> | MR3 Reset: 00 <sub>H</sub> | Bit Field |    |          |                                              | DA | ATA |          |          |          |

|                 | MDU Result Register 3      | Туре      | rh |          |                                              |    |     |          |          |          |

| B6 <sub>H</sub> | MD4 Reset: 00 <sub>H</sub> | Bit Field |    |          |                                              | DA | ATA |          |          |          |

|                 | MDU Operand Register 4     | Туре      | rw |          |                                              |    |     |          |          |          |

| B6 <sub>H</sub> | MR4 Reset: 00 <sub>H</sub> | Bit Field |    |          |                                              | DA | ATA |          |          |          |

|                 | MDU Result Register 4      | Туре      |    |          |                                              | I  | 'n  |          |          |          |

| в7 <sub>Н</sub> | MD5 Reset: 00 <sub>H</sub> | Bit Field |    |          |                                              | DA | ATA |          |          |          |

|                 | MDU Operand Register 5     | Туре      |    |          |                                              | r  | W   |          |          |          |

| в7 <sub>Н</sub> | MR5 Reset: 00 <sub>H</sub> | Bit Field |    |          |                                              | DA | ATA |          |          |          |

|                 | MDU Result Register 5      | Туре      |    |          |                                              | ı  | 'n  |          |          |          |

## Table 5MDU Register Overview (cont'd)

# 3.2.4.3 CORDIC Registers

The CORDIC SFRs can be accessed in the mapped memory area (RMAP = 1).

### Table 6 CORDIC Register Overview

| Addr            | Register Name                    | Bit       | it 7 6 5 4 3 2 1 |  |  |    |     |  | 0 |  |

|-----------------|----------------------------------|-----------|------------------|--|--|----|-----|--|---|--|

| RMAP =          | = 1                              |           |                  |  |  |    |     |  |   |  |

| 9A <sub>H</sub> | CD_CORDXL Reset: 00 <sub>H</sub> | Bit Field | Id DATAL         |  |  |    |     |  |   |  |

|                 | CORDIC X Data Low Byte           | Туре      | rw               |  |  |    |     |  |   |  |

| 9B <sub>H</sub> | CD_CORDXH Reset: 00 <sub>H</sub> | Bit Field | DATAH            |  |  |    |     |  |   |  |

|                 | CORDIC X Data High Byte          | Туре      | rw               |  |  |    |     |  |   |  |

| 9C <sub>H</sub> | CD_CORDYL Reset: 00 <sub>H</sub> | Bit Field | d DATAL          |  |  |    |     |  |   |  |

|                 | CORDIC Y Data Low Byte           | Туре      |                  |  |  | r  | W   |  |   |  |

| 9D <sub>H</sub> | CD_CORDYH Reset: 00 <sub>H</sub> | Bit Field |                  |  |  | DA | TAH |  |   |  |

|                 | CORDIC Y Data High Byte          | Туре      | pe rw            |  |  |    |     |  |   |  |

| 9E <sub>H</sub> | CD_CORDZL Reset: 00 <sub>H</sub> | Bit Field |                  |  |  | DA | TAL |  |   |  |

|                 | CORDIC Z Data Low Byte           | Туре      | rw               |  |  |    |     |  |   |  |

## 3.2.4.8 Timer 2 Registers

The Timer 2 SFRs can be accessed in the standard memory area (RMAP = 0).

| Addr            | Register Name                                               | Bit       | 7          | 6          | 5           | 4    | 3         | 2     | 1    | 0          |

|-----------------|-------------------------------------------------------------|-----------|------------|------------|-------------|------|-----------|-------|------|------------|

| RMAP =          | = 0                                                         |           |            |            |             |      |           |       |      |            |

| C0H             | T2_T2CON Reset: 00 <sub>H</sub><br>Timer 2 Control Register | Bit Field | TF2        | EXF2       | (           | 0    | EXEN<br>2 | TR2   | C/T2 | CP/<br>RL2 |

|                 |                                                             | Туре      | rwh        | rwh        |             | r    | rw        | rwh   | rw   | rw         |

| C1 <sub>H</sub> | T2_T2MOD Reset: 00 <sub>H</sub><br>Timer 2 Mode Register    | Bit Field | T2RE<br>GS | T2RH<br>EN | EDGE<br>SEL | PREN |           | T2PRE |      | DCEN       |

|                 |                                                             | Туре      | rw         | rw         | rw          | rw   | rw        | rw    | rw   | rw         |

|                 | T2_RC2L Reset: 00 <sub>H</sub>                              | Bit Field | RC2        |            |             |      |           |       |      |            |

|                 | Timer 2 Reload/Capture<br>Register Low                      | Туре      | rwh        |            |             |      |           |       |      |            |

| Сз <sub>Н</sub> | T2_RC2H Reset: 00 <sub>H</sub>                              | Bit Field |            |            |             | R    | C2        |       |      |            |

|                 | Timer 2 Reload/Capture<br>Register High                     | Туре      | rwh        |            |             |      |           |       |      |            |

| C4 <sub>H</sub> | T2_T2L Reset: 00 <sub>H</sub>                               | Bit Field |            |            |             | TH   | IL2       |       |      |            |

|                 | Timer 2 Register Low                                        | Туре      | rwh        |            |             |      |           |       |      |            |

| C5 <sub>H</sub> | T2_T2H Reset: 00 <sub>H</sub>                               | Bit Field | Id THL2    |            |             |      |           |       |      |            |

|                 | Timer 2 Register High                                       | Туре      |            |            |             | rv   | vh        |       |      |            |

### Table 11T2 Register Overview

# 3.2.4.9 Timer 21 Registers

The Timer 21 SFRs can be accessed in the mapped memory area (RMAP = 1).

## Table 12T21 Register Overview

|                 | 0                                                         |           |     |      |         |    |     |      |      |                   |

|-----------------|-----------------------------------------------------------|-----------|-----|------|---------|----|-----|------|------|-------------------|

| Addr            | Register Name                                             | Bit       | 7   | 6    | 5       | 4  | 3   | 2    | 1    | 0                 |

| RMAP =          | = 1                                                       |           |     |      |         |    |     |      |      |                   |

| C0H             | T21_T2CONReset: 00HTimer 2 Control Register               | Bit Field | TF2 | EXF2 | (       | 0  |     | TR2  | C/T2 | <u>CP/</u><br>RL2 |

|                 |                                                           | Туре      | rwh | rwh  |         | r  | rw  | rwh  | rw   | rw                |

| C1 <sub>H</sub> | T21_T2MOD Reset: 00 <sub>H</sub><br>Timer 2 Mode Register |           |     | PREN | T2PRE D |    |     | DCEN |      |                   |

|                 |                                                           | Туре      | rw  | rw   | rw      | rw | rw  | rw   | rw   | rw                |

| C2 <sub>H</sub> | T21_RC2L Reset: 00 <sub>H</sub>                           | Bit Field | RC2 |      |         |    |     |      |      |                   |

|                 | Timer 2 Reload/Capture<br>Register Low                    | Туре      | rwh |      |         |    |     |      |      |                   |

| C3 <sub>H</sub> | T21_RC2H Reset: 00 <sub>H</sub>                           | Bit Field |     |      |         | R  | C2  |      |      |                   |

|                 | Timer 2 Reload/Capture<br>Register High                   | Туре      |     |      |         | ٢٧ | vh  |      |      |                   |

| C4 <sub>H</sub> | T21_T2L Reset: 00 <sub>H</sub>                            | Bit Field |     |      |         | TH | IL2 |      |      |                   |

|                 | Timer 2 Register Low                                      | Туре      |     |      |         | r١ | vh  |      |      |                   |

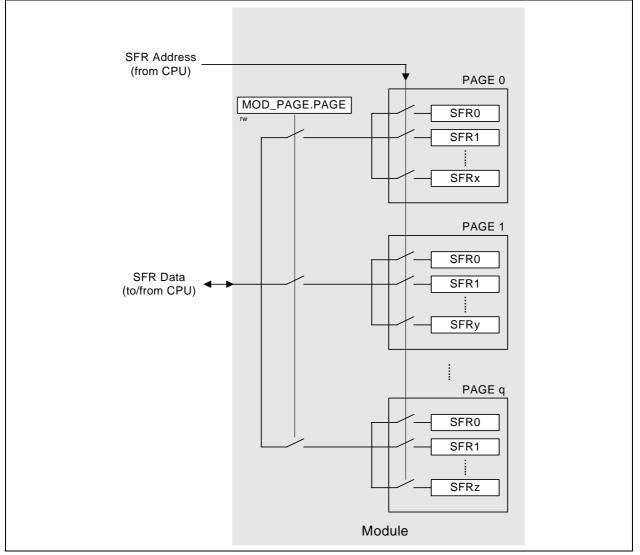

## 3.5 Parallel Ports

The SAL-XC886 has 34 port pins organized into five parallel ports, Port 0 (P0) to Port 4 (P4). Each pin has a pair of internal pull-up and pull-down devices that can be individually enabled or disabled. Ports P0, P1, P3 and P4 are bidirectional and can be used as general purpose input/output (GPIO) or to perform alternate input/output functions for the on-chip peripherals. When configured as an output, the open drain mode can be selected. Port P2 is an input-only port, providing general purpose input functions, alternate input functions for the on-chip peripherals, and also analog inputs for the Analog-to-Digital Converter (ADC).

### **Bidirectional Port Features**

- Configurable pin direction

- Configurable pull-up/pull-down devices

- Configurable open drain mode

- Transfer of data through digital inputs and outputs (general purpose I/O)

- Alternate input/output for on-chip peripherals

#### Input Port Features

- Configurable input driver

- Configurable pull-up/pull-down devices

- Receive of data through digital input (general purpose input)

- Alternate input for on-chip peripherals

- Analog input for ADC module

Figure 19 General Structure of Input Port

## 3.7.1 Module Reset Behavior

**Table 21** lists the functions of the SAL-XC886 and the various reset types that affect these functions. The symbol "■" signifies that the particular function is reset to its default state.

| Module/<br>Function   | Wake-Up<br>Reset                     | Watchdog<br>Reset         | Hardware<br>Reset         | Power-On<br>Reset         | Brownout<br>Reset         |  |  |  |  |  |

|-----------------------|--------------------------------------|---------------------------|---------------------------|---------------------------|---------------------------|--|--|--|--|--|

| CPU Core              |                                      |                           |                           |                           |                           |  |  |  |  |  |

| Peripherals           |                                      |                           |                           |                           |                           |  |  |  |  |  |

| On-Chip<br>Static RAM | Not affected,<br>Reliable            | Not affected,<br>Reliable | Not affected,<br>Reliable | Affected, un-<br>reliable | Affected, un-<br>reliable |  |  |  |  |  |

| Oscillator,<br>PLL    |                                      | Not affected              |                           |                           |                           |  |  |  |  |  |

| Port Pins             |                                      |                           |                           |                           |                           |  |  |  |  |  |

| EVR                   | The voltage regulator is switched on | Not affected              |                           |                           |                           |  |  |  |  |  |

| FLASH                 |                                      |                           |                           |                           |                           |  |  |  |  |  |

| NMI                   | Disabled                             | Disabled                  |                           |                           |                           |  |  |  |  |  |

#### Table 21 Effect of Reset on Device Functions

# 3.7.2 Booting Scheme

When the SAL-XC886 is reset, it must identify the type of configuration with which to start the different modes once the reset sequence is complete. Thus, boot configuration information that is required for activation of special modes and conditions needs to be applied by the external world through input pins. After power-on reset or hardware reset, the pins MBC, TMS and P0.0 collectively select the different boot options. Table 22 shows the available boot options in the SAL-XC886.

| MBC | TMS | P0.0 | Type of Mode                                                               | PC Start Value    |  |

|-----|-----|------|----------------------------------------------------------------------------|-------------------|--|

| 1   | 0   | Х    | User Mode <sup>1)</sup> ; on-chip OSC/PLL non-bypassed                     | 0000 <sub>H</sub> |  |

| 0   | 0   | Х    | BSL Mode; on-chip OSC/PLL non-bypassed <sup>2)</sup>                       | 0000 <sub>H</sub> |  |

| 0   | 1   | 0    | OCDS Mode; on-chip OSC/PLL non-<br>bypassed                                | 0000 <sub>H</sub> |  |

| 1   | 1   | 0    | User (JTAG) Mode <sup>3)</sup> ; on-chip OSC/PLL non-<br>bypassed (normal) | 0000 <sub>H</sub> |  |

Table 22 SAL-XC886 Boot Selection

- 1) BSL mode is automatically entered if no valid password is installed and data at memory address 0000H equals zero.

- 2) OSC is bypassed in MultiCAN BSL mode

- 3) Normal user mode with standard JTAG (TCK,TDI,TDO) pins for hot-attach purpose.

Note: The boot options are valid only with the default set of UART and JTAG pins.

## 3.8 Clock Generation Unit

The Clock Generation Unit (CGU) allows great flexibility in the clock generation for the SAL-XC886. The power consumption is indirectly proportional to the frequency, whereas the performance of the microcontroller is directly proportional to the frequency. During user program execution, the frequency can be programmed for an optimal ratio between performance and power consumption. Therefore the power consumption can be adapted to the actual application state.

### Features

- Phase-Locked Loop (PLL) for multiplying clock source by different factors

- PLL Base Mode

- Prescaler Mode

- PLL Mode

- Power-down mode support

The CGU consists of an oscillator circuit and a PLL. In the SAL-XC886, the oscillator can be from either of these two sources: the on-chip oscillator (10 MHz) or the external oscillator (4 MHz to 12 MHz). The term "oscillator" is used to refer to both on-chip oscillator and external oscillator, unless otherwise stated. After the reset, the on-chip oscillator will be used by default. The external oscillator can be selected via software. In addition, the PLL provides a fail-safe logic to perform oscillator run and loss-of-lock detection. This allows emergency routines to be executed for system recovery or to perform system shut down.

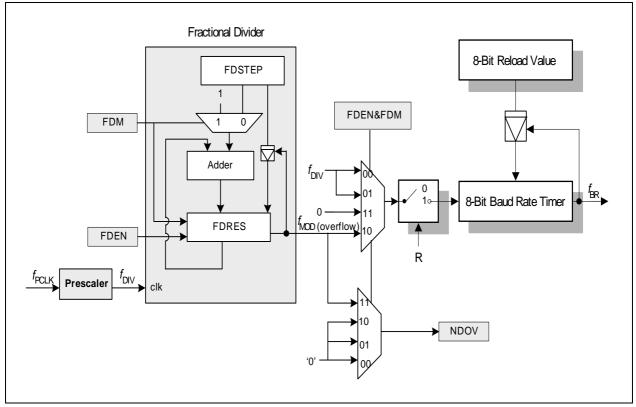

fractional divider) for generating a wide range of baud rates based on its input clock  $f_{PCLK}$ , see **Figure 29**.

### Figure 29 Baud-rate Generator Circuitry

The baud rate timer is a count-down timer and is clocked by either the output of the fractional divider ( $f_{MOD}$ ) if the fractional divider is enabled (FDCON.FDEN = 1), or the output of the prescaler ( $f_{DIV}$ ) if the fractional divider is disabled (FDEN = 0). For baud rate generation, the fractional divider must be configured to fractional divider mode (FDCON.FDM = 0). This allows the baud rate control run bit BCON.R to be used to start or stop the baud rate timer. At each timer underflow, the timer is reloaded with the 8-bit reload value in register BG and one clock pulse is generated for the serial channel.

Enabling the fractional divider in normal divider mode (FDEN = 1 and FDM = 1) stops the baud rate timer and nullifies the effect of bit BCON.R. See Section 3.14.

The baud rate ( $f_{BR}$ ) value is dependent on the following parameters:

- Input clock  $f_{PCLK}$

- Prescaling factor (2<sup>BRPRE</sup>) defined by bit field BRPRE in register BCON

- Fractional divider (STEP/256) defined by register FDSTEP (to be considered only if fractional divider is enabled and operating in fractional divider mode)

- 8-bit reload value (BR\_VALUE) for the baud rate timer defined by register BG

| Table 30   | Table 30 Deviation Error for UART with Fractional Divider enabled |                                |                        |                    |  |  |  |  |  |  |  |

|------------|-------------------------------------------------------------------|--------------------------------|------------------------|--------------------|--|--|--|--|--|--|--|

| $f_{PCLK}$ | Prescaling Factor<br>(BRPRE)                                      | Reload Value<br>(BR_VALUE + 1) | STEP                   | Deviation<br>Error |  |  |  |  |  |  |  |

| 20 MHz     | 1                                                                 | 10 (A <sub>H</sub> )           | 230 (E6 <sub>H</sub> ) | +0.03 %            |  |  |  |  |  |  |  |

| 10 MHz     | 1                                                                 | 5 (5 <sub>H</sub> )            | 230 (E6 <sub>H</sub> ) | +0.03 %            |  |  |  |  |  |  |  |

| 6.67 MHz   | 1                                                                 | 3 (3 <sub>H</sub> )            | 212 (D4 <sub>H</sub> ) | -0.16 %            |  |  |  |  |  |  |  |

| 5 MHz      | 1                                                                 | 2 (2 <sub>H</sub> )            | 189 (BD <sub>H</sub> ) | +0.14 %            |  |  |  |  |  |  |  |

#### war far IIADT with Freetianal Division and blad -61- 20

#### 3.13.2 **Baud Rate Generation using Timer 1**

In UART modes 1 and 3 of UART module, Timer 1 can be used for generating the variable baud rates. In theory, this timer could be used in any of its modes. But in practice, it should be set into auto-reload mode (Timer 1 mode 2), with its high byte set to the appropriate value for the required baud rate. The baud rate is determined by the Timer 1 overflow rate and the value of SMOD as follows:

Mode 1, 3 baud rate =

$$\frac{2^{\text{SMOD}} \times f_{\text{PCLK}}}{32 \times 2 \times (256 - \text{TH1})}$$

(3.7)

#### 3.14 Normal Divider Mode (8-bit Auto-reload Timer)

Setting bit FDM in register FDCON to 1 configures the fractional divider to normal divider mode, while at the same time disables baud rate generation (see Figure 29). Once the fractional divider is enabled (FDEN = 1), it functions as an 8-bit auto-reload timer (with no relation to baud rate generation) and counts up from the reload value with each input clock pulse. Bit field RESULT in register FDRES represents the timer value, while bit field STEP in register FDSTEP defines the reload value. At each timer overflow, an overflow flag (FDCON.NDOV) will be set and an interrupt request generated. This gives an output clock f<sub>MOD</sub> that is 1/n of the input clock f<sub>DIV</sub>, where n is defined by 256 - STEP. The output frequency in normal divider mode is derived as follows:

$$f_{MOD} = f_{DIV} \times \frac{1}{256 - STEP}$$

(3.8)

## 3.15.1 LIN Header Transmission

LIN header transmission is only applicable in master mode. In the LIN communication, a master task decides when and which frame is to be transferred on the bus. It also identifies a slave task to provide the data transported by each frame. The information needed for the handshaking between the master and slave tasks is provided by the master task through the header portion of the frame.

The header consists of a break and synch pattern followed by an identifier. Among these three fields, only the break pattern cannot be transmitted as a normal 8-bit UART data. The break must contain a dominant value of 13 bits or more to ensure proper synchronization of slave nodes.

In the LIN communication, a slave task is required to be synchronized at the beginning of the protected identifier field of frame. For this purpose, every frame starts with a sequence consisting of a break field followed by a synch byte field. This sequence is unique and provides enough information for any slave task to detect the beginning of a new frame and be synchronized at the start of the identifier field.

Upon entering LIN communication, a connection is established and the transfer speed (baud rate) of the serial communication partner (host) is automatically synchronized in the following steps:

- STEP 1: Initialize interface for reception and timer for baud rate measurement

- STEP 2: Wait for an incoming LIN frame from host

- STEP 3: Synchronize the baud rate to the host

- STEP 4: Enter for Master Request Frame or for Slave Response Frame

- Note: Re-synchronization and setup of baud rate are always done for **every** Master Request Header or Slave Response Header LIN frame.

## 3.22.1 JTAG ID Register

This is a read-only register located inside the JTAG module, and is used to recognize the device(s) connected to the JTAG interface. Its content is shifted out when INSTRUCTION register contains the IDCODE command (opcode  $04_H$ ), and the same is also true immediately after reset.

The JTAG ID register contents for the SAL-XC886 Flash devices are given in Table 34.

| Device Type | Device Name    | JTAG ID                |  |  |

|-------------|----------------|------------------------|--|--|

| Flash       | SAL-XC886*-8FF | 1012 0083 <sub>H</sub> |  |  |

|             | SAL-XC886*-6FF | 1012 5083 <sub>H</sub> |  |  |

Note: The asterisk (\*) above denotes all possible device configurations.

## 3.23 Chip Identification Number

The SAL-XC886 identity (ID) register is located at Page 1 of address  $B3_{H}$ . The value of ID register is  $09_{H}$ . However, for easy identification of product variants, the Chip Identification Number, which is an unique number assigned to each product variant, is available. The differentiation is based on the product, variant type and device step information.

Two methods are provided to read a device's chip identification number:

- In-application subroutine, GET\_CHIP\_INFO

- Bootstrap loader (BSL) mode A

Table 35 lists the chip identification numbers of available SAL-XC886 device variants.

| Product Variant  | Chip Identification Number |                       |                       |  |  |  |

|------------------|----------------------------|-----------------------|-----------------------|--|--|--|

|                  | AB-Step                    | AB-Step               | AC-Step               |  |  |  |

| XC886CLM-8FFA 5V | -                          | 09900102 <sub>H</sub> | 0B900102 <sub>H</sub> |  |  |  |

| XC886LM-8FFA 5V  | -                          | 09900122 <sub>H</sub> | 0B900122 <sub>H</sub> |  |  |  |

| XC886CLM-6FFA 5V | -                          | 09951502 <sub>H</sub> | 0B951502 <sub>H</sub> |  |  |  |

| XC886LM-6FFA 5V  | -                          | 09951522 <sub>H</sub> | 0B951522 <sub>H</sub> |  |  |  |

| XC886CM-8FFA 5V  | -                          | 09980102 <sub>H</sub> | 0B980102 <sub>H</sub> |  |  |  |

| XC886C-8FFA 5V   | -                          | 09980142 <sub>H</sub> | 0B980142 <sub>H</sub> |  |  |  |

| XC886-8FFA 5V    | -                          | 09980162 <sub>H</sub> | 0B980162 <sub>H</sub> |  |  |  |

| XC886CM-6FFA 5V  | -                          | 099D1502 <sub>H</sub> | 0B9D1502 <sub>H</sub> |  |  |  |

| XC886C-6FFA 5V   | -                          | 099D1542 <sub>H</sub> | 0B9D1542 <sub>H</sub> |  |  |  |

| XC886-6FFA 5V    | -                          | 099D1562 <sub>H</sub> | 0B9D1562 <sub>H</sub> |  |  |  |

#### Table 35 Chip Identification Number

## **Electrical Parameters**

## 4.1.2 Absolute Maximum Rating

Maximum ratings are the extreme limits to which the SAL-XC886 can be subjected to without permanent damage.

| Parameter                                                    | Symbol            | Limit Values |                                        | Unit | Notes                               |

|--------------------------------------------------------------|-------------------|--------------|----------------------------------------|------|-------------------------------------|

|                                                              |                   | min.         | max.                                   |      |                                     |

| Ambient temperature                                          | T <sub>A</sub>    | -40          | 150                                    | °C   | under bias                          |

| Storage temperature                                          | T <sub>ST</sub>   | -65          | 150                                    | °C   | 1)                                  |

| Junction temperature                                         | TJ                | -40          | 160                                    | °C   | under bias <sup>1)</sup>            |

| Voltage on power supply pin with respect to $V_{\rm SS}$     | $V_{DDP}$         | -0.5         | 6                                      | V    | 1)                                  |

| Voltage on any pin with respect to $V_{\rm SS}$              | V <sub>IN</sub>   | -0.5         | V <sub>DDP</sub> +<br>0.5 or<br>max. 6 | V    | whichever is<br>lower <sup>1)</sup> |

| Input current on any pin during overload condition           | I <sub>IN</sub>   | -10          | 10                                     | mA   | 1)                                  |

| Absolute sum of all input currents during overload condition | $\Sigma  I_{IN} $ | -            | 50                                     | mA   | 1)                                  |

| Table 36 | Absolute Maximum Rating Parameters |

|----------|------------------------------------|

|----------|------------------------------------|

1) Not subjected to production test, verified by design/characterization.

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During absolute maximum rating overload conditions ( $V_{IN} > V_{DDP}$  or  $V_{IN} < V_{SS}$ ) the voltage on  $V_{DDP}$  pin with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

#### **Electrical Parameters**

## Table 38 Input/Output Characteristics (Operating Conditions apply) (cont'd)

| Parameter                                                                      | Symbol                |    | Limit Values                                            |                        | Unit | Test Conditions                                        |

|--------------------------------------------------------------------------------|-----------------------|----|---------------------------------------------------------|------------------------|------|--------------------------------------------------------|

|                                                                                |                       |    | min.                                                    | in. max.               |      |                                                        |

| Input high voltage on RESET pin                                                | $V_{IHR}$             | SR | $0.7 	imes V_{ m DDP}$                                  | -                      | V    | CMOS Mode                                              |

| Input high voltage on<br>TMS pin                                               | $V_{IHT}$             | SR | $0.75 	imes V_{ m DDP}$                                 | -                      | V    | CMOS Mode                                              |

| Input Hysteresis on port pins                                                  | HYSP                  | CC | $\begin{array}{c} 0.07 \times \ V_{ m DDP} \end{array}$ | -                      | V    | CMOS Mode <sup>1)</sup>                                |

| Input Hysteresis on<br>XTAL1                                                   | HYSX                  | CC | $\begin{array}{c} 0.07 \times \ V_{ m DDC} \end{array}$ | -                      | V    | 1)                                                     |

| Input low voltage at XTAL1                                                     | $V_{ILX}$             | SR | V <sub>SS</sub> -<br>0.5                                | $0.3 	imes V_{ m DDC}$ | V    |                                                        |

| Input high voltage at XTAL1                                                    | $V_{IHX}$             | SR | $0.7 	imes V_{ m DDC}$                                  | V <sub>DDC</sub> + 0.5 | V    |                                                        |

| Pull-up current                                                                | I <sub>PU</sub>       | SR | _                                                       | -10                    | μA   | $V_{IHP,min}$                                          |

|                                                                                |                       |    | -150                                                    | -                      | μA   | V <sub>ILP,max</sub>                                   |

| Pull-down current                                                              | $I_{\rm PD}$          | SR | _                                                       | 10                     | μA   | V <sub>ILP,max</sub>                                   |

|                                                                                |                       |    | 150                                                     | -                      | μA   | $V_{IHP,min}$                                          |

| Input leakage current                                                          | I <sub>OZ1</sub>      | CC | -2                                                      | 2                      | μA   | $0 < V_{IN} < V_{DDP},$<br>$T_A \le 150^{\circ}C^{2)}$ |

| Input current at XTAL1                                                         | $I_{\rm ILX}$         | CC | -10                                                     | 10                     | μA   |                                                        |

| Overload current on any pin                                                    | I <sub>OV</sub>       | SR | -5                                                      | 5                      | mA   | 3)                                                     |

| Absolute sum of overload currents                                              | $\Sigma  I_{\rm OV} $ | SR | -                                                       | 25                     | mA   | 3)                                                     |

| Voltage on any pin during $V_{\text{DDP}}$ power off                           | V <sub>PO</sub>       | SR | -                                                       | 0.3                    | V    | 4)                                                     |

| Maximum current per pin (excluding $V_{\text{DDP}}$ and $V_{\text{SS}}$ )      | I <sub>M</sub> SR     | SR | -                                                       | 15                     | mA   |                                                        |

| Maximum current for all pins (excluding $V_{\text{DDP}}$ and $V_{\text{SS}}$ ) | $\Sigma  I_{M} $      | SR | _                                                       | 90                     | mA   |                                                        |

## Package and Quality Declaration

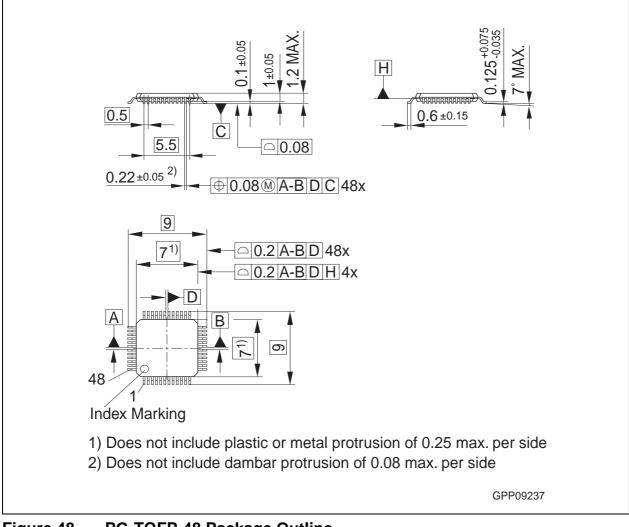

## 5.2 Package Outline

Figure 48 shows the package outlines of the SAL-XC886.

Figure 48 PG-TQFP-48 Package Outline