Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 4300                                                        |

| Number of Logic Elements/Cells | 107500                                                      |

| Total RAM Bits                 | 8936448                                                     |

| Number of I/O                  | 744                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 0.86V ~ 1.15V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 1152-BBGA, FCBGA                                            |

| Supplier Device Package        | 1152-FBGA (35x35)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep3se110f1152c3n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

List of Figures xv

# **List of Figures**

| Figure 1–1: Stratix III Device Packaging Ordering Information                                       | . 1-14 |

|-----------------------------------------------------------------------------------------------------|--------|

| Figure 2–1: Stratix III LAB Structure                                                               |        |

| Figure 2–2: Stratix III LAB and MLAB Structure                                                      | 2-3    |

| Figure 2–3: Direct Link Connection                                                                  |        |

| Figure 2–4: LAB-Wide Control Signals                                                                | 2-5    |

| Figure 2–5: High-Level Block Diagram of the Stratix III ALM                                         | 2-6    |

| Figure 2–6: Stratix III ALM Details                                                                 | 2-7    |

| Figure 2–7: ALM in Normal Mode (Note 1)                                                             | 2-9    |

| Figure 2–8: 4 × 2 Crossbar Switch Example                                                           | . 2-10 |

| Figure 2–9: Input Function in Normal Mode (Note 1)                                                  | . 2-11 |

| Figure 2–10: Template for Supported Seven-Input Functions in Extended LUT Mode                      | . 2-11 |

| Figure 2–11: ALM in Arithmetic Mode                                                                 | . 2-12 |

| Figure 2–12: Conditional Operation Example                                                          | . 2-13 |

| Figure 2–13: ALM in Shared Arithmetic Mode                                                          | . 2-15 |

| Figure 2–14: Example of a 3-Bit Add Utilizing Shared Arithmetic Mode                                | . 2-16 |

| Figure 2–15: LUT Register from Two Combinational Blocks                                             | . 2-17 |

| Figure 2–16: ALM in LUT-Register Mode with 3-Register Capability                                    | . 2-18 |

| Figure 2–17: Register Chain within an LAB (Note 1)                                                  | . 2-19 |

| Figure 2–18: Shared Arithmetic Chain, Carry Chain, and Register Chain Interconnects                 | . 2-20 |

| Figure 3–1: R4 Interconnect Connections (Note 1), (2)                                               | 3-2    |

| Figure 3–2: Shared Arithmetic Chain, Carry Chain, and Register Chain Interconnects                  | 3-3    |

| Figure 3–3: C4 Interconnect Connections (Note 1)                                                    |        |

| Figure 3–4: MLAB RAM Block LAB Row Interface                                                        | 3-7    |

| Figure 3–5: M9K RAM Block LAB Row Interface                                                         |        |

| Figure 3–6: M144K Row Unit Interface to Interconnect                                                |        |

| Figure 3–7: High-Level View, DSP Block Interface to Interconnect                                    |        |

| Figure 3–8: Detailed View, DSP Block Interface to Interconnect                                      | . 3-11 |

| Figure 3–9: Row I/O Block Connection to Interconnect                                                |        |

| Figure 3–10: Column I/O Block Connection to Interconnect                                            |        |

| Figure 4–1: Stratix III Byte-Enable Functional Waveform for M9K and M144K                           | 4-4    |

| Figure 4–2: Stratix III Byte-Enable Functional Waveform for MLABs                                   | 4-5    |

| Figure 4–3: Stratix III Address Clock Enable Block Diagram                                          | 4-6    |

| Figure 4–4: Stratix III Address Clock Enable during Read Cycle Waveform                             |        |

| Figure 4–5: Stratix III Address Clock Enable during Write Cycle Waveform for M9K and M144K $\ldots$ | 4-7    |

| Figure 4–6: Stratix III Address Clock Enable during Write Cycle Waveform for MLABs                  | 4-8    |

| Figure 4–7: Output Latch Asynchronous Clear Waveform                                                | 4-9    |

| Figure 4–8: ECC Block Diagram of the M144K                                                          | . 4-10 |

| Figure 4–9: Single-Port Memory (Note 1)                                                             |        |

| Figure 4–10: Timing Waveform for Read-Write Operations (Single-Port Mode) for M9K and M144K $$      | . 4-12 |

| Figure 4–11: Timing Waveform for Read-Write Operations (Single-Port Mode) for MLABs                 | . 4-12 |

| Figure 4–12: Stratix III Simple Dual-Port Memory (Note 1)                                           |        |

| Figure 4–13: Stratix III Simple Dual-Port Timing Waveforms for M9K and M144K                        |        |

| Figure 4–14: Stratix III Simple Dual-Port Timing Waveforms for MLABs                                |        |

| Figure 4–15: Stratix III True Dual-Port Memory (Note 1)                                             |        |

| Figure 4–16: Stratix III True Dual-Port Timing Waveform                                             |        |

| Figure 4–17: Stratix III Shift-Register Memory Configuration                                        |        |

| Figure 4–18: Stratix III Read-During-Write Data Flow                                                | . 4-21 |

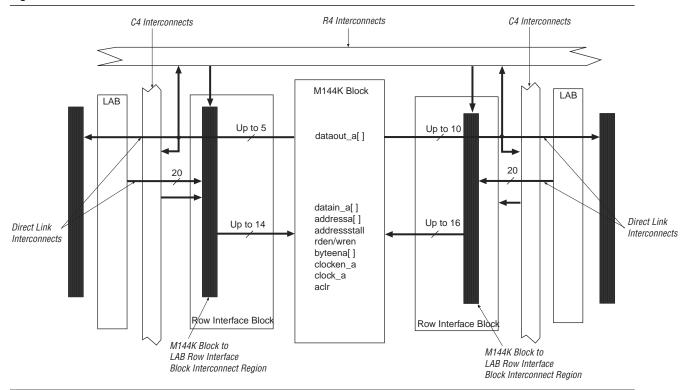

Figure 3-6. M144K Row Unit Interface to Interconnect

## **DSP Block Interface**

Stratix III device DSP block input registers can generate a shift register that cascades down in the same DSP block column. Dedicated connections between DSP blocks provide fast connections between the shift register inputs to cascade the shift register chains. You can cascade registers within multiple DSP blocks for 9-bit or 18-bit finite impulse response (FIR) filters larger than four taps, with additional adder stages implemented in ALMs. If the DSP block is configured as 36-bit blocks, the adder, subtractor, or accumulator stages are implemented in ALMs. Each DSP block can route the shift register chain out of the block to cascade multiple columns of DSP blocks.

The DSP block is divided into four block units that interface with four LAB rows on the left and right. You can consider each block unit as two 18-bit multipliers followed by an adder with 72 inputs and 36 outputs. A local interconnect region is associated with each DSP block. Like a LAB, this interconnect region can be fed with 20 direct link interconnects from the LAB to the left or right of the DSP block in the same row. R4 and C4 routing resources can access the DSP block's local interconnect region.

These outputs work similarly to LAB outputs. Eighteen outputs from the DSP block can drive to the left LAB through direct link interconnects and eighteen can drive to the right LAB though direct link interconnects. All 36 outputs can drive to R4 and C4 routing interconnects. Outputs can drive right- or left-column routing. Figure 3–7 and Figure 3–8 show the DSP block interfaces to LAB rows.

-----

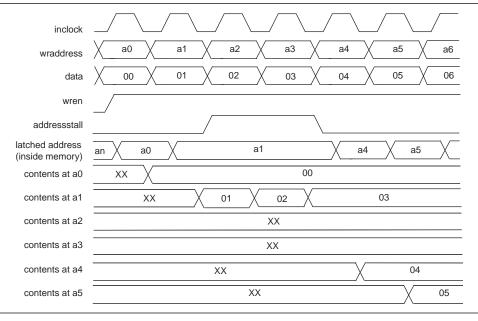

Figure 4–6 shows the address clock enable waveform during the write cycle for MLABs.

Figure 4-6. Stratix III Address Clock Enable during Write Cycle Waveform for MLABs

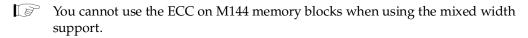

## **Mixed Width Support**

M9K and M144K memory blocks inherently support mixed data widths. MLABs can support mixed data widths through emulation via the Quartus II software. When using simple dual-port or true dual-port mixed width support allows you to read and write different data widths to a memory block. Refer to "Memory Modes" on page 4–10 for details on the different widths supported per memory mode.

MLABs do not support mixed-width FIFO mode.

# **Asynchronous Clear**

Stratix III M9K and M144K memory blocks support asynchronous clears on the output latches and output registers. MLABs supports asynchronous clear on the output registers only as the output is not latched. Therefore, if your M9K and M144K are not using the output registers, you can still clear the RAM outputs via the output latch asynchronous clear. The functional waveform in Figure 4–7 shows this functionality.

### **Read/Write Clock Mode**

Stratix III TriMatrix memory blocks can implement read/write clock mode for simple dual-port memories. In this mode, a write clock controls the data-input, write-address, and write-enable registers. Similarly, a read clock control the data-output, read-address, and read-enable registers. The memory blocks support independent clock enables for both the read and write clocks. Asynchronous clears are available on data output latches and registers only.

When using read/write mode, if you perform a simultaneous read/write to the same address location, the output read data will be unknown. If you require the output data to be a known value in this case, use either single-clock mode or input/output clock mode and choose the appropriate read-during-write behavior in the Megawizard.

### **Single Clock Mode**

Stratix III TriMatrix memory blocks can implement single-clock mode for true dual-port, simple dual-port, and single-port memories. In this mode, a single clock, together with a clock enable, is used to control all registers of the memory block. Asynchronous clears are available on output latches and output registers only.

# **Design Considerations**

This section describes guidelines for designing with TriMatrix memory blocks.

### **Selecting TriMatrix Memory Blocks**

The Quartus II software automatically partitions user-defined memory into embedded memory blocks by taking into account both speed and size constraints placed on your design. For example, the Quartus II software may spread out a memory across multiple memory blocks when resources are available to increase the performance of the design. You can manually assign the memory to a specific block size via the RAM MegaWizard Plug-In Manager.

MLABs can implement single-port SRAM through emulation via the Quartus II software. Emulation results in minimal additional logic resources being used. Because of the dual-purpose architecture of the MLAB, it only has data input registers and output registers in the block. MLABs gain input address registers and additional optional data output registers from adjacent ALMs by using register packing.

For more information about register packing, refer to the *Logic Array Blocks and Adaptive Logic Modules in Stratix III Devices* chapter in volume 1 of the *Stratix III Device Handbook*.

#### **Conflict Resolution**

When using the memory blocks in true dual-port mode, it is possible to attempt two write operations to the same memory location (address). Since no conflict resolution circuitry is built into the memory blocks, this results in unknown data being written to that location. Therefore, you must implement conflict resolution logic external to the memory block to avoid address conflicts.

| <b>Table 5–10.</b> DSP Block Dynamic S | Signals ( | (Part 2 of 2) |

|----------------------------------------|-----------|---------------|

|----------------------------------------|-----------|---------------|

| Signal Name | Function                                                | Count |

|-------------|---------------------------------------------------------|-------|

| ena0        |                                                         |       |

| ena1        | Input and Pipeline Register enable signals              | 4     |

| ena2        | imput and imported register enable signals              | 7     |

| ena3        |                                                         |       |

| aclr0       |                                                         |       |

| aclr1       | DSP block-wide asynchronous clear signals (active low). | 4     |

| aclr2       | bot block wide asynchronous clear signals (active low). |       |

| aclr3       |                                                         |       |

| _           | Total Count per Full Block                              | 34    |

# **Application Examples**

### **FIR Example**

A finite impulse response filter is a common function used in many systems to perform spectral manipulations. The basic form is shown in Equation 5–6.

Equation 5-6. Finite Impulse Response Filter Equation

$$y(n) = \sum_{k=0}^{N-1} x(n-k) \times c(k)$$

In this equation, x(n) is the input samples to the filter, c(k) are the filter coefficients, and y(n) are the filtered output samples. Typically, the coefficients do not change in time in most applications such as Digital Down Converters (DDC). FIR filters can be implemented in many forms, the most simple being the tap-delay line approach.

Stratix III DSP block can implement various types of FIR filters very efficiently. To form the tap-delay line, the input register stage of the DSP block has the ability to cascade the input in a chained fashion in 18-bit wide format. Unlike the Stratix II DSP block, which has two built-in parallel input register scan paths, Stratix III supports only one built-in 18-bit parallel input register scan path for 288 data input.

For a pair of 18-bit input buses, the A input for the first 18-bit bus is fed back to be registered again at the input of the second (lower) pair of inputs. Refer to Figure 5–22 for details.

The B input of the multiplier feeds from the general routing. You can scan in the data in 18-bit parallel form and multiply it by the 18-bit input bus from general routing in each cycle.

**Table 7–9.** Selectable I/O Standards with Expanded On-Chip Series Termination with Calibration Range

|                    | Ехр     | anded OCT R₅ range |      |

|--------------------|---------|--------------------|------|

| I/O Standard       | Row I/O | Column I/O         | Unit |

| 3.3-V LVTTL/LVCMOS | 20–60   | 20–60              | Ω    |

| 3.0-V LVTTL/LVCMOS | 20-60   | 20–60              | Ω    |

| 2.5-V LVTTL/LVCMOS | 20-60   | 20–60              | Ω    |

| 1.8-V LVTTL/LVCMOS | 20-60   | 20–60              | Ω    |

| 1.5-V LVTTL/LVCMOS | 40–60   | 20–60              | Ω    |

| 1.2-V LVTTL/LVCMOS | 40–60   | 20–60              | Ω    |

| SSTL-2             | 20-60   | 20–60              | Ω    |

| SSTL-18            | 20-60   | 20–60              | Ω    |

| SSTL-15            | 40–60   | 20–60              | Ω    |

| HSTL-18            | 20–60   | 20–60              | Ω    |

| HSTL-15            | 40–60   | 20–60              | Ω    |

| HSTL-12            | 40-60   | 20–60              | Ω    |

#### Note to Table 7-9:

#### **Left Shift Series Termination Control**

Stratix III devices support left shift series termination control. You can use the left shift series termination control to get the calibrated OCT  $R_{\rm S}$  with half of the impedance value of the external reference resistors connected to RUP and RDN pins. This feature is useful in applications which require both 25- $\Omega$  and 50- $\Omega$  calibrated OCT  $R_{\rm S}$  at the same  $V_{\rm CCIO}$ . For example, if your applications require 25- $\Omega$  and 50- $\Omega$  calibrated OCT  $R_{\rm S}$  for SSTL–2 Class I and Class II I/O standards, you would only require one OCT calibration block with 50- $\Omega$  external reference resistors. You can enable this feature in the ALTIOBUF megafunction in the Quartus II software. The Quartus II software only allows the left shift series termination control for 25- $\Omega$  calibrated OCT  $R_{\rm S}$  with 50- $\Omega$  external reference resistors connected to RUP and RDN pins. You can only use left shift series termination control for I/O standards that support 25  $\Omega$  calibrated OCT  $R_{\rm S}$ .

Left shift series termination control is automatically enabled if you use a bidirectional I/O with 25-  $\Omega$  calibrated OCT R<sub>S</sub> and 50-  $\Omega$  parallel OCT.

For more information about how to enable left shift series termination in the ALTIOBUF megafunction, refer to the *ALTIOBUF Megafunction User Guide*.

<sup>(1)</sup> The expanded On-Chip Series Termination with calibration of SSTL and HSTL is for impedance matching to improve signal integrity and not for meeting JEDEC standard.

Figure 8-4. Number of DQS/DQ Groups per Bank in EP3SE50, EP3SL50, EP3SL70, EP3SE80, EP3SE110, EP3SL110, EP3SL150, EP3SL200, and EP3SE260 Devices in the 780-pin FineLine BGA Package (Note 1)

| DLL 0                                                                                                                                                                                                                     | I/O Bank 8A (2)  40 User I/Os  x4=6  x8/x9=3  x16/x18=1   | I/O Bank 8C (2)  24 User I/Os  x4=2  x8/x9=1  x16/x18=0                                                                                                                                                             | I/O Bank 7C<br>24 User I/Os<br>x4=3<br>x8/x9=1<br>x16/x18=0 | I/O Bank 7A (2) 40 User I/Os x4=6 x8/x9=3 x16/x18=1      | DLL 3 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------|-------|

| I/O Bank 1A (2)  32 User I/Os x4=4 x8/x9=2 x16/x18=1  I/O Bank 1C (3)  26 User I/Os (4) x4=3 x8/x9=1 x16/x18=0  I/O Bank 2C  26 User I/Os (4) x4=3 x8/x9=1 x16x18=0  I/O Bank 2A (2)  32 User I/Os x4=4 x8/x9=2 x16/x18=1 | EP3SE50, EP3S                                             | I/O Bank 6A (2)  32 User I/Os x4=4 x8/x9=2 x16/x18=1  I/O Bank 6C  26 User I/Os (4) x4=3 x8/x9=1 x16/x18=0  I/O Bank 5C  26 User I/Os (4) x4=3 x8x9=1 x16x18=0  I/O Bank 5A (2)  32 User I/Os x4=4 x8x9=2 x16/x18=1 |                                                             |                                                          |       |

| DLL 1                                                                                                                                                                                                                     | I/O Bank 3A <i>(2)</i> 40 User I/Os x4=6 x8/x9=3 x16x18=1 | I/O Bank 3C (2)  24 User I/Os x4=2 x8/x9=1 x16/x18=0                                                                                                                                                                | I/O Bank 4C<br>24 User I/Os<br>x4=3<br>x8/x9=1<br>x16x18=0  | I/O Bank 4A <i>(2)</i> 40 User I/Os x4=6 x8x9=3 x16x18=1 | DLL 2 |

#### Notes to Figure 8-4:

- (1) This device does not support ×32/×36 mode.

- (2) You can also use DQS/DQSn pins in some of the ×4 groups as RUP/RDN pins. You cannot use a ×4 group for memory interfaces if two pins of the group are being used as RUP and RDN pins for OCT calibration. You can still use the ×16/×18 or ×32/×36 groups that includes these ×4 groups. However, there are restrictions on using ×8/×9 groups that include these ×4 groups as described on page 8–5.

- (3) Some of the DQS/DQ pins in this bank can also be used as configuration pins. Choose the DQS/DQ pins that are not going to be used by your configuration scheme.

- (4) All I/O pin counts include eight dedicated clock inputs (CLK1p, CLK1n, CLK3p, CLK8n, CLK8p, CLK8n, CLK10p, and CLK10n).

**Figure 8–5.** Number of DQS/DQ Groups in EP3SE80, EP3SE110, EP3SL110, EP3SL150, EP3SL200, EP3SE260, and EP3SL340 Devices in the 1152-pin FineLine BGA Package (Note 1)

| DLLO                                                                | I/O Bank 8A (2) 40 User I/Os x4=6 x8/x9=3 x16/x18=1 | I/O Bank 8B<br>24 User I/Os<br>x4=4<br>x8/x9=2<br>x16/x18=1  | I/O Bank 8C <i>(2)</i> 32 User I/Os x4=3 x8/x9=1 x16/x18=0 | I/O Bank 7C<br>32 User I/Os<br>x4=3<br>x8/x9=1<br>x16/x18=0 | I/O Bank 7B<br>24 User I/Os<br>x4=4<br>x8/x9=2<br>x16/x18=1 | VO Bank 7A (2)  40 User VOs  x4=6  x8/x9=3  x16/x18=1           | DLL3                                                            |

|---------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------|

| I/O Bank 1A (2) 48 User I/Os x4=7 x8/x9=3 x16/x18=1                 |                                                     |                                                              |                                                            |                                                             |                                                             |                                                                 | I/O Bank 6A (2)  48 User I/Os x4=7 x8/x9=3 x16/x18=1            |

| I/O Bank 1C (3)<br>42 User I/Os (4)<br>x4=6<br>x8/x9=3<br>x16/x18=1 |                                                     |                                                              |                                                            |                                                             |                                                             |                                                                 | I/O Bank 6C<br>42 User I/Os (4)<br>x4=6<br>x8/x9=3<br>x16/x18=1 |

| I/O Bank 2C<br>42 User I/Os (4)<br>x4=6<br>x8/x9=3<br>x16/x18=1     |                                                     | EP3S                                                         | EP3SE260, and E                                            | L110, EP3SL150, EP3S<br>P3SL340 Devices<br>ineLine BGA      | SL200,                                                      |                                                                 | I/O Bank 5C<br>42 User I/Os (4)<br>x4=6<br>x8/x9=3<br>x16/x18=1 |

| I/O Bank 2A <i>(2)</i> 48 User I/Os x4=7 x8/x9=3 x16/x18=1          |                                                     |                                                              |                                                            |                                                             |                                                             |                                                                 | I/O Bank 5A (2)  48 User I/Os x4=7 x8/x9=3 x16/x18=1            |

| DLL1                                                                | I/O Bank 3A (2) 40 User I/Os x4=6 x8/x9=3 x16/x18=1 | I/O Bank 3B<br>24 User I/Os<br>x4=4<br>x8l/y9=2<br>x16/x18=1 | I/O Bank 3C (2) 32 User I/Os x4=3 x8/x9=1 x16/x18=0        | I/O Bank 4C<br>32 User I/Os<br>x4=3<br>x8/x9=1<br>x16/x18=0 | I/O Bank 4B<br>24 User I/Os<br>x4=4<br>x8/x9=2<br>x16/x18=1 | I/O Bank 4A (2)<br>40 User I/Os<br>x4=6<br>x8/x9=3<br>x16/x18=1 | DLL2                                                            |

#### Notes to Figure 8-5:

- (1) This device does not support ×32/×36 mode.

- (2) You can also use DQS/DQSn pins in some of the ×4 groups as RUP/RDN pins. You cannot use a ×4 group for memory interfaces if two pins of the group are being used as RUP and RDN pins for OCT calibration. You can still use the ×16/×18 or ×32/×36 groups that includes these ×4 groups. However, there are restrictions on using ×8/×9 groups that include these ×4 groups as described on page 8–5.

- (3) Some of the DQS/DQ pins in this bank can also be used as configuration pins. Choose the DQS/DQ pins that are not going to be used by your configuration scheme.

- (4) All I/O pin counts include eight dedicated clock inputs (CLK1p, CLK3p, CLK3p, CLK8p, CLK8p, CLK8p, CLK10p, and CLK10n).

The DQS and DQSn pins are listed in the Stratix III pin tables as DQSXY and DQSnXY, respectively, where X denotes the DQS/DQ grouping number, and Y denotes whether the group is located on the top (T), bottom (B), left (L), or right (R) side of the device.

The corresponding DQ pins are marked as DQXY, where X indicates which DQS group the pins belong to and Y indicates whether the group is located on the top (T), bottom (B), left (L), or right (R) side of the device. For example, DQS1L indicates a DQS pin, located on the left side of the device. Refer to Figure 8–8 for an illustration. The DQ pins belonging to that group are shown as DQ1L in the pin table.

The numbering scheme starts from the top-left side of the device going counter-clockwise. Figure 8–8 shows how the DQS/DQ groups are numbered in a package bottom view of the device. The top and bottom sides of the device can contain up to  $44 \times 4$  DQS/DQ groups. The left and right sides of the device can contain up to  $40 \times 4$  DQS/DQ groups.

The parity, DM, BWSn, NWSn, ECC, and QVLD pins are shown as DQ pins in the pin table. When not used as memory interface pins, these pins are available as regular I/O pins.

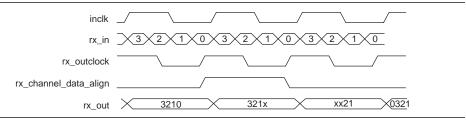

Figure 9–7 shows receiver output (RX\_OUT) after one bit slip pulse with the deserialization factor set to 4.

Figure 9–7. Data Realignment Timing

The data realignment circuit can have up to 11 bit-times of insertion before a rollover occurs. The programmable bit rollover point can be from 1 to 11 bit-times, independent of the deserialization factor. An optional status port, RX\_CDA\_MAX, is available to the FPGA from each channel to indicate when the preset rollover point is reached.

### **Dynamic Phase Aligner (DPA)**

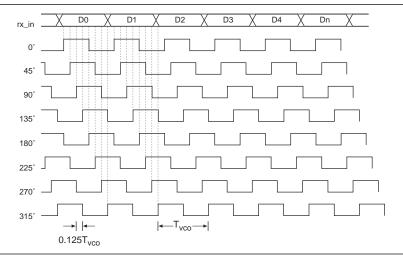

The DPA block takes in high-speed serial data from the differential input buffer and selects one of the eight phase clocks from the left/right PLL to sample the data. The DPA chooses the phase closest to the phase of the serial data. The maximum phase offset between the received data and the selected phase is 1/8 UI, which is the maximum quantization error of the DPA. The eight phases of the clock are equally divided, giving a  $45^{\circ}$  resolution.

Figure 9–8 shows the possible phase relationships between the DPA clocks and the incoming serial data.

Figure 9–8. DPA Clock Phase-to-Serial Data Timing Relationship

The DPA block continuously monitors the phase of the incoming serial data and selects a new clock phase if required. You can prevent the DPA from selecting a new clock phase by asserting the optional RX\_DPLL\_HOLD port, which is available for each channel.

#### SIII51011-2.0

This chapter contains complete information about Stratix® III supported configuration schemes, how to execute the required configuration schemes, and all necessary option pin settings.

Stratix III devices use SRAM cells to store configuration data. Because SRAM memory is volatile, you must download configuration data to the Stratix III device each time the device powers up. You can configure Stratix III devices using one of four configuration schemes:

- Fast passive parallel (FPP)

- Fast active serial (AS)

- Passive serial (PS)

- Joint Test Action Group (JTAG)

All configuration schemes use an external controller (for example, a MAX® II device or microprocessor), a configuration device, or a download cable. Refer to "Configuration Features" on page 11–3 for more information.

# **Configuration Devices**

The Altera® serial configuration devices (EPCS128, EPCS64, and EPCS16) support a single-device and multi-device configuration solution for Stratix III devices and are used in the fast AS configuration scheme. Serial configuration devices offer a low-cost, low-pin count configuration solution.

All minimum timing information in this handbook covers the entire Stratix III family. Some devices may work at less than the minimum timing stated in this handbook due to process variation.

# **Configuration Schemes**

Select the configuration scheme by driving the Stratix III device MSEL pins either high or low, as detailed in Table 11–1. The MSEL pins are powered by the  $V_{\text{CCPGM}}$  power supply of the bank they reside in. The MSEL[2..0] pins have 5-k $\Omega$  internal pull-down resistors that are always active. During power-on reset (POR) and reconfiguration, the MSEL pins must be at LVTTL  $V_{\rm IL}$  and  $V_{\rm IH}$  levels to be considered a logic low and logic high.

To avoid any problems with detecting an incorrect configuration scheme, hard-wire the MSEL[] pins to  $V_{\text{CCPGM}}$  and GND, without any pull-up or pull-down resistors. Do not drive the MSEL[] pins with a microprocessor or another device.

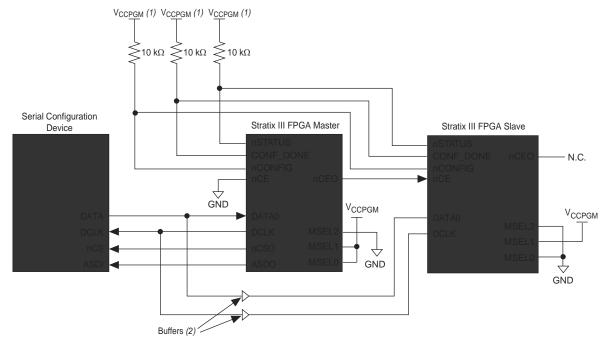

Figure 11–9. Multi-Device Fast AS Configuration

#### Notes to Figure 11-9:

- (1) Connect the pull-up resistors to  $V_{CCPGM}$  at 3.3-V supply.

- (2) Connect the repeater buffers between the Stratix III master and slave device(s) for DATA[0] and DCLK. This prevents any potential signal integrity and clock skew problems.

As shown in Figure 11–9, the nSTATUS and CONF\_DONE pins on all target devices are connected with external pull-up resistors. These pins are open-drain bi-directional pins on the devices. When the first device asserts nCEO (after receiving all of its configuration data), it releases its CONF\_DONE pin. The subsequent devices in the chain keep this shared CONF\_DONE line low until they have received their configuration data. When all target devices in the chain have received their configuration data and released CONF\_DONE, the pull-up resistor drives a high level on this line and all devices simultaneously enter initialization mode.

If an error occurs at any point during configuration, the nSTATUS line is driven low by the failing device. If you enable the **Auto-restart configuration after error** option, reconfiguration of the entire chain begins after a reset time-out period (maximum of  $100~\mu s$ ). If the **Auto-restart configuration after error** option is turned off, the external system must monitor nSTATUS for errors and then pulse nCONFIG low to restart configuration. The external system can pulse nCONFIG if it is under system control rather than tied to  $V_{\text{CCPGM}}$ .

If you have enabled the **Auto-restart configuration after error** option, the nSTATUS pin transitions from high to low and back again to high when a configuration error is detected. This appears as a low pulse at the nSTATUS pin with a minimum pulse width of 10  $\mu s$  to a maximum pulse width of 500  $\mu s$ , as defined in the  $t_{STATUS}$  specification.

While you can cascade Stratix III devices, you cannot cascade or chain together serial configuration devices.

| <b>Table 11–10.</b> PS Timing Parameters for Stratix III Devices (P | (Part 2 01 2) | į |

|---------------------------------------------------------------------|---------------|---|

|---------------------------------------------------------------------|---------------|---|

| Symbol              | Parameter                                         | Minimum                          | Maximum | Units |

|---------------------|---------------------------------------------------|----------------------------------|---------|-------|

| t                   | Input fall time                                   | _                                | 40      | ns    |

| t <sub>CD2UM</sub>  | CONF_DONE high to user mode (2)                   | 20                               | 100     | μs    |

| t <sub>cD2CU</sub>  | CONF_DONE high to CLKUSR enabled                  | 4× maximum<br>DCLK period        | _       |       |

| t <sub>cd2UMC</sub> | CONF_DONE high to user mode with CLKUSR option on | tCD2CU + (4,436 × CLKUSR period) | _       | _     |

#### Notes to Table 11-10:

- (1) This value is applicable if you do not delay configuration by extending the nconfig or nstatus low pulse width.

- (2) The minimum and maximum numbers apply only if you choose the internal oscillator as the clock source for starting the device.

### **PS Configuration Using a Microprocessor**

In this PS configuration scheme, a microprocessor can control the transfer of configuration data from a storage device, such as flash memory, to the target Stratix III device.

For all configuration and timing information, refer to "PS Configuration Using a MAX II Device as an External Host" on page 11–27. This section is also applicable when using a microprocessor as an external host.

# **PS Configuration Using a Download Cable**

In this section, the generic term *download cable* includes the Altera USB-Blaster USB port download cable, MasterBlaster<sup>TM</sup> serial/USB communications cable, ByteBlaster II parallel port download cable, ByteBlasterMV<sup>TM</sup> parallel port download cable, and the EthernetBlaster download cable.

In PS configuration with a download cable, an intelligent host (such as a PC) transfers data from a storage device to the device by using the USB-Blaster, MasterBlaster, ByteBlaster II, EthernetBlaster, or ByteBlasterMV cable.

Table 11–15 describes the optional configuration pins. If these optional configuration pins are not enabled in the Quartus II software, they are available as general-purpose user I/O pins. Therefore, during configuration, these pins function as user I/O pins and are tri-stated with weak pull-up resistors.

**Table 11–15.** Optional Configuration Pins

| Pin Name  | User Mode                                     | Pin Type          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------|-----------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKUSR    | N/A if option is on. I/O if option is off.    | Input             | Optional user-supplied clock input synchronizes the initialization of one or more devices. Enable this pin by turning on the <b>Enable user-supplied start-up clock</b> ( <b>CLKUSR</b> ) option in the Quartus II software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| INIT_DONE | N/A if option is on. I/O<br>if option is off. | Output open-drain | Use the Status pin to indicate when the device has initialized and is in user mode. When nconfigis low and during the beginning of configuration, the INIT_DONE pin is tri-stated and pulled high due to an external 10-k pull-up resistor. After the option bit to enable INIT_DONE is programmed into the device (during the first frame of configuration data), the INIT_DONE pin will go low. When initialization is complete, the INIT_DONE pin is released and pulled high and the device enters user mode. Thus, the monitoring circuitry must be able to detect a low-to-high transition. This pin is enabled by turning on the <b>Enable INIT_DONE output</b> option in the Quartus II software. |

| DEV_OE    | N/A if option is on. I/O<br>if option is off. | Input             | Optional pin that allows you to override all tri-states on the device. When this pin is driven low, all I/O pins are tri-stated, when this pin is driven high, all I/O pins behave as programmed. Enable this pin by turning on the <b>Enable device-wide output enable</b> ( <b>DEV_OE</b> ) option in the Quartus II software.                                                                                                                                                                                                                                                                                                                                                                          |

| DEV_CLRn  | N/A if option is on. I/O<br>if option is off. | Input             | Optional pin that allows you to override all clears on all device registers. When this pin is driven low, all registers are cleared. When this pin is driven high, all registers behave as programmed. This pin is enabled by turning on the <b>Enable device-wide reset</b> ( <b>DEV_CLRn</b> ) option in the Quartus II software.                                                                                                                                                                                                                                                                                                                                                                       |

# **Remote System Upgrade Mode**

Remote system upgrade has one mode of operation: remote update mode. The remote update mode allows you to determine the functionality of your system upon power-up and offers different features.

In remote update mode, Stratix III devices load the factory configuration image upon power up. The user-defined factory configuration determines which application configuration is to be loaded and triggers a reconfiguration cycle. The factory configuration may also contain application logics.

When used with serial configuration devices, the remote update mode allows an application configuration to start at any flash sector boundary. This translates to a maximum of 128 pages in the EPCS64 device and 32 pages in the EPCS16 device, where the minimum size of each page is 512 KBits. Additionally, the remote update mode features a user watchdog timer that determines the validity of an application configuration.

### **Remote Update Mode**

When a Stratix III device is first powered-up in remote update mode, it loads the factory configuration located at page zero (page registers PGM[23:0] = 24 'b0). You should always store the factory configuration image for your system at page address zero. This corresponds to the start address location  $0 \times 000000$  in the serial configuration device.

The factory configuration image is user-designed and contains soft logic to do the following:

- Process any errors based on status information from the dedicated remote system upgrade circuitry

- Communicate with the remote host and receive new application configurations and store this new configuration data in the local non-volatile memory device

- Determine which application configuration is to be loaded into the Stratix III device

- Enable or disable the user watchdog timer and load its time-out value (optional)

- Instruct the dedicated remote system upgrade circuitry to initiate a reconfiguration cycle

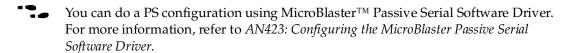

Figure 12–4 shows the transitions between the factory and application configurations in remote update mode.

Figure 12–4. Transitions Between Configurations in Remote Update Mode

After power up or a configuration error, the factory configuration logic is loaded automatically. The factory configuration also needs to specify whether to enable the user watchdog timer for the application configuration and if enabled, to include the timer setting information as well.

The user watchdog timer ensures that the application configuration is valid and functional. The timer must be continually reset within a specific amount of time during user mode operation of an application configuration. Only valid application configurations contain the logic to reset the timer in user mode. This timer reset logic should be part of a user-designed hardware and/or software health monitoring signal that indicates error-free system operation. If the timer is not reset in a specific amount of time, for example, the user application configuration detects a functional problem or if the system hangs, the dedicated circuitry updates the remote system upgrade status register, triggering the loading of the factory configuration.

The user watchdog timer is automatically disabled for factory configurations. For more information about the user watchdog timer, refer to "User Watchdog Timer" on page 12–11.

If there is an error while loading the application configuration, the cause of the reconfiguration is written by the dedicated circuitry to the remote system upgrade status register. Actions that cause the remote system upgrade status register to be written:

- nSTATUS driven low externally

- Internal CRC error

- User watchdog timer time out

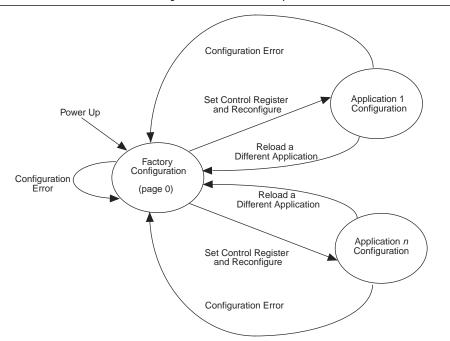

Figure 14–1. Design Security (Note 1)

#### Note to Figure 14-1:

(1) Step 1, Step 2, and Step 3 correspond to the procedure detailed in the "Stratix III Design Security Solution" section.

# **Security Modes Available**

There are several security modes available on the Stratix III device, which are described as follows:

#### **Volatile Key**

Secure operation with volatile key programmed and required external battery—this mode accepts both encrypted and unencrypted configuration bitstreams. Use the unencrypted configuration bitstream support for board-level testing only.

#### **Non-Volatile Key**

Secure operation with one time programmable (OTP) security key programmed—this mode accepts both encrypted and unencrypted configuration bitstreams. Use the unencrypted configuration bitstream support for board-level testing only.

#### Non-Volatile Key with Tamper Protection Bit Set

Secure operation in tamper resistant mode with OTP security key programmed—only encrypted configuration bitstreams are allowed to configure the device. Tamper protection disables JTAG configuration with unencrypted configuration bitstream.

Table 15–2 lists how the fault injection register is implemented and describes error injection.

Table 15–2. Fault Injection Register and Error Injection

| Bit         | Bit[2019] |                |                                      | Bit[188]                                | Bit[70]                                   |

|-------------|-----------|----------------|--------------------------------------|-----------------------------------------|-------------------------------------------|

| Description |           |                | Error Type                           | Byte Location of<br>the Injected Error  | Error Byte Value                          |

|             | Error T   | ype <i>(1)</i> | Error Injection Type                 | Depicts the location                    | Depicts the location of the bit error and |

|             | Bit[20]   | Bit[19]        | Littor injection Type                |                                         |                                           |

| Content     | 0         | 1              | Single byte error injection          | of the injected error in the first data | corresponds to the                        |

|             | 1         | 0              | Double-adjacent byte error injection | frame.                                  | error injection type selection.           |

|             | 0         | 0              | No error injection                   |                                         | Selection.                                |

#### Note to Table 15-2:

(1) Bit[20] and Bit[19] cannot both be set to 1 as this is not a valid selection. The error detection circuitry decodes it as no error injection.

After the test completes, Altera recommends that you reconfigure the device.

### **Automated Single Event Upset Detection**

Stratix III devices offer on-chip circuitry for automated checking of single-event upset detection. Some applications that require the device to operate error-free in high-neutron flux environments require periodic checks to ensure continued data integrity. The error detection CRC feature ensures data reliability and is one of the best options for mitigating SEU.

You can implement the error detection CRC feature with existing circuitry in Stratix III devices, eliminating the need for external logic. The CRC\_ERROR pin reports a soft error when configuration CRAM data is corrupted and you would have to decide whether to reconfigure the device or to ignore the error.