Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 4300                                                        |

| Number of Logic Elements/Cells | 107500                                                      |

| Total RAM Bits                 | 4992000                                                     |

| Number of I/O                  | 744                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 0.86V ~ 1.15V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 1152-BBGA, FCBGA                                            |

| Supplier Device Package        | 1152-FBGA (35x35)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep3sl110f1152c3n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Clock Networks in Stratix III Devices                          |       |

|----------------------------------------------------------------|-------|

| Global Clock Networks                                          | 6-2   |

| Regional Clock Networks                                        | 6-3   |

| Periphery Clock Networks                                       |       |

| Clocking Regions                                               |       |

| Clock Network Sources                                          |       |

| Clock Output Connections                                       |       |

| Clock Source Control for PLLs                                  |       |

| Clock Control Block                                            |       |

| Clock Enable Signals                                           |       |

| PLLs in Stratix III Devices                                    |       |

| Stratix III PLL Hardware Overview                              |       |

| PLL Clock I/O Pins                                             |       |

| Stratix III PLL Software Overview                              |       |

| Clock Feedback Modes                                           |       |

| Source Synchronous Mode                                        |       |

| Source-Synchronous Mode for LVDS Compensation                  |       |

| No-Compensation Mode                                           |       |

| Normal Mode                                                    |       |

| Zero-Delay Buffer Mode                                         |       |

| External Feedback Mode                                         |       |

| Clock Multiplication and Division                              |       |

| Post-Scale Counter Cascading                                   |       |

| Programmable Duty Cycle                                        |       |

| PLL Control Signals                                            |       |

| pfdena                                                         |       |

| areset                                                         |       |

| locked                                                         |       |

| Clock Switchover                                               |       |

| Automatic Clock Switchover                                     |       |

| Manual Clock Switchover                                        |       |

| Guidelines                                                     |       |

| Programmable Bandwidth                                         |       |

| Background                                                     |       |

| Implementation                                                 |       |

| Phase-Shift Implementation                                     |       |

| PLL ReconfigurationPLL Reconfiguration Hardware Implementation |       |

|                                                                |       |

| Post-Scale Counters (C0 to C9)                                 |       |

| Scan Chain Description                                         |       |

|                                                                |       |

| Bypassing PLL  Dynamic Phase-Shifting                          |       |

| PLL Cascading and Clock Network Guidelines                     |       |

| Spread-Spectrum Tracking                                       |       |

|                                                                |       |

| PLL Specifications                                             |       |

| Chapter Nevision History                                       |       |

| Chanter II I/O Interface                                       |       |

| Chapter II. I/O Interfaces Revision History                    | π 1   |

| Revision instory                                               | , H-J |

## Chapter 7. Stratix III Device I/O Features

| Chapter 12. Remote System Upgrades with Stratix III Devices                 |        |

|-----------------------------------------------------------------------------|--------|

| Functional Description                                                      | 12-1   |

| Enabling Remote Update                                                      | 12-3   |

| Configuration Image Types                                                   | 12-4   |

| Remote System Upgrade Mode                                                  |        |

| Remote Update Mode                                                          | 12-5   |

| Dedicated Remote System Upgrade Circuitry                                   |        |

| Remote System Upgrade Registers                                             |        |

| Remote System Upgrade Control Register                                      |        |

| Remote System Upgrade Status Register                                       |        |

| Remote System Upgrade State Machine                                         |        |

| User Watchdog Timer                                                         |        |

| Quartus II Software Support                                                 |        |

| ALTREMOTE_UPDATE Megafunction                                               |        |

| Chapter Revision History                                                    | 2-14   |

| Chapter 13. IEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III Devices |        |

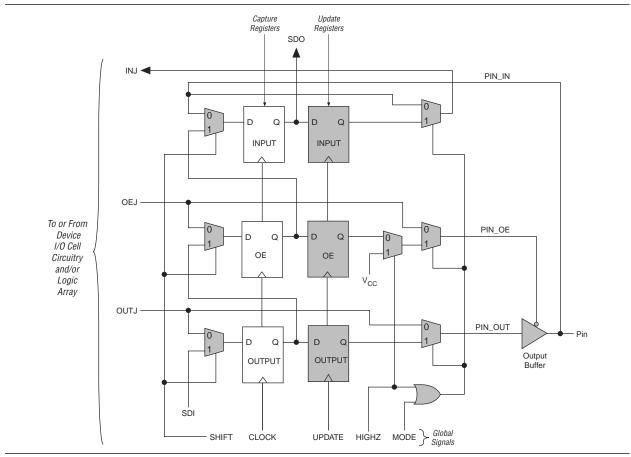

| IEEE Std. 1149.1 BST Architecture                                           |        |

| IEEE Std. 1149.1 Boundary-Scan Register                                     | 13-4   |

| Boundary-Scan Cells of a Stratix III Device I/O Pin                         |        |

| IEEE Std. 1149.1 BST Operation Control                                      |        |

| SAMPLE/PRELOAD Instruction Mode                                             |        |

| EXTEST Instruction Mode                                                     |        |

| BYPASS Instruction Mode                                                     |        |

| IDCODE Instruction Mode                                                     |        |

| USERCODE Instruction Mode                                                   |        |

| CLAMP Instruction Mode                                                      |        |

| HIGHZ Instruction Mode                                                      |        |

| I/O Voltage Support in JTAG Chain                                           |        |

| IEEE Std. 1149.1 BST Circuitry                                              |        |

| IEEE Std. 1149.1 BST Circuitry (Disabling)                                  |        |

| IEEE Std. 1149.1 BST Guidelines                                             |        |

| Boundary-Scan Description Language (BSDL) Support                           |        |

| Chapter Revision History                                                    | 3-21   |

| Chapter IV Design Convity and Cinals Event Uncet (CEII) Militarian          |        |

| Chapter IV. Design Security and Single Event Upset (SEU) Mitigation         | TT 7 1 |

| Revision History                                                            | 1V-1   |

| Chapter 14. Design Security in Stratix III Devices                          |        |

| Introduction                                                                | 14-1   |

| Stratix III Security Protection                                             | 14-1   |

| Security Against Copying                                                    | 14-1   |

| Security Against Reverse Engineering                                        | 14-2   |

| Security Against Tampering                                                  | 14-2   |

| AES Decryption Block                                                        | 14-2   |

| Flexible Security Key Storage                                               | 14-2   |

| Stratix III Design Security Solution                                        | 14-3   |

|                                                                             | 14-4   |

|                                                                             | 14-4   |

| - · · · · · · · · · · · · · · · · · · ·                                     | 14-4   |

| - · · · · · · · · · · · · · · · · · · ·                                     | 14-4   |

| $\Gamma$                                                                    | 14-5   |

| Supported Configuration Schemes                                             | 14-5   |

List of Figures xvii

| Figure 6–24: Phase Relationship Between Clock and Data LVDS Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6-27                                                                                                   |

| Figure 6–25: Phase Relationship Between PLL Clocks in No Compensation Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6-28                                                                                                   |

| Figure 6–26: Phase Relationship Between PLL Clocks in Normal Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                        |

| Figure 6–27: Zero-Delay Buffer Mode in Stratix III PLLs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                        |

| Figure 6–28: Phase Relationship Between PLL Clocks in Zero Delay Buffer Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                        |

| Figure 6–29: External Feedback Mode in Stratix III Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                        |

| Figure 6–30: Phase Relationship Between PLL Clocks in External-Feedback Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                        |

| Figure 6–31: Counter Cascading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                        |

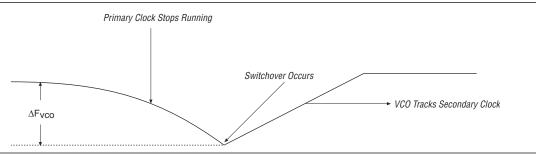

| Figure 6–32: Automatic Clock Switchover Circuit Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                        |

| Figure 6–33: Automatic Switchover Upon Loss of Clock Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                        |

| Figure 6–34: Clock Switchover Using the clkswitch (Manual) Control (Note 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                        |

| Figure 6–35: Manual Clock Switchover Circuitry in Stratix III PLLs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                        |

| Figure 6–36: VCO Switchover Operating Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                        |

| Figure 6–37: Open- and Closed-Loop Response Bode Plots                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                        |

| Figure 6–38: Loop Filter Programmable Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                        |

| Figure 6–39: Delay Insertion Using VCO Phase Output and Counter Delay Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                        |

| Figure 6–40: PLL Reconfiguration Scan Chain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                        |

| Figure 6–41: PLL Reconfiguration Waveform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                        |

| Figure 6–42: Scan-Chain Order of PLL Components for Top/Bottom PLLs (Note 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                        |

| Figure 6–43: Scan-Chain Bit-Order Sequence for Post-Scale Counters in Stratix III PLLs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                        |

| Figure 6–44: Dynamic Phase Shifting Waveform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                        |

| Figure 7–1: I/O Banks for Stratix III Devices (Note 1), (2), (3), (4), (5), (6), (7), (8), (9)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                        |

| Figure 7–2: Number of I/Os in Each Bank in EP3SL50, EP3SL70, and EP3SE50 Devices in 484-Pin F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                        |

| BGA Package (Note 1), (2),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                        |

| Figure 7–3: Number of I/Os in Each Bank in the 780-pin FineLine BGA Package (Note 1), (2), (3),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                        |

| Figure 7–4: Number of I/Os in Each Bank in the 1152-pin FineLine BGA Package (Note 1), (2), (3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                        |

| 7-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ,, (1)                                                                                                 |

| Figure 7–5: Number of I/Os in Each Bank in EP2SL200, EP3SE260, and EP3SL340 Devices in the 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 517-Pin                                                                                                |

| FineLine BGA Package (Note 1), (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                        |

| Figure 7–6: Number of I/Os in Each Bank in EP3SL340 Devices in the 1760-pin FineLine BGA Pac (Note 1), (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | kage                                                                                                   |

| Figure 7–6: Number of I/Os in Each Bank in EP3SL340 Devices in the 1760-pin FineLine BGA Pac (Note 1), (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | kage<br>7-12                                                                                           |

| Figure 7-6: Number of I/Os in Each Bank in EP3SL340 Devices in the 1760-pin FineLine BGA Pac                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | kage<br>7-12<br>7-13                                                                                   |

| Figure 7–6: Number of I/Os in Each Bank in EP3SL340 Devices in the 1760-pin FineLine BGA Pac (Note 1), (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | kage<br>7-12<br>7-13<br>7-21                                                                           |

| Figure 7–6: Number of I/Os in Each Bank in EP3SL340 Devices in the 1760-pin FineLine BGA Pac (Note 1), (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | kage<br>7-12<br>7-13<br>7-21<br>7-21                                                                   |

| Figure 7–6: Number of I/Os in Each Bank in EP3SL340 Devices in the 1760-pin FineLine BGA Pac (Note 1), (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | kage<br>7-12<br>7-13<br>7-21<br>7-24                                                                   |

| Figure 7–6: Number of I/Os in Each Bank in EP3SL340 Devices in the 1760-pin FineLine BGA Pac (Note 1), (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | kage<br>7-12<br>7-13<br>7-21<br>7-24<br>7-25                                                           |

| Figure 7–6: Number of I/Os in Each Bank in EP3SL340 Devices in the 1760-pin FineLine BGA Pac (Note 1), (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | kage<br>7-12<br>7-13<br>7-21<br>7-21<br>7-25<br>7-26                                                   |

| Figure 7–6: Number of I/Os in Each Bank in EP3SL340 Devices in the 1760-pin FineLine BGA Pac (Note 1), (2)  Figure 7–7: IOE Structure for Stratix III Devices (Note 1), (2)  Figure 7–8: On-Chip Series Termination without Calibration for Stratix III Devices  Figure 7–9: On-Chip Series Termination with Calibration for Stratix III Devices  Figure 7–10: On-Chip Parallel Termination with Calibration for Stratix III Devices  Figure 7–11: Dynamic Parallel OCT in Stratix III Devices  Figure 7–12: Differential Input On-Chip Termination  Figure 7–13: OCT Calibration Block (CB) Location in EP3SL50, EP3SL70, and EP3SE50 Devices (Note 1), (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | kage<br>7-12<br>7-13<br>7-21<br>7-24<br>7-25<br>7-26<br>Jote 1) .                                      |

| Figure 7–6: Number of I/Os in Each Bank in EP3SL340 Devices in the 1760-pin FineLine BGA Pac (Note 1), (2)  Figure 7–7: IOE Structure for Stratix III Devices (Note 1), (2)  Figure 7–8: On-Chip Series Termination without Calibration for Stratix III Devices  Figure 7–9: On-Chip Series Termination with Calibration for Stratix III Devices  Figure 7–10: On-Chip Parallel Termination with Calibration for Stratix III Devices  Figure 7–11: Dynamic Parallel OCT in Stratix III Devices  Figure 7–12: Differential Input On-Chip Termination  Figure 7–13: OCT Calibration Block (CB) Location in EP3SL50, EP3SL70, and EP3SE50 Devices (Note 1)  Figure 7–14: OCT Calibration Block (CB) Location in EP3SL110, EP3SL150, EP3SE80, and EP3SE110 (Note 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | kage<br>7-12<br>7-13<br>7-21<br>7-24<br>7-25<br>7-26<br>Note 1) .                                      |

| Figure 7–6: Number of I/Os in Each Bank in EP3SL340 Devices in the 1760-pin FineLine BGA Pac (Note 1), (2)  Figure 7–7: IOE Structure for Stratix III Devices (Note 1), (2)  Figure 7–8: On-Chip Series Termination without Calibration for Stratix III Devices  Figure 7–9: On-Chip Parallel Termination with Calibration for Stratix III Devices  Figure 7–10: On-Chip Parallel Termination with Calibration for Stratix III Devices  Figure 7–11: Dynamic Parallel OCT in Stratix III Devices  Figure 7–12: Differential Input On-Chip Termination  Figure 7–13: OCT Calibration Block (CB) Location in EP3SL50, EP3SL70, and EP3SE50 Devices (N7-27  Figure 7–14: OCT Calibration Block (CB) Location in EP3SL110, EP3SL150, EP3SE80, and EP3SE110 (Note 1)  Figure 7–15: OCT Calibration Block (CB) Location in EP3SL200, EP3SE260 and EP3SL340 (Note 1)                                                                                                                                                                                                                                                                                                                                                                        | kage<br>7-12<br>7-13<br>7-21<br>7-24<br>7-25<br>7-26<br>Note 1) .<br>Devices<br>7-28<br>) 7-28         |

| Figure 7–6: Number of I/Os in Each Bank in EP3SL340 Devices in the 1760-pin FineLine BGA Pac (Note 1), (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | kage<br>7-12<br>7-21<br>7-21<br>7-24<br>7-25<br>7-26<br>Jote 1) .<br>Devices<br>7-28<br>) 7-28         |

| Figure 7–6: Number of I/Os in Each Bank in EP3SL340 Devices in the 1760-pin FineLine BGA Pac (Note 1), (2)  Figure 7–7: IOE Structure for Stratix III Devices (Note 1), (2)  Figure 7–8: On-Chip Series Termination without Calibration for Stratix III Devices  Figure 7–9: On-Chip Series Termination with Calibration for Stratix III Devices  Figure 7–10: On-Chip Parallel Termination with Calibration for Stratix III Devices  Figure 7–11: Dynamic Parallel OCT in Stratix III Devices  Figure 7–12: Differential Input On-Chip Termination  Figure 7–13: OCT Calibration Block (CB) Location in EP3SL50, EP3SL70, and EP3SE50 Devices (N7-27  Figure 7–14: OCT Calibration Block (CB) Location in EP3SL110, EP3SL150, EP3SE80, and EP3SE110 (Note 1)  Figure 7–15: OCT Calibration Block (CB) Location in EP3SL200, EP3SE260 and EP3SL340 (Note 1)  Figure 7–16: Example of Sharing Multiple I/O Banks with One OCT Calibration Block (Note 1)  Figure 7–17: Signals Used for User Mode Calibration (Note 1)                                                                                                                                                                                                                | kage<br>7-12<br>7-13<br>7-21<br>7-24<br>7-25<br>7-26<br>Jote 1) .<br>Devices<br>7-28<br>) 7-29<br>7-30 |

| Figure 7–6: Number of I/Os in Each Bank in EP3SL340 Devices in the 1760-pin FineLine BGA Pac (Note 1), (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | kage 7-12 7-13 7-21 7-24 7-25 7-26 Note 1) .  Devices 7-28 ) 7-28 7-30 7-31                            |

| Figure 7–6: Number of I/Os in Each Bank in EP3SL340 Devices in the 1760-pin FineLine BGA Pac (Note 1), (2)  Figure 7–7: IOE Structure for Stratix III Devices (Note 1), (2)  Figure 7–8: On-Chip Series Termination without Calibration for Stratix III Devices  Figure 7–9: On-Chip Parallel Termination with Calibration for Stratix III Devices  Figure 7–10: On-Chip Parallel Termination with Calibration for Stratix III Devices  Figure 7–11: Dynamic Parallel OCT in Stratix III Devices  Figure 7–12: Differential Input On-Chip Termination  Figure 7–13: OCT Calibration Block (CB) Location in EP3SL50, EP3SL70, and EP3SE50 Devices (N7-27  Figure 7–14: OCT Calibration Block (CB) Location in EP3SL110, EP3SL150, EP3SE80, and EP3SE110 (Note 1)  Figure 7–15: OCT Calibration Block (CB) Location in EP3SL200, EP3SE260 and EP3SL340 (Note 1)  Figure 7–16: Example of Sharing Multiple I/O Banks with One OCT Calibration Block (Note 1)  Figure 7–17: Signals Used for User Mode Calibration (Note 1)  Figure 7–18: OCT User-Mode Signal Timing Waveform for One OCT Block  Figure 7–19: OCT User-Mode Signal Timing Waveform for Two OCT Block                                                                    | kage 7-12 7-13 7-21 7-24 7-25 7-26 Note 1) .  Devices 7-28 7-29 7-30 7-31 7-32                         |

| Figure 7–6: Number of I/Os in Each Bank in EP3SL340 Devices in the 1760-pin FineLine BGA Pac (Note 1), (2)  Figure 7–7: IOE Structure for Stratix III Devices (Note 1), (2)  Figure 7–8: On-Chip Series Termination without Calibration for Stratix III Devices  Figure 7–9: On-Chip Series Termination with Calibration for Stratix III Devices  Figure 7–10: On-Chip Parallel Termination with Calibration for Stratix III Devices  Figure 7–11: Dynamic Parallel OCT in Stratix III Devices  Figure 7–12: Differential Input On-Chip Termination  Figure 7–13: OCT Calibration Block (CB) Location in EP3SL50, EP3SL70, and EP3SE50 Devices (N7-27  Figure 7–14: OCT Calibration Block (CB) Location in EP3SL110, EP3SL150, EP3SE80, and EP3SE110 (Note 1)  Figure 7–15: OCT Calibration Block (CB) Location in EP3SL200, EP3SE260 and EP3SL340 (Note 1)  Figure 7–16: Example of Sharing Multiple I/O Banks with One OCT Calibration Block (Note 1)  Figure 7–17: Signals Used for User Mode Calibration (Note 1)  Figure 7–18: OCT User-Mode Signal Timing Waveform for One OCT Block  Figure 7–19: OCT User-Mode Signal Timing Waveform for Two OCT Blocks  Figure 7–20: SSTL I/O Standard Termination for Stratix III Devices | kage 7-12 7-13 7-21 7-24 7-25 7-26 Jote 1) .  Devices 7-28 7-29 7-31 7-32 7-33                         |

| Figure 7–6: Number of I/Os in Each Bank in EP3SL340 Devices in the 1760-pin FineLine BGA Pac (Note 1), (2)  Figure 7–7: IOE Structure for Stratix III Devices (Note 1), (2)  Figure 7–8: On-Chip Series Termination without Calibration for Stratix III Devices  Figure 7–9: On-Chip Parallel Termination with Calibration for Stratix III Devices  Figure 7–10: On-Chip Parallel Termination with Calibration for Stratix III Devices  Figure 7–11: Dynamic Parallel OCT in Stratix III Devices  Figure 7–12: Differential Input On-Chip Termination  Figure 7–13: OCT Calibration Block (CB) Location in EP3SL50, EP3SL70, and EP3SE50 Devices (N7-27  Figure 7–14: OCT Calibration Block (CB) Location in EP3SL110, EP3SL150, EP3SE80, and EP3SE110 (Note 1)  Figure 7–15: OCT Calibration Block (CB) Location in EP3SL200, EP3SE260 and EP3SL340 (Note 1)  Figure 7–16: Example of Sharing Multiple I/O Banks with One OCT Calibration Block (Note 1)  Figure 7–17: Signals Used for User Mode Calibration (Note 1)  Figure 7–18: OCT User-Mode Signal Timing Waveform for One OCT Block  Figure 7–19: OCT User-Mode Signal Timing Waveform for Two OCT Block                                                                    | kage 7-12 7-13 7-21 7-24 7-25 7-26 Note 1) .  Devices 7-28 7-29 7-30 7-31 7-32 7-33                    |

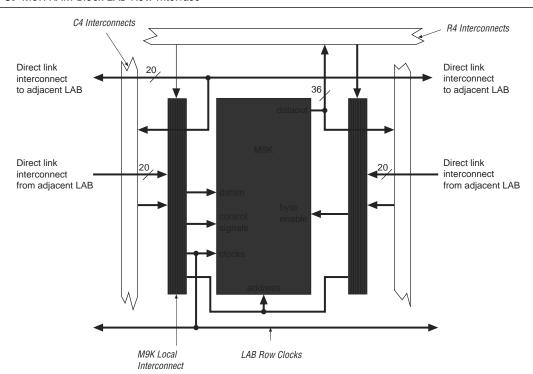

Figure 3-5. M9K RAM Block LAB Row Interface

The M144K blocks use eight interfaces in the same device column. The M144K block local interconnects are driven by R4, C4, and direct link interconnects from adjacent LABs on either the right or left side of the MRAM block. Up to 20 direct link input connections to the M144K block are possible from the left adjacent LABs and another 20 possible from the right adjacent LAB. M144K block outputs can also connect to the LABs on the block's left and right sides through direct link interconnect. Figure 3–6 shows the interface between the M144K RAM block and the logic array.

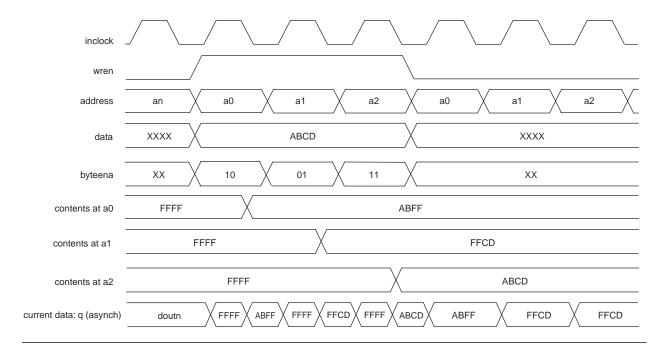

Figure 4–2 shows how the write enable (wren) and byte-enable (byteena) signals control the operations of the MLABs. The write operation in MLABs is triggered by failing clock edges.

Figure 4–2. Stratix III Byte-Enable Functional Waveform for MLABs

## **Packed Mode Support**

Stratix III M9K and M144K blocks support packed mode. The packed mode feature packs two independent single-port RAMs into one memory block. The Quartus II software automatically implements packed mode where appropriate by placing the physical RAM block into true dual-port mode and using the MSB of the address to distinguish between the two logical RAMs. The size of each independent single-port RAM must not exceed half of the target block size.

## **Address Clock Enable Support**

All Stratix III memory blocks support address clock enable, which holds the previous address value for as long as the signal is enabled (addressstall = 1). When the memory blocks are configured in dual-port mode, each port has its own independent address clock enable. The default value for the address clock enable signals is low (disabled).

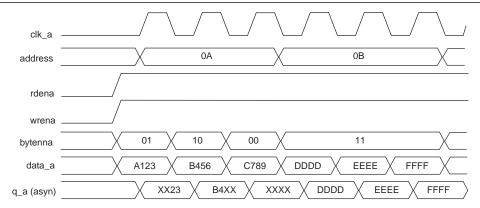

Figure 4–19 shows the sample functional waveforms of same-port read-during-write behavior with new data.

Figure 4–19. Same Port Read-During-Write: New Data Mode (Note 1)

#### Note to Figure 4-19:

(1) "X" can be a don't care value or current data at that location, depending on the setting chosen in the Quartus II software.

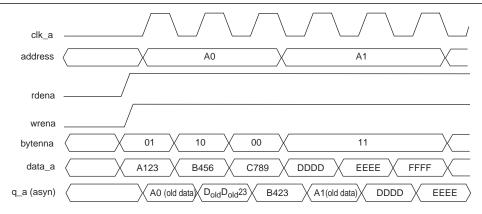

Figure 4–20 shows the sample functional waveforms of same-port read-during-write behavior with old data mode.

Figure 4–20. Same Port Read-During-Write: Old Data Mode (Note 1)

#### Note to Figure 4-20:

(1) Dold is the old data bit at address AO, AO (old data) is the old data at address AO, and A1 (old data) is the old data at address A1.

#### **Mixed-Port Read-During-Write Mode**

This mode applies to a RAM in simple or true dual-port mode which has one port reading and the other port writing to the same address location with the same clock.

In this mode you also have two output choices: old data or don't care. In old data mode, a read-during-write operation to different ports causes the RAM outputs to reflect the old data at that address location. In don't care mode, the same operation results in a "don't care" or "unknown" value on the RAM outputs.

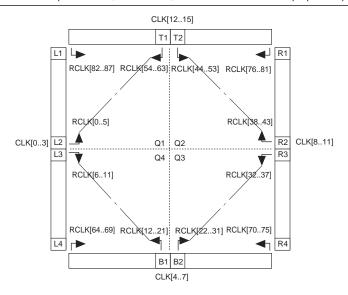

Figure 6-4. Regional Clock Networks (EP3SL200, EP3SE260, and EP3SL340 Devices) (Note 1)

#### Note to Figure 6-4:

(1) The corner RCLKs [64..87] can only be fed by their respective corner PLL outputs. Refer to Table 6-9 on page 6-13 for connectivity.

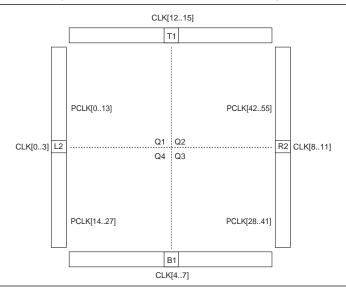

#### **Periphery Clock Networks**