Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 5700                                                       |

| Number of Logic Elements/Cells | 142500                                                     |

| Total RAM Bits                 | 6543360                                                    |

| Number of I/O                  | 488                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 0.86V ~ 1.15V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 780-BBGA, FCBGA                                            |

| Supplier Device Package        | 780-FBGA (29x29)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep3sl150f780c2n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

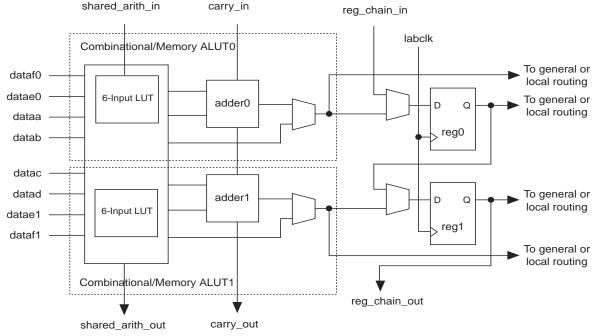

Figure 2-5. High-Level Block Diagram of the Stratix III ALM shared\_arith\_in carry\_in reg\_chain\_in

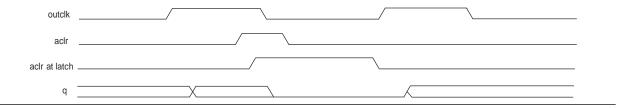

Figure 4–7. Output Latch Asynchronous Clear Waveform

You can selectively enable asynchronous clears per logical memory via the Quartus II RAM MegaWizard Plug-In Manager.

For more information, refer to the *RAM Megafunction User Guide*.

### **Error Correction Code Support**

Stratix III M144K blocks have built-in support for error correction code (ECC) when in ×64-wide simple dual-port mode. ECC allows you to detect and correct data errors in the memory array. The M144K blocks have a single-error-correction double-error-detection (SECDED) implementation. SECDED can detect and fix a single-bit error in a 64-bit word or detect two-bit errors in a 64-bit word. It cannot detect three or more errors.

The M144K ECC status is communicated via a three-bit status flag eccstatus [2..0]. The status flag can be either registered or unregistered. When registered, it uses the same clock and asynchronous clear signals as the output registers. When not registered, it cannot be asynchronously cleared.

Table 4–3 shows the truth table for the ECC status flags.

Table 4-3. Truth Table for ECC Status Flags

| Status                  | eccstatus[2] | eccstatus[1] | eccstatus[0] |

|-------------------------|--------------|--------------|--------------|

| No error                | 0            | 0            | 0            |

| Single error and fixed  | 0            | 1            | 1            |

| Double error and no fix | 1            | 0            | 1            |

| Illegal                 | 0            | 0            | 1            |

| Illegal                 | 0            | 1            | 0            |

| Illegal                 | 1            | 0            | 0            |

| Illegal                 | 1            | 1            | X            |

You cannot use the byte-enable feature when ECC is engaged.

Read during write "old data" mode is not supported when ECC is engaged.

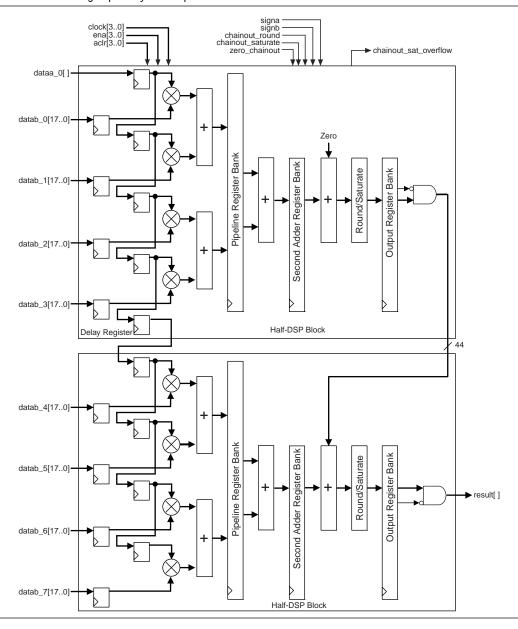

In Figure 5–23, the adder that adds the adjacent half DSP block to the current Four-Multiplier Adder is shown as the chainout adder for clarity. This scheme is used to chain and add multiple DSP blocks together. The output of the chainout adder can be registered. The registered chainout output can feed the lower adjacent DSP block for a chainout summation or it can feed general FPGA routing. The chainout result can be zeroed out by applying logic 1 on the dynamic zerochainout signal. The zerochainout signal can also be registered.

Figure 5-23. FIR Filter using Tap-Delay Line Input and Chained Cascade Summation of Final Result

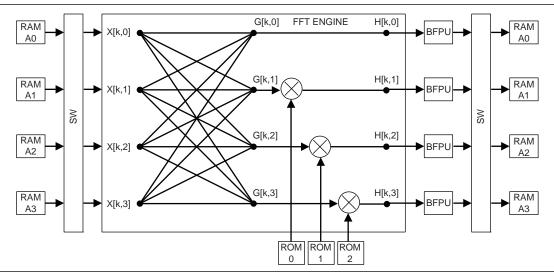

In Figure 5–25, a radix-4 butterfly is shown. Each butterfly requires three complex multipliers. This can be implemented in Stratix III using three half-DSP blocks assuming that the data and twiddle wordlengths are 18 bits or fewer.

Figure 5-25. Radix-4 Butterfly

# **Software Support**

Altera provides two distinct methods for implementing various modes of the DSP block in a design: instantiation and inference. Both methods use the following Quartus II megafunctions:

- LPM\_MULT

- ALTMULT\_ADD

- ALTMULT\_ACCUM

- ALTFP\_MULT

You can instantiate the megafunctions in the Quartus II software to use the DSP block. Alternatively, with inference, you can create an HDL design and synthesize it using a third-party synthesis tool (such as LeonardoSpectrum, Synplify, or Quartus II Native Synthesis) that infers the appropriate megafunction by recognizing multipliers, multiplier adders, multiplier accumulators, and shift functions. Using either method, the Quartus II software maps the functionality to the DSP blocks during compilation.

- For instructions about using the megafunctions and the *MegaWizard Plug-In Manager*, refer to the *Quartus II Software Help*.

- For more information, refer to the *Synthesis* section in volume 1 of the *Quartus II Development Software Handbook*.

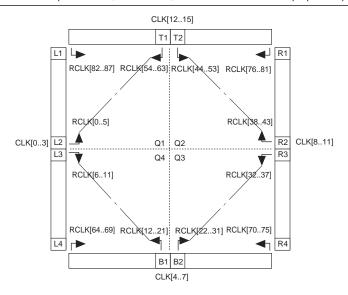

Figure 6-4. Regional Clock Networks (EP3SL200, EP3SE260, and EP3SL340 Devices) (Note 1)

#### Note to Figure 6-4:

(1) The corner RCLKs [64..87] can only be fed by their respective corner PLL outputs. Refer to Table 6-9 on page 6-13 for connectivity.

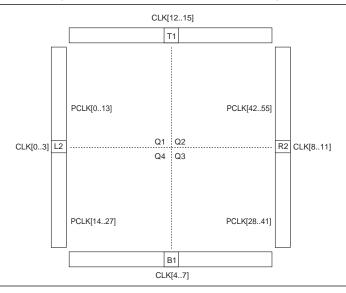

### **Periphery Clock Networks**

Periphery clock (PCLK) networks shown in Figure 6–5 to Figure 6–9 are a collection of individual clock networks driven from the periphery of the Stratix III device. Clock outputs from the DPA block, horizontal I/O pins, and internal logic can drive the PCLK networks. The EP3SL50, EP3SL70, and EP3SE50 devices contain 56 PCLKs; the EP3SL110, EP3SL150, EP3SL200, EP3SE80, and EP3SE110 devices contain 88 PCLKs; the EP3SE260 device contains 112 PCLKs, and the EP3SL340 device contains 132 PCLKs. These PCLKs have higher skew compared to GCLK and RCLK networks and can be used instead of general purpose routing to drive signals into and out of the Stratix III device.

Figure 6-5. Periphery Clock Networks (EP3SL50, EP3SL70, and EP3SE50 Devices)

### **PLL Control Signals**

You can use the following three signals to observe and control the PLL operation and resynchronization.

#### pfdena

Use the pfdena signal to maintain the most recent locked frequency so your system has time to store its current settings before shutting down. The pfdena signal controls the PFD output with a programmable gate. If you disable the PFD, the VCO is free running and the PLL output drifts. The PLL output jitter may not meet the datasheet specifications. The lock signal cannot be used as an indicator when the PFD is disabled.

#### areset

The areset signal is the reset or resynchronization input for each PLL. The device input pins or internal logic can drive these input signals. When areset is driven high, the PLL counters reset, clearing the PLL output and placing the PLL out-of-lock. The VCO is then set back to its nominal setting. When areset is driven low again, the PLL will resynchronize to its input as it re-locks.

You should assert the areset signal every time the PLL loses lock to guarantee the correct phase relationship between the PLL input clock and output clocks. You can set up the PLL to automatically reset (self reset) upon a loss-of-lock condition using the Quartus II MegaWizard Plug-In Manager. You should include the areset signal in designs if the following condition is true:

PLL reconfiguration or clock switchover is enabled in the design.

If the input clock to the PLL is not toggling or is unstable upon power up, assert the areset signal after the input clock is stable and within specifications.

#### locked

The lock signal is an asynchronous output of the PLL. The locked output of the PLL indicates that the PLL has locked onto the reference clock and the PLL clock outputs are operating at the desired phase and frequency set in the Quartus II MegaWizard Plug-In Manager. The lock detection circuit provides a signal to the core logic that gives an indication if the feedback clock has locked onto the reference clock both in phase and frequency.

Altera recommends that you use the areset and locked signals in your designs to control and observe the status of your PLL.

### **Clock Switchover**

The clock switchover feature allows the PLL to switch between two reference input clocks. Use this feature for clock redundancy or for a dual-clock domain application such as in a system that turns on the redundant clock if the previous clock stops running. The design can perform clock switchover automatically, when the clock is no longer toggling or based on a user control signal, clkswitch.

The rselodd bit indicates an odd divide factor for the VCO output frequency along with a 50% duty cycle. For example, if the post-scale divide factor is 3, the high- and low-time count values could be set to 2 and 1, respectively, to achieve this division. This implies a 67%-33% duty cycle. If you need a 50%-50% duty cycle, you can set the rselodd control bit to 1 to achieve this duty cycle despite an odd division factor. The PLL implements this duty cycle by transitioning the output clock from high to low on a falling edge of the VCO output clock. When you set rselodd = 1, you subtract 0.5 cycles from the high time and you add 0.5 cycles to the low time. For example:

- High-time count = 2 cycles

- Low-time count = 1 cycle

- rselodd = 1 effectively equals:

- High-time count = 1.5 cycles

- Low-time count = 1.5 cycles

- Duty cycle = (1.5/3) % high-time count and (1.5/3) % low-time count

### **Scan Chain Description**

The length of the scan chain varies for different Stratix III PLLs. The Top/Bottom PLLs have 10 post-scale counters and a 234-bit scan chain, while the Left/Right PLLs have 7 post-scale counters and a 180-bit scan chain. Table 6–16 lists the number of bits for each component of a Stratix III PLL.

**Table 6–16.** Top/Bottom PLL Reprogramming Bits (Part 1 of 2)

| Diagk Nama                 | Numbe   | Total     |         |

|----------------------------|---------|-----------|---------|

| Block Name                 | Counter | Other (1) | - Total |

| C9 (2)                     | 16      | 2         | 18      |

| C8                         | 16      | 2         | 18      |

| C7                         | 16      | 2         | 18      |

| C6 (3)                     | 16      | 2         | 18      |

| C5                         | 16      | 2         | 18      |

| C4                         | 16      | 2         | 18      |

| C3                         | 16      | 2         | 18      |

| C2                         | 16      | 2         | 18      |

| C1                         | 16      | 2         | 18      |

| CO                         | 16      | 2         | 18      |

| N                          | 16      | 2         | 18      |

| M                          | 16      | 2         | 18      |

| Charge Pump Current        | 0       | 3         | 3       |

| VCO Post-Scale divider (K) | 1       | 0         | 1       |

| Loop Filter Capacitor (4)  | 0       | 2         | 2       |

| Loop Filter Resistor       | 0       | 5         | 5       |

| Unused CP/LF               | 0       | 7         | 7       |

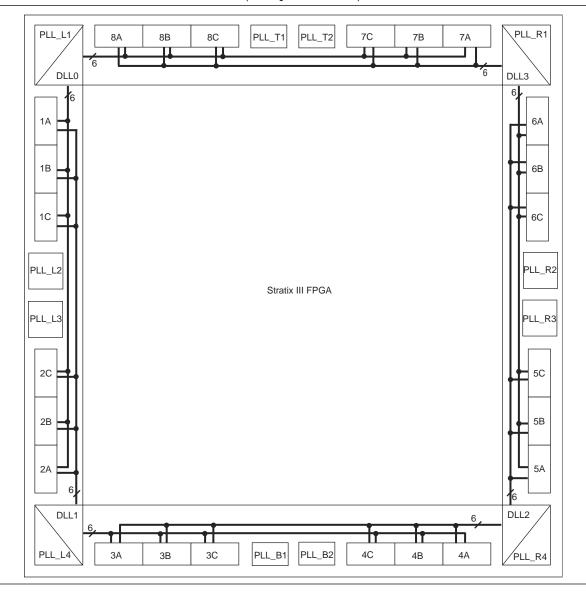

### **Modular I/O Banks**

The I/O pins in Stratix III devices are arranged in groups called modular I/O banks. Depending on device densities, the number of I/O banks range from 16 to 24 banks. The size of each bank is 24, 32, 36, 40, or 48 I/O pins. Figure 7–3 to Figure 7–5 show the number of I/O pins available in each I/O bank and packaging information for different sets of available devices.

In Stratix III devices, the maximum number of I/O banks per side is four or six, depending on the device density. When migrating between devices with a different number of I/O banks per side, it is the middle or "B" bank which is removed or inserted. For example, when moving from a 24-bank device to a 16-bank device, the banks that are dropped are "B" banks, namely: 1B, 2B, 3B, 4B, 5B, 6B, 7B, and 8B. Similarly, when moving from a 16-bank device to a 24-bank device, the banks that are added are "B" banks, namely: 1B, 2B, 3B, 4B, 5B, 6B, 7B, and 8B.

During migration from a smaller device to a larger device, the bank size increases or remains the same but never decreases. For example, banks may increase from a size of 24 I/O to a bank of size 32, 36, 40, or 48 I/O, but never decrease. Table 7–3 lists the increase in bank size when migrating from a smaller device to a larger device.

|            | Banks | Increase | Increase in Bank Size (number of I/O) |    |  |

|------------|-------|----------|---------------------------------------|----|--|

|            | А     | 40       | 48                                    | _  |  |

| Column I/O | В     | 24       | 48                                    | _  |  |

|            | С     | 24       | 32                                    | 48 |  |

| Row I/O    | А     | 32       | 48                                    | _  |  |

|            | В     | 24       | 36                                    | _  |  |

|            | C     | 2/       | 40                                    | 48 |  |

**Table 7–3.** Bank Migration Path with Increasing Device Size (Note 1)

#### Note to Table 7-3:

<sup>(1)</sup> Number of 1/0 shown does not include dedicated clock input pins CLK[1,3,8,10][p,n].

I/O Standard **Default Slew Rate Setting** 1.2-V, 1.5-V, 1.8-V, 2.5-V, 3.0-V, and 3.3-V LVTTL / LVCMOS 3 3.0-V PCI / PCI-X 3 3 SSTL-2, -18, -15 Class I and Class II 3 HSTL-18, -15, -12 Class I and II Differential SSTL-2, -18, -15 Class I and Class II 3 Differential HSTL-18, -15, -12 Class I and Class II 3 3 LVDS\_E\_1R, mini-LVDS\_E\_1R, RSDS\_E\_1R LVDS\_E\_3R, mini-LVDS\_E\_3R, RSDS\_E\_3R 3

**Table 7–6.** Default Programmable Slew Rate

You can use faster slew rates to improve the available timing margin in memory-interface applications or when the output pin has high-capacitive loading. Altera recommends performing IBIS or SPICE simulations to determine the right slew rate setting for your specific application.

### **Programmable Delay**

The Stratix III device IOE includes programmable delays (refer to Figure 7–7) that you can activate to ensure zero hold times, minimize setup times, or increase clock-to-output times. Each pin can have a different input delay from pin to input register or a delay from the output register to the output pin values to ensure that the bus has the same delay going into or out of the device. This feature helps read and time margins as it minimizes the uncertainties between signals in the bus.

For the programmable IOE delay specifications, refer to the *DC* and *Switching Characteristics of Stratix III Devices* chapter.

#### **Programmable Output Buffer Delay**

Stratix III devices support delay chains built inside the single-ended output buffer, as shown in Figure 7–7 on page 7–13. The delay chains can independently control the rising and falling edge delays of the output buffer, providing the ability to adjust the output-buffer duty cycle, compensate channel-to-channel skew, reduce simultaneous switching output (SSO) noise by deliberately introducing channel-to-channel skew, and improve high-speed memory-interface timing margins. Stratix III devices support four levels of output buffer delay settings. The default setting is **No Delay**.

For the programmable output buffer delay specifications, refer to the *DC and Switching Characteristics of Stratix III Devices* chapter.

# **Open-Drain Output**

Stratix III devices provide an optional open-drain output (equivalent to an open-collector output) for each I/O pin. When configured as open-drain, the logic value of the output is either high-Z or 0. Typically, an external pull-up resistor is required to provide logic high.

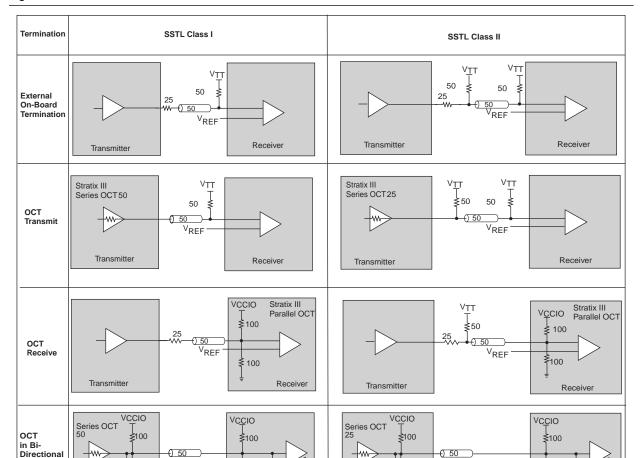

Figure 7–20. SSTL I/O Standard Termination for Stratix III Devices

### Note to Figure 7-20:

**≱**100

Pins (1)

(1) In Stratix III devices, series and parallel OCT cannot be used simultaneously. For more information, refer to "Dynamic OCT" on page 7-25.

**≱**100

Stratix III Series OCT

0 50

**\$**100

Stratix III

**≱**100

Stratix III Series OCT

You must pick your DQS and DQ pins manually for the  $\times 8$ ,  $\times 16/\times 18$ , or  $\times 32/\times 36$  DQS/DQ group whose members are being used for RUP and RDN because the Quartus II software might not be able to place this correctly when there are no specific pin assignments and might give you a "no-fit" instead.

Table 8–2 lists the maximum number of DQS/DQ groups per side of the Stratix III device. For a more detailed listing of the number of DQS/DQ groups available per bank in each Stratix III device, refer to Figure 8–3 through Figure 8–7. These figures represent the package bottom view of the Stratix III device.

**Table 8–2.** Number of DQS/DQ Groups in Stratix III Devices per Side (Part 1 of 2)

| Device              | Package                     | Side           | <b>×4</b> (1) | ×8/×9 | ×16/×18 | <b>×32/×36</b> (2) |

|---------------------|-----------------------------|----------------|---------------|-------|---------|--------------------|

|                     |                             | Left/ Right    | 12            | 4     | 0       | 0                  |

| EP3SE50             | 484-pin FineLine BGA        | Top/<br>Bottom | 5             | 2     | 0       | 0                  |

| EP3SL50<br>EP3SL70  |                             | Left/ Right    | 14            | 6     | 2       | 0                  |

|                     | 780-pin FineLine BGA        | Top/<br>Bottom | 17            | 8     | 2       | 0                  |

|                     |                             | Left/ Right    | 14            | 6     | 2       | 0                  |

| EP3SE80<br>EP3SE110 | 780-pin FineLine BGA        | Top/<br>Bottom | 17            | 8     | 2       | 0                  |

| EP3SL110            |                             | Left/ Right    | 26            | 12    | 4       | 0                  |

| EP3SL150            | 1152-pin FineLine BGA       | Top/<br>Bottom | 26            | 12    | 4       | 0                  |

|                     | 780-pin Hybrid FineLine BGA | Left/ Right    | 14            | 6     | 2       | 0                  |

|                     |                             | Top/<br>Bottom | 17            | 8     | 2       | 0                  |

|                     |                             | Left/ Right    | 26            | 12    | 4       | 0                  |

| EP3SL200            | 1152-pin FineLine BGA       | Top/<br>Bottom | 26            | 12    | 4       | 0                  |

|                     | 1517-pin FineLine BGA       | Left/ Right    | 34            | 16    | 6       | 0                  |

|                     |                             | Top/<br>Bottom | 38            | 18    | 8       | 4                  |

|                     |                             | Left/ Right    | 14            | 6     | 2       | 0                  |

| EP3SE260            | 780-pin Hybrid FineLine BGA | Top/<br>Bottom | 17            | 8     | 2       | 0                  |

|                     |                             | Left/ Right    | 26            | 12    | 4       | 0                  |

|                     | 1152-pin FineLine BGA       | Top/<br>Bottom | 26            | 12    | 4       | 0                  |

|                     |                             | Left/ Right    | 34            | 16    | 6       | 0                  |

|                     | 1517-pin FineLine BGA       | Top/<br>Bottom | 38            | 18    | 8       | 4                  |

Figure 8–11. Stratix III DLL and I/O Bank Locations (Package Bottom View)

The DLL can access the two adjacent sides from its location within the device. For example, DLL0 on the top left of the device can access the top side (I/O banks 7A, 7B, 7C, 8A, 8B, and 8C) and the left side of the device (I/O banks 1A, 1B, 1C, 2A, 2B, and 2C). This means that each I/O bank is accessible by two DLLs, giving more flexibility to create multiple frequencies and multiple-type interfaces. For example, you can design an interface spanning one side of the device or within two sides adjacent to the DLL. The DLL outputs the same DQS delay settings for both sides of the device adjacent to the DLL.

Each bank can use settings from either or both DLLs that the bank is adjacent to. For example, DQS1L can get its phase-shift settings from DLL0, while DQS2L can get its phase-shift settings from DLL1. Table 8–5 lists the DLL location and supported I/O banks for Stratix III devices.

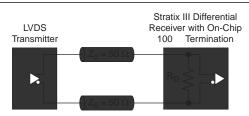

# **Differential I/O Termination**

Stratix III devices provide a  $100-\Omega$ OCT  $R_D$  option on each differential receiver channel for LVDS standards. OCT saves board space by eliminating the need to add external resistors on the board. You can enable OCT in the Quartus II software Assignment Editor.

OCT  $R_D$  is supported on all row I/O pins and SERDES block clock pins: CLK (0, 2, 9, and 11). It is not supported for column I/O pins, high-speed clock pins CLK [1, 3, 8, 10], or the corner PLL clock inputs.

Figure 9–11 shows the device OCT.

Figure 9-11. On-Chip Differential I/O Termination for Stratix III Devices

# Left/Right PLLs (PLL\_Lx/ PLL\_Rx)

Stratix III devices contain up to eight left/right PLLs, with up to four PLLs located on the left side and four on the right side of the device. The left PLLs can support high-speed differential I/O banks on the left side and the right PLLs can support banks on the right side of the device. The high-speed differential I/O receiver and transmitter channels use these left/right PLLs to generate the parallel global clocks (rx- or tx-clock) and high-speed clocks (difficalk). Figure 9–1 shows the locations of the left/right PLLs. The PLL VCO operates at the clock frequency of the data rate. Each left/right PLL offers a single serial data rate support, but up to two separate serialization and/or deserialization factors (from the C0 and C1 left/right PLL clock outputs). Clock switchover and dynamic left/right PLL reconfiguration is available in high-speed differential I/O support mode.

For more information, refer to the *Clock Network and PLLs in Stratix III Devices* chapter.

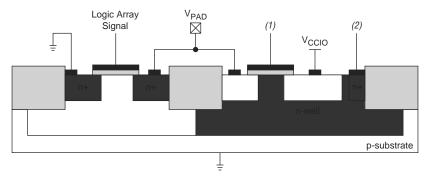

Figure 10–2 shows a transistor-level cross section of the Stratix III device I/O buffers. This design prevents leakage current from I/O pins to the  $V_{\text{CCIO}}$  supply when  $V_{\text{CCIO}}$  is powered before the other voltage supplies or if the I/O pad voltage is higher than  $V_{\text{CCIO}}$ . This also applies for sudden voltage spikes during hot insertion. The  $V_{\text{PAD}}$  leakage current charges the 3.3-V tolerant circuit capacitance.

Figure 10–2. Transistor Level Diagram of a Stratix III Device I/O Buffers

#### Notes to Figure 10-2:

- (1) This is the logic array signal or the larger of either the V<sub>CCIO</sub> or V<sub>PAD</sub> signal.

- (2) This is the larger of either the  $V_{CCIO}$  or  $V_{PAD}$  signal.

# **Power-On Reset Circuitry**

When power is applied to a Stratix III device, a POR event occurs when all the power supplies reach the recommended operating range within a certain period of time (specified as a maximum power supply ramp time;  $t_{\text{RAMP}}$ ). Hot socketing feature in Stratix III allows the required power supplies to be powered up in any sequence and at any time between them with each individual power supply must reach the recommended operating range within  $t_{\text{RAMP}}$ .

For maximum power supplies ramp-up time for Stratix III Devices, refer Table 10–1.

Stratix III devices provide a dedicated input pin (PORSEL) to select a POR delay time during power up. When the PORSEL pin is connected to ground, the POR delay time is 100 ms. When the PORSEL pin is set to high, the POR delay time is 12 ms.

The POR block consists of a regulator POR, satellite POR, and main POR to check the power supply levels for proper device configuration. The satellite POR monitors  $V_{\text{CCPD}}$  and  $V_{\text{CCPGM}}$  power supplies that are used in the configuration buffers for device programming. The POR block also checks for functionality of I/O level shifters powered by  $V_{\text{CCPD}}$  and  $V_{\text{CCPGM}}$  during power-up mode. The main POR checks the  $V_{\text{CC}}$  and  $V_{\text{CCL}}$  supplies used in core. The internal configuration memory supply, which is used during device configuration, is checked by the regulator POR block and is gated in the main POR block for the final POR trip. A simplified block diagram of the POR block is shown in Figure 10–3.

All configuration-related dedicated and dual function I/O pins must be powered by  $V_{\text{\tiny CCPCM}}$ .

The POR circuit does not monitor the power supplies listed in Table 10–3.

**Table 10–3.** Power Supplies That Are Not Monitored by the POR Circuitry

| Voltage Supply                                                                                  | Description                                                           | Setting (V)   |  |

|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------|--|

| V <sub>ccio</sub>                                                                               | I/O power supply                                                      |               |  |

| V <sub>CCA_PLL</sub>                                                                            | PLL analog global power supply                                        | 2.5           |  |

| V <sub>CCD_PLL</sub>                                                                            | PLL digital power supply                                              |               |  |

| V <sub>CC_CLKIN</sub> PLL differential clock input power supply (top and bottom I/O banks only) |                                                                       | 2.5           |  |

| V <sub>CCBAT</sub>                                                                              | Battery back-up power supply for design security volatile key storage | 1.0 – 3.3 (1) |  |

#### Note to Table 10-3:

(1) The nominal voltage for  $V_{CCBAT}$  is 3.0-V.

During power up, all power supplies listed in Table 10–2 and Table 10–3 are required to monotonically reach their full-rail values within  $t_{RAMP}$ .

The POR specification is designed to ensure that all the circuits in the Stratix III device are at certain known states during power up.

The POR signal pulse width is programmable using the PORSEL input pin. When PORSEL is set to low, the POR signal pulse width is set to 100 ms. A POR pulse width of 100 ms allows serial flash devices with 65 ms to 100 ms internal POR delay to be powered up and ready to receive the nSTATUS signal from Stratix III. When the PORSEL is set to high, the POR signal pulse width is set to 12 ms. A POR pulse width of 12 ms allows time for power supplies to ramp-up to full rail.

Table 11–6 defines the timing parameters for Stratix III devices for FPP configuration when the decompression feature, design security feature, or both are enabled.

**Table 11–6.** FPP Timing Parameters for Stratix III Devices with Decompression or Design Security Feature Enabled (Note 1)

| Symbol              | Parameter                                           | Minimum                       | Maximum | Units |

|---------------------|-----------------------------------------------------|-------------------------------|---------|-------|

| t <sub>CF2CD</sub>  | nCONFIG low to CONF_DONE low                        | _                             | 800     | ns    |

| t <sub>CF2ST0</sub> | nconfig low to nstatus low                          | _                             | 800     | ns    |

| t <sub>CFG</sub>    | nCONFIG low pulse width                             | 2                             | _       | μs    |

| t <sub>status</sub> | nSTATUS low pulse width                             | 10                            | 100 (2) | μS    |

| t <sub>CF2ST1</sub> | nCONFIG high to nSTATUS high                        | _                             | 100 (2) | μs    |

| t <sub>CF2CK</sub>  | nCONFIG high to first rising edge on DCLK           | 100                           | _       | μs    |

| t <sub>st2CK</sub>  | nSTATUS high to first rising edge of DCLK           | 2                             | _       | μS    |

| t <sub>DSU</sub>    | Data setup time before rising edge on DCLK          | 5                             | _       | ns    |

| t <sub>DH</sub>     | Data hold time after rising edge on DCLK            | 30                            | _       | ns    |

| t <sub>ch</sub>     | DCLK high time                                      | 4                             | _       | ns    |

| t <sub>cL</sub>     | DCLK low time                                       | 4                             | _       | ns    |

| t <sub>clk</sub>    | DCLK period                                         | 10                            | _       | ns    |

| f <sub>MAX</sub>    | DCLK frequency                                      | _                             | 100     | MHz   |

| t <sub>DATA</sub>   | Data rate                                           | _                             | 200     | Mbps  |

| t <sub>R</sub>      | Input rise time                                     | _                             | 40      | ns    |

| t                   | Input fall time                                     | _                             | 40      | ns    |

| t <sub>CD2UM</sub>  | CONF_DONE high to user mode (3)                     | 20                            | 100     | μs    |

| +                   | COME DONE high to CI MICD anabled                   | 4 × maximum                   |         |       |

| t <sub>cD2CU</sub>  | CONF_DONE high to CLKUSR enabled                    | DCLK period                   | _       | _     |

| +                   | GOVE DONE high to user mode with GI VIIGE entire on | t <sub>cd2CU</sub> + (4,436 × |         |       |

| t <sub>CD2UMC</sub> | CONF_DONE high to user mode with CLKUSR option on   | CLKUSR period)                | _       |       |

#### Notes to Table 11-6:

- (1) Use these timing parameters when the decompression and design security features are used.

- (2) This value is obtainable if you do not delay configuration by extending the nconfig or nstatus low pulse width.

- (3) The minimum and maximum numbers apply only if you chose the internal oscillator as the clock source for starting up the device.

# **FPP Configuration Using a Microprocessor**

In this configuration scheme, a microprocessor can control the transfer of configuration data from a storage device, such as flash memory, to the target Stratix III device.

All information in "FPP Configuration Using a MAX II Device as an External Host" on page 11–8 is also applicable when using a microprocessor as an external host. Refer to this section for all configuration and timing information.

An optional INIT\_DONE pin is available, which signals the end of initialization and the start of user-mode with a low-to-high transition. The Enable INIT\_DONE Output option is available in the Quartus II software on the General tab of the Device and Pin Options dialog box. If you use the INIT\_DONE pin, it will be high due to an external 10-kΩ pull-up resistor when nCONFIG is low and during the beginning of configuration. When the option bit to enable INIT\_DONE is programmed into the device (during the first frame of configuration data), the INIT\_DONE pin will go low. When initialization is complete, the INIT\_DONE pin will be released and pulled high. The MAX II device must be able to detect this low-to-high transition, which signals the device has entered user mode. When initialization is complete, the device enters user mode. In user mode, the user I/O pins will no longer have weak pull-up resistors and will function as assigned in your design.

To ensure DCLK and DATA0 are not left floating at the end of configuration, the MAX II device must drive them either high or low, whichever is convenient on your board. The DATA[0] pin is available as a user I/O pin after configuration. When you choose the PS scheme as a default in the Quartus II software, this I/O pin is tri-stated in user mode and should be driven by the MAX II device. To change this default option in the Quartus II software, click the **Dual-Purpose Pins** tab of the **Device and Pin Options** dialog box.

The configuration clock (DCLK) speed must be below the specified frequency to ensure correct configuration. No maximum DCLK period exists, which means you can pause configuration by halting DCLK for an indefinite amount of time.

If an error occurs during configuration, the device drives its nSTATUS pin low, resetting itself internally. The low signal on the nSTATUS pin also alerts the MAX II device that there is an error. If the **Auto-restart configuration after error** option (available in the Quartus II software on the **General** tab of the **Device and Pin Options** dialog box) is turned on, the Stratix III device releases nSTATUS after a reset time-out period (maximum of 100  $\mu$ s). After nSTATUS is released and pulled high by a pull-up resistor, the MAX II device can attempt to reconfigure the target device without needing to pulse nCONFIG low. If this option is turned off, the MAX II device must generate a low-to-high transition (with a low pulse of at least 2  $\mu$ s) on nCONFIG to restart the configuration process.

If you have enabled the **Auto-restart configuration after error** option, the nSTATUS pin transitions from high to low and back again to high when a configuration error is detected. This appears as a low pulse at the nSTATUS pin with a minimum pulse width of  $10~\mu s$  to a maximum pulse width of  $500~\mu s$ , as defined in the  $t_{STATUS}$  specification.

The MAX II device can also monitor the CONF\_DONE and INIT\_DONE pins to ensure successful configuration. The CONF\_DONE pin must be monitored by the MAX II device to detect errors and determine when programming completes. If all configuration data is sent, but CONF\_DONE or INIT\_DONE have not gone high, the MAX II device must reconfigure the target device.

If you use the optional CLKUSR pin and nCONFIG is pulled low to restart configuration during device initialization, you must ensure that CLKUSR continues toggling during the time nSTATUS is low (maximum of  $100~\mu s$ ).

Table 11–15 describes the optional configuration pins. If these optional configuration pins are not enabled in the Quartus II software, they are available as general-purpose user I/O pins. Therefore, during configuration, these pins function as user I/O pins and are tri-stated with weak pull-up resistors.

**Table 11–15.** Optional Configuration Pins

| Pin Name  | User Mode                                     | Pin Type          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------|-----------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKUSR    | N/A if option is on. I/O if option is off.    | Input             | Optional user-supplied clock input synchronizes the initialization of one or more devices. Enable this pin by turning on the <b>Enable user-supplied start-up clock</b> ( <b>CLKUSR</b> ) option in the Quartus II software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| INIT_DONE | N/A if option is on. I/O<br>if option is off. | Output open-drain | Use the Status pin to indicate when the device has initialized and is in user mode. When nconfigis low and during the beginning of configuration, the INIT_DONE pin is tri-stated and pulled high due to an external 10-k pull-up resistor. After the option bit to enable INIT_DONE is programmed into the device (during the first frame of configuration data), the INIT_DONE pin will go low. When initialization is complete, the INIT_DONE pin is released and pulled high and the device enters user mode. Thus, the monitoring circuitry must be able to detect a low-to-high transition. This pin is enabled by turning on the <b>Enable INIT_DONE output</b> option in the Quartus II software. |

| DEV_OE    | N/A if option is on. I/O<br>if option is off. | Input             | Optional pin that allows you to override all tri-states on the device. When this pin is driven low, all I/O pins are tri-stated, when this pin is driven high, all I/O pins behave as programmed. Enable this pin by turning on the <b>Enable device-wide output enable</b> ( <b>DEV_OE</b> ) option in the Quartus II software.                                                                                                                                                                                                                                                                                                                                                                          |

| DEV_CLRn  | N/A if option is on. I/O<br>if option is off. | Input             | Optional pin that allows you to override all clears on all device registers. When this pin is driven low, all registers are cleared. When this pin is driven high, all registers behave as programmed. This pin is enabled by turning on the <b>Enable device-wide reset</b> ( <b>DEV_CLRn</b> ) option in the Quartus II software.                                                                                                                                                                                                                                                                                                                                                                       |

SIII51014-1.5

## Introduction

This chapter provides an overview of the design security feature and its implementation on Stratix® III devices using advanced encryption standard (AES) as well as security modes available in Stratix III devices.

As Stratix III devices start to play a role in larger and more critical designs in competitive commercial and military environments, it is increasingly important to protect the designs from copying, reverse engineering, and tampering. Stratix III devices address these concerns and are the industry's only high-density, high-performance devices with both volatile and non-volatile security feature support. Stratix III devices have the ability to decrypt configuration bitstreams using the AES algorithm, an industry standard encryption algorithm that is FIPS-197 certified. They also have a design security feature that utilizes a 256-bit security key.

Altera® Stratix III devices store configuration data in static random access memory (SRAM) configuration cells during device operation. Because SRAM memory is volatile, SRAM cells must be loaded with configuration data each time the device powers-up. It is possible to intercept configuration data when it is being transmitted from the memory source (flash memory or a configuration device) to the device. The intercepted configuration data could then be used to configure another device.

When using the Stratix III design security feature, the security key is stored in the Stratix III device. Depending on the security mode, you can configure the Stratix III device using a configuration file that is encrypted with the same key, or for board testing, configured with a normal configuration file.

The design security feature is available when configuring Stratix III devices using the fast passive parallel (FPP) configuration mode with an external host (such as a MAX® II device or microprocessor), or when using fast active serial (AS) or passive serial (PS) configuration schemes. However, the design security feature is also available in remote update with fast AS configuration mode. The design security feature is not available when you are configuring your Stratix III device using Joint Test Action Group (JTAG)-based configuration. For more information, refer to "Supported Configuration Schemes" on page 14–5.

# **Stratix III Security Protection**

Stratix III device designs are protected from copying, reverse engineering, and tampering using configuration bitstream encryption.

# **Security Against Copying**

The security key is securely stored in the Stratix III device and cannot be read out through any interfaces. In addition, as configuration file read-back is not supported in Stratix III devices, the design information cannot be copied.

**Table 15–4.** Error Detection Registers (Part 2 of 2)

| Register                         | Description                                                                                                                                                                 |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAG Shift Register              | This register is accessible by the JTAG interface and allows the contents of the JTAG Update Register to be sampled and read out by the JTAG instruction SHIFT_EDERROR_REG. |

| User Shift Register              | This register is accessible by the core logic and allows the contents of the User Update Register to be sampled and read by the user logic.                                 |

| JTAG Fault Injection<br>Register | This 21-bit register is fully controlled by the JTAG instruction EDERROR_INJECT. This register holds the information of the error injection that you want in the bitstream. |

| Fault Injection Register         | The content of the JTAG Fault Injection Register is loaded in this 21-bit register when it is being updated.                                                                |

# **Error Detection Timing**

When the CRC feature is enabled through the Quartus II software, the device automatically activates the CRC process upon entering user mode, after configuration, and after initialization is complete.

If an error is detected within a frame, CRC\_ERROR is driven high at the end of the error location search, and after the Error Message Register gets updated. At the end of this cycle, the CRC\_ERROR pin is pulled low for a minimum 32 clock cycles. If the next frame also contains an error, the CRC\_ERROR is driven high again after the Error Message Register gets overwritten by the new value. You can start to unload the error message on each rising edge of CRC\_ERROR pin. The error detection runs until the device is reset.

Error detection circuitry runs off an internal configuration oscillator with a divisor that sets the maximum frequency. Table 15–5 lists the minimum and maximum error detection frequencies.

Table 15-5. Minimum and Maximum Error Detection Frequencies

| Device Type | Error Detection<br>Frequency | Maximum Error<br>Detection Frequency | Minimum Error Detection<br>Frequency | Valid Exponents ( <i>n</i> ) |

|-------------|------------------------------|--------------------------------------|--------------------------------------|------------------------------|

| Stratix III | 100 MHz / 2 <sup>n</sup>     | 50 MHz                               | 390 kHz                              | 1, 2, 3, 4, 5, 6, 7, 8       |

You can set a lower clock frequency by specifying a division factor in the Quartus II software (refer to "Software Support" on page 15–11). The divisor is a power of two (2), where n is between 1 and 8. The divisor ranges from 2 through 256. Refer to Equation 15–1.

### Equation 15-1.

Error detection frequency =

$$\frac{100 MHz}{2^n}$$

The error detection frequency reflects the frequency of the error detection process for a frame because the CRC calculation in Stratix III devices is done on a per-frame basis.