Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Last Time Buy                                                                    |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, SLDM, SPI, UART/USART                         |

| Peripherals                | PWM, WDT                                                                         |

| Number of I/O              | 99                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 2.7V                                                                     |

| Data Converters            | A/D 12x8/10b                                                                     |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-LQFP                                                                         |

| Supplier Device Package    | PG-TQFP-144-7                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc161cj16f40fbbfxuma1 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

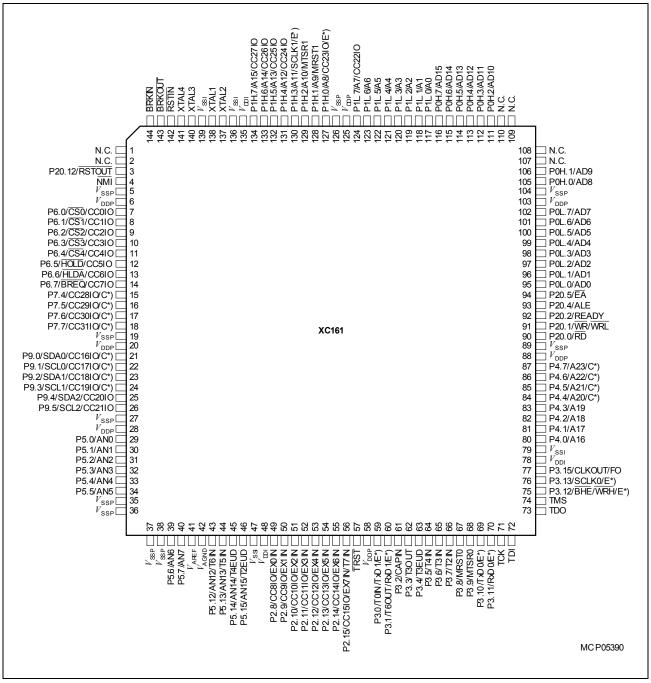

# 2.2 Pin Configuration and Definition

The pins of the XC161 are described in detail in **Table 2**, including all their alternate functions. **Figure 2** summarizes all pins in a condensed way, showing their location on the 4 sides of the package. E\*) and C\*) mark pins to be used as alternate external interrupt inputs, C\*) marks pins that can have CAN/SDLM interface lines assigned to them.

Figure 2 Pin Configuration (top view)

| Table 2     | Table 2         Pin Definitions and Functions |                 |                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                             |  |  |

|-------------|-----------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|--|

| Sym-<br>bol | Pin<br>Num.                                   | Input<br>Outp.  | Function                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                             |  |  |

| P20.12      | 3                                             | 10              | For details                                                                                                                                                                                                                                                                                                                                                                                                        | , please refer to the description of <b>P20</b> .                                                           |  |  |

| NMI         | 4                                             | 1               | Non-Maskable Interrupt Input. A high to low transition at this<br>pin causes the CPU to vector to the NMI trap routine. When<br>the PWRDN (power down) instruction is executed, the NMI<br>pin must be low in order to force the XC161 into power down<br>mode. If NMI is high, when PWRDN is executed, the part will<br>continue to run in normal mode.<br>If not used, pin NMI should be pulled high externally. |                                                                                                             |  |  |

| P6          |                                               | IO              | Port 6 is an 8-bit bidirectional I/O port. Each pin can be<br>programmed for input (output driver in high-impedance<br>state) or output (configurable as push/pull or open drain<br>driver). The input threshold of Port 6 is selectable (standard<br>or special).<br>The Port 6 pins also serve for alternate functions:                                                                                          |                                                                                                             |  |  |

| P6.0        | 7                                             | 0               | CS0                                                                                                                                                                                                                                                                                                                                                                                                                | Chip Select 0 Output,                                                                                       |  |  |

| P6.1        | 8                                             | I/O<br>O<br>I/O | CC0IO<br>CS1                                                                                                                                                                                                                                                                                                                                                                                                       | CAPCOM1: CC0 Capture Inp./Compare Output<br>Chip Select 1 Output,                                           |  |  |

| P6.2        | 9                                             | 0               | CC1IOCAPCOM1: CC1 Capture Inp./Compare OutputCS2Chip Select 2 Output,CS2CAPCOM1 CO2 Output,                                                                                                                                                                                                                                                                                                                        |                                                                                                             |  |  |

| P6.3        | 10                                            | I/O<br>O        | CS3                                                                                                                                                                                                                                                                                                                                                                                                                | CC2IOCAPCOM1: CC2 Capture Inp./Compare OutputCS3Chip Select 3 Output,                                       |  |  |

| P6.4        | 11                                            | I/O<br>O<br>I/O | CC3IO<br>CS4                                                                                                                                                                                                                                                                                                                                                                                                       | CAPCOM1: CC3 Capture Inp./Compare Output<br>Chip Select 4 Output,                                           |  |  |

| P6.5        | 12                                            | 1               | CC4IO<br>HOLD                                                                                                                                                                                                                                                                                                                                                                                                      | CAPCOM1: CC4 Capture Inp./Compare Output<br>External Master Hold Request Input,                             |  |  |

| P6.6        | 13                                            | I/O<br>O/I      | CC5IO<br>HLDA                                                                                                                                                                                                                                                                                                                                                                                                      | CAPCOM1: CC5 Capture Inp./Compare Output<br>Hold Acknowledge Output (master mode) or<br>Input (slave mode), |  |  |

| P6.7        | 14                                            | I/O<br>O<br>I/O | CC6IO<br>BREQ<br>CC7IO                                                                                                                                                                                                                                                                                                                                                                                             | CAPCOM1: CC6 Capture Inp./Compare Output<br>Bus Request Output,<br>CAPCOM1: CC7 Capture Inp./Compare Output |  |  |

| Table 2     | Pi          | Pin Definitions and Functions (cont'd) |                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|-------------|-------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Sym-<br>bol | Pin<br>Num. | Input<br>Outp.                         | Function                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| P9          |             | IO                                     | Port 9 is a 6-bit bidirectional I/O port. Each pin can be<br>programmed for input (output driver in high-impedance<br>state) or output (configurable as push/pull or open drain<br>driver). The input threshold of Port 9 is selectable (standard<br>or special).<br>The following Port 9 pins also serve for alternate functions: <sup>1)</sup> |  |  |  |

| P9.0        | 21          | I/O<br>I<br>I/O                        | CC16IO CAPCOM2: CC16 Capture Inp./Compare Outp.,<br>CAN2_RxD CAN Node 2 Receive Data Input,<br>SDA0 IIC Bus Data Line 0                                                                                                                                                                                                                          |  |  |  |

| P9.1        | 22          | I/O<br>O<br>I/O                        | CC17IOCAPCOM2: CC17 Capture Inp./Compare Outp.,CAN2_TxDCAN Node 2 Transmit Data Output,SCL0IIC Bus Clock Line 0                                                                                                                                                                                                                                  |  |  |  |

| P9.2        | 23          | I/O<br>I<br>O<br>I/O                   | CC18IOCAPCOM2: CC18 Capture Inp./Compare Outp.,CAN1_RxD CAN Node 1 Receive Data Input,SDL_TxDSDLM Transmit Data Output,SDA1IIC Bus Data Line 1                                                                                                                                                                                                   |  |  |  |

| P9.3        | 24          | I/O<br>O<br>I<br>I/O                   | CC19IOCAPCOM2: CC19 Capture Inp./Compare Outp.,CAN1_TxDCAN Node 1 Transmit Data Output,SDL_RxDSDLM Receive Data Input,SCL1IIC Bus Clock Line 1                                                                                                                                                                                                   |  |  |  |

| P9.4        | 25          | I/O<br>I/O                             | CC20IO CAPCOM2: CC20 Capture Inp./Compare Outp.,<br>SDA2 IIC Bus Data Line 2                                                                                                                                                                                                                                                                     |  |  |  |

| P9.5        | 26          | I/O<br>I/O                             | CC21IO CAPCOM2: CC21 Capture Inp./Compare Outp.,<br>SCL2 IIC Bus Clock Line 2                                                                                                                                                                                                                                                                    |  |  |  |

| P5          |             | I                                      | Port 5 is a 12-bit input-only port.<br>The pins of Port 5 also serve as analog input channels for the A/D converter, or they serve as timer inputs:                                                                                                                                                                                              |  |  |  |

| P5.0        | 29          | 1                                      | ANO                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| P5.1        | 30          | 1                                      | AN1                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| P5.2        | 31          | 1                                      | AN2                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| P5.3        | 32          | 1                                      | AN3                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| P5.4        | 33          | 1                                      | AN4                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| P5.5        | 34          | 1                                      | AN5                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| P5.6        | 39          |                                        | AN6                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| P5.7        | 40          |                                        | AN7                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| P5.12       | 43          |                                        | AN12, T6IN GPT2 Timer T6 Count/Gate Input                                                                                                                                                                                                                                                                                                        |  |  |  |

| P5.13       | 44          |                                        | AN13, T5IN GPT2 Timer T5 Count/Gate Input                                                                                                                                                                                                                                                                                                        |  |  |  |

| P5.14       | 45          |                                        | AN14, T4EUD GPT1 Timer T4 Ext. Up/Down Ctrl. Inp.                                                                                                                                                                                                                                                                                                |  |  |  |

| P5.15       | 46          | 1                                      | AN15, T2EUD GPT1 Timer T2 Ext. Up/Down Ctrl. Inp.                                                                                                                                                                                                                                                                                                |  |  |  |

| Table 2     | Pi          | n Defini       | efinitions and Functions (cont'd)                       |                                                                                                                                                                                                                                                                    |  |  |

|-------------|-------------|----------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Sym-<br>bol | Pin<br>Num. | Input<br>Outp. | Function                                                |                                                                                                                                                                                                                                                                    |  |  |

| P3          |             | IO             | programm<br>state) or or<br>driver). The<br>or special) | Port 3 is a 15-bit bidirectional I/O port. Each pin can be<br>programmed for input (output driver in high-impedance<br>state) or output (configurable as push/pull or open drain<br>driver). The input threshold of Port 3 is selectable (standard<br>or special). |  |  |

| P3.0        | 59          | <br>0<br>      | T0IN<br>TxD1<br>EX1IN                                   | ing Port 3 pins also serve for alternate functions:<br>CAPCOM1 Timer T0 Count Input,<br>ASC1 Clock/Data Output (Async./Sync),<br>Fast External Interrupt 1 Input (alternate pin B)                                                                                 |  |  |

| P3.1        | 60          | 0<br>I/O<br>I  | T6OUT<br>RxD1<br>EX1IN                                  | GPT2 Timer T6 Toggle Latch Output,<br>ASC1 Data Input (Async.) or Inp./Outp. (Sync.),<br>Fast External Interrupt 1 Input (alternate pin A)                                                                                                                         |  |  |

| P3.2        | 61          | 1              | CAPIN                                                   | GPT2 Register CAPREL Capture Input                                                                                                                                                                                                                                 |  |  |

| P3.3        | 62          | 0              | T3OUT                                                   | GPT1 Timer T3 Toggle Latch Output                                                                                                                                                                                                                                  |  |  |

| P3.4        | 63          | 1              | T3EUD                                                   | GPT1 Timer T3 External Up/Down Control Input                                                                                                                                                                                                                       |  |  |

| P3.5        | 64          | 1              | T4IN                                                    | GPT1 Timer T4 Count/Gate/Reload/Capture Inp                                                                                                                                                                                                                        |  |  |

| P3.6        | 65          | 1              | T3IN                                                    | GPT1 Timer T3 Count/Gate Input                                                                                                                                                                                                                                     |  |  |

| P3.7        | 66          | 1              | T2IN                                                    | GPT1 Timer T2 Count/Gate/Reload/Capture Inp                                                                                                                                                                                                                        |  |  |

| P3.8        | 67          | I/O            | MRST0                                                   | SSC0 Master-Receive/Slave-Transmit In/Out.                                                                                                                                                                                                                         |  |  |

| P3.9        | 68          | I/O            | MTSR0                                                   | SSC0 Master-Transmit/Slave-Receive Out/In.                                                                                                                                                                                                                         |  |  |

| P3.10       | 69          | 0              | TxD0 ASC0 Clock/Data Output (Async./Sync.),             |                                                                                                                                                                                                                                                                    |  |  |

|             |             | 1              | EX2IN                                                   | Fast External Interrupt 2 Input (alternate pin B)                                                                                                                                                                                                                  |  |  |

| P3.11       | 70          | I/O<br>I       | RxD0<br>EX2IN                                           | ASC0 Data Input (Async.) or Inp./Outp. (Sync.),<br>Fast External Interrupt 2 Input (alternate pin A)                                                                                                                                                               |  |  |

| P3.12       | 75          | 0<br>0<br>I    | BHE<br>WRH<br>EX3IN                                     | External Memory High Byte Enable Signal,<br>External Memory High Byte Write Strobe,<br>Fast External Interrupt 3 Input (alternate pin B)                                                                                                                           |  |  |

| P3.13       | 76          | I/O<br>I       | SCLK0<br>EX3IN                                          | SSC0 Master Clock Output/Slave Clock Input.,<br>Fast External Interrupt 3 Input (alternate pin A)                                                                                                                                                                  |  |  |

| P3.15       | 77          | 0<br>0         | CLKOUT<br>FOUT                                          | Master Clock Output,<br>Programmable Frequency Output                                                                                                                                                                                                              |  |  |

| ТСК         | 71          | I              | Debug Sys                                               | stem: JTAG Clock Input                                                                                                                                                                                                                                             |  |  |

| TDI         | 72          | I              | Debug Sys                                               | stem: JTAG Data In                                                                                                                                                                                                                                                 |  |  |

| TDO         | 73          | 0              | Debug Sys                                               | stem: JTAG Data Out                                                                                                                                                                                                                                                |  |  |

| TMS         | 74          |                | Debug Sys                                               | Debug System: JTAG Test Mode Selection                                                                                                                                                                                                                             |  |  |

| Table 2                                                            | Pi                                           | n Definit | ions and F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | unctions (cont'd)                                                                                |  |  |  |

|--------------------------------------------------------------------|----------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|

| Sym-                                                               | Pin                                          | Input     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                  |  |  |  |

| bol                                                                | Num.                                         | Outp.     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                  |  |  |  |

| PORT0<br>POL.0 -<br>POL.7,<br>POH.0,<br>POH.1,<br>POH.2 -<br>POH.7 | 95 -<br>102,<br>105,<br>106,<br>111 -<br>116 | IO        | PORT0 consists of the two 8-bit bidirectional I/O ports P0L<br>and P0H. Each pin can be programmed for input (output<br>driver in high-impedance state) or output.<br>In case of an external bus configuration, PORT0 serves as<br>the address (A) and address/data (AD) bus in multiplexed<br>bus modes and as the data (D) bus in demultiplexed bus<br>modes.<br><b>Demultiplexed bus modes:</b><br>8-bit data bus: P0H = I/O, P0L = D7 - D0<br>16-bit data bus: P0H = D15 - D8, P0L = D7 - D0<br><b>Multiplexed bus modes:</b><br>8-bit data bus: P0H = A15 - A8, P0L = AD7 - AD0<br>16-bit data bus: P0H = AD15 - AD8, P0L = AD7 - AD0 |                                                                                                  |  |  |  |

|                                                                    |                                              |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Note: At the end of an external reset (EA = 0) PORT0 also may input configuration values.        |  |  |  |

| PORT1                                                              |                                              | 10        | PORT1 consists of the two 8-bit bidirectional I/O ports P1L<br>and P1H. Each pin can be programmed for input (output<br>driver in high-impedance state) or output.<br>PORT1 is used as the 16-bit address bus (A) in<br>demultiplexed bus modes (also after switching from a<br>demultiplexed to a multiplexed bus mode).<br>The following PORT1 pins also serve for alt. functions:                                                                                                                                                                                                                                                       |                                                                                                  |  |  |  |

| P1L.0 -<br>P1L.6                                                   | 117 -<br>123                                 | 0         | (A0-6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Address output only                                                                              |  |  |  |

| P1L.7                                                              | 123                                          | I/O       | CC22IO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CAPCOM2: CC22 Capture Inp./Compare Outp.                                                         |  |  |  |

| P1H.0                                                              | 127                                          | I/O<br>I  | CC23IO<br>EX0IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CAPCOM2: CC23 Capture Inp./Compare Outp.,<br>Fast External Interrupt 0 Input (alternate pin B)   |  |  |  |

| P1H.1                                                              | 128                                          | I/O       | MRST1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SSC1 Master-Receive/Slave-Transmit In/Outp.                                                      |  |  |  |

| P1H.2                                                              | 129                                          | I/O       | MTSR1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SSC1 Master-Transmit/Slave-Receive Out/Inp.                                                      |  |  |  |

| P1H.3                                                              | 130                                          | 1/O<br>1  | SCLK1<br>EX0IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SSC1 Master Clock Output/Slave Clock Input,<br>Fast External Interrupt 0 Input (alternate pin A) |  |  |  |

| P1H.4                                                              | 131                                          | I/O       | CC24IO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CAPCOM2: CC24 Capture Inp./Compare Outp.                                                         |  |  |  |

| P1H.5                                                              | 132                                          | 1/0       | CC25IO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CAPCOM2: CC25 Capture Inp./Compare Outp.                                                         |  |  |  |

| P1H.6                                                              | 133                                          | 1/0       | CC26IO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CAPCOM2: CC26 Capture Inp./Compare Outp.                                                         |  |  |  |

| P1H.7                                                              | 134                                          | I/O       | CC27IO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CAPCOM2: CC27 Capture Inp./Compare Outp.                                                         |  |  |  |

# Table 4XC161 Interrupt Nodes (cont'd)

| Source of Interrupt or PEC<br>Service Request | Control<br>Register | Vector<br>Location <sup>1)</sup> | Trap<br>Number                    |

|-----------------------------------------------|---------------------|----------------------------------|-----------------------------------|

| CAPCOM Register 29                            | CC2_CC29IC          | xx'0110 <sub>H</sub>             | 44 <sub>H</sub> / 68 <sub>D</sub> |

| CAPCOM Register 30                            | CC2_CC30IC          | xx'0114 <sub>H</sub>             | 45 <sub>H</sub> / 69 <sub>D</sub> |

| CAPCOM Register 31                            | CC2_CC31IC          | xx'0118 <sub>H</sub>             | 46 <sub>H</sub> / 70 <sub>D</sub> |

| CAPCOM Timer 0                                | CC1_T0IC            | xx'0080 <sub>H</sub>             | 20 <sub>H</sub> / 32 <sub>D</sub> |

| CAPCOM Timer 1                                | CC1_T1IC            | xx'0084 <sub>H</sub>             | 21 <sub>H</sub> / 33 <sub>D</sub> |

| CAPCOM Timer 7                                | CC2_T7IC            | xx'00F4 <sub>H</sub>             | 3D <sub>H</sub> / 61 <sub>D</sub> |

| CAPCOM Timer 8                                | CC2_T8IC            | xx'00F8 <sub>H</sub>             | 3E <sub>H</sub> / 62 <sub>D</sub> |

| GPT1 Timer 2                                  | GPT12E_T2IC         | xx'0088 <sub>H</sub>             | 22 <sub>H</sub> / 34 <sub>D</sub> |

| GPT1 Timer 3                                  | GPT12E_T3IC         | xx'008C <sub>H</sub>             | 23 <sub>H</sub> / 35 <sub>D</sub> |

| GPT1 Timer 4                                  | GPT12E_T4IC         | xx'0090 <sub>H</sub>             | 24 <sub>H</sub> / 36 <sub>D</sub> |

| GPT2 Timer 5                                  | GPT12E_T5IC         | xx'0094 <sub>H</sub>             | 25 <sub>H</sub> / 37 <sub>D</sub> |

| GPT2 Timer 6                                  | GPT12E_T6IC         | xx'0098 <sub>H</sub>             | 26 <sub>H</sub> / 38 <sub>D</sub> |

| GPT2 CAPREL Register                          | GPT12E_CRIC         | xx'009C <sub>H</sub>             | 27 <sub>H</sub> / 39 <sub>D</sub> |

| A/D Conversion Complete                       | ADC_CIC             | xx'00A0 <sub>H</sub>             | 28 <sub>H</sub> / 40 <sub>D</sub> |

| A/D Overrun Error                             | ADC_EIC             | xx'00A4 <sub>H</sub>             | 29 <sub>H</sub> / 41 <sub>D</sub> |

| ASC0 Transmit                                 | ASC0_TIC            | xx'00A8 <sub>H</sub>             | 2A <sub>H</sub> / 42 <sub>D</sub> |

| ASC0 Transmit Buffer                          | ASC0_TBIC           | xx'011C <sub>H</sub>             | 47 <sub>H</sub> / 71 <sub>D</sub> |

| ASC0 Receive                                  | ASC0_RIC            | xx'00AC <sub>H</sub>             | 2B <sub>H</sub> / 43 <sub>D</sub> |

| ASC0 Error                                    | ASC0_EIC            | xx'00B0 <sub>H</sub>             | 2C <sub>H</sub> / 44 <sub>D</sub> |

| ASC0 Autobaud                                 | ASC0_ABIC           | xx'017C <sub>H</sub>             | 5F <sub>H</sub> / 95 <sub>D</sub> |

| SSC0 Transmit                                 | SSC0_TIC            | xx'00B4 <sub>H</sub>             | 2D <sub>H</sub> / 45 <sub>D</sub> |

| SSC0 Receive                                  | SSC0_RIC            | xx'00B8 <sub>H</sub>             | 2E <sub>H</sub> / 46 <sub>D</sub> |

| SSC0 Error                                    | SSC0_EIC            | xx'00BC <sub>H</sub>             | 2F <sub>H</sub> / 47 <sub>D</sub> |

| IIC Data Transfer Event                       | IIC_DTIC            | xx'0100 <sub>H</sub>             | 40 <sub>H</sub> / 64 <sub>D</sub> |

| IIC Protocol Event                            | IIC_PEIC            | xx'0104 <sub>H</sub>             | 41 <sub>H</sub> / 65 <sub>D</sub> |

| PLL/OWD                                       | PLLIC               | xx'010C <sub>H</sub>             | 43 <sub>H</sub> / 67 <sub>D</sub> |

| ASC1 Transmit                                 | ASC1_TIC            | xx'0120 <sub>H</sub>             | 48 <sub>H</sub> / 72 <sub>D</sub> |

| ASC1 Transmit Buffer                          | ASC1_TBIC           | xx'0178 <sub>H</sub>             | 5E <sub>H</sub> / 94 <sub>D</sub> |

| ASC1 Receive                                  | ASC1_RIC            | xx'0124 <sub>H</sub>             | 49 <sub>H</sub> / 73 <sub>D</sub> |

| ASC1 Error                                    | ASC1_EIC            | xx'0128 <sub>H</sub>             | 4A <sub>H</sub> / 74 <sub>D</sub> |

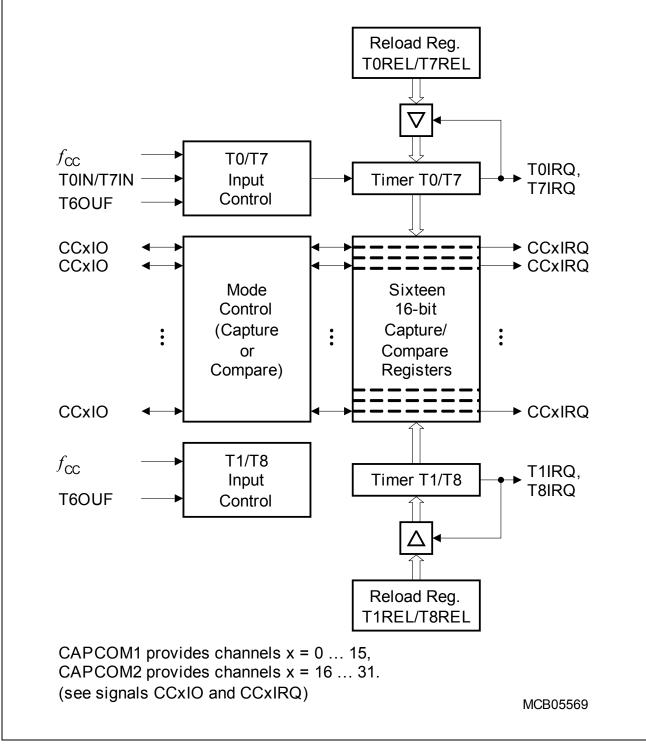

# 3.6 Capture/Compare Units (CAPCOM1/2)

The CAPCOM units support generation and control of timing sequences on up to 32 channels with a maximum resolution of 1 system clock cycle (8 cycles in staggered mode). The CAPCOM units are typically used to handle high speed I/O tasks such as pulse and waveform generation, pulse width modulation (PMW), Digital to Analog (D/A) conversion, software timing, or time recording relative to external events.

Four 16-bit timers (T0/T1, T7/T8) with reload registers provide two independent time bases for each capture/compare register array.

The input clock for the timers is programmable to several prescaled values of the internal system clock, or may be derived from an overflow/underflow of timer T6 in module GPT2. This provides a wide range of variation for the timer period and resolution and allows precise adjustments to the application specific requirements. In addition, external count inputs for CAPCOM timers T0 and T7 allow event scheduling for the capture/compare registers relative to external events.

Both of the two capture/compare register arrays contain 16 dual purpose capture/compare registers, each of which may be individually allocated to either CAPCOM timer T0 or T1 (T7 or T8, respectively), and programmed for capture or compare function.

All registers of each module have each one port pin associated with it which serves as an input pin for triggering the capture function, or as an output pin to indicate the occurrence of a compare event.

| Compare Modes           | Function                                                                                                                        |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Mode 0                  | Interrupt-only compare mode;<br>several compare interrupts per timer period are possible                                        |

| Mode 1                  | Pin toggles on each compare match;<br>several compare events per timer period are possible                                      |

| Mode 2                  | Interrupt-only compare mode;<br>only one compare interrupt per timer period is generated                                        |

| Mode 3                  | Pin set '1' on match; pin reset '0' on compare timer overflow;<br>only one compare event per timer period is generated          |

| Double Register<br>Mode | Two registers operate on one pin;<br>pin toggles on each compare match;<br>several compare events per timer period are possible |

| Single Event Mode       | Generates single edges or pulses;<br>can be used with any compare mode                                                          |

| Table 6 Compare Wodes (CAPCOWT/2) | Table 6 | <b>Compare Modes</b> | (CAPCOM1/2) |

|-----------------------------------|---------|----------------------|-------------|

|-----------------------------------|---------|----------------------|-------------|

Figure 5 CAPCOM1/2 Unit Block Diagram

# 3.7 General Purpose Timer (GPT12E) Unit

The GPT12E unit represents a very flexible multifunctional timer/counter structure which may be used for many different time related tasks such as event timing and counting, pulse width and duty cycle measurements, pulse generation, or pulse multiplication.

The GPT12E unit incorporates five 16-bit timers which are organized in two separate modules, GPT1 and GPT2. Each timer in each module may operate independently in a number of different modes, or may be concatenated with another timer of the same module.

Each of the three timers T2, T3, T4 of **module GPT1** can be configured individually for one of four basic modes of operation, which are Timer, Gated Timer, Counter, and Incremental Interface Mode. In Timer Mode, the input clock for a timer is derived from the system clock, divided by a programmable prescaler, while Counter Mode allows a timer to be clocked in reference to external events.

Pulse width or duty cycle measurement is supported in Gated Timer Mode, where the operation of a timer is controlled by the 'gate' level on an external input pin. For these purposes, each timer has one associated port pin (TxIN) which serves as gate or clock input. The maximum resolution of the timers in module GPT1 is 4 system clock cycles.

The count direction (up/down) for each timer is programmable by software or may additionally be altered dynamically by an external signal on a port pin (TxEUD) to facilitate e.g. position tracking.

In Incremental Interface Mode the GPT1 timers (T2, T3, T4) can be directly connected to the incremental position sensor signals A and B via their respective inputs TxIN and TxEUD. Direction and count signals are internally derived from these two input signals, so the contents of the respective timer Tx corresponds to the sensor position. The third position sensor signal TOP0 can be connected to an interrupt input.

Timer T3 has an output toggle latch (T3OTL) which changes its state on each timer overflow/underflow. The state of this latch may be output on pin T3OUT e.g. for time out monitoring of external hardware components. It may also be used internally to clock timers T2 and T4 for measuring long time periods with high resolution.

In addition to their basic operating modes, timers T2 and T4 may be configured as reload or capture registers for timer T3. When used as capture or reload registers, timers T2 and T4 are stopped. The contents of timer T3 is captured into T2 or T4 in response to a signal at their associated input pins (TxIN). Timer T3 is reloaded with the contents of T2 or T4 triggered either by an external signal or by a selectable state transition of its toggle latch T3OTL. When both T2 and T4 are configured to alternately reload T3 on opposite state transitions of T3OTL with the low and high times of a PWM signal, this signal can be constantly generated without software intervention.

count direction (up/down) for each timer is programmable by software or may additionally be altered dynamically by an external signal on a port pin (TxEUD). Concatenation of the timers is supported via the output toggle latch (T6OTL) of timer T6, which changes its state on each timer overflow/underflow.

The state of this latch may be used to clock timer T5, and/or it may be output on pin T6OUT. The overflows/underflows of timer T6 can additionally be used to clock the CAPCOM1/2 timers, and to cause a reload from the CAPREL register.

The CAPREL register may capture the contents of timer T5 based on an external signal transition on the corresponding port pin (CAPIN), and timer T5 may optionally be cleared after the capture procedure. This allows the XC161 to measure absolute time differences or to perform pulse multiplication without software overhead.

The capture trigger (timer T5 to CAPREL) may also be generated upon transitions of GPT1 timer T3's inputs T3IN and/or T3EUD. This is especially advantageous when T3 operates in Incremental Interface Mode.

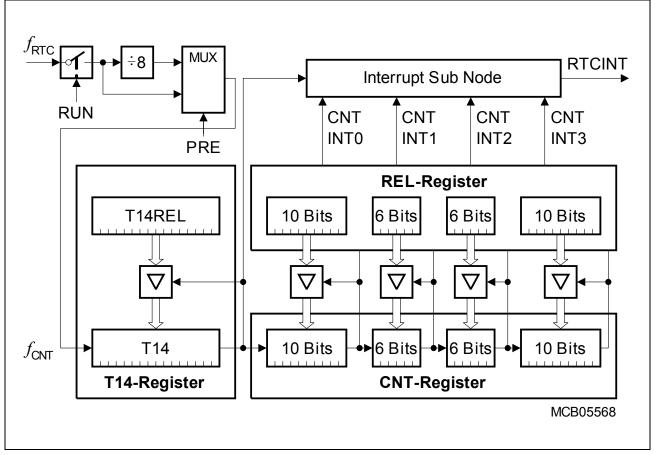

# 3.8 Real Time Clock

The Real Time Clock (RTC) module of the XC161 is directly clocked via a separate clock driver either with the on-chip auxiliary oscillator frequency ( $f_{\text{RTC}} = f_{\text{OSCa}}$ ) or with the prescaled on-chip main oscillator frequency ( $f_{\text{RTC}} = f_{\text{OSCm}}/32$ ). It is therefore independent from the selected clock generation mode of the XC161.

The RTC basically consists of a chain of divider blocks:

- a selectable 8:1 divider (on off)

- the reloadable 16-bit timer T14

- the 32-bit RTC timer block (accessible via registers RTCH and RTCL), made of:

- a reloadable 10-bit timer

- a reloadable 6-bit timer

- a reloadable 6-bit timer

- a reloadable 10-bit timer

All timers count up. Each timer can generate an interrupt request. All requests are combined to a common node request.

### Figure 8 RTC Block Diagram

Note: The registers associated with the RTC are not affected by a reset in order to maintain the correct system time even when intermediate resets are executed.

# 3.11 High Speed Synchronous Serial Channels (SSC0/SSC1)

The High Speed Synchronous Serial Channels SSC0/SSC1 support full-duplex and halfduplex synchronous communication. It may be configured so it interfaces with serially linked peripheral components, full SPI functionality is supported.

A dedicated baud rate generator allows to set up all standard baud rates without oscillator tuning. For transmission, reception and error handling three separate interrupt vectors are provided.

The SSC transmits or receives characters of 2 ... 16 bits length synchronously to a shift clock which can be generated by the SSC (master mode) or by an external master (slave mode). The SSC can start shifting with the LSB or with the MSB and allows the selection of shifting and latching clock edges as well as the clock polarity.

A number of optional hardware error detection capabilities has been included to increase the reliability of data transfers. Transmit error and receive error supervise the correct handling of the data buffer. Phase error and baudrate error detect incorrect serial data.

# Summary of Features

- Master or Slave mode operation

- Full-duplex or Half-duplex transfers

- Baudrate generation from 20 Mbit/s to 305.18 bit/s (@ 40 MHz)

- Flexible data format

- Programmable number of data bits: 2 to 16 bits

- Programmable shift direction: LSB-first or MSB-first

- Programmable clock polarity: idle low or idle high

- Programmable clock/data phase: data shift with leading or trailing clock edge

- Loop back option available for testing purposes

- Interrupt generation on transmitter buffer empty condition, receive buffer full condition, error condition (receive, phase, baudrate, transmit error)

- Three pin interface with flexible SSC pin configuration

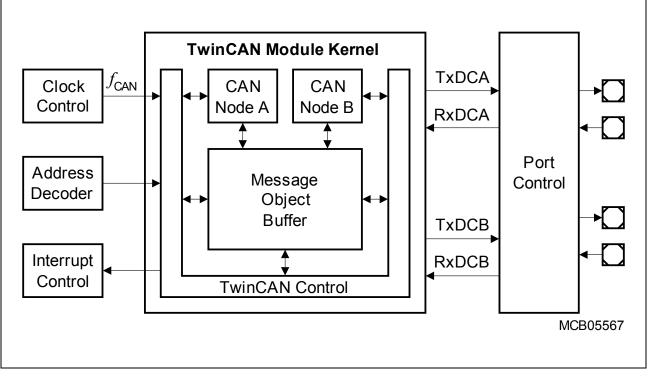

# 3.13 TwinCAN Module

The integrated TwinCAN module handles the completely autonomous transmission and reception of CAN frames in accordance with the CAN specification V2.0 part B (active), i.e. the on-chip TwinCAN module can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers.

Two Full-CAN nodes share the TwinCAN module's resources to optimize the CAN bus traffic handling and to minimize the CPU load. The module provides up to 32 message objects, which can be assigned to one of the CAN nodes and can be combined to FIFO-structures. Each object provides separate masks for acceptance filtering.

The flexible combination of Full-CAN functionality and FIFO architecture reduces the efforts to fulfill the real-time requirements of complex embedded control applications. Improved CAN bus monitoring functionality as well as the number of message objects permit precise and comfortable CAN bus traffic handling.

Gateway functionality allows automatic data exchange between two separate CAN bus systems, which reduces CPU load and improves the real time behavior of the entire system.

The bit timing for both CAN nodes is derived from the master clock and is programmable up to a data rate of 1 Mbit/s. Each CAN node uses two pins of Port 4, Port 7, or Port 9 to interface to an external bus transceiver. The interface pins are assigned via software.

Figure 9 TwinCAN Module Block Diagram

# Summary of Features

- CAN functionality according to CAN specification V2.0 B active

- Data transfer rate up to 1 Mbit/s

- Flexible and powerful message transfer control and error handling capabilities

- Full-CAN functionality and Basic CAN functionality for each message object

- 32 flexible message objects

- Assignment to one of the two CAN nodes

- Configuration as transmit object or receive object

- Concatenation to a 2-, 4-, 8-, 16-, or 32-message buffer with FIFO algorithm

- Handling of frames with 11-bit or 29-bit identifiers

- Individual programmable acceptance mask register for filtering for each object

- Monitoring via a frame counter

- Configuration for Remote Monitoring Mode

- Up to eight individually programmable interrupt nodes can be used

- CAN Analyzer Mode for bus monitoring is implemented

Note: When a CAN node has the interface lines assigned to Port 4, the segment address output on Port 4 must be limited. CS lines can be used to increase the total amount of addressable external memory.

# 3.14 IIC Bus Module

The integrated IIC Bus Module handles the transmission and reception of frames over the two-line IIC bus in accordance with the IIC Bus specification. The IIC Module can operate in slave mode, in master mode or in multi-master mode. It can receive and transmit data using 7-bit or 10-bit addressing. Up to 4 send/receive data bytes can be stored in the extended buffers.

Several physical interfaces (port pins) can be established under software control. Data can be transferred at speeds up to 400 kbit/s.

Two interrupt nodes dedicated to the IIC module allow efficient interrupt service and also support operation via PEC transfers.

Note: The port pins associated with the IIC interfaces must be switched to open drain mode, as required by the IIC specification.

| Table 7             | Summary of the XC161's Parallel Ports          |                                                                                                                                |  |  |  |

|---------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Port                | Control                                        | Alternate Functions                                                                                                            |  |  |  |

| PORT0               | Pad drivers                                    | Address/Data lines or data lines <sup>1)</sup>                                                                                 |  |  |  |

| PORT1               | Pad drivers                                    | Address lines <sup>2)</sup>                                                                                                    |  |  |  |

|                     |                                                | Capture inputs or compare outputs,<br>Serial interface lines                                                                   |  |  |  |

| Port 2              | Pad drivers,<br>Open drain,<br>Input threshold | Capture inputs or compare outputs,<br>Timer control signal,<br>Fast external interrupt inputs                                  |  |  |  |

| Port 3              | Pad drivers,<br>Open drain,<br>Input threshold | Timer control signals, serial interface lines,<br>Optional bus control signal BHE/WRH,<br>System clock output CLKOUT (or FOUT) |  |  |  |

| Port 4 Pad drivers, |                                                | Segment address lines <sup>3)</sup>                                                                                            |  |  |  |

|                     | Open drain,<br>Input threshold                 | CAN/SDLM interface lines <sup>4)</sup>                                                                                         |  |  |  |

| Port 5              | -                                              | Analog input channels to the A/D converter,<br>Timer control signals                                                           |  |  |  |

| Port 6              | Open drain,<br>Input threshold                 | Capture inputs or compare outputs,<br>Bus arbitration signals BREQ, HLDA, HOLD,<br>Optional chip select signals                |  |  |  |

| Port 7              | Open drain,<br>Input threshold                 | Capture inputs or compare outputs,<br>CAN/SDLM interface lines <sup>4)</sup>                                                   |  |  |  |

| Port 9              | Pad drivers,                                   | Capture inputs or compare outputs                                                                                              |  |  |  |

|                     | Open drain,<br>Input threshold                 | CAN/SDLM interface lines <sup>4)</sup> ,<br>IIC bus interface lines <sup>4)</sup>                                              |  |  |  |

| Port 20             | Pad drivers,<br>Open drain                     | Bus control signals RD, WR/WRL, READY, ALE,<br>External access enable pin EA,<br>Reset indication output RSTOUT                |  |  |  |

1) For multiplexed bus cycles.

2) For demultiplexed bus cycles.

3) For more than 64 Kbytes of external resources.

4) Can be assigned by software.

| Port Output Driver<br>Mode | Maximum Output Current $(I_{OLmax}, -I_{OHmax})^{1}$ | Nominal Output Current<br>( <i>I</i> <sub>OLnom</sub> , - <i>I</i> <sub>OHnom</sub> ) |

|----------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------|

| Strong driver              | 10 mA                                                | 2.5 mA                                                                                |

| Medium driver              | 4.0 mA                                               | 1.0 mA                                                                                |

| Weak driver                | 0.5 mA                                               | 0.1 mA                                                                                |

#### Table 12 Current Limits for Port Output Drivers

1) An output current above  $|I_{OXnom}|$  may be drawn from up to three pins at the same time. For any group of 16 neighboring port output pins the total output current in each direction ( $\Sigma I_{OL}$  and  $\Sigma - I_{OH}$ ) must remain below 50 mA.

| Table 13 | <b>Power Consumption</b> | n (Operating | Conditions apply) |

|----------|--------------------------|--------------|-------------------|

|          |                          |              |                   |

| Parameter                                                                                                                                               | Sym-                                  | Lim  | it Values                                | Unit | <b>Test Condition</b>                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------|------------------------------------------|------|--------------------------------------------------------------------------------------------------------|

|                                                                                                                                                         | bol                                   | Min. | Max.                                     |      |                                                                                                        |

| Power supply current (active) with all peripherals active                                                                                               | I <sub>DDI</sub>                      | -    | 15 +<br>2.6 × f <sub>CPU</sub>           | mA   | $f_{\rm CPU}$ in [MHz] <sup>1)2)</sup>                                                                 |

| Pad supply current                                                                                                                                      | $I_{\rm DDP}$                         | -    | 5                                        | mA   | 3)                                                                                                     |

| Idle mode supply current with all peripherals active                                                                                                    | I <sub>IDX</sub>                      | -    | 15 +<br>1.2 × f <sub>CPU</sub>           | mA   | $f_{\rm CPU}$ in [MHz] <sup>2)</sup>                                                                   |

| Sleep and Power down mode<br>supply current caused by<br>leakage <sup>4)</sup>                                                                          | <i>I</i> <sub>PDL</sub> <sup>5)</sup> | _    | 128,000<br>× e <sup>-α</sup>             | mA   | $V_{\rm DDI} = V_{\rm DDImax}^{6}$<br>$T_{\rm J}$ in [°C]<br>$\alpha =$<br>4670 / (273 + $T_{\rm J}$ ) |

| Sleep and Power down mode<br>supply current caused by<br>leakage and the RTC running,<br>clocked by the main oscillator <sup>4)</sup>                   | <i>I</i> <sub>PDM</sub> <sup>7)</sup> | -    | 0.6 +<br>0.02 × $f_{OSC}$<br>+ $I_{PDL}$ | mA   | $V_{\rm DDI}$ = $V_{\rm DDImax}$<br>$f_{\rm OSC}$ in [MHz]                                             |

| Sleep and Power down mode<br>supply current caused by<br>leakage and the RTC running,<br>clocked by the auxiliary<br>oscillator at 32 kHz <sup>4)</sup> | I <sub>PDA</sub>                      | _    | 0.1 + I <sub>PDL</sub>                   | mA   | $V_{\rm DDI}$ = $V_{\rm DDImax}$                                                                       |

1) During Flash programming or erase operations the supply current is increased by max. 5 mA.

2) The supply current is a function of the operating frequency. This dependency is illustrated in Figure 10. These parameters are tested at V<sub>DDImax</sub> and maximum CPU clock frequency with all outputs disconnected and all inputs at V<sub>IL</sub> or V<sub>IH</sub>.

# 4.3 Analog/Digital Converter Parameters

| Table 14 | A/D Converter Characteristics (Operating Conditions apply) |

|----------|------------------------------------------------------------|

|----------|------------------------------------------------------------|

| Parameter                                   | Symbol                  |    | Limit                                                         | Values | Unit            | Test             |  |

|---------------------------------------------|-------------------------|----|---------------------------------------------------------------|--------|-----------------|------------------|--|

|                                             |                         |    | Min. Max.                                                     |        |                 | Condition        |  |

| Analog reference supply                     | V <sub>AREF</sub>       | SR | 4.5 <i>V</i> <sub>DDP</sub><br>+ 0.1                          |        | V               | 1)               |  |

| Analog reference ground                     | $V_{AGND}$              | SR | V <sub>SS</sub> - 0.1 V <sub>SS</sub> + 0.1                   |        | V               | -                |  |

| Analog input voltage range                  | $V_{AIN}$               | SR | V <sub>AGND</sub> V <sub>AREF</sub>                           |        | V               | 2)               |  |

| Basic clock frequency                       | $f_{\sf BC}$            |    | 0.5 20                                                        |        | MHz             | 3)               |  |

| Conversion time for 10-bit                  | t <sub>C10P</sub>       | CC | $52 \times t_{\rm BC} + t_{\rm S} + 6 \times t_{\rm SYS}$     |        | -               | Post-calibr. on  |  |

| result <sup>4)</sup>                        | <i>t</i> <sub>C10</sub> | CC | $40 \times t_{\rm BC} + t_{\rm S} + 6 \times t_{\rm SYS}$     |        | -               | Post-calibr. off |  |

| Conversion time for 8-bit                   | t <sub>C8P</sub>        | CC | $44 \times t_{\rm BC} + t_{\rm S} + 6 \times t_{\rm SYS}$     |        | -               | Post-calibr. on  |  |

| result <sup>4)</sup>                        | t <sub>C8</sub>         | CC | $32 \times t_{\rm BC}$ + $t_{\rm S}$ + $6 \times t_{\rm SYS}$ |        | -               | Post-calibr. off |  |

| Calibration time after reset                | t <sub>CAL</sub>        | CC | 484                                                           | 11,696 | t <sub>BC</sub> | 5)               |  |

| Total unadjusted error                      | TUE                     | CC | _                                                             | ±2     | LSB             | 1)               |  |

| Total capacitance<br>of an analog input     | $C_{AINT}$              | CC | -                                                             | 15     | pF              | 6)               |  |

| Switched capacitance of an analog input     | $C_{AINS}$              | CC | _                                                             | 10     | pF              | 6)               |  |

| Resistance of the analog input path         | R <sub>AIN</sub>        | CC | _                                                             | 2      | kΩ              | 6)               |  |

| Total capacitance<br>of the reference input | $C_{AREFT}$             | CC | _                                                             | 20     | pF              | 6)               |  |

| Switched capacitance of the reference input | $C_{AREFS}$             | CC | _                                                             | 15     | pF              | 6)               |  |

| Resistance of the reference input path      | R <sub>AREF</sub>       | CC | _                                                             | 1      | kΩ              | 6)               |  |

1) TUE is tested at  $V_{AREF} = V_{DDP} + 0.1 \text{ V}$ ,  $V_{AGND} = 0 \text{ V}$ . It is verified by design for all other voltages within the defined voltage range.

If the analog reference supply voltage drops below 4.5 V (and  $V_{AREF} \ge 4.0$  V) or exceeds the power supply voltage by up to 0.2 V (i.e.  $V_{AREF} \le V_{DDP}$  + 0.2 V) the maximum TUE is increased to ±3 LSB. This range is not subject to production test.

The specified TUE is guaranteed only, if the absolute sum of input overload currents on Port 5 pins (see  $I_{OV}$  specification) does not exceed 10 mA, and if  $V_{AREF}$  and  $V_{AGND}$  remain stable during the respective period of time. During the reset calibration sequence the maximum TUE may be ±4 LSB.

V<sub>AIN</sub> may exceed V<sub>AGND</sub> or V<sub>AREF</sub> up to the absolute maximum ratings. However, the conversion result in these cases will be X000<sub>H</sub> or X3FF<sub>H</sub>, respectively.

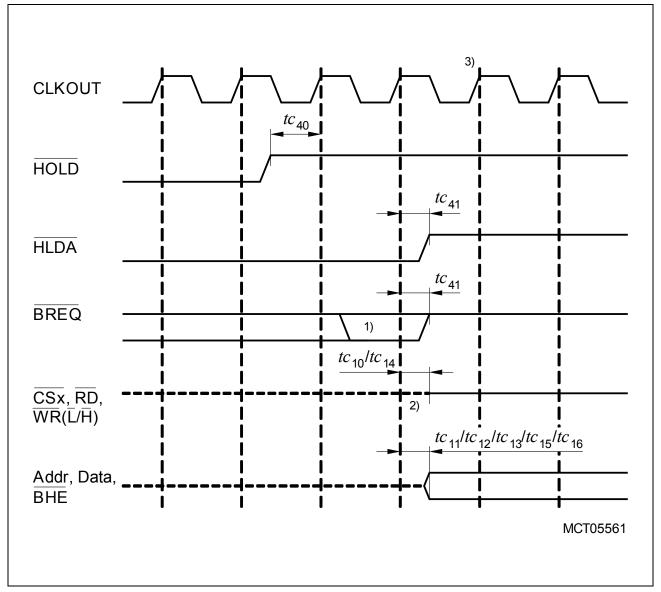

### Table 22 External Bus Cycle Timing (Operating Conditions apply)

| Parameter                                                    | Sym                     | ool |      | Unit |    |

|--------------------------------------------------------------|-------------------------|-----|------|------|----|

|                                                              |                         |     | Min. | Max. |    |

| Output valid delay for:<br>RD, WR(L/H)                       | <i>tc</i> <sub>10</sub> | CC  | 1    | 13   | ns |

| Output valid delay for:<br>BHE, ALE                          | <i>tc</i> <sub>11</sub> | CC  | -1   | 7    | ns |

| Output valid delay for:<br>A23 A16, A15 A0 (on PORT1)        | <i>tc</i> <sub>12</sub> | CC  | 1    | 16   | ns |

| Output valid delay for:<br>A15 … A0 (on PORT0)               | <i>tc</i> <sub>13</sub> | CC  | 3    | 16   | ns |

| Output valid delay for:<br>CS                                | <i>tc</i> <sub>14</sub> | CC  | 1    | 14   | ns |

| Output valid delay for:<br>D15 … D0 (write data, MUX-mode)   | <i>tc</i> <sub>15</sub> | СС  | 3    | 17   | ns |

| Output valid delay for:<br>D15 … D0 (write data, DEMUX-mode) | <i>tc</i> <sub>16</sub> | CC  | 3    | 17   | ns |

| Output hold time for:<br>RD, WR(L/H)                         | <i>tc</i> <sub>20</sub> | CC  | -3   | 3    | ns |

| Output hold time for:<br>BHE, ALE                            | <i>tc</i> <sub>21</sub> | CC  | 0    | 8    | ns |

| Output hold time for:<br>A23 A16, A15 A0 (on PORT0)          | <i>tc</i> <sub>23</sub> | CC  | 1    | 13   | ns |

| Output hold time for:<br>CS                                  | <i>tc</i> <sub>24</sub> | CC  | -3   | 3    | ns |

| Output hold time for:<br>D15 … D0 (write data)               | <i>tc</i> <sub>25</sub> | CC  | 1    | 13   | ns |