Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Last Time Buy                                                                    |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, SLDM, SPI, UART/USART                         |

| Peripherals                | PWM, WDT                                                                         |

| Number of I/O              | 99                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 2.7V                                                                     |

| Data Converters            | A/D 12x8/10b                                                                     |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-LQFP                                                                         |

| Supplier Device Package    | PG-TQFP-144-7                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc161cj16f40fbbkxuma1 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Summary of Features**

# Table 1 XC161 Derivative Synopsis

| Derivative <sup>1)</sup>                  | Temp.<br>Range      | Program<br>Memory   | On-Chip RAM                                          | Interfaces                                             |

|-------------------------------------------|---------------------|---------------------|------------------------------------------------------|--------------------------------------------------------|

| SAK-XC161CJ-16F40F,<br>SAK-XC161CJ-16F20F | -40 °C to<br>125 °C | 128 Kbytes<br>Flash | 2 Kbytes DPRAM,<br>4 Kbytes DSRAM,<br>2 Kbytes PSRAM | ASC0, ASC1,<br>SSC0, SSC1,<br>CAN0, CAN1,<br>SDLM, IIC |

| SAF-XC161CJ-16F40F,<br>SAF-XC161CJ-16F20F | -40 °C to<br>85 °C  | 128 Kbytes<br>Flash | 2 Kbytes DPRAM,<br>4 Kbytes DSRAM,<br>2 Kbytes PSRAM | ASC0, ASC1,<br>SSC0, SSC1,<br>CAN0, CAN1,<br>SDLM, IIC |

1) This Data Sheet is valid for devices starting with and including design step BB.

# **General Device Information**

| Table 2     | Pi          | n Defini       | tions and F                                             | unctions (cont'd)                                                                                                                                                                                                                                               |

|-------------|-------------|----------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sym-<br>bol | Pin<br>Num. | Input<br>Outp. | Function                                                |                                                                                                                                                                                                                                                                 |

| P3          |             | IO             | programm<br>state) or or<br>driver). The<br>or special) | 15-bit bidirectional I/O port. Each pin can be<br>ed for input (output driver in high-impedance<br>utput (configurable as push/pull or open drain<br>e input threshold of Port 3 is selectable (standard<br>ing Port 3 pins also serve for alternate functions: |

| P3.0        | 59          | <br>0<br>      | T0IN<br>TxD1<br>EX1IN                                   | CAPCOM1 Timer T0 Count Input,<br>ASC1 Clock/Data Output (Async./Sync),<br>Fast External Interrupt 1 Input (alternate pin B)                                                                                                                                     |

| P3.1        | 60          | 0<br>I/O<br>I  | T6OUT<br>RxD1<br>EX1IN                                  | GPT2 Timer T6 Toggle Latch Output,<br>ASC1 Data Input (Async.) or Inp./Outp. (Sync.),<br>Fast External Interrupt 1 Input (alternate pin A)                                                                                                                      |

| P3.2        | 61          | 1              | CAPIN                                                   | GPT2 Register CAPREL Capture Input                                                                                                                                                                                                                              |

| P3.3        | 62          | 0              | T3OUT                                                   | GPT1 Timer T3 Toggle Latch Output                                                                                                                                                                                                                               |

| P3.4        | 63          | 1              | T3EUD                                                   | GPT1 Timer T3 External Up/Down Control Input                                                                                                                                                                                                                    |

| P3.5        | 64          | 1              | T4IN                                                    | GPT1 Timer T4 Count/Gate/Reload/Capture Inp                                                                                                                                                                                                                     |

| P3.6        | 65          | 1              | T3IN                                                    | GPT1 Timer T3 Count/Gate Input                                                                                                                                                                                                                                  |

| P3.7        | 66          | 1              | T2IN                                                    | GPT1 Timer T2 Count/Gate/Reload/Capture Inp                                                                                                                                                                                                                     |

| P3.8        | 67          | I/O            | MRST0                                                   | SSC0 Master-Receive/Slave-Transmit In/Out.                                                                                                                                                                                                                      |

| P3.9        | 68          | I/O            | MTSR0                                                   | SSC0 Master-Transmit/Slave-Receive Out/In.                                                                                                                                                                                                                      |

| P3.10       | 69          | 0              | TxD0                                                    | ASC0 Clock/Data Output (Async./Sync.),                                                                                                                                                                                                                          |

|             |             | 1              | EX2IN                                                   | Fast External Interrupt 2 Input (alternate pin B)                                                                                                                                                                                                               |

| P3.11       | 70          | I/O<br>I       | RxD0<br>EX2IN                                           | ASC0 Data Input (Async.) or Inp./Outp. (Sync.),<br>Fast External Interrupt 2 Input (alternate pin A)                                                                                                                                                            |

| P3.12       | 75          | 0<br>0<br>I    | BHE<br>WRH<br>EX3IN                                     | External Memory High Byte Enable Signal,<br>External Memory High Byte Write Strobe,<br>Fast External Interrupt 3 Input (alternate pin B)                                                                                                                        |

| P3.13       | 76          | I/O<br>I       | SCLK0<br>EX3IN                                          | SSC0 Master Clock Output/Slave Clock Input.,<br>Fast External Interrupt 3 Input (alternate pin A)                                                                                                                                                               |

| P3.15       | 77          | 0<br>0         | CLKOUT<br>FOUT                                          | Master Clock Output,<br>Programmable Frequency Output                                                                                                                                                                                                           |

| ТСК         | 71          | I              | Debug Sys                                               | stem: JTAG Clock Input                                                                                                                                                                                                                                          |

| TDI         | 72          | I              | Debug Sys                                               | stem: JTAG Data In                                                                                                                                                                                                                                              |

| TDO         | 73          | 0              | Debug Sys                                               | stem: JTAG Data Out                                                                                                                                                                                                                                             |

| TMS         | 74          |                | Debug Sys                                               | stem: JTAG Test Mode Selection                                                                                                                                                                                                                                  |

# 3 Functional Description

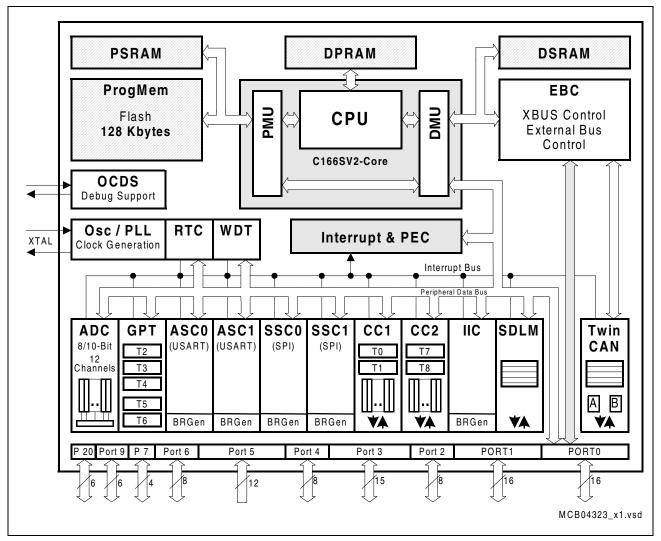

The architecture of the XC161 combines advantages of RISC, CISC, and DSP processors with an advanced peripheral subsystem in a very well-balanced way. In addition, the on-chip memory blocks allow the design of compact systems-on-silicon with maximum performance (computing, control, communication).

The on-chip memory blocks (program code-memory and SRAM, dual-port RAM, data SRAM) and the set of generic peripherals are connected to the CPU via separate buses. Another bus, the LXBus, connects additional on-chip resources as well as external resources (see **Figure 3**).

This bus structure enhances the overall system performance by enabling the concurrent operation of several subsystems of the XC161.

The following block diagram gives an overview of the different on-chip components and of the advanced, high bandwidth internal bus structure of the XC161.

Figure 3 Block Diagram

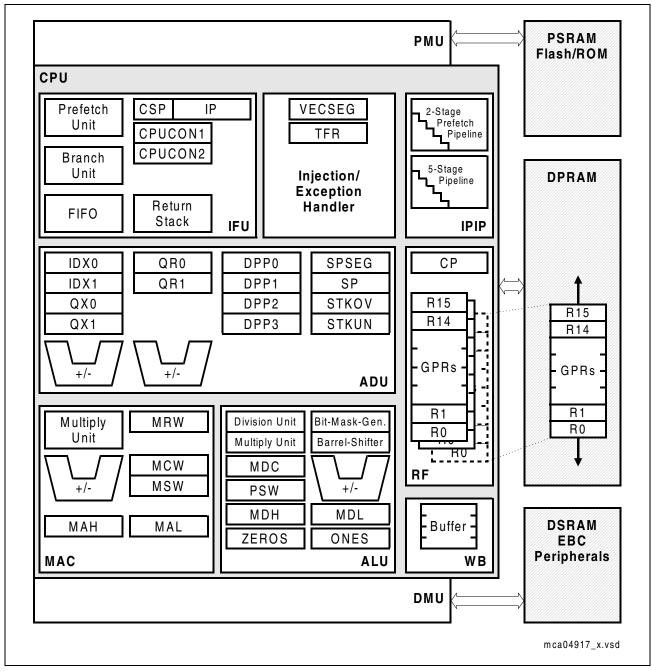

# 3.3 Central Processing Unit (CPU)

The main core of the CPU consists of a 5-stage execution pipeline with a 2-stage instruction-fetch pipeline, a 16-bit arithmetic and logic unit (ALU), a 32-bit/40-bit multiply and accumulate unit (MAC), a register-file providing three register banks, and dedicated SFRs. The ALU features a multiply and divide unit, a bit-mask generator, and a barrel shifter.

# Figure 4 CPU Block Diagram

Based on these hardware provisions, most of the XC161's instructions can be executed in just one machine cycle which requires 25 ns at 40 MHz CPU clock. For example, shift

# 3.4 Interrupt System

With an interrupt response time of typically 8 CPU clocks (in case of internal program execution), the XC161 is capable of reacting very fast to the occurrence of non-deterministic events.

The architecture of the XC161 supports several mechanisms for fast and flexible response to service requests that can be generated from various sources internal or external to the microcontroller. Any of these interrupt requests can be programmed to being serviced by the Interrupt Controller or by the Peripheral Event Controller (PEC).

In contrast to a standard interrupt service where the current program execution is suspended and a branch to the interrupt vector table is performed, just one cycle is 'stolen' from the current CPU activity to perform a PEC service. A PEC service implies a single byte or word data transfer between any two memory locations with an additional increment of either the PEC source, or the destination pointer, or both. An individual PEC transfer counter is implicitly decremented for each PEC service except when performing in the continuous transfer mode. When this counter reaches zero, a standard interrupt is performed to the corresponding source related vector location. PEC services are very well suited, for example, for supporting the transmission or reception of blocks of data. The XC161 has 8 PEC channels each of which offers such fast interrupt-driven data transfer capabilities.

A separate control register which contains an interrupt request flag, an interrupt enable flag and an interrupt priority bitfield exists for each of the possible interrupt nodes. Via its related register, each node can be programmed to one of sixteen interrupt priority levels. Once having been accepted by the CPU, an interrupt service can only be interrupted by a higher prioritized service request. For the standard interrupt processing, each of the possible interrupt nodes has a dedicated vector location.

Fast external interrupt inputs are provided to service external interrupts with high precision requirements. These fast interrupt inputs feature programmable edge detection (rising edge, falling edge, or both edges).

Software interrupts are supported by means of the 'TRAP' instruction in combination with an individual trap (interrupt) number.

**Table 4** shows all of the possible XC161 interrupt sources and the corresponding hardware-related interrupt flags, vectors, vector locations and trap (interrupt) numbers.

Note: Interrupt nodes which are not assigned to peripherals (unassigned nodes), may be used to generate software controlled interrupt requests by setting the respective interrupt request bit (xIR).

# Table 4XC161 Interrupt Nodes (cont'd)

| Source of Interrupt or PEC<br>Service Request | Control<br>Register | Vector<br>Location <sup>1)</sup> | Trap<br>Number                    |

|-----------------------------------------------|---------------------|----------------------------------|-----------------------------------|

| CAPCOM Register 29                            | CC2_CC29IC          | xx'0110 <sub>H</sub>             | 44 <sub>H</sub> / 68 <sub>D</sub> |

| CAPCOM Register 30                            | CC2_CC30IC          | xx'0114 <sub>H</sub>             | 45 <sub>H</sub> / 69 <sub>D</sub> |

| CAPCOM Register 31                            | CC2_CC31IC          | xx'0118 <sub>H</sub>             | 46 <sub>H</sub> / 70 <sub>D</sub> |

| CAPCOM Timer 0                                | CC1_T0IC            | xx'0080 <sub>H</sub>             | 20 <sub>H</sub> / 32 <sub>D</sub> |

| CAPCOM Timer 1                                | CC1_T1IC            | xx'0084 <sub>H</sub>             | 21 <sub>H</sub> / 33 <sub>D</sub> |

| CAPCOM Timer 7                                | CC2_T7IC            | xx'00F4 <sub>H</sub>             | 3D <sub>H</sub> / 61 <sub>D</sub> |

| CAPCOM Timer 8                                | CC2_T8IC            | xx'00F8 <sub>H</sub>             | 3E <sub>H</sub> / 62 <sub>D</sub> |

| GPT1 Timer 2                                  | GPT12E_T2IC         | xx'0088 <sub>H</sub>             | 22 <sub>H</sub> / 34 <sub>D</sub> |

| GPT1 Timer 3                                  | GPT12E_T3IC         | xx'008C <sub>H</sub>             | 23 <sub>H</sub> / 35 <sub>D</sub> |

| GPT1 Timer 4                                  | GPT12E_T4IC         | xx'0090 <sub>H</sub>             | 24 <sub>H</sub> / 36 <sub>D</sub> |

| GPT2 Timer 5                                  | GPT12E_T5IC         | xx'0094 <sub>H</sub>             | 25 <sub>H</sub> / 37 <sub>D</sub> |

| GPT2 Timer 6                                  | GPT12E_T6IC         | xx'0098 <sub>H</sub>             | 26 <sub>H</sub> / 38 <sub>D</sub> |

| GPT2 CAPREL Register                          | GPT12E_CRIC         | xx'009C <sub>H</sub>             | 27 <sub>H</sub> / 39 <sub>D</sub> |

| A/D Conversion Complete                       | ADC_CIC             | xx'00A0 <sub>H</sub>             | 28 <sub>H</sub> / 40 <sub>D</sub> |

| A/D Overrun Error                             | ADC_EIC             | xx'00A4 <sub>H</sub>             | 29 <sub>H</sub> / 41 <sub>D</sub> |

| ASC0 Transmit                                 | ASC0_TIC            | xx'00A8 <sub>H</sub>             | 2A <sub>H</sub> / 42 <sub>D</sub> |

| ASC0 Transmit Buffer                          | ASC0_TBIC           | xx'011C <sub>H</sub>             | 47 <sub>H</sub> / 71 <sub>D</sub> |

| ASC0 Receive                                  | ASC0_RIC            | xx'00AC <sub>H</sub>             | 2B <sub>H</sub> / 43 <sub>D</sub> |

| ASC0 Error                                    | ASC0_EIC            | xx'00B0 <sub>H</sub>             | 2C <sub>H</sub> / 44 <sub>D</sub> |

| ASC0 Autobaud                                 | ASC0_ABIC           | xx'017C <sub>H</sub>             | 5F <sub>H</sub> / 95 <sub>D</sub> |

| SSC0 Transmit                                 | SSC0_TIC            | xx'00B4 <sub>H</sub>             | 2D <sub>H</sub> / 45 <sub>D</sub> |

| SSC0 Receive                                  | SSC0_RIC            | xx'00B8 <sub>H</sub>             | 2E <sub>H</sub> / 46 <sub>D</sub> |

| SSC0 Error                                    | SSC0_EIC            | xx'00BC <sub>H</sub>             | 2F <sub>H</sub> / 47 <sub>D</sub> |

| IIC Data Transfer Event                       | IIC_DTIC            | xx'0100 <sub>H</sub>             | 40 <sub>H</sub> / 64 <sub>D</sub> |

| IIC Protocol Event                            | IIC_PEIC            | xx'0104 <sub>H</sub>             | 41 <sub>H</sub> / 65 <sub>D</sub> |

| PLL/OWD                                       | PLLIC               | xx'010C <sub>H</sub>             | 43 <sub>H</sub> / 67 <sub>D</sub> |

| ASC1 Transmit                                 | ASC1_TIC            | xx'0120 <sub>H</sub>             | 48 <sub>H</sub> / 72 <sub>D</sub> |

| ASC1 Transmit Buffer                          | ASC1_TBIC           | xx'0178 <sub>H</sub>             | 5E <sub>H</sub> / 94 <sub>D</sub> |

| ASC1 Receive                                  | ASC1_RIC            | xx'0124 <sub>H</sub>             | 49 <sub>H</sub> / 73 <sub>D</sub> |

| ASC1 Error                                    | ASC1_EIC            | xx'0128 <sub>H</sub>             | 4A <sub>H</sub> / 74 <sub>D</sub> |

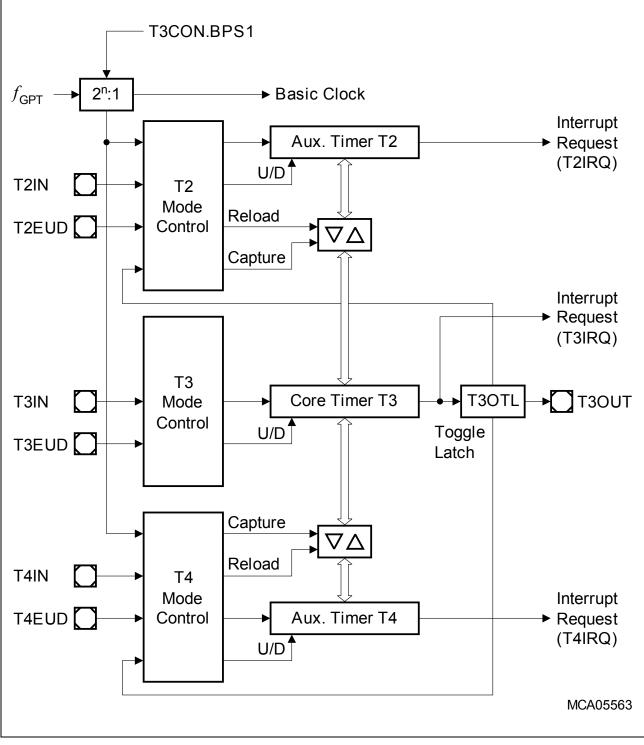

# Figure 6 Block Diagram of GPT1

With its maximum resolution of 2 system clock cycles, the **GPT2 module** provides precise event control and time measurement. It includes two timers (T5, T6) and a capture/reload register (CAPREL). Both timers can be clocked with an input clock which is derived from the CPU clock via a programmable prescaler or with external signals. The

# 3.16 Clock Generation

The Clock Generation Unit uses a programmable on-chip PLL with multiple prescalers to generate the clock signals for the XC161 with high flexibility. The master clock  $f_{MC}$  is the reference clock signal, and is used for TwinCAN and is output to the external system. The CPU clock  $f_{CPU}$  and the system clock  $f_{SYS}$  are derived from the master clock either directly (1:1) or via a 2:1 prescaler ( $f_{SYS} = f_{CPU} = f_{MC} / 2$ ). See also Section 4.4.1.

The on-chip oscillator can drive an external crystal or accepts an external clock signal. The oscillator clock frequency can be multiplied by the on-chip PLL (by a programmable factor) or can be divided by a programmable prescaler factor.

If the bypass mode is used (direct drive or prescaler) the PLL can deliver an independent clock to monitor the clock signal generated by the on-chip oscillator. This PLL clock is independent from the XTAL1 clock. When the expected oscillator clock transitions are missing the Oscillator Watchdog (OWD) activates the PLL Unlock/OWD interrupt node and supplies the CPU with an emergency clock, the PLL clock signal. Under these circumstances the PLL will oscillate with its basic frequency.

The oscillator watchdog can be disabled by switching the PLL off. This reduces power consumption, but also no interrupt request will be generated in case of a missing oscillator clock.

Note: At the end of an external reset ( $\overline{EA} = '0'$ ) the oscillator watchdog may be disabled via hardware by (externally) pulling the  $\overline{RD}$  line low upon a reset, similar to the standard reset configuration.

# 3.17 Parallel Ports

The XC161 provides up to 99 I/O lines which are organized into nine input/output ports and one input port. All port lines are bit-addressable, and all input/output lines are individually (bit-wise) programmable as inputs or outputs via direction registers. The I/O ports are true bidirectional ports which are switched to high impedance state when configured as inputs. The output drivers of some I/O ports can be configured (pin by pin) for push/pull operation or open-drain operation via control registers. During the internal reset, all port pins are configured as inputs (except for pin RSTOUT).

The edge characteristics (shape) and driver characteristics (output current) of the port drivers can be selected via registers POCONx.

The input threshold of some ports is selectable (TTL or CMOS like), where the special CMOS like input threshold reduces noise sensitivity due to the input hysteresis. The input threshold may be selected individually for each byte of the respective ports.

All port lines have programmable alternate input or output functions associated with them. All port lines that are not used for these alternate functions may be used as general purpose IO lines.

| 7 Summary of the XC161's Parallel Ports              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Control                                              | Alternate Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Pad drivers                                          | Address/Data lines or data lines <sup>1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| Pad drivers                                          | Address lines <sup>2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                                      | Capture inputs or compare outputs,<br>Serial interface lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| Pad drivers,<br>Open drain,<br>Input threshold       | Capture inputs or compare outputs,<br>Timer control signal,<br>Fast external interrupt inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| Pad drivers,<br>Open drain,<br>Input threshold       | Timer control signals, serial interface lines,<br>Optional bus control signal BHE/WRH,<br>System clock output CLKOUT (or FOUT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| ort 4 Pad drivers,<br>Open drain,<br>Input threshold | Segment address lines <sup>3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                                                      | CAN/SDLM interface lines <sup>4)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| -                                                    | Analog input channels to the A/D converter,<br>Timer control signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Open drain,<br>Input threshold                       | Capture inputs or compare outputs,<br>Bus arbitration signals BREQ, HLDA, HOLD,<br>Optional chip select signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| Open drain,<br>Input threshold                       | Capture inputs or compare outputs,<br>CAN/SDLM interface lines <sup>4)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| Pad drivers,                                         | Capture inputs or compare outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Open drain,<br>Input threshold                       | CAN/SDLM interface lines <sup>4)</sup> ,<br>IIC bus interface lines <sup>4)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Pad drivers,<br>Open drain                           | Bus control signals RD, WR/WRL, READY, ALE,<br>External access enable <u>pin EA,</u><br>Reset indication output RSTOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                                                      | Control Pad drivers Pad drivers Pad drivers, Open drain, Input threshold Pad drivers, Open drain, Input threshold Pad drivers, Open drain, Input threshold - Open drain, Input threshold Open drain, Input threshold Pad drivers, |  |  |  |

1) For multiplexed bus cycles.

2) For demultiplexed bus cycles.

3) For more than 64 Kbytes of external resources.

4) Can be assigned by software.

| Table 8 Instru | uction Set Summary (cont'd)         |       |

|----------------|-------------------------------------|-------|

| Mnemonic       | Description                         | Bytes |

| NOP            | Null operation                      | 2     |

| CoMUL/CoMAC    | Multiply (and accumulate)           | 4     |

| CoADD/CoSUB    | Add/Subtract                        | 4     |

| Co(A)SHR       | (Arithmetic) Shift right            | 4     |

| CoSHL          | Shift left                          | 4     |

| CoLOAD/STORE   | Load accumulator/Store MAC register | 4     |

| CoCMP          | Compare                             | 4     |

| CoMAX/MIN      | Maximum/Minimum                     | 4     |

| CoABS/CoRND    | Absolute value/Round accumulator    | 4     |

| CoMOV          | Data move                           | 4     |

| CoNEG/NOP      | Negate accumulator/Null operation   | 4     |

- 3) The pad supply voltage pins ( $V_{\text{DDP}}$ ) mainly provide the current consumed by the pin output drivers. This output driver current is not covered by parameter  $I_{\text{DDP}}$ . A small amount of current is consumed even though no outputs are driven, because the drivers' input stages are switched and also the Flash module draws some power from the  $V_{\text{DDP}}$  supply.

- 4) The total supply current in Sleep and Power down mode is the sum of the temperature dependent leakage current and the frequency dependent current for RTC and main oscillator or auxiliary oscillator (if active).

- 5) This parameter is determined mainly by the transistor leakage currents. This current heavily depends on the junction temperature (see Figure 12). The junction temperature  $T_J$  is the same as the ambient temperature  $T_A$  if no current flows through the port output drivers. Otherwise, the resulting temperature difference must be taken into account.

- 6) All inputs (including JTAG pins and pins configured as inputs) at 0 V to 0.1 V or at V<sub>DDP</sub> 0.1 V to V<sub>DDP</sub>, all outputs (including pins configured as outputs) disconnected. This parameter is tested at 25 °C and is valid for T<sub>J</sub> ≥ 25 °C.

- 7) This parameter is determined mainly by the current consumed by the oscillator switched to low gain mode (see Figure 11). This current, however, is influenced by the external oscillator circuitry (crystal, capacitors). The given values refer to a typical circuitry and may change in case of a not optimized external oscillator circuitry.

# 4.3 Analog/Digital Converter Parameters

| Table 14 | A/D Converter Characteristics (Operating Conditions apply) |

|----------|------------------------------------------------------------|

|----------|------------------------------------------------------------|

| Parameter                                   | Symbol                  |    | Limit Values                          |                                 | Unit            | Test             |

|---------------------------------------------|-------------------------|----|---------------------------------------|---------------------------------|-----------------|------------------|

|                                             |                         |    | Min.                                  | Max.                            |                 | Condition        |

| Analog reference supply                     | V <sub>AREF</sub>       | SR | 4.5                                   | V <sub>DDP</sub><br>+ 0.1       | V               | 1)               |

| Analog reference ground                     | $V_{AGND}$              | SR | V <sub>SS</sub> - 0.1                 | V <sub>SS</sub> + 0.1           | V               | -                |

| Analog input voltage range                  | $V_{AIN}$               | SR | $V_{AGND}$                            | $V_{AREF}$                      | V               | 2)               |

| Basic clock frequency                       | $f_{\sf BC}$            |    | 0.5                                   | 20                              | MHz             | 3)               |

| Conversion time for 10-bit                  | t <sub>C10P</sub>       | CC | $52 \times t_{\rm BC}$ + $t_{\rm BC}$ | $t_{\rm S}$ + 6 × $t_{\rm SYS}$ | _               | Post-calibr. on  |

| result <sup>4)</sup>                        | <i>t</i> <sub>C10</sub> | CC | $40 \times t_{\rm BC}$ + $t_{\rm BC}$ | $t_{\rm S}$ + 6 × $t_{\rm SYS}$ | -               | Post-calibr. off |

| Conversion time for 8-bit                   | t <sub>C8P</sub>        | CC | $44 \times t_{\rm BC}$ + $t_{\rm BC}$ | $t_{\rm S}$ + 6 × $t_{\rm SYS}$ | -               | Post-calibr. on  |

| result <sup>4)</sup>                        | t <sub>C8</sub>         | CC | $32 \times t_{\rm BC}$ + $t_{\rm BC}$ | $t_{\rm S}$ + 6 × $t_{\rm SYS}$ | -               | Post-calibr. off |

| Calibration time after reset                | t <sub>CAL</sub>        | CC | 484                                   | 11,696                          | t <sub>BC</sub> | 5)               |

| Total unadjusted error                      | TUE                     | CC | _                                     | ±2                              | LSB             | 1)               |

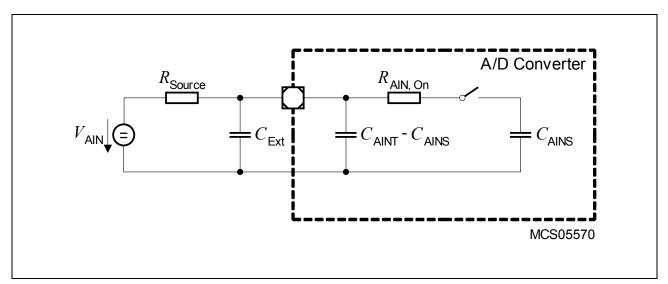

| Total capacitance<br>of an analog input     | $C_{AINT}$              | CC | -                                     | 15                              | pF              | 6)               |

| Switched capacitance of an analog input     | $C_{AINS}$              | CC | _                                     | 10                              | pF              | 6)               |

| Resistance of the analog input path         | R <sub>AIN</sub>        | CC | _                                     | 2                               | kΩ              | 6)               |

| Total capacitance<br>of the reference input | $C_{AREFT}$             | CC | _                                     | 20                              | pF              | 6)               |

| Switched capacitance of the reference input | $C_{AREFS}$             | CC | _                                     | 15                              | pF              | 6)               |

| Resistance of the reference input path      | R <sub>AREF</sub>       | CC | _                                     | 1                               | kΩ              | 6)               |

1) TUE is tested at  $V_{AREF} = V_{DDP} + 0.1 \text{ V}$ ,  $V_{AGND} = 0 \text{ V}$ . It is verified by design for all other voltages within the defined voltage range.

If the analog reference supply voltage drops below 4.5 V (and  $V_{AREF} \ge 4.0$  V) or exceeds the power supply voltage by up to 0.2 V (i.e.  $V_{AREF} \le V_{DDP}$  + 0.2 V) the maximum TUE is increased to ±3 LSB. This range is not subject to production test.

The specified TUE is guaranteed only, if the absolute sum of input overload currents on Port 5 pins (see  $I_{OV}$  specification) does not exceed 10 mA, and if  $V_{AREF}$  and  $V_{AGND}$  remain stable during the respective period of time. During the reset calibration sequence the maximum TUE may be ±4 LSB.

V<sub>AIN</sub> may exceed V<sub>AGND</sub> or V<sub>AREF</sub> up to the absolute maximum ratings. However, the conversion result in these cases will be X000<sub>H</sub> or X3FF<sub>H</sub>, respectively.

- 3) The limit values for  $f_{BC}$  must not be exceeded when selecting the peripheral frequency and the ADCTC setting.

- 4) This parameter includes the sample time t<sub>S</sub>, the time for determining the digital result and the time to load the result register with the conversion result (t<sub>SYS</sub> = 1/f<sub>SYS</sub>). Values for the basic clock t<sub>BC</sub> depend on programming and can be taken from Table 15. When the post-calibration is switched off, the conversion time is reduced by 12 × t<sub>BC</sub>.

- 5) The actual duration of the reset calibration depends on the noise on the reference signal. Conversions executed during the reset calibration increase the calibration time. The TUE for those conversions may be increased.

- 6) Not subject to production test verified by design/characterization. The given parameter values cover the complete operating range. Under relaxed operating conditions (temperature, supply voltage) reduced values can be used for calculations. At room temperature and nominal supply voltage the following typical values can be used:

$C_{AINTtyp}$  = 12 pF,  $C_{AINStyp}$  = 7 pF,  $R_{AINtyp}$  = 1.5 k $\Omega$ ,  $C_{AREFTtyp}$  = 15 pF,  $C_{AREFStyp}$  = 13 pF,  $R_{AREFtyp}$  = 0.7 k $\Omega$ .

Figure 13 Equivalent Circuitry for Analog Inputs

Sample time and conversion time of the XC161's A/D Converter are programmable. In compatibility mode, the above timing can be calculated using **Table 15**. The limit values for  $f_{\rm BC}$  must not be exceeded when selecting ADCTC.

| ADCON.15 14<br>(ADCTC) | A/D Converter<br>Basic Clock $f_{\rm BC}$ | ADCON.13 12<br>(ADSTC) | Sample Time<br><i>t</i> <sub>s</sub> |

|------------------------|-------------------------------------------|------------------------|--------------------------------------|

| 00                     | <i>f</i> <sub>SYS</sub> / 4               | 00                     | $t_{\rm BC} 	imes 8$                 |

| 01                     | f <sub>SYS</sub> / 2                      | 01                     | $t_{\rm BC} 	imes$ 16                |

| 10                     | <i>f</i> <sub>SYS</sub> / 16              | 10                     | $t_{\rm BC} 	imes 32$                |

| 11                     | f <sub>SYS</sub> / 8                      | 11                     | $t_{\rm BC} 	imes 64$                |

Table 15

A/D Converter Computation Table<sup>1)</sup>

1) These selections are available in compatibility mode. An improved mechanism to control the ADC input clock can be selected.

# **Converter Timing Example:**

| Assumptions:      | $f_{\rm SYS}$     | = 40 MHz (i.e. <i>t</i> <sub>SYS</sub> = 25 ns), ADCTC = '01', ADSTC = '00'           |

|-------------------|-------------------|---------------------------------------------------------------------------------------|

| Basic clock       | $f_{\rm BC}$      | = f <sub>SYS</sub> / 2 = 20 MHz, i.e. t <sub>BC</sub> = 50 ns                         |

| Sample time       | t <sub>S</sub>    | $= t_{\rm BC} \times 8 = 400  \rm ns$                                                 |

| Conversion 10-bi  | t:                |                                                                                       |

| With post-calibr. | t <sub>C10P</sub> | = $52 \times t_{BC}$ + $t_{S}$ + $6 \times t_{SYS}$ = (2600 + 400 + 150) ns = 3.15 µs |

| Post-calibr. off  | t <sub>C10</sub>  | = $40 \times t_{BC}$ + $t_{S}$ + $6 \times t_{SYS}$ = (2000 + 400 + 150) ns = 2.55 µs |

| Conversion 8-bit: |                   |                                                                                       |

| With post-calibr. | t <sub>C8P</sub>  | = $44 \times t_{BC} + t_{S} + 6 \times t_{SYS}$ = (2200 + 400 + 150) ns = 2.75 µs     |

| Post-calibr. off  | t <sub>C8</sub>   | = $32 \times t_{BC} + t_{S} + 6 \times t_{SYS}$ = (1600 + 400 + 150) ns = 2.15 µs     |

| PLLCON.PLLVB | VCO Frequency Range | Base Frequency Range |

|--------------|---------------------|----------------------|

| 00           | 100 150 MHz         | 20 80 MHz            |

| 01           | 150 200 MHz         | 40 130 MHz           |

| 10           | 200 250 MHz         | 60 180 MHz           |

| 11           | Reserved            |                      |

#### .1) 4: . . 40 £

1) Not subject to production test - verified by design/characterization.

# 4.4.4 Testing Waveforms

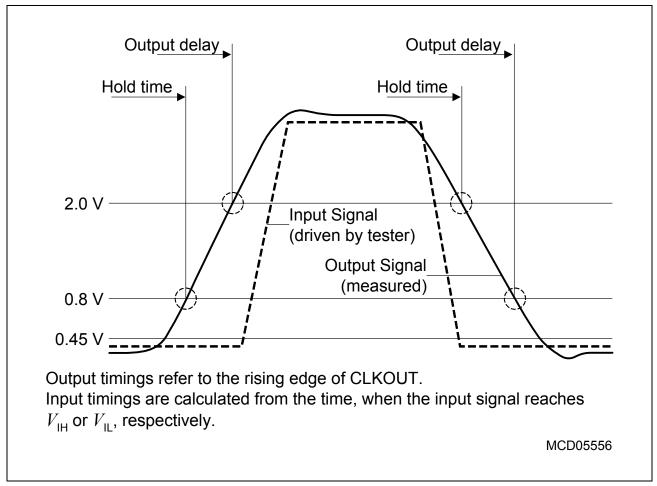

# Figure 17 Input Output Waveforms

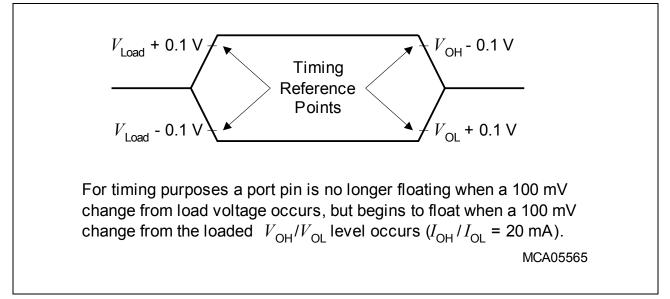

### Figure 18 Float Waveforms

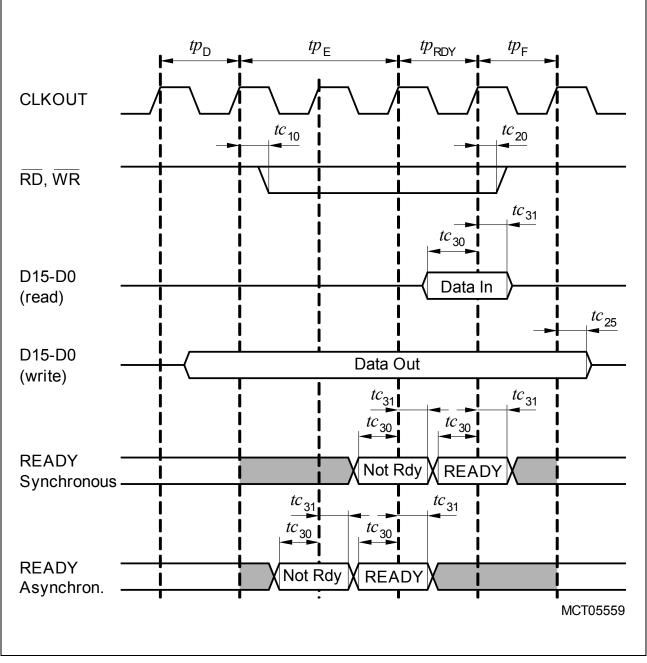

# Bus Cycle Control via READY Input

The duration of an external bus cycle can be controlled by the external circuitry via the READY input signal. The polarity of this input signal can be selected.

**Synchronous** READY permits the shortest possible bus cycle but requires the input signal to be synchronous to the reference signal CLKOUT.

**Asynchronous** READY puts no timing constraints on the input signal but incurs one waitstate minimum due to the additional synchronization stage. The minimum duration of an asynchronous READY signal to be safely synchronized must be one CLKOUT period plus the input setup time.

An active READY signal can be deactivated in response to the trailing (rising) edge of the corresponding command ( $\overline{RD}$  or  $\overline{WR}$ ).

If the next following bus cycle is READY-controlled, an active READY signal must be disabled before the first valid sample point for the next bus cycle. This sample point depends on the programmed phases of the next following cycle.

# XC161CJ-16F Derivatives

# **Electrical Parameters**

Figure 22 READY Timing

Note: If the READY input is sampled inactive at the indicated sampling point ("Not Rdy") a READY-controlled waitstate is inserted  $(tp_{RDY})$ , sampling the READY input active at the indicated sampling point ("Ready") terminates the currently running bus cycle. Note the different sampling points for synchronous and asynchronous READY. This example uses one mandatory waitstate (see  $tp_E$ ) before the READY input is evaluated.

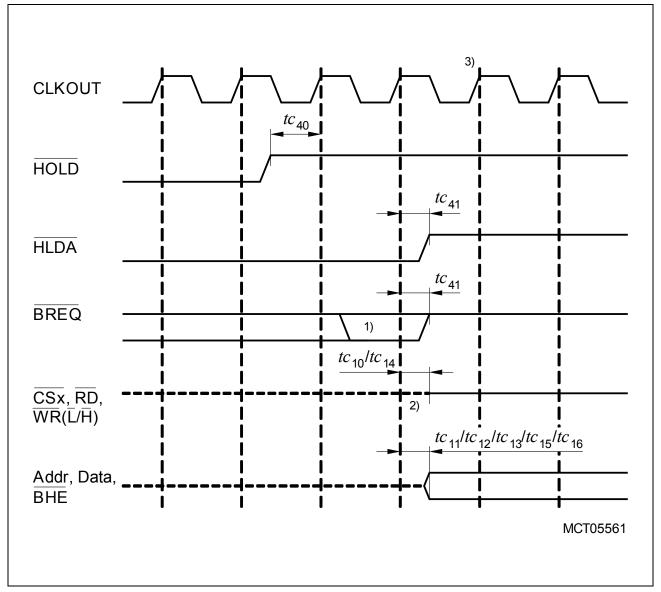

Figure 24 External Bus Arbitration, Regaining the Bus

### Notes

- This is the last chance for BREQ to trigger the indicated regain-sequence. Even if BREQ is activated earlier, the regain-sequence is initiated by HOLD going high. Please note that HOLD may also be deactivated without the XC161 requesting the bus.

- 2. The control outputs will be resistive high (pull-up) before being driven inactive (ALE will be low).

- 3. The next XC161 driven bus cycle may start here.

www.infineon.com