Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | dsPIC                                                                         |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 30 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 12                                                                            |

| Program Memory Size        | 12KB (4K x 24)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x12b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 28-QFN (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f2011-30i-ml |

Y Data Bus X Data Bus **∦**16 **/**16 16 Data Latch Data Latch Interrupt PSV & Table Controller Y Data X Data Data Access 24 Control Block 16 512 bytes (512 bytes Address Address 24 Latch Latch 1 16 1 16 16 EMUD3/AN0/VREF+/CN2/RB0 24 X RAGU EMUC3/AN1/VREF-/CN3/RB1 Y AGU PCH PCL X WAGU PCU AN2/SS1/LVDIN/CN4/RB2 Program Counter AN3/CN5/RB3 Stack Control Logic Loop Control AN4/CN6/RB4 Address Latch AN5/CN7/RB5 Program Memory Logic AN6/OCFA/RB6 (12 Kbytes) EMUD2/AN7/RB7 AN8/OC1/RB8 Effective Address AN9/OC2/RB9 ROM Latch IR EMUD1/SOSCI/T2CK/U1ATX/CN1/RC13 EMUC1/SOSCO/T1CK/U1ARX/CN0/RC14 16 16 OSC2/CLKO/RC15 16 x 16 W Reg Array PORTC Decode Instruction Decode & Control DSP Divide Power-up Engine Unit Timer EMUC2/IC1/INT1/RD8 Timing Generation Oscillator OSC1/CLKI Start-up Timer  $\boxtimes$ ALU<16> POR/BOR Reset MCLR PORTD Watchdog 16  $\boxtimes$ Low-Voltage Detect VDD, VSS AVDD, AVSS Input Output 12-bit ADC Compare  $I^2C^{TM}$ Capture Module Module PGC/EMUC/U1RX/SDI1/SDA/RF2 PGD/EMUD/U1TX/SDO1/SCL/RF3 CN17/RF4 CN18/RF5 SCK1/INT0/RF6 Timers SPI1 UART1

FIGURE 1-2: dsPIC30F2012 BLOCK DIAGRAM

Table 1-1 provides a brief description of device I/O pinouts and the functions that may be multiplexed to a port pin. Multiple functions may exist on one port pin. When multiplexing occurs, the peripheral module's functional requirements may force an override of the data direction of the port pin.

**TABLE 1-1: PINOUT I/O DESCRIPTIONS**

| Pin Name                                                           | Pin<br>Type                                   | Buffer<br>Type                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|--------------------------------------------------------------------|-----------------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| AN0 - AN9                                                          | I                                             | Analog                                 | Analog input channels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| AVDD                                                               | Р                                             | Р                                      | Positive supply for analog module. This pin must be connected at all times.                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| AVss                                                               | Р                                             | Р                                      | Ground reference for analog module. This pin must be connected at all times.                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| CLKI<br>CLKO                                                       | 0                                             | ST/CMOS<br>—                           | xternal clock source input. Always associated with OSC1 pin function. scillator crystal output. Connects to crystal or resonator in Crystal Oscillato node. Optionally functions as CLKO in RC and EC modes. Always associated ith OSC2 pin function.                                                                                                                                                                                                                                   |  |  |  |  |

| CN0 - CN7                                                          | I                                             | ST                                     | Input change notification inputs. Can be software programmed for internal weak pull-ups on all inputs.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| EMUD<br>EMUC<br>EMUD1<br>EMUC1<br>EMUD2<br>EMUC2<br>EMUD3<br>EMUC3 | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST | ICD Primary Communication Channel data input/output pin. ICD Primary Communication Channel clock input/output pin. ICD Secondary Communication Channel data input/output pin. ICD Secondary Communication Channel clock input/output pin. ICD Tertiary Communication Channel data input/output pin. ICD Tertiary Communication Channel clock input/output pin. ICD Quaternary Communication Channel data input/output pin. ICD Quaternary Communication Channel clock input/output pin. |  |  |  |  |

| IC1 - IC2                                                          | ı                                             | ST                                     | Capture inputs 1 through 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| INTO<br>INT1<br>INT2                                               | <br>                                          | ST<br>ST<br>ST                         | External interrupt 0. External interrupt 1. External interrupt 2.                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| LVDIN<br>MCLR                                                      | I<br>I/P                                      | Analog<br>ST                           | Low-Voltage Detect Reference Voltage Input pin.  Master Clear (Reset) input or programming voltage input. This pin is an active-low Reset to the device.                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| OC1-OC2<br>OCFA                                                    | 0                                             | —<br>ST                                | Compare outputs 1 through 2. Compare Fault A input.                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| OSC1<br>OSC2                                                       | I<br>I/O                                      | ST/CMOS                                | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise. Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                                                                                                                                                                                                                                                |  |  |  |  |

| PGD<br>PGC                                                         | I/O<br>I                                      | ST<br>ST                               | In-Circuit Serial Programming™ data input/output pin. In-Circuit Serial Programming clock input pin.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| RB0 - RB9                                                          | I/O                                           | ST                                     | PORTB is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| RC13 - RC15                                                        | I/O                                           | ST                                     | PORTC is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| RD0,<br>RD8-RD9                                                    | I/O                                           | ST                                     | PORTD is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| RF2 - RF5                                                          | I/O                                           | ST                                     | PORTF is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| SCK1<br>SDI1<br>SDO1<br>SS1                                        | I/O<br>I<br>O<br>I                            | ST<br>ST<br>—<br>ST                    | Synchronous serial clock input/output for SPI1. SPI1 Data In. SPI1 Data Out. SPI1 Slave Synchronization.                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

**Legend:** CMOS = CMOS compatible input or output Analog = Analog input ST Schmitt Trigger input with CMOS levels 0 Output Ρ Power

Input

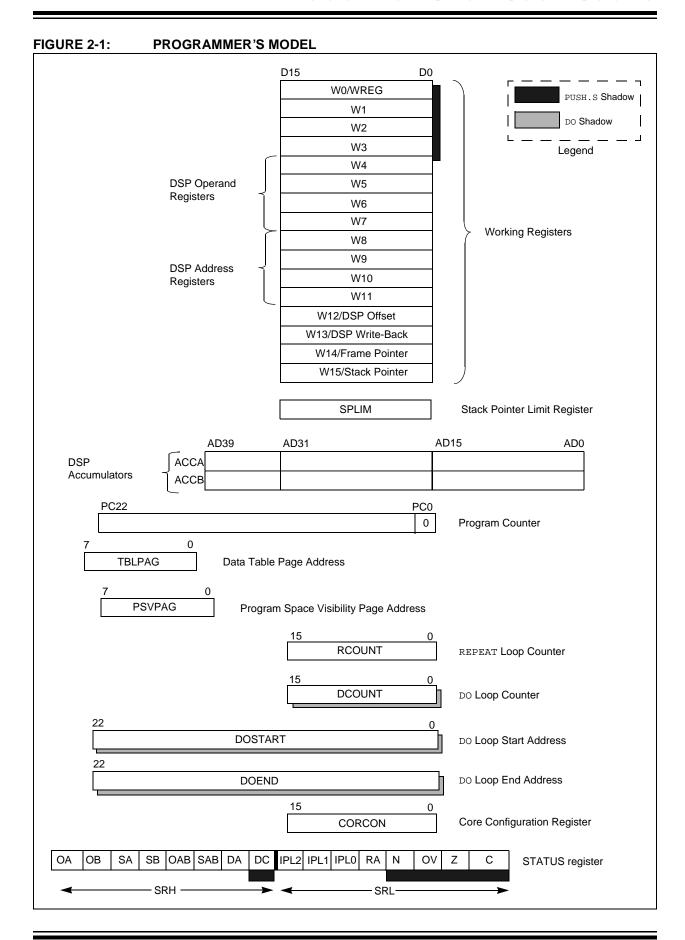

# 2.0 CPU ARCHITECTURE OVERVIEW

Note:

This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

This section is an overview of the CPU architecture of the dsPIC30F. The core has a 24-bit instruction word. The Program Counter (PC) is 23 bits wide with the Least Significant bit (LSb) always clear (see Section 3.1 "Program Address Space"). The Most Significant bit (MSb) is ignored during normal program execution, except for certain specialized instructions. Thus, the PC can address up to 4M instruction words of user program space. An instruction prefetch mechanism helps maintain throughput. Program loop constructs, free from loop count management overhead, are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

### 2.1 Core Overview

The working register array consists of 16 x 16-bit registers, each of which can act as data, address or offset registers. One working register (W15) operates as a Software Stack Pointer for interrupts and calls.

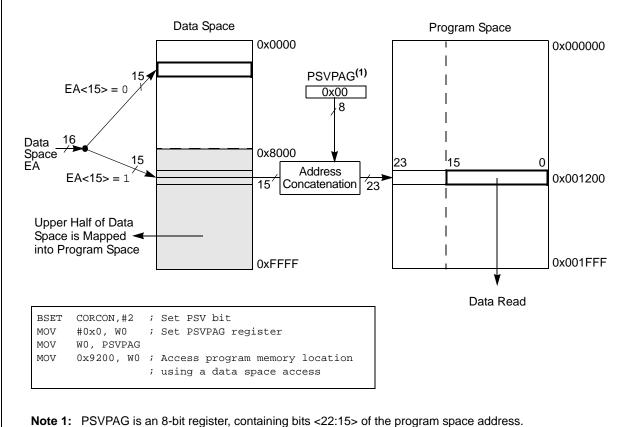

The data space is 64 Kbytes (32K words) and is split into two blocks, referred to as X and Y data memory. Each block has its own independent Address Generation Unit (AGU). Most instructions operate solely through the X memory, AGU, which provides the appearance of a single unified data space. The Multiply-Accumulate (MAC) class of dual source DSP instructions operate through both the X and Y AGUs, splitting the data address space into two parts (see Section 3.2 "Data Address Space"). The X and Y data space boundary is device specific and cannot be altered by the user. Each data word consists of 2 bytes and most instructions can address data either as words or bytes.

Two ways to access data in program memory are:

- The upper 32 Kbytes of data space memory can be mapped into the lower half (user space) of program space at any 16K program word boundary, defined by the 8-bit Program Space Visibility Page register (PSVPAG). Thus any instruction can access program space as if it were data space, with a limitation that the access requires an additional cycle. Only the lower 16 bits of each instruction word can be accessed using this method.

- Linear indirect access of 32K word pages within program space is also possible using any working register, via table read and write instructions.

Table read and write instructions can be used to access all 24 bits of an instruction word.

Overhead-free circular buffers (Modulo Addressing) are supported in both X and Y address spaces. This is primarily intended to remove the loop overhead for DSP algorithms.

The X AGU also supports Bit-Reversed Addressing on destination effective addresses to greatly simplify input or output data reordering for radix-2 FFT algorithms. Refer to **Section 4.0 "Address Generator Units"** for details on Modulo and Bit-Reversed Addressing.

The core supports Inherent (no operand), Relative, Literal, Memory Direct, Register Direct, Register Indirect, Register Offset and Literal Offset Addressing modes. Instructions are associated with pre-defined addressing modes, depending upon their functional requirements.

For most instructions, the core is capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, 3 operand instructions are supported, allowing C = A+B operations to be executed in a single cycle.

A DSP engine has been included to significantly enhance the core arithmetic capability and throughput. It features a high-speed 17-bit by 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bidirectional barrel shifter. Data in the accumulator or any working register can be shifted up to 15 bits right, or 16 bits left in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal real-time performance. The MAC class of instructions can concurrently fetch two data operands from memory while multiplying two W registers. To enable this concurrent fetching of data operands, the data space has been split for these instructions and linear is for all others. This has been achieved in a transparent and flexible manner, by dedicating certain working registers to each address space for the MAC class of instructions.

FIGURE 3-5: DATA SPACE WINDOW INTO PROGRAM SPACE OPERATION

## 4.1.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note:

For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (register offset) field is shared between both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- · Register Direct

- · Register Indirect

- · Register Indirect Post-modified

- · Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- · Register Indirect with Literal Offset

- 8-bit Literal

- 16-bit Literal

Note:

Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

### 4.1.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY.N, MOVSAC and MSC), also referred to as MAC instructions, utilize a simplified set of addressing modes to allow the user to effectively manipulate the data pointers through register indirect tables.

The two source operand prefetch registers must belong to the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU. W10 and W11 are always directed to the Y AGU. The effective addresses generated (before and after modification) must, therefore, be valid addresses within X data space for W8 and W9 and Y data space for W10 and W11.

Note:

Register Indirect with Register Offset addressing is only available for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the MAC class of instructions:

- · Register Indirect

- · Register Indirect Post-modified by 2

- · Register Indirect Post-modified by 4

- Register Indirect Post-modified by 6

- Register Indirect with Register Offset (Indexed)

### 4.1.5 OTHER INSTRUCTIONS

Besides the various addressing modes outlined above, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ADD Acc, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

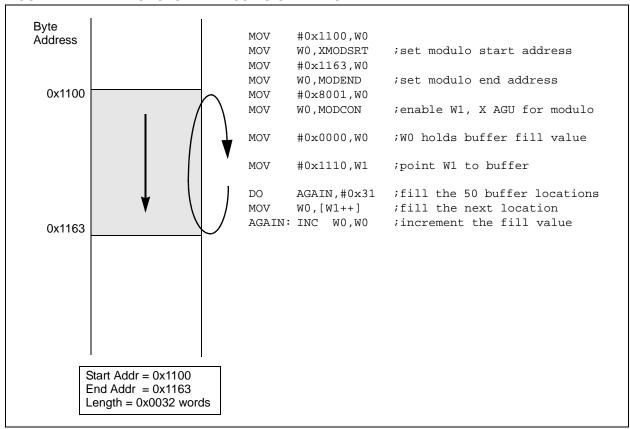

### 4.2 Modulo Addressing

Modulo Addressing is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either data or program space (since the data pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into program space) and Y data spaces. Modulo Addressing can operate on any W register pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can only be configured to operate in one direction, as there are certain restrictions on the buffer Start address (for incrementing buffers), or end address (for decrementing buffers) based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-2 length. As these buffers satisfy the Start and the end address criteria, they can operate in a Bidirectional mode (i.e., address boundary checks are performed on both the lower and upper address boundaries).

#### 4.2.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and an ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 3-3).

Note: Y space Modulo Addressing EA calculations assume word-sized data (LSb of every EA is always clear).

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding Start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

## 4.2.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W address registers. The XWM and YWM fields select which registers operate with Modulo Addressing. If XWM = 15, X RAGU and X WAGU Modulo Addressing is disabled. Similarly, if YWM = 15, Y AGU Modulo Addressing is disabled.

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 3-3). Modulo Addressing is enabled for X data space when XWM is set to any value other than '15' and the XMODEN bit is set at MODCON<15>.

The Y Address Space Pointer W register (YWM), to which Modulo Addressing is to be applied, is stored in MODCON<7:4>. Modulo Addressing is enabled for Y data space when YWM is set to any value other than '15' and the YMODEN bit is set at MODCON<14>.

FIGURE 4-1: MODULO ADDRESSING OPERATION EXAMPLE

### 6.2 Erasing Data EEPROM

## 6.2.1 ERASING A BLOCK OF DATA EEPROM

In order to erase a block of data EEPROM, the NVMADRU and NVMADR registers must initially point to the block of memory to be erased. Configure NVMCON for erasing a block of data EEPROM and set the WR and WREN bits in the NVMCON register. Setting the WR bit initiates the erase, as shown in Example 6-2.

#### **EXAMPLE 6-2: DATA EEPROM BLOCK ERASE**

```

; Select data EEPROM block, WR, WREN bits

MOV

#0x4045,W0

MOV

W0 NVMCON

; Initialize NVMCON SFR

; Start erase cycle by setting WR after writing key sequence

; Block all interrupts with priority <7 for

DISI

; next 5 instructions

MOV

#0x55,W0

WO NVMKEY

; Write the 0x55 key

MOV

MOV

#0xAA,W1

MOV

W1 NVMKEY

; Write the OxAA key

BSET

NVMCON, #WR

; Initiate erase sequence

NOP

NOP

; Erase cycle will complete in 2mS. CPU is not stalled for the Data Erase Cycle

; User can poll WR bit, use NVMIF or Timer IRQ to determine erasure complete

```

# 6.2.2 ERASING A WORD OF DATA EEPROM

The NVMADRU and NVMADR registers must point to the block. Select WR a block of data Flash and set the WR and WREN bits in the NVMCON register. Setting the WR bit initiates the erase, as shown in Example 6-3.

### **EXAMPLE 6-3:** DATA EEPROM WORD ERASE

```

; Select data EEPROM word, WR, WREN bits

#0x4044,W0

MOV

W0 NVMCON

; Start erase cycle by setting WR after writing key sequence

DISI

; Block all interrupts with priority <7 for

; next 5 instructions

MOV

#0x55,W0

WO NVMKEY

MOV

; Write the 0x55 key

#0xAA,W1

MOV

W1 NVMKEY

; Write the 0xAA key

MOV

BSET

NVMCON, #WR

; Initiate erase sequence

NOP

; Erase cycle will complete in 2mS. CPU is not stalled for the Data Erase Cycle

; User can poll WR bit, use NVMIF or Timer IRQ to determine erasure complete

```

### 8.6 Fast Context Saving

A context saving option is available using shadow registers. Shadow registers are provided for the DC, N, OV, Z and C bits in SR, and the registers W0 through W3. The shadows are only one level deep. The shadow registers are accessible using the  ${\tt PUSH.S}$  and  ${\tt POP.S}$  instructions only.

When the processor vectors to an interrupt, the PUSH.S instruction can be used to store the current value of the aforementioned registers into their respective shadow registers.

If an ISR of a certain priority uses the PUSH.S and POP.S instructions for fast context saving, then a higher priority ISR should not include the same instructions. Users must save the key registers in software during a lower priority interrupt if the higher priority ISR uses fast context saving.

### 8.7 External Interrupt Requests

The interrupt controller supports three external interrupt request signals, INT0-INT2. These inputs are edge sensitive; they require a low-to-high or a high-to-low transition to generate an interrupt request. The INTCON2 register has three bits, INT0EP-INT2EP, that select the polarity of the edge detection circuitry.

### 8.8 Wake-up from Sleep and Idle

The interrupt controller may be used to wake-up the processor from either Sleep or Idle modes, if Sleep or Idle mode is active when the interrupt is generated.

If an enabled interrupt request of sufficient priority is received by the interrupt controller, then the standard interrupt request is presented to the processor. At the same time, the processor wakes up from Sleep or Idle and begins execution of the ISR needed to process the interrupt request.

#### 11.1.2 CAPTURE BUFFER OPERATION

Each capture channel has an associated FIFO buffer which is four 16-bit words deep. There are two status flags which provide status on the FIFO buffer:

- ICBNE Input Capture Buffer Not Empty

- ICOV Input Capture Overflow

The ICBNE is set on the first input capture event and remains set until all capture events have been read from the FIFO. As each word is read from the FIFO, the remaining words are advanced by one position within the buffer.

In the event that the FIFO is full with four capture events, and a fifth capture event occurs prior to a read of the FIFO, an overflow condition occurs and the ICOV bit is set to a logic '1'. The fifth capture event is lost and is not stored in the FIFO. No additional events are captured until all four events have been read from the buffer.

If a FIFO read is performed after the last read and no new capture event has been received, the read will yield indeterminate results.

## 11.1.3 TIMER2 AND TIMER3 SELECTION MODE

The input capture module consists of up to 8 input capture channels. Each channel can select between one of two timers for the time base, Timer2 or Timer3.

Selection of the timer resource is accomplished through SFR bit, ICTMR (ICxCON<7>). Timer3 is the default timer resource available for the input capture module.

### 11.1.4 HALL SENSOR MODE

When the input capture module is set for capture on every edge, rising and falling, ICM<2:0> = 001, the following operations are performed by the input capture logic:

- The input capture interrupt flag is set on every edge, rising and falling.

- The interrupt on Capture mode setting bits, ICI<1:0>, is ignored since every capture generates an interrupt.

- A capture overflow condition is not generated in this mode.

# 11.2 Input Capture Operation During Sleep and Idle Modes

An input capture event generates a device wake-up or interrupt, if enabled, if the device is in CPU Idle or Sleep mode.

Independent of the timer being enabled, the input capture module wakes up from the CPU Sleep or Idle mode when a capture event occurs if ICM<2:0> = 111 and the interrupt enable bit is asserted. The same wake-up can generate an interrupt if the conditions for processing the interrupt have been satisfied. The wake-up feature is useful as a method of adding extra external pin interrupts.

## 11.2.1 INPUT CAPTURE IN CPU SLEEP MODE

CPU Sleep mode allows input capture module operation with reduced functionality. In the CPU Sleep mode, the ICI<1:0> bits are not applicable and the input capture module can only function as an external interrupt source.

The capture module must be configured for interrupt only on rising edge (ICM<2:0>=111) in order for the input capture module to be used while the device is in Sleep mode. The prescale settings of 4:1 or 16:1 are not applicable in this mode.

# 11.2.2 INPUT CAPTURE IN CPU IDLE MODE

CPU Idle mode allows input capture module operation with full functionality. In the CPU Idle mode, the Interrupt mode selected by the ICI<1:0> bits is applicable, as well as the 4:1 and 16:1 capture prescale settings which are defined by control bits ICM<2:0>. This mode requires the selected timer to be enabled. Moreover, the ICSIDL bit must be asserted to a logic '0'.

If the input capture module is defined as ICM<2:0> = 111 in CPU Idle mode, the input capture pin serves only as an external interrupt pin.

### 11.3 Input Capture Interrupts

The input capture channels have the ability to generate an interrupt based on the selected number of capture events. The selection number is set by control bits, ICI<1:0> (ICxCON<6:5>).

Each channel provides an interrupt flag (ICxIF) bit. The respective capture channel interrupt flag is located in the corresponding IFSx register.

Enabling an interrupt is accomplished via the respective capture channel interrupt enable (ICxIE) bit. The capture interrupt enable bit is located in the corresponding IEC Control register.

#### 12.1 Timer2 and Timer3 Selection Mode

Each output compare channel can select between one of two 16-bit timers, Timer2 or Timer3.

The selection of the timers is controlled by the OCTSEL bit (OCxCON<3>). Timer2 is the default timer resource for the output compare module.

## 12.2 Simple Output Compare Match Mode

When control bits OCM<2:0> (OCxCON<2:0>) = 001, 010 or 011, the selected output compare channel is configured for one of three simple Output Compare Match modes:

- · Compare forces I/O pin low

- Compare forces I/O pin high

- Compare toggles I/O pin

The OCxR register is used in these modes. The OCxR register is loaded with a value and is compared to the selected incrementing timer count. When a compare occurs, one of these Compare Match modes occurs. If the counter resets to zero before reaching the value in OCxR, the state of the OCx pin remains unchanged.

### 12.3 Dual Output Compare Match Mode

When control bits OCM<2:0> (OCxCON<2:0>) = 100 or 101, the selected output compare channel is configured for one of two Dual Output Compare modes, which are:

- · Single Output Pulse mode

- · Continuous Output Pulse mode

#### 12.3.1 SINGLE PULSE MODE

For the user to configure the module for the generation of a single output pulse, the following steps are required (assuming timer is off):

- · Determine instruction cycle time Tcy.

- Calculate desired pulse width value based on Tcy.

- Calculate time to start pulse from timer start value of 0x0000.

- Write pulse width start and stop times into OCxR and OCxRS Compare registers (x denotes channel 1 to N).

- Set Timer Period register to value equal to or greater than value in OCxRS Compare register.

- Set OCM<2:0> = 100.

- Enable timer, TON bit (TxCON<15>) = 1.

To initiate another single pulse, issue another write to set OCM<2:0> = 100.

#### 12.3.2 CONTINUOUS PULSE MODE

For the user to configure the module for the generation of a continuous stream of output pulses, the following steps are required:

- · Determine instruction cycle time Tcy.

- · Calculate desired pulse value based on Tcy.

- Calculate timer to start pulse width from timer start value of 0x0000.

- Write pulse width start and stop times into OCxR and OCxRS (x denotes channel 1 to N) Compare registers, respectively.

- Set Timer Period register to value equal to or greater than value in OCxRS Compare register.

- Set OCM<2:0> = 101.

- Enable timer, TON bit (TxCON<15>) = 1.

### 12.4 Simple PWM Mode

When control bits OCM<2:0> (OCxCON<2:0>) = 110 or 111, the selected output compare channel is configured for the PWM mode of operation. When configured for the PWM mode of operation, OCxR is the main latch (read-only) and OCxRS is the secondary latch. This enables glitchless PWM transitions.

The user must perform the following steps in order to configure the output compare module for PWM operation:

- Set the PWM period by writing to the appropriate period register.

- Set the PWM duty cycle by writing to the OCxRS register.

- Configure the output compare module for PWM operation.

- Set the TMRx prescale value and enable the Timer, TON bit (TxCON<15>) = 1.

## 12.4.1 INPUT PIN FAULT PROTECTION FOR PWM

When control bits OCM<2:0> (OCxCON<2:0>) = 111, the selected output compare channel is again configured for the PWM mode of operation with the additional feature of input Fault protection. While in this mode, if a logic '0' is detected on the OCFA/B pin, the respective PWM output pin is placed in the high impedance input state. The OCFLT bit (OCxCON<4>) indicates whether a Fault condition has occurred. This state is maintained until both of the following events have occurred:

- The external Fault condition has been removed.

- The PWM mode has been re-enabled by writing to the appropriate control bits.

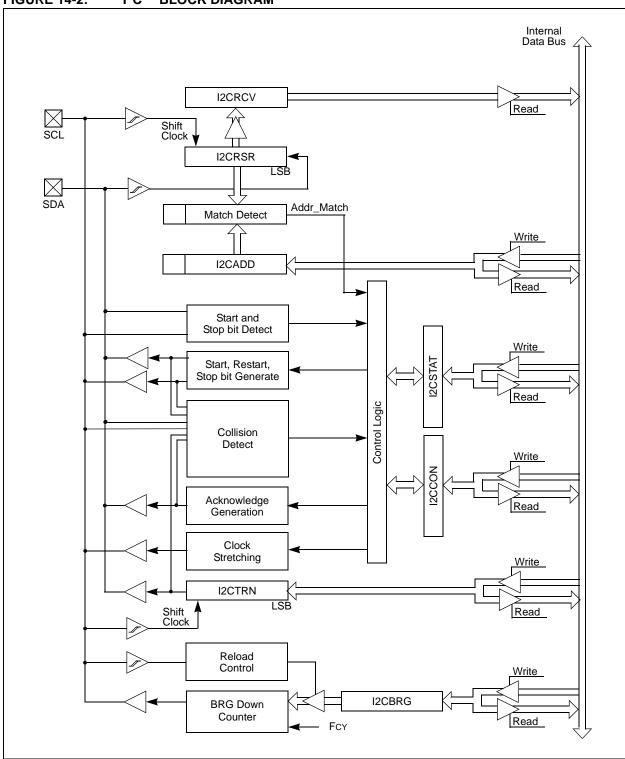

FIGURE 14-2: I<sup>2</sup>C™ BLOCK DIAGRAM

## 14.4.1 10-BIT MODE SLAVE TRANSMISSION

Once a slave is addressed in this fashion with the full 10-bit address (we will refer to this state as "PRIOR\_ADDR\_MATCH"), the master can begin sending data bytes for a slave reception operation.

#### 14.4.2 10-BIT MODE SLAVE RECEPTION

Once addressed, the master can generate a Repeated Start, reset the high byte of the address and set the R\_W bit without generating a Stop bit, thus initiating a slave transmit operation.

### 14.5 Automatic Clock Stretch

In the Slave modes, the module can synchronize buffer reads and write to the master device by clock stretching.

#### 14.5.1 TRANSMIT CLOCK STRETCHING

Both 10-bit and 7-bit Transmit modes implement clock stretching by asserting the SCLREL bit after the falling edge of the ninth clock, if the TBF bit is cleared, indicating the buffer is empty.

In Slave Transmit modes, clock stretching is always performed irrespective of the STREN bit.

Clock synchronization takes place following the ninth clock of the transmit sequence. If the device samples an ACK on the falling edge of the ninth clock and if the TBF bit is still clear, then the SCLREL bit is automatically cleared. The SCLREL being cleared to '0' will assert the SCL line low. The user's ISR must set the SCLREL bit before transmission is allowed to continue. By holding the SCL line low, the user has time to service the ISR and load the contents of the I2CTRN before the master device can initiate another transmit sequence.

- Note 1: If the user loads the contents of I2CTRN, setting the TBF bit before the falling edge of the ninth clock, the SCLREL bit will not be cleared and clock stretching will not occur.

- **2:** The SCLREL bit can be set in software, regardless of the state of the TBF bit.

### 14.5.2 RECEIVE CLOCK STRETCHING

The STREN bit in the I2CCON register can be used to enable clock stretching in Slave Receive mode. When the STREN bit is set, the SCL pin will be held low at the end of each data receive sequence.

### 14.5.3 CLOCK STRETCHING DURING 7-BIT ADDRESSING (STREN = 1)

When the STREN bit is set in Slave Receive mode, the SCL line is held low when the buffer register is full. The method for stretching the SCL output is the same for both 7 and 10-bit addressing modes.

Clock stretching takes place following the ninth clock of the receive sequence. On the falling edge of the ninth clock at the end of the  $\overline{ACK}$  sequence, if the RBF bit is set, the SCLREL bit is automatically cleared, forcing the SCL output to be held low. The user's ISR must set the SCLREL bit before reception is allowed to continue. By holding the SCL line low, the user has time to service the ISR and read the contents of the I2CRCV before the master device can initiate another receive sequence. This will prevent buffer overruns from occurring.

- Note 1: If the user reads the contents of the I2CRCV, clearing the RBF bit before the falling edge of the ninth clock, the SCLREL bit will not be cleared and clock stretching will not occur.

- 2: The SCLREL bit can be set in software regardless of the state of the RBF bit. The user should be careful to clear the RBF bit in the ISR before the next receive sequence in order to prevent an overflow condition.

### 14.5.4 CLOCK STRETCHING DURING 10-BIT ADDRESSING (STREN = 1)

Clock stretching takes place automatically during the addressing sequence. Because this module has a register for the entire address, it is not necessary for the protocol to wait for the address to be updated.

After the address phase is complete, clock stretching will occur on each data receive or transmit sequence as was described earlier.

### 14.6 Software Controlled Clock Stretching (STREN = 1)

When the STREN bit is '1', the SCLREL bit may be cleared by software to allow software to control the clock stretching. The logic will synchronize writes to the SCLREL bit with the SCL clock. Clearing the SCLREL bit will not assert the SCL output until the module detects a falling edge on the SCL output and SCL is sampled low. If the SCLREL bit is cleared by the user while the SCL line has been sampled low, the SCL output will be asserted (held low). The SCL output will remain low until the SCLREL bit is set, and all other devices on the I<sup>2</sup>C bus have de-asserted SCL. This ensures that a write to the SCLREL bit will not violate the minimum high time requirement for SCL.

If the STREN bit is '0', a software write to the SCLREL bit will be disregarded and have no effect on the SCLREL bit.

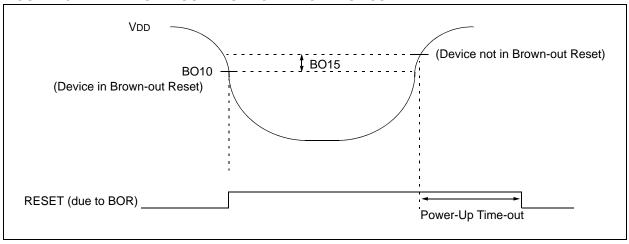

FIGURE 20-2: BROWN-OUT RESET CHARACTERISTICS

TABLE 20-11: ELECTRICAL CHARACTERISTICS: BOR

| DC CHARACTERISTICS  |       | Standard Operating Conditions: 2.5V to 5.5V (unless otherwise stated)<br>Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |                          |      |                    |      |       |                        |

|---------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|--------------------|------|-------|------------------------|

| Param No. Character |       |                                                                                                                                                                                                                                                     | istic                    | Min  | Typ <sup>(1)</sup> | Max  | Units | Conditions             |

| BO10                | VBOR  | BOR Voltage <sup>(2)</sup> on VDD transition high to                                                                                                                                                                                                | BORV = 11 <sup>(3)</sup> | _    | _                  | _    | V     | Not in operating range |

|                     |       | low                                                                                                                                                                                                                                                 | BORV = 10                | 2.6  | _                  | 2.71 | V     |                        |

|                     |       |                                                                                                                                                                                                                                                     | BORV = 01                | 4.1  | _                  | 4.4  | V     |                        |

|                     |       |                                                                                                                                                                                                                                                     | BORV = 00                | 4.58 | _                  | 4.73 | V     |                        |

| BO15                | VBHYS |                                                                                                                                                                                                                                                     |                          | _    | 5                  |      | mV    |                        |

- **Note 1:** Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: These parameters are characterized but not tested in manufacturing.

- **3:** 11 values not in usable operating range.

TABLE 20-12: DC CHARACTERISTICS: PROGRAM AND EEPROM

| DC CHARACTERISTICS |        | Standard Operating Conditions: 2.5V to 5.5V (unless otherwise stated) |                            |          |         |                                                                   |                                                            |  |

|--------------------|--------|-----------------------------------------------------------------------|----------------------------|----------|---------|-------------------------------------------------------------------|------------------------------------------------------------|--|

| DC CHARACTERISTICS |        |                                                                       | Operati                    | ing temp | erature | -40°C ≤TA ≤+85°C for Industrial<br>-40°C ≤TA ≤+125°C for Extended |                                                            |  |

| Param<br>No.       | Symbol | Characteristic                                                        | Min Typ <sup>(1)</sup> Max |          | Units   | Conditions                                                        |                                                            |  |

|                    |        | Data EEPROM Memory <sup>(2)</sup>                                     |                            |          |         |                                                                   |                                                            |  |

| D120               | ED     | Byte Endurance                                                        | 100K                       | 1M       |         | E/W                                                               | -40° C ≤TA ≤+85°C                                          |  |

| D121               | VDRW   | VDD for Read/Write                                                    | VMIN                       | _        | 5.5     | V                                                                 | Using EECON to Read/Write VMIN = Minimum operating voltage |  |

| D122               | TDEW   | Erase/Write Cycle Time                                                | 0.8                        | 2        | 2.6     | ms                                                                | RTSP                                                       |  |

| D123               | TRETD  | Characteristic Retention                                              | 40                         | 100      | _       | Year                                                              | Provided no other specifications are violated              |  |

| D124               | IDEW   | IDD During Programming                                                | _                          | 10       | 30      | mA                                                                | Row Erase                                                  |  |

|                    |        | Program Flash Memory <sup>(2)</sup>                                   |                            |          |         |                                                                   |                                                            |  |

| D130               | ЕР     | Cell Endurance                                                        | 10K                        | 100K     | _       | E/W                                                               | -40° C ≤TA ≤+85°C                                          |  |

| D131               | VPR    | VDD for Read                                                          | VMIN                       | _        | 5.5     | V                                                                 | VMIN = Minimum operating voltage                           |  |

| D132               | VEB    | VDD for Bulk Erase                                                    | 4.5                        | _        | 5.5     | V                                                                 |                                                            |  |

| D133               | VPEW   | VDD for Erase/Write                                                   | 3.0                        | _        | 5.5     | V                                                                 |                                                            |  |

| D134               | TPEW   | Erase/Write Cycle Time                                                | 0.8                        | 2        | 2.6     | ms                                                                | RTSP                                                       |  |

| D135               | TRETD  | Characteristic Retention                                              | 40                         | 100      | _       | Year                                                              | Provided no other specifications are violated              |  |

| D137               | IPEW   | IDD During Programming                                                | _                          | 10       | 30      | mA                                                                | Row Erase                                                  |  |

| D138               | lев    | IDD During Programming                                                |                            | 10       | 30      | mA                                                                | Bulk Erase                                                 |  |

**Note 1:** Data in "Typ" column is at 5V, 25°C unless otherwise stated.

<sup>2:</sup> These parameters are characterized but not tested in manufacturing.

**TABLE 20-14: EXTERNAL CLOCK TIMING REQUIREMENTS**

| AC CHARACTERISTICS                         |               |                                                              | Standard Operating Conditions: 2.5V to 5.5V           |                    |      |                    |                                       |  |  |  |

|--------------------------------------------|---------------|--------------------------------------------------------------|-------------------------------------------------------|--------------------|------|--------------------|---------------------------------------|--|--|--|

|                                            |               |                                                              | (unless otherwise stated)                             |                    |      |                    |                                       |  |  |  |

|                                            |               |                                                              | Operating temperature -40°C ≤TA ≤+85°C for Industrial |                    |      |                    |                                       |  |  |  |

|                                            |               |                                                              | -40°C ≤TA ≤+125°C for Extended                        |                    |      |                    |                                       |  |  |  |

| Param<br>No.                               | Symbol        | Characteristic                                               | Min                                                   | Typ <sup>(1)</sup> | Max  | Units              | Conditions                            |  |  |  |

| OS10                                       | Fosc          | External CLKN Frequency <sup>(2)</sup>                       | DC                                                    | _                  | 40   | MHz                | EC                                    |  |  |  |

|                                            |               | (External clocks allowed only                                | 4                                                     | _                  | 10   | MHz                | EC with 4x PLL                        |  |  |  |

|                                            |               | in EC mode)                                                  | 4                                                     |                    | 10   | MHz                | EC with 8x PLL                        |  |  |  |

|                                            |               |                                                              | 4                                                     | _                  | 7.5  | MHz                | EC with 16x PLL                       |  |  |  |

|                                            |               | Oscillator Frequency <sup>(2)</sup>                          | DC                                                    | _                  | 4    | MHz                | RC                                    |  |  |  |

|                                            |               |                                                              | 0.4                                                   | _                  | 4    | MHz                | XTL                                   |  |  |  |

|                                            |               |                                                              | 4                                                     | _                  | 10   | MHz                | XT                                    |  |  |  |

|                                            |               |                                                              | 4                                                     | _                  | 10   | MHz                | XT with 4x PLL                        |  |  |  |

|                                            |               |                                                              | 4                                                     | _                  | 10   | MHz                | XT with 8x PLL                        |  |  |  |

|                                            |               |                                                              | 4                                                     | _                  | 7.5  | MHz                | XT with 16x PLL                       |  |  |  |

|                                            |               |                                                              | 10                                                    | _                  | 25   | MHz                | HS                                    |  |  |  |

|                                            |               |                                                              | 10                                                    | _                  | 20   | MHz                | HS/2 with 4x PLL                      |  |  |  |

|                                            |               |                                                              | 10                                                    | _                  | 20   | MHz                | HS/2 with 8x PLL                      |  |  |  |

|                                            |               |                                                              | 10                                                    |                    | 15   | MHz                | HS/2 with 16x PLL                     |  |  |  |

|                                            |               |                                                              | 12                                                    |                    | 25   | MHz                | HS/3 with 4x PLL                      |  |  |  |

|                                            |               |                                                              | 12                                                    | _                  | 25   | MHz                | HS/3 with 8x PLL                      |  |  |  |

|                                            |               |                                                              | 12                                                    | _                  | 22.5 | MHz                | HS/3 with 16x PLL                     |  |  |  |

|                                            |               |                                                              | 31                                                    | 7.07               | 33   | kHz                | LP                                    |  |  |  |

|                                            |               |                                                              | _                                                     | 7.37<br>7.37       | _    | MHz<br>MHz         | FRC internal<br>FRC internal w/4x PLL |  |  |  |

|                                            |               |                                                              | _                                                     | 7.37               |      | MHz                | FRC internal w/8x PLL                 |  |  |  |

|                                            |               |                                                              |                                                       | 7.37               |      | MHz                | FRC internal w/16x PLL                |  |  |  |

|                                            |               |                                                              | _                                                     | 512                | _    | kHz                | LPRC internal                         |  |  |  |

| OS20                                       | Tosc          | Tosc = 1/Fosc                                                | _                                                     | _                  | _    | _                  | See parameter OS10 for Fosc value     |  |  |  |

| OS25                                       | Tcy           | Instruction Cycle Time <sup>(2)(3)</sup>                     | 33                                                    | _                  | DC   | ns                 | See Table 20-17                       |  |  |  |

| OS30                                       | TosL,<br>TosH | External Clock <sup>(2)</sup> in (OSC1)<br>High or Low Time  | .45 x<br>Tosc                                         | _                  |      | ns                 | EC                                    |  |  |  |

| OS31                                       | TosR,<br>TosF | External Clock <sup>(2)</sup> in (OSC1)<br>Rise or Fall Time | _                                                     | _                  | 20   | ns                 | EC                                    |  |  |  |

| OS40                                       | TckR          | CLKO Rise Time <sup>(2)(4)</sup>                             | _                                                     | _                  | _    | ns                 | See parameter DO31                    |  |  |  |

| OS41 TckF CLKO Fall Time <sup>(2)(4)</sup> |               | _                                                            | _                                                     |                    | ns   | See parameter DO32 |                                       |  |  |  |

- **Note 1:** Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: These parameters are characterized but not tested in manufacturing.

- 3: Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

- **4:** Measurements are taken in EC or ERC modes. The CLKO signal is measured on the OSC2 pin. CLKO is low for the Q1-Q2 period (1/2 Tcy) and high for the Q3-Q4 period (1/2 Tcy).

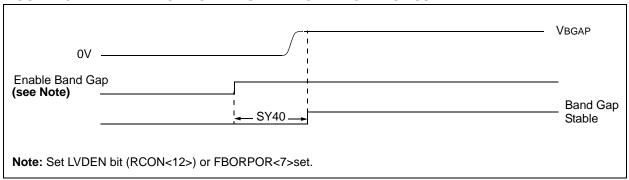

### FIGURE 20-7: BAND GAP START-UP TIME CHARACTERISTICS

### TABLE 20-22: BAND GAP START-UP TIME REQUIREMENTS

| AC CHARACTERISTICS |        |                               | Standard Operating Conditions: 2.5V to 5.5V (unless otherwise stated)  Operating temperature -40°C ≤TA ≤+85°C for Industrial -40°C ≤TA ≤+125°C for Extended |    |    |    |                                                                                                                                                  |

|--------------------|--------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup> | Min Typ <sup>(2)</sup> Max Units Conditions                                                                                                                 |    |    |    | Conditions                                                                                                                                       |

| SY40               | Твдар  | Band Gap Start-up Time        |                                                                                                                                                             | 40 | 65 | μs | Defined as the time between the instant that the band gap is enabled and the moment that the band gap reference voltage is stable.  RCON<13> bit |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated.

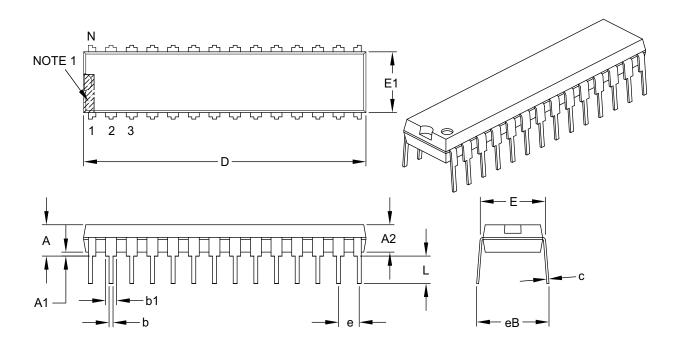

### 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    | INCHES |          |       |  |  |

|----------------------------|----------|--------|----------|-------|--|--|

| Dimensio                   | n Limits | MIN    | NOM      | MAX   |  |  |

| Number of Pins             | N        | 28     |          |       |  |  |

| Pitch                      | е        |        | .100 BSC |       |  |  |

| Top to Seating Plane       | Α        | _      | -        | .200  |  |  |

| Molded Package Thickness   | A2       | .120   | .135     | .150  |  |  |

| Base to Seating Plane      | A1       | .015   | -        | _     |  |  |

| Shoulder to Shoulder Width | E        | .290   | .310     | .335  |  |  |

| Molded Package Width       | E1       | .240   | .285     | .295  |  |  |

| Overall Length             | D        | 1.345  | 1.365    | 1.400 |  |  |

| Tip to Seating Plane       | L        | .110   | .130     | .150  |  |  |

| Lead Thickness             | С        | .008   | .010     | .015  |  |  |

| Upper Lead Width           | b1       | .040   | .050     | .070  |  |  |

| Lower Lead Width           | b        | .014   | .018     | .022  |  |  |

| Overall Row Spacing §      | eВ       | _      | _        | .430  |  |  |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

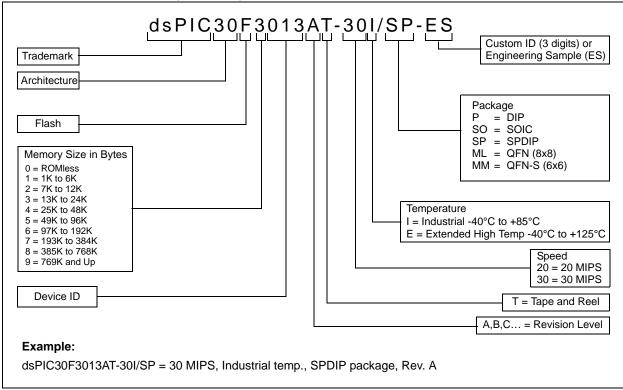

### PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.