Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | dsPIC                                                                          |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 30 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                          |

| Number of I/O              | 12                                                                             |

| Program Memory Size        | 12KB (4K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 1K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                    |

| Data Converters            | A/D 8x12b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 18-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f2011t-30i-so |

© 2010 Microchip Technology Inc.

| TABLE 3-3: | CORE REGISTER MAP |

|------------|-------------------|

| IADLE 353. | CORE REGISTER WAR |

| SFR Name | Address<br>(Home) | Bit 15 | Bit 14 | Bit 13 | Bit 12     | Bit 11  | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4               | Bit 3  | Bit 2 | Bit 1 | Bit 0 | Reset State         |

|----------|-------------------|--------|--------|--------|------------|---------|--------|-------|--------|-------|-------|-------|---------------------|--------|-------|-------|-------|---------------------|

| W0       | 0000              |        |        |        |            |         |        |       | W0/WR  | EG .  |       |       |                     |        |       |       |       | 0000 0000 0000 0000 |

| W1       | 0002              |        |        |        |            |         |        |       | W1     |       |       |       |                     |        |       |       |       | 0000 0000 0000 0000 |

| W2       | 0004              |        | W2     |        |            |         |        |       |        |       |       |       | 0000 0000 0000 0000 |        |       |       |       |                     |

| W3       | 0006              |        |        |        |            |         |        |       | W3     |       |       |       |                     |        |       |       |       | 0000 0000 0000 0000 |

| W4       | 8000              |        |        |        |            |         |        |       | W4     |       |       |       |                     |        |       |       |       | 0000 0000 0000 0000 |

| W5       | 000A              |        |        |        |            |         |        |       | W5     |       |       |       |                     |        |       |       |       | 0000 0000 0000 0000 |

| W6       | 000C              |        |        |        |            |         |        |       | W6     |       |       |       |                     |        |       |       |       | 0000 0000 0000 0000 |

| W7       | 000E              |        |        |        |            |         |        |       | W7     |       |       |       |                     |        |       |       |       | 0000 0000 0000 0000 |

| W8       | 0010              |        |        |        |            |         |        |       | W8     |       |       |       |                     |        |       |       |       | 0000 0000 0000 0000 |

| W9       | 0012              |        |        |        |            |         |        |       | W9     |       |       |       |                     |        |       |       |       | 0000 0000 0000 0000 |

| W10      | 0014              |        |        |        |            |         |        |       | W10    |       |       |       |                     |        |       |       |       | 0000 0000 0000 0000 |

| W11      | 0016              |        |        |        |            |         |        |       | W11    |       |       |       |                     |        |       |       |       | 0000 0000 0000 0000 |

| W12      | 0018              |        |        |        |            |         |        |       | W12    |       |       |       |                     |        |       |       |       | 0000 0000 0000 0000 |

| W13      | 001A              |        |        |        |            |         |        |       | W13    |       |       |       |                     |        |       |       |       | 0000 0000 0000 0000 |

| W14      | 001C              |        |        |        |            |         |        |       | W14    |       |       |       |                     |        |       |       |       | 0000 0000 0000 0000 |

| W15      | 001E              |        |        |        |            |         |        |       | W15    |       |       |       |                     |        |       |       |       | 0000 1000 0000 0000 |

| SPLIM    | 0020              |        |        |        |            |         |        |       | SPLIM  | 1     |       |       |                     |        |       |       |       | 0000 0000 0000 0000 |

| ACCAL    | 0022              |        |        |        |            |         |        |       | ACCA   | L     |       |       |                     |        |       |       |       | 0000 0000 0000 0000 |

| ACCAH    | 0024              |        |        |        |            |         |        |       | ACCA   | H     |       |       |                     |        |       |       |       | 0000 0000 0000 0000 |

| ACCAU    | 0026              |        |        | Sign E | xtension ( | ACCA<39 | 9>)    |       |        |       |       |       | ACC                 | AU     |       |       |       | 0000 0000 0000 0000 |

| ACCBL    | 0028              |        |        |        |            |         |        |       | ACCBI  | L     |       |       |                     |        |       |       |       | 0000 0000 0000 0000 |

| ACCBH    | 002A              |        |        |        |            |         |        |       | ACCBI  | H     |       |       |                     |        |       |       |       | 0000 0000 0000 0000 |

| ACCBU    | 002C              |        |        | Sign E | xtension ( | ACCB<39 | 9>)    |       |        |       |       |       | ACC                 | BU     |       |       |       | 0000 0000 0000 0000 |

| PCL      | 002E              |        |        |        |            |         |        |       | PCL    |       |       |       |                     |        |       |       |       | 0000 0000 0000 0000 |

| PCH      | 0030              | _      | _      | _      | _          | _       | _      | _     | _      | _     |       |       |                     | PCH    |       |       |       | 0000 0000 0000 0000 |

| TBLPAG   | 0032              | _      | _      | _      | _          | _       | _      | _     | _      |       |       |       | TBLP                | AG     |       |       |       | 0000 0000 0000 0000 |

| PSVPAG   | 0034              | _      | _      | _      | _          | _       | _      | _     | _      |       |       |       | PSVF                | PAG    |       |       |       | 0000 0000 0000 0000 |

| RCOUNT   | 0036              |        |        |        |            |         |        |       | RCOUN  | IT.   |       |       |                     |        |       |       |       | uuuu uuuu uuuu uuuu |

| DCOUNT   | 0038              |        |        |        |            |         |        |       | DCOUN  | IT.   |       |       |                     |        |       |       |       | uuuu uuuu uuuu uuuu |

| DOSTARTL | 003A              |        |        |        |            |         |        | DC    | STARTL |       |       |       |                     |        |       |       | 0     | uuuu uuuu uuu0      |

| DOSTARTH | 003C              | _      | _      | _      | _          | _       | _      | _     | _      | _     |       |       | DC                  | STARTH |       |       |       | 0000 0000 0uuu uuuu |

| DOENDL   | 003E              |        |        |        |            |         |        | D     | OENDL  |       |       |       |                     |        |       |       | 0     | uuuu uuuu uuu0      |

| DOENDH   | 0040              | _      | _      |        |            | _       | _      | _     | _      | _     |       |       | D                   | OENDH  |       |       |       | 0000 0000 0uuu uuuu |

| SR       | 0042              | OA     | ОВ     | SA     | SB         | OAB     | SAB    | DA    | DC     | IPL2  | IPL1  | IPL0  | RA                  | N      | OV    | Z     | С     | 0000 0000 0000 0000 |

u = uninitialized bit; — = unimplemented bit, read as '0' Legend:

Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields. Note:

**NOTES:**

#### 5.6 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. A programming operation is nominally 2 msec in duration and the processor stalls (waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

## 5.6.1 PROGRAMMING ALGORITHM FOR PROGRAM FLASH

The user can erase or program one row of program Flash memory at a time. The general process is:

- Read one row of program Flash (32 instruction words) and store into data RAM as a data "image".

- Update the data image with the desired new data.

- 3. Erase program Flash row.

- Set up NVMCON register for multi-word, program Flash, erase, and set WREN bit.

- b) Write address of row to be erased into NVMADRU/NVMDR.

- c) Write 0x55 to NVMKEY.

- d) Write 0xAA to NVMKEY.

- e) Set the WR bit. This begins erase cycle.

- f) CPU stalls for the duration of the erase cycle.

- g) The WR bit is cleared when erase cycle ends.

- Write 32 instruction words of data from data RAM "image" into the program Flash write latches

- Program 32 instruction words into program Flash.

- Set up NVMCON register for multi-word, program Flash, program, and set WREN bit.

- b) Write 0x55 to NVMKEY.

- c) Write 0xAA to NVMKEY.

- d) Set the WR bit. This begins program cycle.

- e) CPU stalls for duration of the program cycle.

- f) The WR bit is cleared by the hardware when program cycle ends.

- Repeat steps 1 through 5 as needed to program desired amount of program Flash memory.

## 5.6.2 ERASING A ROW OF PROGRAM MEMORY

Example 5-1 shows a code sequence that can be used to erase a row (32 instructions) of program memory.

#### **EXAMPLE 5-1: ERASING A ROW OF PROGRAM MEMORY**

```

; Setup NVMCON for erase operation, multi word write

; program memory selected, and writes enabled

#0x4041,W0

MOV

W0 NVMCON

; Init NVMCON SFR

; Init pointer to row to be ERASED

#tblpage(PROG_ADDR),W0

MOV

;

MOV

W0 NVMADRU

; Initialize PM Page Boundary SFR

MOV

#tbloffset(PROG_ADDR),W0

; Intialize in-page EA[15:0] pointer

MOV

W0, NVMADR

; Initialize NVMADR SFR

; Block all interrupts with priority <7 for

DISI

#5

; next 5 instructions

#0x55,W0

MOV

WO NVMKEY

; Write the 0x55 key

MOV

MOV

#0xAA,W1

W1 NVMKEY

MOV

; Write the OxAA key

BSET

NVMCON, #WR

; Start the erase sequence

; Insert two NOPs after the erase

NOP

NOP

; command is asserted

```

**NOTES:**

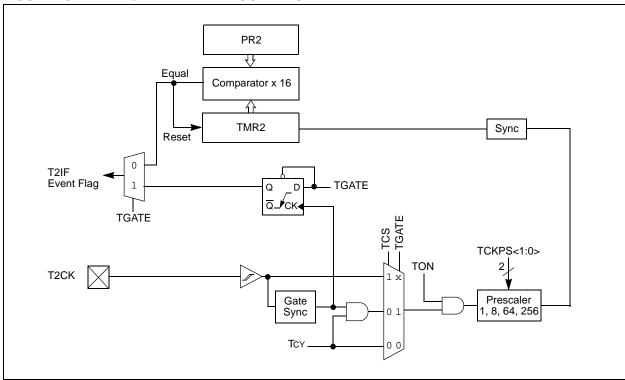

FIGURE 10-2: 16-BIT TIMER2 BLOCK DIAGRAM

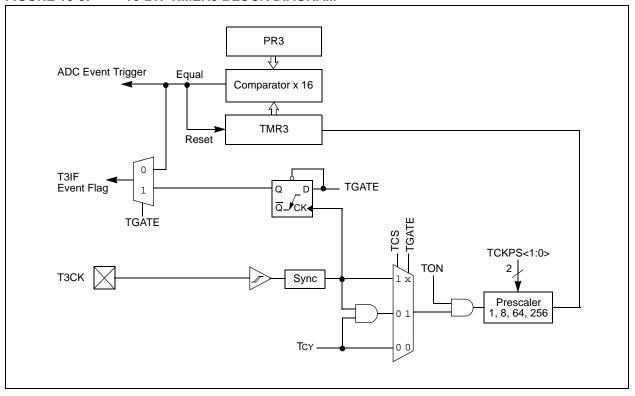

FIGURE 10-3: 16-BIT TIMER3 BLOCK DIAGRAM

#### 13.0 SPI™ MODULE

Note:

This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

The Serial Peripheral Interface (SPI<sup>TM</sup>) module is a synchronous serial interface. It is useful for communicating with other peripheral devices, such as EEPROMs, shift registers, display drivers and A/D converters, or other microcontrollers. It is compatible with Motorola's SPI and SIOP interfaces. The dsPIC30F2011/2012/3012/3013 devices feature one SPI module, SPI1.

### 13.1 Operating Function Description

Figure 13-1 is a simplified block diagram of the SPI module, which consists of a 16-bit shift register, SPI1SR, used for shifting data in and out, and a buffer register, SPI1BUF. Control register SPI1CON (not shown) configures the module. Additionally, status register SPI1STAT (not shown) indicates various status conditions.

Note: See "dsPIC30F Family Reference Manual" (DS70046) for detailed information on the control and status registers.

Four I/O pins comprise the serial interface:

- SDI1 (serial data input)

- SDO1 (serial data output)

- SCK1 (shift clock input or output)

- SS1 (active-low slave select).

In Master mode operation, SCK1 is a clock output. In Slave mode, it is a clock input.

A series of eight (8) or sixteen (16) clock pulses shift out bits from the SPI1SR to SDO1 pin and simultaneously shift in data from SDI1 pin. An interrupt is generated when the transfer is complete and the interrupt flag bit (SPI1IF) is set. This interrupt can be disabled through the interrupt enable bit, SPI1IE.

The receive operation is double-buffered. When a complete byte is received, it is transferred from SPI1SR to SPI1BUF.

If the receive buffer is full when new data is being transferred from SPI1SR to SPI1BUF, the module will set the SPIROV bit indicating an overflow condition. The transfer of the data from SPI1SR to SPI1BUF is not completed and the new data is lost. The module will not respond to SCL transitions while SPIROV is '1', effectively disabling the module until SPI1BUF is read by user software.

Transmit writes are also double-buffered. The user writes to SPI1BUF. When the master or slave transfer is completed, the contents of the shift register (SPI1SR) are moved to the receive buffer. If any transmit data has been written to the buffer register, the contents of the transmit buffer are moved to SPI1SR. The received data is thus placed in SPI1BUF and the transmit data in SPI1SR is ready for the next transfer.

**Note:** Both the transmit buffer (SPI1TXB) and the receive buffer (SPI1RXB) are mapped to the same register address, SPI1BUF.

### 14.7 Interrupts

The I<sup>2</sup>C module generates two interrupt flags, MI2CIF (I<sup>2</sup>C Master Interrupt Flag) and SI2CIF (I<sup>2</sup>C Slave Interrupt Flag). The MI2CIF interrupt flag is activated on completion of a master message event. The SI2CIF interrupt flag is activated on detection of a message directed to the slave.

### 14.8 Slope Control

The I<sup>2</sup>C standard requires slope control on the SDA and SCL signals for Fast mode (400 kHz). The control bit, DISSLW, enables the user to disable slew rate control if desired. It is necessary to disable the slew rate control for 1 MHz mode.

### 14.9 IPMI Support

The control bit, IPMIEN, enables the module to support Intelligent Peripheral Management Interface (IPMI). When this bit is set, the module accepts and acts upon all addresses.

#### 14.10 General Call Address Support

The general call address can address all devices. When this address is used, all devices should, in theory, respond with an acknowledgement.

The general call address is one of eight addresses reserved for specific purposes by the  $I^2C$  protocol. It consists of all '0's with  $R_W = 0$ .

The general call address is recognized when the General Call Enable (GCEN) bit is set (I2CCON<7> = 1). Following a Start bit detection, 8 bits are shifted into I2CRSR and the address is compared with I2CADD, and is also compared with the general call address which is fixed in hardware.

If a general call address match occurs, the I2CRSR is transferred to the I2CRCV after the eighth clock, the RBF flag is set and on the falling edge of the ninth bit (ACK bit), the master event interrupt flag (MI2CIF) is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the I2CRCV to determine if the address was device specific or a general call address.

### 14.11 I<sup>2</sup>C Master Support

As a master device, six operations are supported:

- · Assert a Start condition on SDA and SCL.

- · Assert a Restart condition on SDA and SCL.

- Write to the I2CTRN register initiating transmission of data/address.

- · Generate a Stop condition on SDA and SCL.

- Configure the I<sup>2</sup>C port to receive data.

- Generate an ACK condition at the end of a received byte of data.

### 14.12 I<sup>2</sup>C Master Operation

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the data direction bit. In this case, the data direction bit (R\_W) is logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an  $\overline{ACK}$  bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the data direction bit. In this case, the data direction bit (R\_W) is logic '1'. Thus, the first byte transmitted is a 7-bit slave address, followed by a '1' to indicate receive bit. Serial data is received via SDA while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an ACK bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

### 14.12.1 I<sup>2</sup>C MASTER TRANSMISSION

Transmission of a data byte, a 7-bit address, or the second half of a 10-bit address, is accomplished by simply writing a value to I2CTRN register. The user should only write to I2CTRN when the module is in a WAIT state. This action will set the Buffer Full Flag (TBF) and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted. The Transmit Status Flag, TRSTAT (I2CSTAT<14>), indicates that a master transmit is in progress.

**NOTES:**

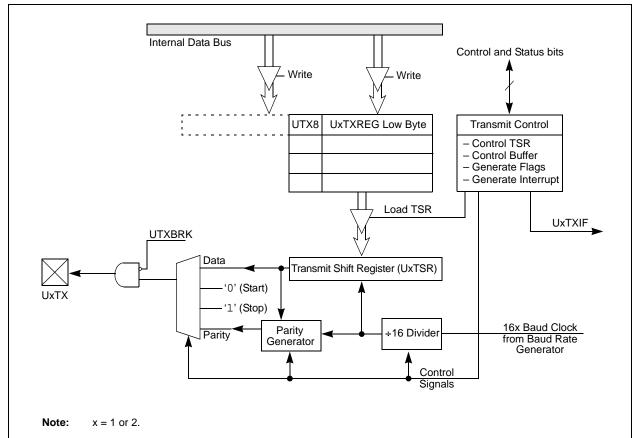

### 15.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART) MODULE

Note:

This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

This section describes the Universal Asynchronous Receiver/Transmitter Communications module. The dsPIC30F2011/2012/3012 processors have one UART module (UART1). The dsPIC30F3013 processor has two UART modules (UART1 and UART2).

#### 15.1 UART Module Overview

The key features of the UART module are:

- Full-duplex, 8 or 9-bit data communication

- Even, odd or no parity options (for 8-bit data)

- · One or two Stop bits

- Fully integrated Baud Rate Generator with 16-bit prescaler

- Baud rates range from 38 bps to 1.875 Mbps at a 30 MHz instruction rate

- 4-word deep transmit data buffer

- · 4-word deep receive data buffer

- Parity, framing and buffer overrun error detection

- Support for interrupt only on address detect (9th bit = 1)

- · Separate transmit and receive interrupts

- Loopback mode for diagnostic support

- Alternate receive and transmit pins for UART1

FIGURE 15-1: UART TRANSMITTER BLOCK DIAGRAM

The configuration procedures in the next section provide the required setup values for the conversion speeds above 100 ksps.

# 16.7.1 200 KSPS CONFIGURATION GUIDELINE

The following configuration items are required to achieve a 200 ksps conversion rate.

- Comply with conditions provided in Table 16-1.

- Connect external VREF+ and VREF- pins following the recommended circuit shown in Figure 16-2.

- Set SSRC<2.0> = 111 in the ADCON1 register to enable the auto convert option.

- Enable automatic sampling by setting the ASAM control bit in the ADCON1 register.

- Write the SMPI<3.0> control bits in the ADCON2 register for the desired number of conversions between interrupts.

- · Configure the ADC clock period to be:

$$\frac{1}{(14+1) \times 200,000} = 334 \text{ ns}$$

by writing to the ADCS<5:0> control bits in the ADCON3 register.

Configure the sampling time to be 1 TAD by writing: SAMC<4:0> = 00001. The following figure shows the timing diagram of the ADC running at 200 ksps. The TAD selection in conjunction with the guidelines described above allows a conversion speed of 200 ksps. See Example 16-1 for code example.

#### 16.8 A/D Acquisition Requirements

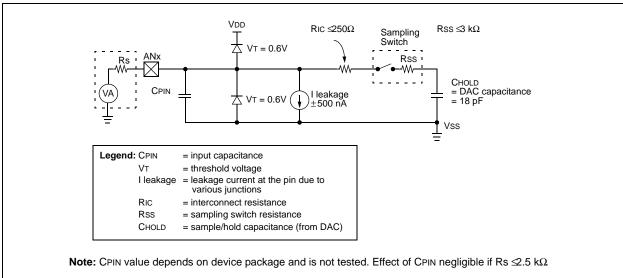

The analog input model of the 12-bit ADC is shown in Figure 16-3. The total sampling time for the A/D is a function of the internal amplifier settling time and the holding capacitor charge time.

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the voltage level on the analog input pin. The impedance source (Rs), the interconnect impedance (Ric) and the internal sampling switch (Rss) impedance combine to directly affect the time required to charge the capacitor CHOLD. The combined impedance of the analog sources must therefore be small enough to fully charge the holding capacitor within the chosen sample time. To minimize the effects of pin leakage currents on the accuracy of the ADC, the maximum recommended source impedance, Rs, is 2.5 k $\Omega$  After the analog input channel is selected (changed), this sampling function must be completed prior to starting the conversion. The internal holding capacitor will be in a discharged state prior to each sample operation.

#### FIGURE 16-3: 12-BIT A/D CONVERTER ANALOG INPUT MODEL

TABLE 16-3: A/D CONVERTER REGISTER MAP FOR dsPIC30F2012/3013

| SFR<br>Name | Addr. | Bit 15 | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10             | Bit 9 | Bit 8  | Bit 7 | Bit 6    | Bit 5       | Bit 4 | Bit 3               | Bit 2               | Bit 1   | Bit 0 | Reset State         |

|-------------|-------|--------|-----------|--------|--------|--------|--------------------|-------|--------|-------|----------|-------------|-------|---------------------|---------------------|---------|-------|---------------------|

| ADCBUF0     | 0280  | _      |           |        | _      |        | ADC Data Buffer 0  |       |        |       |          |             |       |                     | 0000 uuuu uuuu uuuu |         |       |                     |

| ADCBUF1     | 0282  | _      | _         | _      | _      |        |                    |       |        |       | ADC Dat  | ta Buffer 1 |       |                     |                     |         |       | 0000 uuuu uuuu uuuu |

| ADCBUF2     | 0284  | _      | _         | _      | _      |        |                    |       |        |       | ADC Dat  | ta Buffer 2 |       |                     |                     |         |       | 0000 uuuu uuuu uuuu |

| ADCBUF3     | 0286  | _      | _         | _      | _      |        |                    |       |        |       | ADC Dat  | ta Buffer 3 |       |                     |                     |         |       | 0000 uuuu uuuu uuuu |

| ADCBUF4     | 0288  | _      | _         | _      | _      |        |                    |       |        |       | ADC Dat  | ta Buffer 4 |       |                     |                     |         |       | 0000 uuuu uuuu uuuu |

| ADCBUF5     | 028A  | _      | _         | _      | _      |        |                    |       |        |       | ADC Dat  | ta Buffer 5 |       |                     |                     |         |       | 0000 uuuu uuuu uuuu |

| ADCBUF6     | 028C  | _      | _         | _      | _      |        |                    |       |        |       | ADC Dat  | ta Buffer 6 |       |                     |                     |         |       | 0000 uuuu uuuu uuuu |

| ADCBUF7     | 028E  | _      | _         | _      | _      |        |                    |       |        |       | ADC Dat  | ta Buffer 7 |       |                     |                     |         |       | 0000 uuuu uuuu uuuu |

| ADCBUF8     | 0290  | _      | _         | _      | _      |        |                    |       |        |       | ADC Dat  | ta Buffer 8 |       |                     |                     |         |       | 0000 uuuu uuuu uuuu |

| ADCBUF9     | 0292  | _      | _         | _      | _      |        |                    |       |        |       | ADC Dat  | ta Buffer 9 |       |                     |                     |         |       | 0000 uuuu uuuu uuuu |

| ADCBUFA     | 0294  | _      | _         | _      | _      |        | ADC Data Buffer 10 |       |        |       |          |             |       | 0000 uuuu uuuu uuuu |                     |         |       |                     |

| ADCBUFB     | 0296  | _      | _         | _      | _      |        |                    |       |        |       | ADC Data | a Buffer 11 |       |                     |                     |         |       | 0000 uuuu uuuu uuuu |

| ADCBUFC     | 0298  | _      | _         | _      | _      |        |                    |       |        |       | ADC Data | a Buffer 12 | 2     |                     |                     |         |       | 0000 uuuu uuuu uuuu |

| ADCBUFD     | 029A  | _      | _         | _      | _      |        |                    |       |        |       | ADC Data | a Buffer 13 | 3     |                     |                     |         |       | 0000 uuuu uuuu uuuu |

| ADCBUFE     | 029C  | _      | _         | _      | _      |        |                    |       |        |       | ADC Data | a Buffer 14 | 1     |                     |                     |         |       | 0000 uuuu uuuu uuuu |

| ADCBUFF     | 029E  | _      | _         | _      | _      |        |                    |       |        |       | ADC Data | a Buffer 15 | 5     |                     |                     |         |       | 0000 uuuu uuuu uuuu |

| ADCON1      | 02A0  | ADON   | _         | ADSIDL | _      | _      | _                  | FORM  | /<1:0> | S     | SRC<2:0  | >           | _     | _                   | ASAM                | SAMP    | DONE  | 0000 0000 0000 0000 |

| ADCON2      | 02A2  | V      | 'CFG<2:0> | •      | _      | _      | CSCNA              | _     | _      | BUFS  | _        |             | SMPI  | <3:0>               |                     | BUFM    | ALTS  | 0000 0000 0000 0000 |

| ADCON3      | 02A4  | _      | _         | _      |        | SA     | MC<4:0>            |       |        | ADRC  | _        |             |       | ADCS                | S<5:0>              |         |       | 0000 0000 0000 0000 |

| ADCHS       | 02A6  | _      | _         | _      | CH0NB  |        | CH0SB-             | <3:0> |        | _     | _        |             | CH0NA |                     | CH0S                | SA<3:0> |       | 0000 0000 0000 0000 |

| ADPCFG      | 02A8  | _      | _         | _      | _      | _      | _                  | PCFG9 | PCFG8  | PCFG7 | PCFG6    | PCFG5       | PCFG4 | PCFG3               | PCFG2               | PCFG1   | PCFG0 | 0000 0000 0000 0000 |

| ADCSSL      | 02AA  | _      | _         | _      | _      | _      | _                  | CSSL9 | CSSL8  | CSSL7 | CSSL6    | CSSL5       | CSSL4 | CSSL3               | CSSL2               | CSSL1   | CSSL0 | 0000 0000 0000 0000 |

**Legend:** u = uninitialized bit; — = unimplemented bit, read as '0'

**Note:** Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

Any interrupt that is individually enabled (using the corresponding IE bit) and meets the prevailing priority level will be able to wake-up the processor. The processor will process the interrupt and branch to the ISR. The Sleep Status bit in the RCON register is set upon wake-up.

Note:

In spite of various delays applied (TPOR, TLOCK and TPWRT), the crystal oscillator (and PLL) may not be active at the end of the time-out (e.g., for low-frequency crystals). In such cases, if FSCM is enabled, then the device will detect this as a clock failure and process the clock failure trap, the FRC oscillator will be enabled and the user will have to re-enable the crystal oscillator. If FSCM is not enabled, then the device will simply suspend execution of code until the clock is stable and will remain in Sleep until the oscillator clock has started.

All Resets will wake-up the processor from Sleep mode. Any Reset, other than POR, will set the Sleep Status bit. In a POR, the Sleep bit is cleared.

If the Watchdog Timer is enabled, then the processor will wake-up from Sleep mode upon WDT time-out. The Sleep and WDTO Status bits are both set.

#### 17.6.2 IDLE MODE

In Idle mode, the clock to the CPU is shut down while peripherals keep running. Unlike Sleep mode, the clock source remains active.

Several peripherals have a control bit in each module that allows them to operate during Idle.

LPRC Fail-Safe Clock remains active if clock failure detect is enabled.

The processor wakes up from Idle if at least one of the following conditions has occurred:

- any interrupt that is individually enabled (IE bit is '1') and meets the required priority level

- any Reset (POR, BOR, MCLR)

- WDT time-out

Upon wake-up from Idle mode, the clock is re-applied to the CPU and instruction execution begins immediately, starting with the instruction following the PWRSAV instruction.

Any interrupt that is individually enabled (using IE bit) and meets the prevailing priority level will be able to wake-up the processor. The processor will process the interrupt and branch to the ISR. The Idle Status bit in the RCON register is set upon wake-up.

Any Reset other than POR will set the Idle Status bit. On a POR, the Idle bit is cleared.

If Watchdog Timer is enabled, then the processor will wake-up from Idle mode upon WDT time-out. The Idle and WDTO Status bits are both set.

Unlike wake-up from Sleep, there are no time delays involved in wake-up from Idle.

### 17.7 Device Configuration Registers

The Configuration bits in each device Configuration register specify some of the device modes and are programmed by a device programmer, or by using the In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) feature of the device. Each device Configuration register is a 24-bit register, but only the lower 16 bits of each register are used to hold configuration data. There are five device Configuration registers available to the user:

- FOSC (0xF80000): Oscillator Configuration Register

- FWDT (0xF80002): Watchdog Timer Configuration Register

- FBORPOR (0xF80004): BOR and POR Configuration Register

- 4. FGS (0xF8000A): General Code Segment Configuration Register

- FICD (0xF8000C): Debug Configuration Register

The placement of the Configuration bits is automatically handled when you select the device in your device programmer. The desired state of the Configuration bits may be specified in the source code (dependent on the language tool used), or through the programming interface. After the device has been programmed, the application software may read the Configuration bit values through the table read instructions. For additional information, please refer to the Programming Specifications of the device.

Note:

If the code protection Configuration fuse bits (FGS<GCP> and FGS<GWRP>) have been programmed, an erase of the entire code-protected device is only possible at voltages VDD  $\geq$  4.5V.

### TABLE 18-1: SYMBOLS USED IN OPCODE DESCRIPTIONS (CONTINUED)

| Field | Description                                                                                                                                                                                                           |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wb    | Base W register ∈ {W0W15}                                                                                                                                                                                             |

| Wd    | Destination W register ∈ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                                                                                                                                                     |

| Wdo   | Destination W register ∈ { Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] }                                                                                                                                     |

| Wm,Wn | Dividend, Divisor working register pair (direct addressing)                                                                                                                                                           |

| Wm*Wm | Multiplicand and Multiplier working register pair for Square instructions ∈ {W4*W4,W5*W5,W6*W6,W7*W7}                                                                                                                 |

| Wm*Wn | Multiplicand and Multiplier working register pair for DSP instructions ∈ {W4*W5,W4*W6,W4*W7,W5*W6,W5*W7,W6*W7}                                                                                                        |

| Wn    | One of 16 working registers ∈ {W0W15}                                                                                                                                                                                 |

| Wnd   | One of 16 destination working registers ∈ {W0W15}                                                                                                                                                                     |

| Wns   | One of 16 source working registers ∈ {W0W15}                                                                                                                                                                          |

| WREG  | W0 (working register used in file register instructions)                                                                                                                                                              |

| Ws    | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                                                                                                                                                          |

| Wso   | Source W register ∈ { Wns, [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }                                                                                                                                                 |

| Wx    | X data space prefetch address register for DSP instructions ∈ {[W8]+=6, [W8]+=4, [W8]+=2, [W8], [W8]-=6, [W8]-=4, [W8]-=2, [W9]+=6, [W9]+=4, [W9]+=2, [W9], [W9]-=6, [W9]-=4, [W9]-=2, [W9+W12],none}                 |

| Wxd   | X data space prefetch destination register for DSP instructions ∈ {W4W7}                                                                                                                                              |

| Wy    | Y data space prefetch address register for DSP instructions ∈ {[W10]+=6, [W10]+=4, [W10]+=2, [W10], [W10]-=6, [W10]-=4, [W10]-=2, [W11]+=6, [W11]+=4, [W11]+=2, [W11], [W11]-=6, [W11]-=4, [W11]-=2, [W11+W12], none} |

| Wyd   | Y data space prefetch destination register for DSP instructions ∈ {W4W7}                                                                                                                                              |

TABLE 20-9: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

| DC CHA       | NRACTER | ISTICS                                                 | Standard Operating Conditions: 2.5V to 5.5V  (unless otherwise stated)  Operating temperature -40°C ≤TA ≤+85°C for Industrial -40°C ≤TA ≤+125°C for Extended |   |      |    |                                                                        |  |  |  |  |

|--------------|---------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|----|------------------------------------------------------------------------|--|--|--|--|

| Param<br>No. | Symbol  | Characteristic                                         | Min Typ <sup>(1)</sup> Max Units Conditions                                                                                                                  |   |      |    |                                                                        |  |  |  |  |

|              | Vol     | Output Low Voltage <sup>(2)</sup>                      |                                                                                                                                                              |   |      |    |                                                                        |  |  |  |  |

| DO10         |         | I/O ports                                              | _                                                                                                                                                            | _ | 0.6  | V  | IOL = 8.5  mA, VDD = 5V                                                |  |  |  |  |

|              |         |                                                        | _                                                                                                                                                            | _ | 0.15 | V  | IOL = 2.0  mA, VDD = 3V                                                |  |  |  |  |

| DO16         |         | OSC2/CLKO                                              | _                                                                                                                                                            | _ | 0.6  | V  | IOL = 1.6 mA, VDD = 5V                                                 |  |  |  |  |

|              |         | (RC or EC Osc mode)                                    | _                                                                                                                                                            | _ | 0.72 | V  | IOL = 2.0  mA, VDD = 3V                                                |  |  |  |  |

|              | Vон     | Output High Voltage <sup>(2)</sup>                     |                                                                                                                                                              |   |      |    |                                                                        |  |  |  |  |

| DO20         |         | I/O ports                                              | VDD - 0.7                                                                                                                                                    | _ | _    | V  | IOH = -3.0 mA, VDD = 5V                                                |  |  |  |  |

|              |         |                                                        | VDD - 0.2                                                                                                                                                    | _ | _    | V  | IOH = -2.0 mA, VDD = 3V                                                |  |  |  |  |

| DO26         |         | OSC2/CLKO                                              | VDD - 0.7                                                                                                                                                    | _ | _    | V  | IOH = -1.3 mA, VDD = 5V                                                |  |  |  |  |

|              |         | (RC or EC Osc mode)                                    | VDD - 0.1                                                                                                                                                    | _ | _    | V  | IOH = -2.0 mA, VDD = 3V                                                |  |  |  |  |

|              |         | Capacitive Loading Specs on Output Pins <sup>(2)</sup> |                                                                                                                                                              |   |      |    |                                                                        |  |  |  |  |

| DO50         | Cosc2   | OSC2/SOSC2 pin                                         | _                                                                                                                                                            | _ | 15   | pF | In XTL, XT, HS and LP modes when external clock is used to drive OSC1. |  |  |  |  |

| DO56         | Cio     | All I/O pins and OSC2                                  | _                                                                                                                                                            | _ | 50   | pF | RC or EC Osc mode                                                      |  |  |  |  |

| DO58         | Св      | SCL, SDA                                               | _                                                                                                                                                            | _ | 400  | pF | In I <sup>2</sup> C mode                                               |  |  |  |  |

**Note 1:** Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**<sup>2:</sup>** These parameters are characterized but not tested in manufacturing.

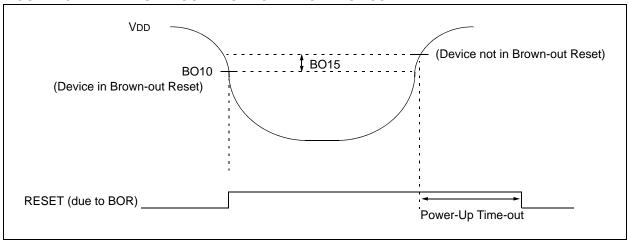

FIGURE 20-2: BROWN-OUT RESET CHARACTERISTICS

TABLE 20-11: ELECTRICAL CHARACTERISTICS: BOR

| DC CHAR      | ACTERIST | ics                                                  | (unless otherw           | Standard Operating Conditions: 2.5V to 5.5V (unless otherwise stated)  Operating temperature -40°C ≤TA ≤+85°C for Industrial -40°C ≤TA ≤+125°C for Extended |                    |      |       |                        |  |  |  |

|--------------|----------|------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|-------|------------------------|--|--|--|

| Param<br>No. | Symbol   | Character                                            | istic                    | Min                                                                                                                                                         | Typ <sup>(1)</sup> | Max  | Units | Conditions             |  |  |  |

| BO10         | VBOR     | BOR Voltage <sup>(2)</sup> on VDD transition high to | BORV = 11 <sup>(3)</sup> | _                                                                                                                                                           | _                  | _    | V     | Not in operating range |  |  |  |

|              |          | low                                                  | BORV = 10                | 2.6                                                                                                                                                         | _                  | 2.71 | V     |                        |  |  |  |

|              |          |                                                      | BORV = 01                | 4.1                                                                                                                                                         | _                  | 4.4  | V     |                        |  |  |  |

|              |          |                                                      | BORV = 00                | 4.58                                                                                                                                                        | _                  | 4.73 | V     |                        |  |  |  |

| BO15         | VBHYS    |                                                      |                          | _                                                                                                                                                           | 5                  |      | mV    |                        |  |  |  |

- **Note 1:** Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: These parameters are characterized but not tested in manufacturing.

- **3:** 11 values not in usable operating range.

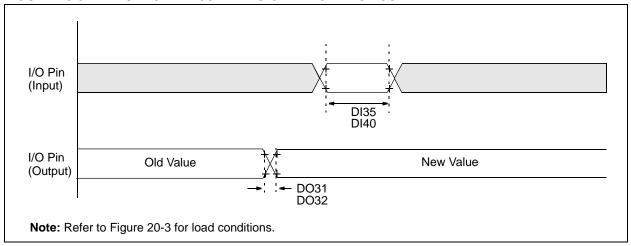

#### FIGURE 20-5: CLKO AND I/O TIMING CHARACTERISTICS

#### TABLE 20-20: CLKO AND I/O TIMING REQUIREMENTS

| AC CHAR      | ACTERISTI | cs                                  | Standard Operating Conditions: 2.5V to 5.5V  (unless otherwise stated)  Operating temperature -40°C ≤TA ≤+85°C for Industrial -40°C ≤TA ≤+125°C for Extended |       |                    |     |       |            |  |  |

|--------------|-----------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------|-----|-------|------------|--|--|

| Param<br>No. | Symbol    | Characteristic <sup>(1)(2)(3)</sup> |                                                                                                                                                              | Min   | Typ <sup>(4)</sup> | Max | Units | Conditions |  |  |

| DO31         | TioR      | Port output rise time               |                                                                                                                                                              | _     | 7                  | 20  | ns    |            |  |  |

| DO32         | TioF      | Port output fall time               |                                                                                                                                                              | _     | 7                  | 20  | ns    |            |  |  |

| DI35         | TINP      | INTx pin high or low time (output)  |                                                                                                                                                              | 20    | _                  |     | ns    |            |  |  |

| DI40         | TRBP      | CNx high or low time                | (input)                                                                                                                                                      | 2 Tcy | _                  |     | ns    | _          |  |  |

- Note 1: These parameters are asynchronous events not related to any internal clock edges

- 2: Measurements are taken in RC mode and EC mode where CLKO output is 4 x Tosc.

- 3: These parameters are characterized but not tested in manufacturing.

- **4:** Data in "Typ" column is at 5V, 25°C unless otherwise stated.

SP36 **SCK**X (CKP = 0)SP11 SP10 SP20 SP21 SCKx (CKP = 1)SP35 SP20 SP21 LSb SDOx MSb **BIT 14** SP40 SP30,SP31 SDIX MS<sub>b</sub> IN LS<sub>b</sub> IN SP41 Note: Refer to Figure 20-3 for load conditions.

FIGURE 20-13: SPI MODULE MASTER MODE (CKE =1) TIMING CHARACTERISTICS

TABLE 20-30: SPI MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHA       | RACTERIST             | TICS                                       | Standard Operating Conditions: 2.5V to 5.5V (unless otherwise stated) Operating temperature -40°C ≤TA ≤+85°C for Industrial -40°C ≤TA ≤+125°C for Extended |                    |     |       |                       |  |  |  |  |

|--------------|-----------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|-----------------------|--|--|--|--|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>              | Min                                                                                                                                                        | Typ <sup>(2)</sup> | Max | Units | Conditions            |  |  |  |  |

| SP10         | TscL                  | SCKx output low time(3)                    | Tcy/2                                                                                                                                                      | _                  | _   | ns    | _                     |  |  |  |  |

| SP11         | TscH                  | SCKx output high time <sup>(3)</sup>       | Tcy/2                                                                                                                                                      | _                  | _   | ns    | _                     |  |  |  |  |

| SP20         | TscF                  | SCKx output fall time <sup>(4)</sup>       | _                                                                                                                                                          | _                  | _   | ns    | See parameter<br>DO32 |  |  |  |  |

| SP21         | TscR                  | SCKx output rise time <sup>(4)</sup>       | _                                                                                                                                                          | _                  | _   | ns    | See parameter<br>DO31 |  |  |  |  |

| SP30         | TdoF                  | SDOx data output fall time <sup>(4)</sup>  | _                                                                                                                                                          | _                  | _   | ns    | See parameter<br>DO32 |  |  |  |  |

| SP31         | TdoR                  | SDOx data output rise time <sup>(4)</sup>  | _                                                                                                                                                          | _                  | _   | ns    | See parameter<br>DO31 |  |  |  |  |

| SP35         | TscH2doV,<br>TscL2doV | SDOx data output valid after SCKx edge     | _                                                                                                                                                          | _                  | 30  | ns    | _                     |  |  |  |  |

| SP36         | TdoV2sc,<br>TdoV2scL  | SDOx data output setup to first SCKx edge  | 30                                                                                                                                                         | _                  | 1   | ns    | _                     |  |  |  |  |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup time of SDIx data input to SCKx edge | 20                                                                                                                                                         | _                  |     | ns    |                       |  |  |  |  |

| SP41         | TscH2diL,<br>TscL2diL | Hold time of SDIx data input to SCKx edge  | 20                                                                                                                                                         | _                  | _   | ns    | _                     |  |  |  |  |

- Note 1: These parameters are characterized but not tested in manufacturing.

- **2:** Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** The minimum clock period for SCK is 100 ns. Therefore, the clock generated in master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPI pins.

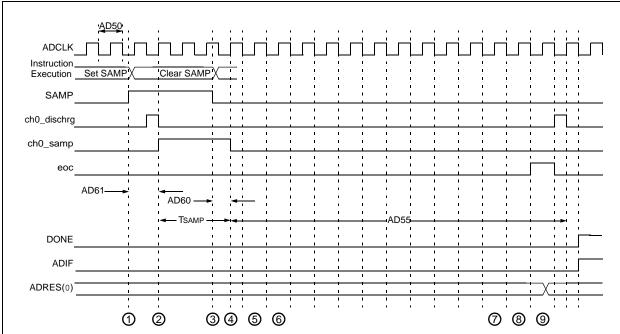

FIGURE 20-21: 12-BIT A/D CONVERSION TIMING CHARACTERISTICS (ASAM = 0, SSRC = 000)

- 1 Software sets ADCON. SAMP to start sampling.

- ② Sampling starts after discharge period.

TSAMP is described in **Section 18. "12-bit A/D Converter"** in the *dsPIC30F Family Reference Manual* (DS70046).

- 3 Software clears ADCON. SAMP to Start conversion.

- 4 Sampling ends, conversion sequence starts.

- (5) Convert bit 11.

- 6 Convert bit 10.

- 7 Convert bit 1.

- 8 Convert bit 0.

- (9) One TAD for end of conversion.

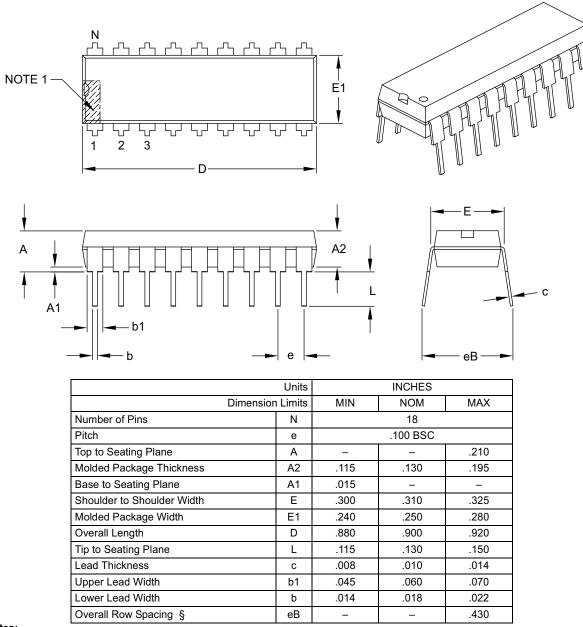

### 18-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-007B

| Erasing, Word                                                | 56  | Input                                                           | 156 |

|--------------------------------------------------------------|-----|-----------------------------------------------------------------|-----|

| Protection Against Spurious Write                            | 58  | Output                                                          | 156 |

| Reading                                                      | 55  | I/O Ports                                                       | 59  |

| Write Verify                                                 | 58  | Parallel (PIO)                                                  |     |

| Writing                                                      | 57  | I <sup>2</sup> C 10-bit Slave Mode Operation                    | 99  |

| Writing, Block                                               |     | Reception                                                       |     |

| Writing, Word                                                |     | Transmission                                                    |     |

| DC Characteristics                                           |     | I <sup>2</sup> C 7-bit Slave Mode Operation                     |     |

| BOR                                                          |     | Reception                                                       |     |

| Brown-out Reset                                              |     | Transmission                                                    |     |

| I/O Pin Input Specifications                                 |     | I <sup>2</sup> C Master Mode Operation                          |     |

| I/O Pin Output Specifications                                |     | Baud Rate Generator                                             |     |

| Idle Current (IIDLE)                                         |     | Clock Arbitration                                               | 102 |

| Low-Voltage Detect                                           |     | Multi-Master Communication,                                     | 400 |

| LVDL                                                         |     | Bus Collision and Bus Arbitration                               |     |

| Operating Current (IDD)                                      |     | Reception Transmission                                          |     |

| Power-Down Current (IPD) Program and EEPROM                  |     | I <sup>2</sup> C Master Mode Support                            |     |

| Temperature and Voltage Specifications                       |     | I <sup>2</sup> C Module                                         | 101 |

| Development Support                                          |     | Addresses                                                       | aa  |

| Device Configuration                                         | 140 | Bus Data Timing Characteristics                                 | 55  |

| Register Map                                                 | 136 | Master Mode                                                     | 177 |

| Device Configuration Registers                               |     | Slave Mode                                                      |     |

| FBORPOR                                                      | 134 | Bus Data Timing Requirements                                    |     |

| FGS                                                          |     | Master Mode                                                     | 178 |

| FOSC                                                         |     | Slave Mode                                                      |     |

| FWDT                                                         |     | Bus Start/Stop Bits Timing Characteristics                      |     |

| Device Overview                                              |     | Master Mode                                                     | 177 |

| Disabling the UART                                           | 107 | Slave Mode                                                      | 179 |

| Divide Support                                               |     | General Call Address Support                                    | 101 |

| Instructions (Table)                                         |     | Interrupts                                                      |     |

| DSP Engine                                                   | 23  | IPMI Support                                                    | 101 |

| Multiplier                                                   | 25  | Operating Function Description                                  | 97  |

| Dual Output Compare Match Mode                               | 88  | Operation During CPU Sleep and Idle Modes                       | 102 |

| Continuous Pulse Mode                                        | 88  | Pin Configuration                                               | 97  |

| Single Pulse Mode                                            | 88  | Programmer's Model                                              | 97  |

| E                                                            |     | Register Map                                                    |     |

|                                                              |     | Registers                                                       |     |

| Electrical Characteristics                                   |     | Slope Control                                                   |     |

| AC                                                           |     | Software Controlled Clock Stretching (STREN = 1)                |     |

| DC                                                           | 150 | Various Modes                                                   |     |

| Enabling and Setting Up UART                                 | 407 | Idle Current (IDLE)                                             |     |

| Alternate I/OSetting Up Data, Parity and Stop Bit Selection: |     | In-Circuit Serial Programming (ICSP)                            |     |

| Enabling the UART                                            |     | Input Capture (CAPX) Timing Characteristics                     |     |

| Equations                                                    | 107 | Input Capture Module                                            |     |

| ADC Conversion Clock                                         | 115 | Interrupts                                                      |     |

| Baud Rate                                                    |     | Register MapInput Capture Operation During Sleep and Idle Modes |     |

| Serial Clock Rate                                            |     | CPU Idle Mode                                                   |     |

| Errata                                                       |     | CPU Sleep Mode                                                  |     |

| Exception Sequence                                           |     | Input Capture Timing Requirements                               |     |

| Trap Sources                                                 | 67  | Input Change Notification Module                                |     |

| External Clock Timing Characteristics                        |     | dsPIC30F2012/3013 Register Map (Bits 7-0)                       |     |

| Type A, B and C Timer                                        | 167 | Instruction Addressing Modes                                    |     |

| External Clock Timing Requirements                           |     | File Register Instructions                                      |     |

| Type A Timer                                                 |     | Fundamental Modes Supported                                     |     |

| Type B Timer                                                 |     | MAC Instructions                                                |     |

| Type C Timer                                                 | 168 | MCU Instructions                                                |     |

| External Interrupt Requests                                  |     | Move and Accumulator Instructions                               |     |

| _                                                            |     | Other Instructions                                              |     |

| F                                                            |     | Instruction Set                                                 |     |

| Fast Context Saving                                          | 70  | Overview                                                        | 140 |

| Flash Program Memory                                         | 49  | Summary                                                         | 137 |

| 1                                                            |     | Internal Clock Timing Examples                                  | 163 |

| I/O Din Chapitications                                       |     | Internet Address                                                | 205 |

| I/O Pin Specifications                                       |     |                                                                 |     |