Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                         |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 30 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 20                                                                            |

| Program Memory Size        | 12KB (4K x 24)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | <u>.</u>                                                                      |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 10x12b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 28-QFN (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f2012-30i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The SA and SB bits are modified each time data passes through the adder/subtracter but can only be cleared by the user. When set, they indicate that the accumulator has overflowed its maximum range (bit 31 for 32-bit saturation or bit 39 for 40-bit saturation) and will be saturated if saturation is enabled. When saturation is not enabled, SA and SB default to bit 39 overflow and thus indicate that a catastrophic overflow has occurred. If the COVTE bit in the INTCON1 register is set, SA and SB bits generate an arithmetic warning trap when saturation is disabled.

The overflow and saturation Status bits can optionally be viewed in the STATUS register (SR) as the logical OR of OA and OB (in bit OAB) and the logical OR of SA and SB (in bit SAB). This allows programmers to check one bit in the STATUS register to determine if either accumulator has overflowed, or one bit to determine if either accumulator has saturated. This would be useful for complex number arithmetic which typically uses both the accumulators.

The device supports three saturation and overflow modes:

1. Bit 39 Overflow and Saturation:

When bit 39 overflow and saturation occurs, the saturation logic loads the maximally positive 9.31 (0x7FFFFFFFF) or maximally negative 9.31 value (0x800000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user. This is referred to as 'super saturation' and provides protection against erroneous data or unexpected algorithm problems (e.g., gain calculations).

- 2. Bit 31 Overflow and Saturation: When bit 31 overflow and saturation occurs, the saturation logic then loads the maximally positive 1.31 value (0x007FFFFFF) or maximally negative 1.31 value (0x0080000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user. When this Saturation mode is in effect, the guard bits are not used, so the OA, OB or OAB bits are never set.

- 3. Bit 39 Catastrophic Overflow:

The bit 39 overflow Status bit from the adder is used to set the SA or SB bit which remains set until cleared by the user. No saturation operation is performed and the accumulator is allowed to overflow (destroying its sign). If the COVTE bit in the INTCON1 register is set, a catastrophic overflow can initiate a trap exception.

## 2.4.2.2 Accumulator 'Write-Back'

The MAC class of instructions (with the exception of MPY, MPY.N, ED and EDAC) can optionally write a rounded version of the high word (bits 31 through 16) of the accumulator that is not targeted by the instruction into data space memory. The write is performed across the X bus into combined X and Y address space. The following addressing modes are supported:

1. W13, Register Direct:

The rounded contents of the non-target accumulator are written into W13 as a 1.15 fraction.

[W13]+ = 2, Register Indirect with Post-Increment: The rounded contents of the non-target accumulator are written into the address pointed to by W13 as a 1.15 fraction. W13 is then incremented by 2 (for a word write).

## 2.4.2.3 Round Logic

The round logic is a combinational block which performs a conventional (biased) or convergent (unbiased) round function during an accumulator write (store). The Round mode is determined by the state of the RND bit in the CORCON register. It generates a 16-bit, 1.15 data value, which is passed to the data space write saturation logic. If rounding is not indicated by the instruction, a truncated 1.15 data value is stored and the least significant word (lsw) is simply discarded.

Conventional rounding takes bit 15 of the accumulator, zero-extends it and adds it to the ACCxH word (bits 16 through 31 of the accumulator). If the ACCxL word (bits 0 through 15 of the accumulator) is between 0x8000 and 0xFFFF (0x8000 included), ACCxH is incremented. If ACCxL is between 0x0000 and 0x7FFF, ACCxH is left unchanged. A consequence of this algorithm is that over a succession of random rounding operations, the value tends to be biased slightly positive.

Convergent (or unbiased) rounding operates in the same manner as conventional rounding, except when ACCxL equals 0x8000. If this is the case, the LSb (bit 16 of the accumulator) of ACCxH is examined. If it is '1', ACCxH is incremented. If it is '0', ACCxH is not modified. Assuming that bit 16 is effectively random in nature, this scheme will remove any rounding bias that may accumulate.

The SAC and SAC.R instructions store either a truncated (SAC) or rounded (SAC.R) version of the contents of the target accumulator to data memory via the X bus (subject to data saturation, see **Section 2.4.2.4 "Data Space Write Saturation"**). Note that for the MAC class of instructions, the accumulator write-back operation functions in the same manner, addressing combined MCU (X and Y) data space though the X bus. For this class of instructions, the data is always subject to rounding.

|                          | Access                                  | Program Space Address |           |               |               |      |  |  |  |  |  |  |

|--------------------------|-----------------------------------------|-----------------------|-----------|---------------|---------------|------|--|--|--|--|--|--|

| Access Type              | Space                                   | <23>                  | <22:16>   | <14:1>        | <0>           |      |  |  |  |  |  |  |

| Instruction Access       | User                                    | 0                     |           | PC<22:1>      |               | 0    |  |  |  |  |  |  |

| TBLRD/TBLWT              | User<br>(TBLPAG<7> = 0)                 | TBL                   | PAG<7:0>  |               | Data EA<15:0> |      |  |  |  |  |  |  |

| TBLRD/TBLWT              | Configuration<br>(TBLPAG<7> = 1)        | TBL                   | .PAG<7:0> | Data EA<15:0> |               |      |  |  |  |  |  |  |

| Program Space Visibility | isibility User 0 PSVPAG<7:0> Data EA<14 |                       |           |               |               | 4:0> |  |  |  |  |  |  |

### TABLE 3-1: PROGRAM SPACE ADDRESS CONSTRUCTION

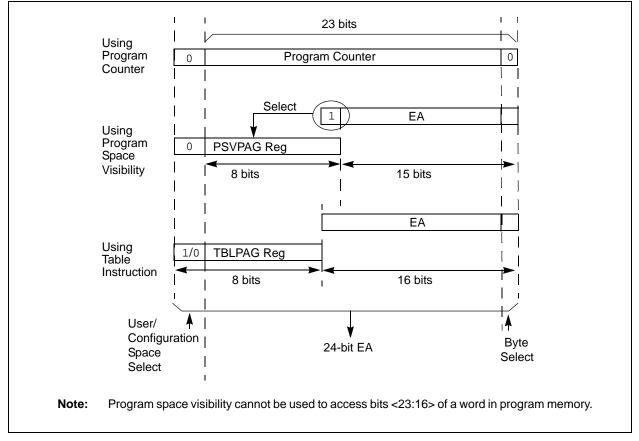

### FIGURE 3-2: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

## 3.2.2 DATA SPACES

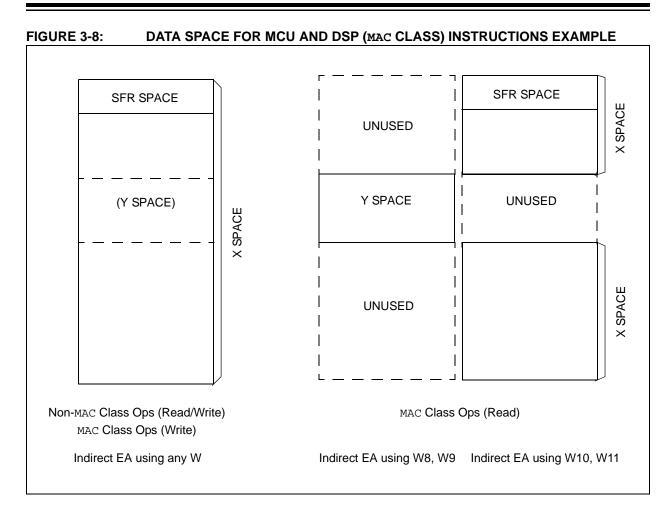

The X data space is used by all instructions and supports all addressing modes. There are separate read and write data buses. The X read data bus is the return data path for all instructions that view data space as combined X and Y address space. It is also the X address space data path for the dual operand read instructions (MAC class). The X write data bus is the only write path to data space for all instructions.

The X data space also supports Modulo Addressing for all instructions, subject to Addressing mode restrictions. Bit-Reversed Addressing is only supported for writes to X data space.

The Y data space is used in concert with the X data space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths. No writes occur across the Y bus. This class of instructions dedicates two W register pointers, W10 and W11, to always address Y data space, independent of X data space, whereas W8 and W9 always address X data space. Note that during accumulator write back, the data address space is considered a combination of X and Y data spaces, so the write occurs across the X bus. Consequently, the write can be to any address in the entire data space.

The Y data space can only be used for the data prefetch operation associated with the MAC class of instructions. It also supports Modulo Addressing for automated circular buffers. Of course, all other instructions can access the Y data address space through the X data path as part of the composite linear space.

The boundary between the X and Y data spaces is defined as shown in Figure 3-7 and is not user programmable. Should an EA point to data outside its own assigned address space, or to a location outside physical memory, an all zero word/byte is returned. For example, although Y address space is visible by all non-MAC instructions using any addressing mode, an attempt by a MAC instruction to fetch data from that space using W8 or W9 (X space pointers) returns 0x0000.

#### TABLE 3-2: EFFECT OF INVALID MEMORY ACCESSES

| Attempted Operation                                         | Data Returned |

|-------------------------------------------------------------|---------------|

| EA = an unimplemented address                               | 0x0000        |

| W8 or W9 used to access Y data space in a MAC instruction   | 0x0000        |

| W10 or W11 used to access X data space in a MAC instruction | 0x0000        |

All Effective Addresses are 16 bits wide and point to bytes within the data space. Therefore, the data space address range is 64 Kbytes or 32K words.

## 3.2.3 DATA SPACE WIDTH

The core data width is 16 bits. All internal registers are organized as 16-bit wide words. Data space memory is organized in byte addressable, 16-bit wide blocks.

## 3.2.4 DATA ALIGNMENT

To help maintain backward compatibility with PIC® MCU devices and improve data space memory usage efficiency, the dsPIC30F instruction set supports both word and byte operations. Data is aligned in data memory and registers as words, but all data space EAs resolve to bytes. Data byte reads read the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the X data path (no byte accesses are possible from the Y data path as the MAC class of instruction can only fetch words). That is, data memory and registers are organized as two parallel byte wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register which matches the byte address.

As a consequence of this byte accessibility, all Effective Address calculations (including those generated by the DSP operations which are restricted to word-sized data) are internally scaled to step through word-aligned memory. For example, the core would recognize that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care should be taken when mixing byte and word operations, or translating from 8-bit MCU code. Should a misaligned read or write be attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed, whereas if it occurred on a write, the instruction is executed, but the write does not occur. In either case, a trap is then executed, allowing the system and/or user to examine the machine state prior to execution of the address fault.

#### FIGURE 3-9: DATA ALIGNMENT

|      | 15 <b>MSB</b> 8 | B 7 LSB | 0 |      |

|------|-----------------|---------|---|------|

| 0001 | Byte 1          | Byte 0  |   | 0000 |

| 0003 | Byte 3          | Byte 2  |   | 0002 |

| 0005 | Byte 5          | Byte 4  |   | 0004 |

|      |                 |         |   |      |

NOTES:

| TABLE       | 8-2: | dsP    | PIC30F | 2011/2    | 012/30 | 12 INT | ERRU   | PT COI     | NTROL  | LER R  | EGIS  | ER N    | IAP     |         |        |             |        |                     |

|-------------|------|--------|--------|-----------|--------|--------|--------|------------|--------|--------|-------|---------|---------|---------|--------|-------------|--------|---------------------|

| SFR<br>Name | ADR  | Bit 15 | Bit 14 | Bit 13    | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8  | Bit 7  | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | Reset State         |

| INTCON1     | 0080 | NSTDIS | _      | _         | _      | _      | OVATE  | OVBTE      | COVTE  | _      |       | _       | MATHERR | ADDRERR | STKERR | OSCFAIL     | _      | 0000 0000 0000 0000 |

| INTCON2     | 0082 | ALTIVT | DISI   |           | _      | I      | _      |            |        | _      |       | -       |         | _       | INT2EP | INT1EP      | INT0EP | 0000 0000 0000 0000 |

| IFS0        | 0084 | CNIF   | MI2CIF | SI2CIF    | NVMIF  | ADIF   | U1TXIF | U1RXIF     | SPI1IF | T3IF   | T2IF  | OC2IF   | IC2IF   | T1IF    | OC1IF  | IC1IF       | INTOIF | 0000 0000 0000 0000 |

| IFS1        | 0086 | _      | _      |           | _      | I      | _      |            |        | INT2IF |       | _       |         | _       | _      | _           | INT1IF | 0000 0000 0000 0000 |

| IFS2        | 0088 | _      | _      |           | _      |        | LVDIF  |            |        | _      |       | _       |         | _       | _      | _           | _      | 0000 0000 0000 0000 |

| IEC0        | 008C | CNIE   | MI2CIE | SI2CIE    | NVMIE  | ADIE   | U1TXIE | U1RXIE     | SPI1IE | T3IE   | T2IE  | OC2IE   | IC2IE   | T1IE    | OC1IE  | IC1IE       | INTOIE | 0000 0000 0000 0000 |

| IEC1        | 008E |        | _      |           |        |        | _      |            |        | INT2IE |       | _       |         | _       | _      | _           | INT1IE | 0000 0000 0000 0000 |

| IEC2        | 0090 |        |        |           |        |        | LVDIE  |            |        | _      |       | _       |         | —       | _      | —           |        | 0000 0000 0000 0000 |

| IPC0        | 0094 | _      | -      | T1IP<2:0> | •      |        | 0      | DC1IP<2:0  | >      | —      |       | IC1IP<  | 2:0>    | _       |        | NT0IP<2:0;  | >      | 0100 0100 0100 0100 |

| IPC1        | 0096 | _      | 1      | [31P<2:0  | >      | I      |        | T2IP<2:0>  |        | _      |       | OC2IP<  | 2:0>    | _       |        | IC2IP<2:0>  |        | 0100 0100 0100 0100 |

| IPC2        | 0098 | _      | A      | ADIP<2:0> | >      | _      | U      | 1TXIP<2:0  | )>     | —      |       | U1RXIP  | <2:0>   | _       | 5      | SPI1IP<2:0; | >      | 0100 0100 0100 0100 |

| IPC3        | 009A | _      | C      | CNIP<2:0  | >      |        | N      | 112CIP<2:0 | )>     | _      |       | SI2CIP< | 2:0>    | _       | ١      | NVMIP<2:0   | >      | 0100 0100 0100 0100 |

| IPC4        | 009C | _      | _      |           | _      | I      | _      |            |        | _      |       | _       |         | _       |        | NT1IP<2:0>  | >      | 0000 0000 0000 0100 |

| IPC5        | 009E | _      | IN     | T2IP<2:0  | >      |        | _      |            |        | _      |       | _       |         | _       | _      | _           | -      | 0100 0000 0000 0000 |

| IPC6        | 00A0 |        | _      |           |        |        | _      |            |        | _      | 1     | 0       | 0       | —       | 1      | 0           | 0      | 0000 0000 0100 0100 |

| IPC7        | 00A2 |        | -      | I         | -      |        | _      |            |        | -      |       | _       |         | —       | _      | _           | -      | 0000 0000 0000 0000 |

| IPC8        | 00A4 |        | _      | -         | _      |        | _      |            |        | _      | -     | -       |         | _       | _      | _           |        | 0000 0000 0000 0000 |

| IPC9        | 00A6 |        | -      | I         | -      | I      | _      | _          |        | -      |       | _       |         | _       | _      | _           | _      | 0000 0000 0000 0000 |

| IPC10       | 00A8 |        | _      | _         | _      |        | L      | VDIP<2:0   | >      | _      | _     | -       |         | —       | _      | —           | —      | 0000 0100 0000 0000 |

#### TABLE 8-2. dePIC30E2011/2012/3012 INTERRUPT CONTROLLER REGISTER MAP

**Legend:** u = uninitialized bit; — = unimplemented bit, read as '0'

Note: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

### TABLE 9-1: TIMER1 REGISTER MAP

| SFR Name | Addr.                     | Bit 15 | Bit 14                                        | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5               | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset State |

|----------|---------------------------|--------|-----------------------------------------------|--------|--------|--------|--------|-------|-------|-------|-------|---------------------|-------|-------|-------|-------|-------|-------------|

| TMR1     | TMR1 0100 Timer1 Register |        |                                               |        |        |        |        |       |       |       |       | uuuu uuuu uuuu uuuu |       |       |       |       |       |             |

| PR1      | 0102 Period Register 1    |        |                                               |        |        |        |        |       |       |       |       | 1111 1111 1111 1111 |       |       |       |       |       |             |

| T1CON    | 0104                      | TON    | TON - TSIDL TGATE TCKPS1 TCKPS0 - TSYNC TCS - |        |        |        |        |       |       |       |       | 0000 0000 0000 0000 |       |       |       |       |       |             |

Legend: u = uninitialized bit; - = unimplemented bit, read as '0'

Note: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

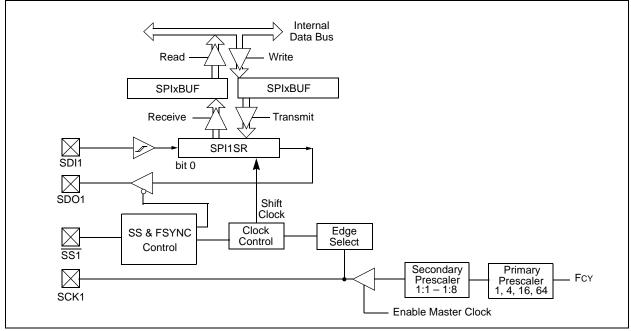

## FIGURE 13-1: SPI BLOCK DIAGRAM

Figure 13-2 depicts the a master/slave connection between two processors. In Master mode, the clock is generated by prescaling the system clock. Data is transmitted as soon as a value is written to SPI1BUF. The interrupt is generated at the middle of the transfer of the last bit.

In Slave mode, data is transmitted and received as external clock pulses appear on SCK. Again, the interrupt is generated when the last bit is latched. If SS1 control is enabled, then transmission and reception are enabled only when SS1 = low. The SDO1 output will be disabled in SS1 mode with SS1 high.

The clock provided to the module is (Fosc/4). This clock is then prescaled by the primary (PPRE<1:0>) and the secondary (SPRE<2:0>) prescale factors. The CKE bit determines whether transmit occurs on transition from active clock state to Idle clock state, or vice versa. The CKP bit selects the Idle state (high or low) for the clock.

#### 13.1.1 WORD AND BYTE COMMUNICATION

A control bit, MODE16 (SPI1CON<10>), allows the module to communicate in either 16-bit or 8-bit mode. 16-bit operation is identical to 8-bit operation except that the number of bits transmitted is 16 instead of 8.

The user software must disable the module prior to changing the MODE16 bit. The SPI module is reset when the MODE16 bit is changed by the user.

A basic difference between 8-bit and 16-bit operation is that the data is transmitted out of bit 7 of the SPI1SR for 8-bit operation, and data is transmitted out of bit 15 of the SPI1SR for 16-bit operation. In both modes, data is shifted into bit 0 of the SPI1SR.

## 13.1.2 SDO1 DISABLE

A control bit, DISSDO, is provided to the SPI1CON register to allow the SDO1 output to be disabled. This will allow the SPI module to be connected in an input only configuration. SDO1 can also be used for general purpose I/O.

## 13.2 Framed SPI Support

The module supports a basic framed SPI protocol in Master or Slave mode. The control bit, FRMEN, enables framed SPI support and causes the SS1 pin to perform the Frame Synchronization Pulse (FSYNC) function. The control bit, SPIFSD, determines whether the SS1 pin is an input or an output (i.e., whether the module receives or generates the Frame Synchronization Pulse). The frame pulse is an active-high pulse for a single SPI clock cycle. When Frame Synchronization is enabled, the data transmission starts only on the subsequent transmit edge of the SPI clock.

## 14.0 I<sup>2</sup>C<sup>™</sup> MODULE

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

The Inter-Integrated Circuit  $(l^2C^{TM})$  module provides complete hardware support for both Slave and Multi-Master modes of the  $l^2C$  serial communication standard, with a 16-bit interface.

This module offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation.

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing.

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing.

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves.

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control).

- I<sup>2</sup>C supports multi-master operation; detects bus collision and will arbitrate accordingly.

## 14.1 Operating Function Description

The hardware fully implements all the master and slave functions of the  $I^2C$  Standard and Fast mode specifications, as well as 7 and 10-bit addressing.

Thus, the  $l^2C$  module can operate either as a slave or a master on an  $l^2C$  bus.

## 14.1.1 VARIOUS I<sup>2</sup>C MODES

The following types of I<sup>2</sup>C operation are supported:

- I<sup>2</sup>C slave operation with 7-bit addressing

- I<sup>2</sup>C slave operation with 10-bit addressing

- I<sup>2</sup>C master operation with 7-bit or 10-bit addressing

See the I<sup>2</sup>C programmer's model (Figure 14-1).

### 14.1.2 PIN CONFIGURATION IN I<sup>2</sup>C MODE

${\sf I}^2{\sf C}$  has a 2-pin interface; the SCL pin is clock and the SDA pin is data.

## 14.1.3 I<sup>2</sup>C REGISTERS

I2CCON and I2CSTAT are control and status registers, respectively. The I2CCON register is readable and writable. The lower 6 bits of I2CSTAT are read-only. The remaining bits of the I2CSTAT are read/write.

I2CRSR is the shift register used for shifting data, whereas I2CRCV is the buffer register to which data bytes are written, or from which data bytes are read. I2CRCV is the receive buffer as shown in Figure 14-1. I2CTRN is the transmit register to which bytes are written during a transmit operation, as shown in Figure 14-2.

The I2CADD register holds the slave address. A Status bit, ADD10, indicates 10-bit Address mode. The I2CBRG acts as the Baud Rate Generator reload value.

In receive operations, I2CRSR and I2CRCV together form a double-buffered receiver. When I2CRSR receives a complete byte, it is transferred to I2CRCV and an interrupt pulse is generated. During transmission, the I2CTRN is not double-buffered.

**Note:** Following a Restart condition in 10-bit mode, the user only needs to match the first 7-bit address.

#### **FIGURE 14-1: PROGRAMMER'S MODEL** I2CRCV (8 bits) Bit 7 Bit 0 I2CTRN (8 bits) Bit 7 Bit 0 I2CBRG (9 bits) Bit 8 Bit 0 I2CCON (16 bits) Bit 15 Bit 0 I2CSTAT (16 bits) Bit 15 Bit 0 I2CADD (10 bits) Bit 9 Bit 0

## 14.7 Interrupts

The I<sup>2</sup>C module generates two interrupt flags, MI2CIF (I<sup>2</sup>C Master Interrupt Flag) and SI2CIF (I<sup>2</sup>C Slave Interrupt Flag). The MI2CIF interrupt flag is activated on completion of a master message event. The SI2CIF interrupt flag is activated on detection of a message directed to the slave.

## 14.8 Slope Control

The I<sup>2</sup>C standard requires slope control on the SDA and SCL signals for Fast mode (400 kHz). The control bit, DISSLW, enables the user to disable slew rate control if desired. It is necessary to disable the slew rate control for 1 MHz mode.

## 14.9 IPMI Support

The control bit, IPMIEN, enables the module to support Intelligent Peripheral Management Interface (IPMI). When this bit is set, the module accepts and acts upon all addresses.

## 14.10 General Call Address Support

The general call address can address all devices. When this address is used, all devices should, in theory, respond with an acknowledgement.

The general call address is one of eight addresses reserved for specific purposes by the  $I^2C$  protocol. It consists of all '0's with R\_W = 0.

The general call address is recognized when the General Call Enable (GCEN) bit is set (I2CCON<7> = 1). Following a Start bit detection, 8 bits are shifted into I2CRSR and the address is compared with I2CADD, and is also compared with the general call address which is fixed in hardware.

If a general call address match occurs, the I2CRSR is transferred to the I2CRCV after the eighth clock, the RBF flag is set and on the falling edge of the ninth bit (ACK bit), the master event interrupt flag (MI2CIF) is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the I2CRCV to determine if the address was device specific or a general call address.

## 14.11 I<sup>2</sup>C Master Support

As a master device, six operations are supported:

- · Assert a Start condition on SDA and SCL.

- Assert a Restart condition on SDA and SCL.

- Write to the I2CTRN register initiating transmission of data/address.

- Generate a Stop condition on SDA and SCL.

- Configure the I<sup>2</sup>C port to receive data.

- Generate an ACK condition at the end of a received byte of data.

## 14.12 I<sup>2</sup>C Master Operation

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the data direction bit. In this case, the data direction bit ( $R_W$ ) is logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an ACK bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the data direction bit. In this case, the data direction bit (R\_W) is logic '1'. Thus, the first byte transmitted is a 7-bit slave address, followed by a '1' to indicate receive bit. Serial data is received via SDA while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an ACK bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

### 14.12.1 I<sup>2</sup>C MASTER TRANSMISSION

Transmission of a data byte, a 7-bit address, or the second half of a 10-bit address, is accomplished by simply writing a value to I2CTRN register. The user should only write to I2CTRN when the module is in a WAIT state. This action will set the Buffer Full Flag (TBF) and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted. The Transmit Status Flag, TRSTAT (I2CSTAT<14>), indicates that a master transmit is in progress.

## 16.0 12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

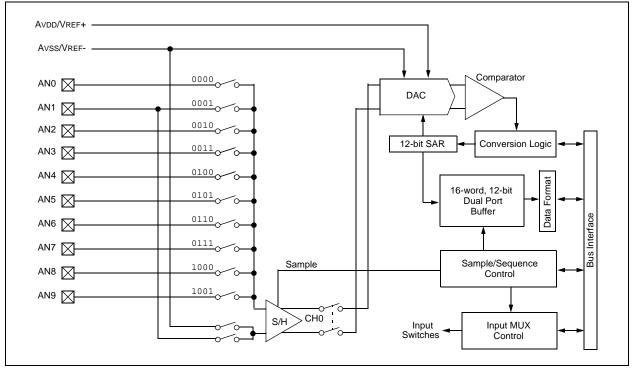

The 12-bit Analog-to-Digital Converter allows conversion of an analog input signal to a 12-bit digital number. This module is based on a Successive Approximation Register (SAR) architecture and provides a maximum sampling rate of 200 ksps. The ADC module has up to 10 analog inputs which are multiplexed into a sample and hold amplifier. The output of the sample and hold is the input into the converter which generates the result. The analog reference voltage is software selectable to either the device supply voltage (AVDD/AVSS) or the voltage level on the (VREF+/VREF-) pin. The ADC has a unique feature of being able to operate while the device is in Sleep mode with RC oscillator selection.

The ADC module has six 16-bit registers:

- A/D Control Register 1 (ADCON1)

- A/D Control Register 2 (ADCON2)

- A/D Control Register 3 (ADCON3)

- A/D Input Select Register (ADCHS)

- A/D Port Configuration Register (ADPCFG)

- A/D Input Scan Selection Register (ADCSSL)

The ADCON1, ADCON2 and ADCON3 registers control the operation of the ADC module. The ADCHS register selects the input channels to be converted. The ADPCFG register configures the port pins as analog inputs or as digital I/O. The ADCSSL register selects inputs for scanning.

| Note: | The SSRC<2:0>, ASAM, SMPI<3:0>,           |

|-------|-------------------------------------------|

|       | BUFM and ALTS bits, as well as the        |

|       | ADCON3 and ADCSSL registers, must         |

|       | not be written to while $ADON = 1$ . This |

|       | would lead to indeterminate results.      |

The block diagram of the 12-bit ADC module is shown in Figure 16-1.

## FIGURE 16-1: 12-BIT ADC FUNCTIONAL BLOCK DIAGRAM

### 16.9 Module Power-Down Modes

The module has two internal power modes.

When the ADON bit is '1', the module is in Active mode; it is fully powered and functional.

When ADON is '0', the module is in Off mode. The digital and analog portions of the circuit are disabled for maximum current savings.

In order to return to the Active mode from Off mode, the user must wait for the ADC circuitry to stabilize.

## 16.10 A/D Operation During CPU Sleep and Idle Modes

#### 16.10.1 A/D OPERATION DURING CPU SLEEP MODE

When the device enters Sleep mode, all clock sources to the module are shut down and stay at logic '0'.

If Sleep occurs in the middle of a conversion, the conversion is aborted. The converter will not continue with a partially completed conversion on exit from Sleep mode.

Register contents are not affected by the device entering or leaving Sleep mode.

The ADC module can operate during Sleep mode if the A/D clock source is set to RC (ADRC = 1). When the RC clock source is selected, the ADC module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed which eliminates all digital switching noise from the conversion. When the conversion is complete, the CONV bit will be cleared and the result loaded into the ADCBUF register.

If the A/D interrupt is enabled, the device will wake-up from Sleep. If the A/D interrupt is not enabled, the ADC module will then be turned off, although the ADON bit will remain set.

## 16.10.2 A/D OPERATION DURING CPU IDLE MODE

The ADSIDL bit selects if the module will stop on Idle or continue on Idle. If ADSIDL = 0, the module will continue operation on assertion of Idle mode. If ADSIDL = 1, the module will stop on Idle.

## 16.11 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the ADC module to be turned off, and any conversion and sampling sequence is aborted. The values that are in the ADCBUF registers are not modified. The A/D Result register will contain unknown data after a Power-on Reset.

## 16.12 Output Formats

The A/D result is 12 bits wide. The data buffer RAM is also 12 bits wide. The 12-bit data can be read in one of four different formats. The FORM<1:0> bits select the format. Each of the output formats translates to a 16-bit result on the data bus.

| FIGURE 16-4: | A/D OUTPUT DATA FORMATS |

|--------------|-------------------------|

|              |                         |

| RAM Contents:     |     |     |     |     | d11 | d10 | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 |

|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Read to Bus:      |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Signed Fractional | d11 | d10 | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 | 0   | 0   | 0   | 0   |

|                   |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     | J   |

| Fractional        | d11 | d10 | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 | 0   | 0   | 0   | 0   |

|                   | LI  |     |     |     |     |     |     |     |     |     |     |     |     |     |     | II  |

| Signed Integer    | d11 | d11 | d11 | d11 | d11 | d10 | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 |

|                   |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     | L]  |

| Integer           | 0   | 0   | 0   | 0   | d11 | d10 | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 |

|                   |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

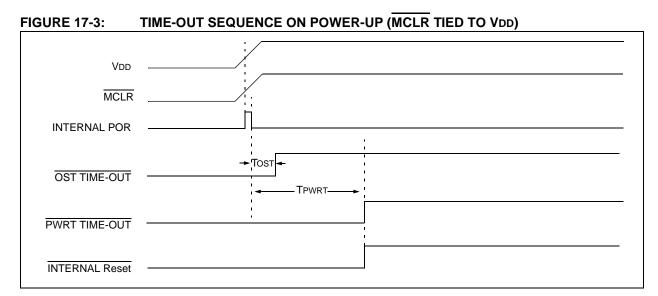

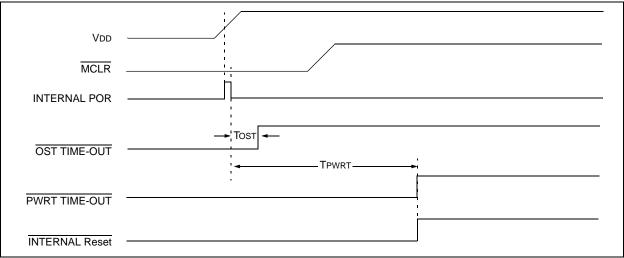

## FIGURE 17-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

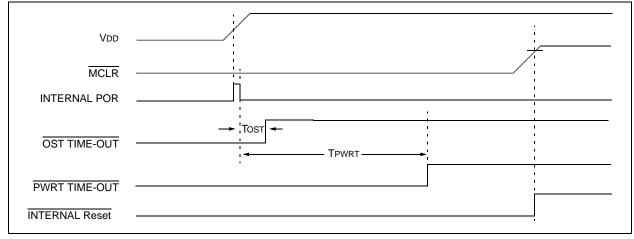

## FIGURE 17-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

## 17.8 Peripheral Module Disable (PMD) Registers

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled via the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The Control and Status registers associated with the peripheral will also be disabled so writes to those registers will have no effect and read values will be invalid.

A peripheral module will only be enabled if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

- **Note 1:** If a PMD bit is set, the corresponding module is disabled after a delay of 1 instruction cycle. Similarly, if a PMD bit is cleared, the corresponding module is enabled after a delay of 1 instruction cycle (assuming the module Control registers are already configured to enable module operation).

- 2: In dsPIC30F2011, dsPIC30F3012 and dsPIC30F2012 devices, the U2MD bit is readable and writable and will be read as '1' when set.

## 17.9 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 2 is selected as a Debugger, the In-Circuit Debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. When the device has this feature enabled, some of the resources are not available for general use. These resources include the first 80 bytes of Data RAM and two I/O pins.

One of four pairs of Debug I/O pins may be selected by the user using configuration options in MPLAB IDE. These pin pairs are named EMUD/EMUC, EMUD1/EMUC1, EMUD2/EMUC2 and EMUD3/EMUC3.

In each case, the selected EMUD pin is the Emulation/Debug Data line, and the EMUC pin is the Emulation/Debug Clock line. These pins will interface to the MPLAB ICD 2 module available from Microchip. The selected pair of Debug I/O pins is used by MPLAB ICD 2 to send commands and receive responses, as well as to send and receive data. To use the In-Circuit Debugger function of the device, the design must implement ICSP connections to MCLR, VDD, VSS, PGC, PGD and the selected EMUDx/EMUCx pin pair.

This gives rise to two possibilities:

- 1. If EMUD/EMUC is selected as the Debug I/O pin pair, then only a 5-pin interface is required, as the EMUD and EMUC pin functions are multiplexed with the PGD and PGC pin functions in all dsPIC30F devices.

- If EMUD1/EMUC1, EMUD2/EMUC2 or EMUD3/EMUC3 is selected as the Debug I/O pin pair, then a 7-pin interface is required, as the EMUDx/EMUCx pin functions (x = 1, 2 or 3) are not multiplexed with the PGD and PGC pin functions.

### TABLE 20-15: PLL CLOCK TIMING SPECIFICATIONS (VDD = 2.5 TO 5.5 V)

| AC CHA       | RACTERI | STICS                | Standard (<br>(unless of<br>Operating | herwise      | <b>stated)</b><br>ure -40° | 'C ≤Ta ≤+8          | 5°C for I | Industrial<br>Extended |

|--------------|---------|----------------------|---------------------------------------|--------------|----------------------------|---------------------|-----------|------------------------|

| Param<br>No. | Symbol  | Characterist         | ic <sup>(1)</sup>                     | Min          | Тур <sup>(2)</sup>         | Max                 | Units     | Conditions             |

| OS50         | Fplli   | PLL Input Frequency  | Range <sup>(2)</sup>                  | 4            | _                          | 10                  | MHz       | EC with 4x PLL         |

|              |         |                      |                                       | 4            | —                          | 10                  | MHz       | EC with 8x PLL         |

|              |         |                      |                                       | 4            | —                          | 7.5 <sup>(4)</sup>  | MHz       | EC with 16x PLL        |

|              |         |                      |                                       | 4            | —                          | 10                  | MHz       | XT with 4x PLL         |

|              |         |                      |                                       | 4            | —                          | 10                  | MHz       | XT with 8x PLL         |

|              |         |                      |                                       | 4            | —                          | 7.5 <sup>(4)</sup>  | MHz       | XT with 16x PLL        |

|              |         |                      |                                       | 5 <b>(3)</b> | —                          | 10                  | MHz       | HS/2 with 4x PLL       |

|              |         |                      |                                       | 5 <b>(3)</b> | —                          | 10                  | MHz       | HS/2 with 8x PLL       |

|              |         |                      |                                       | 5 <b>(3)</b> | —                          | 7.5 <sup>(4)</sup>  | MHz       | HS/2 with 16x PLL      |

|              |         |                      |                                       | 4            | —                          | 8.33 <sup>(3)</sup> | MHz       | HS/3 with 4x PLL       |

|              |         |                      |                                       | 4            | _                          | 8.33 <sup>(3)</sup> | MHz       | HS/3 with 8x PLL       |

|              |         |                      |                                       | 4            | —                          | 7.5 <sup>(4)</sup>  | MHz       | HS/3 with 16x PLL      |

| OS51         | Fsys    | On-Chip PLL Output   | (2)                                   | 16           | _                          | 120                 | MHz       | EC, XT, HS/2, HS/3     |

|              |         | · · ·                |                                       |              |                            |                     |           | modes with PLL         |

| OS52         | TLOC    | PLL Start-up Time (L | ock Time)                             | _            | 20                         | 50                  | μs        |                        |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: Limited by oscillator frequency range.

4: Limited by device operating frequency range.

## TABLE 20-16: PLL JITTER

| AC CHAI      | RACTERISTICS   | (unless | Standard Operating Conditions: 2.5V to 5.5V   (unless otherwise stated)   Operating temperature -40°C ≤TA ≤+85°C for Industrial   -40°C ≤TA ≤+125°C for Extended |       |       |                                   |                   |  |  |  |  |  |  |

|--------------|----------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-----------------------------------|-------------------|--|--|--|--|--|--|

| Param<br>No. | Characteristic | Min     | Typ <sup>(1)</sup>                                                                                                                                               | Max   | Units | Condi                             | tions             |  |  |  |  |  |  |

| OS61         | x4 PLL         |         | 0.251                                                                                                                                                            | 0.413 | %     | -40°C ≤TA ≤+85°C                  | VDD = 3.0 to 3.6V |  |  |  |  |  |  |

|              |                | _       | 0.251                                                                                                                                                            | 0.413 | %     | -40°C ≤TA ≤+125°C                 | VDD = 3.0 to 3.6V |  |  |  |  |  |  |

|              |                | —       | 0.256                                                                                                                                                            | 0.47  | %     | -40°C ≤TA ≤+85°C                  | VDD = 4.5 to 5.5V |  |  |  |  |  |  |

|              |                | —       | 0.256                                                                                                                                                            | 0.47  | %     | -40°C ≤TA ≤+125°C                 | VDD = 4.5 to 5.5V |  |  |  |  |  |  |

|              | x8 PLL         | —       | 0.355                                                                                                                                                            | 0.584 | %     | -40°C ≤TA ≤+85°C                  | VDD = 3.0 to 3.6V |  |  |  |  |  |  |

|              |                | —       | 0.355                                                                                                                                                            | 0.584 | %     | -40°C ≤TA ≤+125°C                 | VDD = 3.0 to 3.6V |  |  |  |  |  |  |

|              |                |         | 0.362                                                                                                                                                            | 0.664 | %     | -40°C ≤TA ≤+85°C                  | VDD = 4.5 to 5.5V |  |  |  |  |  |  |

|              |                | —       | 0.362                                                                                                                                                            | 0.664 | %     | -40°C ≤TA ≤+125°C                 | VDD = 4.5 to 5.5V |  |  |  |  |  |  |

|              | x16 PLL        | —       | 0.67                                                                                                                                                             | 0.92  | %     | -40°C ≤TA ≤+85°C VDD = 3.0 to 3.  |                   |  |  |  |  |  |  |

|              |                |         | 0.632                                                                                                                                                            | 0.956 | %     | -40°C ≤TA ≤+85°C VDD = 4.5 to 5.5 |                   |  |  |  |  |  |  |

|              |                | —       | 0.632                                                                                                                                                            | 0.956 | %     | -40°C ≤TA ≤+125°C                 | VDD = 4.5 to 5.5V |  |  |  |  |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

| Clock<br>Oscillator<br>Mode | Fosc<br>(MHz) <sup>(1)</sup> | Τ <b>C</b> Υ (μsec) <sup>(2)</sup> | MIPS <sup>(3)</sup><br>w/o PLL | MIPS <sup>(3)</sup><br>w PLL x4 | MIPS <sup>(3)</sup><br>w PLL x8 | MIPS <sup>(3)</sup><br>w PLL x16 |

|-----------------------------|------------------------------|------------------------------------|--------------------------------|---------------------------------|---------------------------------|----------------------------------|

| EC                          | 0.200                        | 20.0                               | 0.05                           | —                               | —                               | —                                |

|                             | 4                            | 1.0                                | 1.0                            | 4.0                             | 8.0                             | 16.0                             |

|                             | 10                           | 0.4                                | 2.5                            | 10.0                            | 20.0                            | —                                |

|                             | 25                           | 0.16                               | 6.25                           | —                               | —                               | —                                |

| XT                          | 4                            | 1.0                                | 1.0                            | 4.0                             | 8.0                             | 16.0                             |

|                             | 10                           | 0.4                                | 2.5                            | 10.0                            | 20.0                            | —                                |

#### TABLE 20-17: INTERNAL CLOCK TIMING EXAMPLES

Note 1: Assumption: Oscillator Postscaler is divide by 1.

**2:** Instruction Execution Cycle Time: TCY = 1/MIPS.

**3:** Instruction Execution Frequency: MIPS = (Fosc \* PLLx)/4 [since there are 4 Q clocks per instruction cycle].

### TABLE 20-18: AC CHARACTERISTICS: INTERNAL FRC ACCURACY

| AC CHARACTERISTICS |                                                             | Standard Operating Conditions: 2.5V to 5.5V   (unless otherwise stated)   Operating temperature -40°C ≤TA ≤+85°C for Industrial   -40°C ≤TA ≤+125°C for Extended |     |       |       |                   |                |  |  |  |

|--------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-------|-------------------|----------------|--|--|--|

| Param<br>No.       | Characteristic                                              | Min                                                                                                                                                              | Тур | Max   | Units | Conditions        |                |  |  |  |

|                    | Internal FRC Accuracy @ FRC Freq. = 7.37 MHz <sup>(1)</sup> |                                                                                                                                                                  |     |       |       |                   |                |  |  |  |

| OS63               | FRC                                                         | —                                                                                                                                                                | —   | ±2.00 | %     | -40°C ≤TA ≤+85°C  | VDD = 3.0-5.5V |  |  |  |

|                    |                                                             | _                                                                                                                                                                |     | ±5.00 | %     | -40°C ≤TA ≤+125°C | VDD = 3.0-5.5V |  |  |  |

**Note 1:** Frequency calibrated at 7.372 MHz ±2%, 25°C and 5V. TUN bits (OSCCON<3:0>) can be used to compensate for temperature drift.

#### TABLE 20-19: AC CHARACTERISTICS: INTERNAL LPRC ACCURACY

| AC CHARACTERISTICS |                                       | Standard Operating Conditions: 2.5V to 5.5V   (unless otherwise stated)   Operating temperature   -40°C ≤TA ≤+85°C for Industrial   -40°C ≤TA ≤+125°C for Extended |     |     |       |                  |  |  |

|--------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|------------------|--|--|

| Param<br>No.       | Characteristic                        | Min                                                                                                                                                                | Тур | Max | Units | Conditions       |  |  |

|                    | LPRC @ Freq. = 512 kHz <sup>(1)</sup> |                                                                                                                                                                    |     |     |       |                  |  |  |

| OS65A              |                                       | -50                                                                                                                                                                | —   | +50 | %     | VDD = 5.0V, ±10% |  |  |

| OS65B              |                                       | -60                                                                                                                                                                | _   | +60 | %     | VDD = 3.3V, ±10% |  |  |

| OS65C              |                                       | -70                                                                                                                                                                | _   | +70 | %     | VDD = 2.5V       |  |  |

Note 1: Change of LPRC frequency as VDD changes.

## TABLE 20-33: I<sup>2</sup>C<sup>™</sup> BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| AC CHA       | RACTER  | ISTICS                         |                           | Standard Operating Conditions: 2.5V to 5.5V   (unless otherwise stated)   Operating temperature -40°C ≤TA ≤+85°C for Industrial   -40°C ≤TA ≤+125°C for Extended |      |       |                        |  |  |

|--------------|---------|--------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------------------|--|--|

| Param<br>No. | Symbol  | Charac                         | teristic                  | Min <sup>(1)</sup>                                                                                                                                               | Max  | Units | Conditions             |  |  |

| IM10         | TLO:SCL | Clock Low Time                 | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                  |      | μs    |                        |  |  |

|              |         |                                | 400 kHz mode              | TCY/2 (BRG + 1)                                                                                                                                                  | —    | μs    |                        |  |  |

|              |         |                                | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                  | —    | μs    |                        |  |  |

| IM11         | THI:SCL | Clock High Time                | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                  | —    | μs    |                        |  |  |

|              |         |                                | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                  | —    | μs    |                        |  |  |

|              |         |                                | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                  | _    | μs    |                        |  |  |

| IM20         | TF:SCL  | SDA and SCL                    | 100 kHz mode              | —                                                                                                                                                                | 300  | ns    | CB is specified to be  |  |  |

|              |         | Fall Time                      | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                      | 300  | ns    | from 10 to 400 pF      |  |  |

|              |         |                                | 1 MHz mode <sup>(2)</sup> | _                                                                                                                                                                | 100  | ns    |                        |  |  |

| IM21         | TR:SCL  | SDA and SCL<br>Rise Time       | 100 kHz mode              | _                                                                                                                                                                | 1000 | ns    | CB is specified to be  |  |  |

|              |         |                                | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                      | 300  | ns    | from 10 to 400 pF      |  |  |

|              |         |                                | 1 MHz mode <sup>(2)</sup> | _                                                                                                                                                                | 300  | ns    |                        |  |  |

| IM25         | TSU:DAT | Data Input<br>Setup Time       | 100 kHz mode              | 250                                                                                                                                                              | —    | ns    |                        |  |  |

|              |         |                                | 400 kHz mode              | 100                                                                                                                                                              | —    | ns    |                        |  |  |

|              |         |                                | 1 MHz mode <sup>(2)</sup> | —                                                                                                                                                                | _    | ns    |                        |  |  |

| IM26         | THD:DAT | Data Input<br>Hold Time        | 100 kHz mode              | 0                                                                                                                                                                | —    | ns    |                        |  |  |

|              |         |                                | 400 kHz mode              | 0                                                                                                                                                                | 0.9  | μs    |                        |  |  |

|              |         |                                | 1 MHz mode <sup>(2)</sup> | —                                                                                                                                                                | _    | ns    |                        |  |  |

| IM30         | TSU:STA | Start Condition<br>Setup Time  | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                  | —    | μs    | Only relevant for      |  |  |

|              |         |                                | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                  | —    | μs    | Repeated Start         |  |  |

|              |         |                                | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                  | _    | μs    | condition              |  |  |

| IM31         | THD:STA | Start Condition<br>Hold Time   | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                  | —    | μs    | After this period the  |  |  |

|              |         |                                | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                  | —    | μs    | first clock pulse is   |  |  |

|              |         |                                | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                  | _    | μs    | generated              |  |  |

| IM33         | Tsu:sto | O Stop Condition<br>Setup Time | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                  | _    | μs    |                        |  |  |

|              |         |                                | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                  | —    | μs    |                        |  |  |

|              |         |                                | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                  | _    | μs    |                        |  |  |

| IM34         | THD:STO | Stop Condition                 | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                  | _    | ns    |                        |  |  |

|              |         | Hold Time                      | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                  | _    | ns    |                        |  |  |

|              |         |                                | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                  | _    | ns    |                        |  |  |

| IM40         | TAA:SCL | Output Valid<br>From Clock     | 100 kHz mode              | —                                                                                                                                                                | 3500 | ns    |                        |  |  |

|              |         |                                | 400 kHz mode              | —                                                                                                                                                                | 1000 | ns    |                        |  |  |

|              |         |                                | 1 MHz mode <sup>(2)</sup> | _                                                                                                                                                                |      | ns    |                        |  |  |

| IM45         | TBF:SDA | Bus Free Time                  | 100 kHz mode              | 4.7                                                                                                                                                              |      | μs    | Time the bus must be   |  |  |

|              |         |                                | 400 kHz mode              | 1.3                                                                                                                                                              |      | μs    | free before a new      |  |  |

|              |         |                                | 1 MHz mode <sup>(2)</sup> | _                                                                                                                                                                |      | μs    | transmission can start |  |  |

| IM50         | Св      | Bus Capacitive L               |                           |                                                                                                                                                                  | 400  | pF    |                        |  |  |

Note 1: BRG is the value of the I<sup>2</sup>C Baud Rate Generator. Refer to Section 21. "Inter-Integrated Circuit™ (I<sup>2</sup>C)" (DS70068) in the *dsPIC30F Family Reference Manual* (DS70046).

**2:** Maximum pin capacitance = 10 pF for all  $I^2C^{TM}$  pins (for 1 MHz mode only).

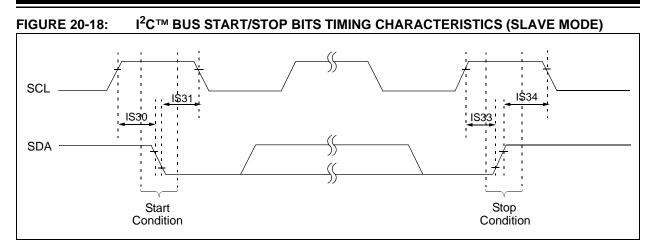

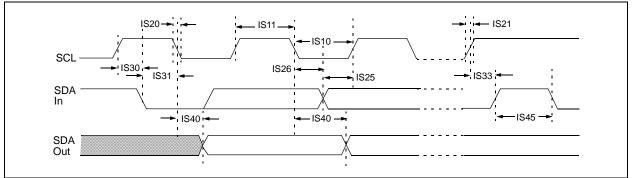

## TABLE 20-34: I<sup>2</sup>C<sup>™</sup> BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

| AC CHARACTERISTICS |         |                          | Standard Operating Conditions: 2.5V to 5.5V   (unless otherwise stated)   Operating temperature -40°C ≤TA ≤+85°C for Industrial   -40°C ≤TA ≤+125°C for Extended |             |      |       |                                             |  |  |

|--------------------|---------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|-------|---------------------------------------------|--|--|

| Param<br>No.       | Symbol  | Charac                   | teristic                                                                                                                                                         | Min         |      | Units | Conditions                                  |  |  |

| IS10               | TLO:SCL | Clock Low Time           | 100 kHz mode                                                                                                                                                     | 4.7         | _    | μs    | Device must operate at a minimum of 1.5 MHz |  |  |

|                    |         |                          | 400 kHz mode                                                                                                                                                     | 1.3         | —    | μs    | Device must operate at a minimum of 10 MHz. |  |  |

|                    |         |                          | 1 MHz mode <sup>(1)</sup>                                                                                                                                        | 0.5         | —    | μs    |                                             |  |  |

| IS11               | THI:SCL | Clock High Time          | 100 kHz mode                                                                                                                                                     | 4.0         | —    | μs    | Device must operate at a minimum of 1.5 MHz |  |  |

|                    |         |                          | 400 kHz mode                                                                                                                                                     | 0.6         | _    | μs    | Device must operate at a minimum of 10 MHz  |  |  |

|                    |         |                          | 1 MHz mode <sup>(1)</sup>                                                                                                                                        | 0.5         | —    | μs    |                                             |  |  |

| IS20               | TF:SCL  | SDA and SCL<br>Fall Time | 100 kHz mode                                                                                                                                                     | —           | 300  | ns    | CB is specified to be from                  |  |  |

|                    |         |                          | 400 kHz mode                                                                                                                                                     | 20 + 0.1 Св | 300  | ns    | 10 to 400 pF                                |  |  |

|                    |         |                          | 1 MHz mode <sup>(1)</sup>                                                                                                                                        | —           | 100  | ns    | ]                                           |  |  |

| IS21               | TR:SCL  | SDA and SCL<br>Rise Time | 100 kHz mode                                                                                                                                                     | —           | 1000 | ns    | CB is specified to be from                  |  |  |

|                    |         |                          | 400 kHz mode                                                                                                                                                     | 20 + 0.1 Св | 300  | ns    | 10 to 400 pF                                |  |  |

|                    |         |                          | 1 MHz mode <sup>(1)</sup>                                                                                                                                        | —           | 300  | ns    |                                             |  |  |

**Note 1:** Maximum pin capacitance = 10 pF for all  $I^2C^{TM}$  pins (for 1 MHz mode only).

| AC CHARACTERISTICS |         |                               | Standard Operating Conditions: 2.5V to 5.5V   (unless otherwise stated)   Operating temperature -40°C ≤TA ≤+85°C for Industrial   -40°C ≤TA ≤+125°C for Extended |      |      |       |                                                      |  |  |

|--------------------|---------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------------------------------------------------|--|--|

| Param<br>No.       | Symbol  | Charac                        | teristic                                                                                                                                                         | Min  | Max  | Units | Conditions                                           |  |  |

| IS25               | TSU:DAT | Data Input<br>Setup Time      | 100 kHz mode                                                                                                                                                     | 250  | _    | ns    |                                                      |  |  |

|                    |         |                               | 400 kHz mode                                                                                                                                                     | 100  | —    | ns    |                                                      |  |  |

|                    |         |                               | 1 MHz mode <sup>(1)</sup>                                                                                                                                        | 100  | _    | ns    |                                                      |  |  |

| IS26               | THD:DAT | Data Input                    | 100 kHz mode                                                                                                                                                     | 0    | _    | ns    |                                                      |  |  |

|                    |         | Hold Time                     | 400 kHz mode                                                                                                                                                     | 0    | 0.9  | μs    |                                                      |  |  |

|                    |         |                               | 1 MHz mode <sup>(1)</sup>                                                                                                                                        | 0    | 0.3  | μs    |                                                      |  |  |

| IS30               | TSU:STA | Start Condition<br>Setup Time | 100 kHz mode                                                                                                                                                     | 4.7  |      | μs    | Only relevant for Repeate<br>Start condition         |  |  |

|                    |         |                               | 400 kHz mode                                                                                                                                                     | 0.6  |      | μs    |                                                      |  |  |

|                    |         |                               | 1 MHz mode <sup>(1)</sup>                                                                                                                                        | 0.25 | _    | μs    |                                                      |  |  |

| IS31               | THD:STA | Start Condition<br>Hold Time  | 100 kHz mode                                                                                                                                                     | 4.0  |      | μs    | After this period the first clock pulse is generated |  |  |

|                    |         |                               | 400 kHz mode                                                                                                                                                     | 0.6  |      | μs    |                                                      |  |  |

|                    |         |                               | 1 MHz mode <sup>(1)</sup>                                                                                                                                        | 0.25 | _    | μs    |                                                      |  |  |

| IS33               | Τςυ:ςτο | Stop Condition<br>Setup Time  | 100 kHz mode                                                                                                                                                     | 4.7  |      | μs    |                                                      |  |  |

|                    |         |                               | 400 kHz mode                                                                                                                                                     | 0.6  |      | μs    |                                                      |  |  |

|                    |         |                               | 1 MHz mode <sup>(1)</sup>                                                                                                                                        | 0.6  | _    | μs    |                                                      |  |  |

| IS34               | THD:STO | Stop Condition<br>Hold Time   | 100 kHz mode                                                                                                                                                     | 4000 | _    | ns    |                                                      |  |  |

|                    |         |                               | 400 kHz mode                                                                                                                                                     | 600  | _    | ns    |                                                      |  |  |

|                    |         |                               | 1 MHz mode <sup>(1)</sup>                                                                                                                                        | 250  |      | ns    |                                                      |  |  |

| IS40               | TAA:SCL | Output Valid<br>From Clock    | 100 kHz mode                                                                                                                                                     | 0    | 3500 | ns    |                                                      |  |  |

|                    |         |                               | 400 kHz mode                                                                                                                                                     | 0    | 1000 | ns    |                                                      |  |  |

|                    |         |                               | 1 MHz mode <sup>(1)</sup>                                                                                                                                        | 0    | 350  | ns    | 1                                                    |  |  |