Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | dsPIC                                                                          |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 30 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                          |

| Number of I/O              | 20                                                                             |

| Program Memory Size        | 12KB (4K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 1K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                    |

| Data Converters            | A/D 10x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 28-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f2012t-30i-so |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U S A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2010, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

#### ISBN: 978-1-60932-631-9

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL00® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mnufacture of development systems is ISO 9001:2000 certified.

NOTES:

#### 5.6 **Programming Operations**

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. A programming operation is nominally 2 msec in duration and the processor stalls (waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### 5.6.1 PROGRAMMING ALGORITHM FOR PROGRAM FLASH

The user can erase or program one row of program Flash memory at a time. The general process is:

- 1. Read one row of program Flash (32 instruction words) and store into data RAM as a data "image".

- 2. Update the data image with the desired new data.

- 3. Erase program Flash row.

- a) Set up NVMCON register for multi-word, program Flash, erase, and set WREN bit.

- b) Write address of row to be erased into NVMADRU/NVMDR.

- c) Write 0x55 to NVMKEY.

- d) Write 0xAA to NVMKEY.

- e) Set the WR bit. This begins erase cycle.

- f) CPU stalls for the duration of the erase cycle.

- g) The WR bit is cleared when erase cycle ends.

#### EXAMPLE 5-1: ERASING A ROW OF PROGRAM MEMORY

| 4. | Write  | 32 instruction words of data from data |  |

|----|--------|----------------------------------------|--|

|    | RAM    | "image" into the program Flash write   |  |

|    | latche | S.                                     |  |

- 5. Program 32 instruction words into program Flash.

- Set up NVMCON register for multi-word, program Flash, program, and set WREN bit.

- b) Write 0x55 to NVMKEY.

- c) Write 0xAA to NVMKEY.

- d) Set the WR bit. This begins program cycle.

- e) CPU stalls for duration of the program cycle.

- f) The WR bit is cleared by the hardware when program cycle ends.

- 6. Repeat steps 1 through 5 as needed to program desired amount of program Flash memory.

## 5.6.2 ERASING A ROW OF PROGRAM MEMORY

Example 5-1 shows a code sequence that can be used to erase a row (32 instructions) of program memory.

| p   | program memor | ry selected, and writes enab        | led |                                           |

|-----|---------------|-------------------------------------|-----|-------------------------------------------|

|     | MOV           | #0x4041,W0                          | ;   |                                           |

|     | MOV           | W0,NVMCON                           | ;   | Init NVMCON SFR                           |

| ; I | Init pointer  | to row to be ERASED                 |     |                                           |

|     | MOV           | <pre>#tblpage(PROG_ADDR),W0</pre>   | ;   |                                           |

|     | MOV           | W0 <sub>,</sub> NVMADRU             | ;   | Initialize PM Page Boundary SFR           |

|     | MOV           | <pre>#tbloffset(PROG_ADDR),W0</pre> | ;   | Intialize in-page EA[15:0] pointer        |

|     | MOV           | W0, NVMADR                          | ;   | Initialize NVMADR SFR                     |

|     | DISI          | #5                                  | ;   | Block all interrupts with priority <7 for |

|     |               |                                     | ;   | next 5 instructions                       |

|     | MOV           | #0x55,W0                            |     |                                           |

|     | MOV           | W0,NVMKEY                           | ;   | Write the 0x55 key                        |

|     | MOV           | #0xAA,W1                            | ;   |                                           |

|     | MOV           | W1,NVMKEY                           | ;   | Write the OxAA key                        |

|     | BSET          | NVMCON, #WR                         | ;   | Start the erase sequence                  |

|     | NOP           |                                     | ;   | Insert two NOPs after the erase           |

|     | NOP           |                                     | ;   | command is asserted                       |

### TABLE 7-5: PORTD REGISTER MAP FOR dsPIC30F2012/3013

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset State         |

|-------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|---------------------|

| TRISD       | 02D2  | —      | —      | —      |        |        | —      | TRISD9 | TRISD8 |       | —     |       | —     | —     | —     | _     | -     | 0000 0011 0000 0000 |

| PORTD       | 02D4  | _      | _      | _      | -      | _      | _      | RD9    | RD8    | _     | _     |       | -     | _     | _     | _     | _     | 0000 0000 0000 0000 |

| LATD        | 02D6  | —      | —      | —      | —      | _      |        | LATD9  | LATD8  |       | _     |       | _     | _     |       | _     | _     | 0000 0000 0000 0000 |

Legend: — = unimplemented bit, read as '0'

#### TABLE 7-6: PORTF REGISTER MAP FOR dsPIC30F2012/3013

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 | Reset State         |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|--------|--------|--------|--------|--------|-------|-------|---------------------|

| TRISF       | 02DE  | —      | —      | _      | _      | —      | —      | —     | _     | _     | TRISF6 | TRISF5 | TRISF4 | TRISF3 | TRISF2 | _     | -     | 0000 0000 0111 1100 |

| PORTF       | 02E0  | _      | _      | -      | _      | _      | _      |       | _     | _     | RF6    | RF5    | RF4    | RF3    | RF2    | _     | _     | 0000 0000 0000 0000 |

| LATF        | 02E2  | -      | _      | _      | -      | _      | —      | _     |       |       | LATF6  | LATF5  | LATF4  | LATF3  | LATF2  |       |       | 0000 0000 0000 0000 |

Legend: — = unimplemented bit, read as '0'

Note: The dsPIC30F2011/3012 devices do not have TRISF, PORTF, or LATF.

| TABLE       | 8-2: | dsP    | PIC30F | 2011/2    | 012/30 | 12 INT | ERRU   | PT COI     | NTROL  | LER R  | EGIS  | ER N    | IAP     |         |             |             |        |                     |

|-------------|------|--------|--------|-----------|--------|--------|--------|------------|--------|--------|-------|---------|---------|---------|-------------|-------------|--------|---------------------|

| SFR<br>Name | ADR  | Bit 15 | Bit 14 | Bit 13    | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8  | Bit 7  | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2       | Bit 1       | Bit 0  | Reset State         |

| INTCON1     | 0080 | NSTDIS | _      | _         | _      | _      | OVATE  | OVBTE      | COVTE  | _      |       | _       | MATHERR | ADDRERR | STKERR      | OSCFAIL     | _      | 0000 0000 0000 0000 |

| INTCON2     | 0082 | ALTIVT | DISI   |           | _      | I      | _      |            |        | _      |       | -       |         | _       | INT2EP      | INT1EP      | INT0EP | 0000 0000 0000 0000 |

| IFS0        | 0084 | CNIF   | MI2CIF | SI2CIF    | NVMIF  | ADIF   | U1TXIF | U1RXIF     | SPI1IF | T3IF   | T2IF  | OC2IF   | IC2IF   | T1IF    | OC1IF       | IC1IF       | INTOIF | 0000 0000 0000 0000 |

| IFS1        | 0086 | _      | _      |           | _      | I      | _      |            |        | INT2IF |       | _       |         | _       | _           | _           | INT1IF | 0000 0000 0000 0000 |

| IFS2        | 0088 | _      | _      |           | _      |        | LVDIF  |            |        | _      |       | _       |         | _       | _           | _           | _      | 0000 0000 0000 0000 |

| IEC0        | 008C | CNIE   | MI2CIE | SI2CIE    | NVMIE  | ADIE   | U1TXIE | U1RXIE     | SPI1IE | T3IE   | T2IE  | OC2IE   | IC2IE   | T1IE    | OC1IE       | IC1IE       | INTOIE | 0000 0000 0000 0000 |

| IEC1        | 008E |        | _      |           |        |        | _      |            |        | INT2IE |       | _       |         | _       | _           | _           | INT1IE | 0000 0000 0000 0000 |

| IEC2        | 0090 |        |        |           |        |        | LVDIE  |            |        | _      |       | _       |         | —       | _           | —           |        | 0000 0000 0000 0000 |

| IPC0        | 0094 | _      | -      | T1IP<2:0> | •      |        | 0      | DC1IP<2:0  | >      | —      |       | IC1IP<  | 2:0>    | _       | INT0IP<2:0> |             |        | 0100 0100 0100 0100 |

| IPC1        | 0096 | _      | 1      | [31P<2:0  | >      | I      |        | T2IP<2:0>  |        | _      |       | OC2IP<  | 2:0>    | _       |             | IC2IP<2:0>  |        | 0100 0100 0100 0100 |

| IPC2        | 0098 | _      | A      | ADIP<2:0> | >      | _      | U      | 1TXIP<2:0  | )>     | —      |       | U1RXIP  | <2:0>   | _       | 5           | SPI1IP<2:0; | >      | 0100 0100 0100 0100 |

| IPC3        | 009A | _      | C      | CNIP<2:0  | >      | I      | N      | 112CIP<2:0 | )>     | _      |       | SI2CIP< | 2:0>    | _       | ١           | NVMIP<2:0   | >      | 0100 0100 0100 0100 |

| IPC4        | 009C | _      | _      |           | _      | I      | _      |            |        | _      |       | _       |         | _       |             | NT1IP<2:0>  | >      | 0000 0000 0000 0100 |

| IPC5        | 009E | _      | IN     | T2IP<2:0  | >      |        | _      |            |        | _      |       | _       |         | _       | _           | _           | -      | 0100 0000 0000 0000 |

| IPC6        | 00A0 |        | _      |           |        |        | _      |            |        | _      | 1     | 0       | 0       | —       | 1           | 0           | 0      | 0000 0000 0100 0100 |

| IPC7        | 00A2 |        | -      | I         | -      |        | _      |            |        | -      |       | _       |         | —       | _           | _           | -      | 0000 0000 0000 0000 |

| IPC8        | 00A4 |        | _      | -         | _      |        | _      |            |        | _      | -     | -       |         | _       | _           | _           |        | 0000 0000 0000 0000 |

| IPC9        | 00A6 |        | -      | I         | -      | I      | _      | _          |        | -      |       | _       |         | _       | _           | _           | _      | 0000 0000 0000 0000 |

| IPC10       | 00A8 |        | _      | _         | _      |        | L      | VDIP<2:0   | >      | _      | _     | -       |         | —       | _           | _           | —      | 0000 0100 0000 0000 |

#### TABLE 8-2. dePIC30E2011/2012/3012 INTERRUPT CONTROLLER REGISTER MAP

**Legend:** u = uninitialized bit; — = unimplemented bit, read as '0'

Note: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

NOTES:

#### TABLE 13-1: SPI1 REGISTER MAP

| SFR<br>Name | Addr.                            | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3               | Bit 2 | Bit 1  | Bit 0  | Reset State         |

|-------------|----------------------------------|--------|--------|---------|--------|--------|--------|-------|-------|-------|--------|-------|-------|---------------------|-------|--------|--------|---------------------|

| SPI1STAT    | 0220                             | SPIEN  | —      | SPISIDL | —      | —      | —      | —     | _     | _     | SPIROV | _     | —     | _                   | —     | SPITBF | SPIRBF | 0000 0000 0000 0000 |

| SPI1CON     | 0222                             | _      | FRMEN  | SPIFSD  | _      | DISSDO | MODE16 | SMP   | CKE   | SSEN  | CKP    | MSTEN | SPRE2 | SPRE1               | SPRE0 | PPRE1  | PPRE0  | 0000 0000 0000 0000 |

| SPI1BUF     | 0224 Transmit and Receive Buffer |        |        |         |        |        |        |       |       |       |        |       |       | 0000 0000 0000 0000 |       |        |        |                     |

Legend: — = unimplemented bit, read as '0'

Note: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

NOTES:

### 17.2.7 FAIL-SAFE CLOCK MONITOR

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate even in the event of an oscillator failure. The FSCM function is enabled by appropriately programming the FCKSM Configuration bits (clock switch and monitor selection bits) in the FOSC Device Configuration register. If the FSCM function is enabled, the LPRC internal oscillator will run at all times (except during Sleep mode) and will not be subject to control by the SWDTEN bit.

In the event of an oscillator failure, the FSCM will generate a clock failure trap event and will switch the system clock over to the FRC oscillator. The user will then have the option to either attempt to restart the oscillator or execute a controlled shutdown. The user may decide to treat the trap as a warm Reset by simply loading the Reset address into the oscillator fail trap vector. In this event, the CF (Clock Fail) bit (OSCCON<3>) is also set whenever a clock failure is recognized.

In the event of a clock failure, the WDT is unaffected and continues to run on the LPRC clock.

If the oscillator has a very slow start-up time coming out of POR, BOR or Sleep, it is possible that the PWRT timer will expire before the oscillator has started. In such cases, the FSCM will be activated and the FSCM will initiate a clock failure trap, and the COSC<2:0> bits are loaded with FRC oscillator selection. This will effectively shut-off the original oscillator that was trying to start.

The user may detect this situation and restart the oscillator in the clock fail trap ISR.

Upon a clock failure detection, the FSCM module will initiate a clock switch to the FRC oscillator as follows:

- 1. The COSC bits (OSCCON<14:12>) are loaded with the FRC oscillator selection value.

- 2. CF bit is set (OSCCON<3>).

- 3. OSWEN control bit (OSCCON<0>) is cleared.

For the purpose of clock switching, the clock sources are sectioned into four groups:

- Primary (with or without PLL)

- Secondary

- Internal FRC

- Internal LPRC

The user can switch between these functional groups but cannot switch between options within a group. If the primary group is selected, then the choice within the group is always determined by the FPR<4:0> Configuration bits. The OSCCON register holds the Control and Status bits related to clock switching.

- COSC<2:0>: Read-only bits always reflect the current oscillator group in effect.

- NOSC<2:0>: Control bits which are written to indicate the new oscillator group of choice.

- On POR and BOR, COSC<2:0> and NOSC<2:0> are both loaded with the Configuration bit values FOS<2:0>.

- LOCK: The LOCK bit indicates a PLL lock.

- CF: Read-only bit indicating if a clock fail detect has occurred.

- OSWEN: Control bit changes from a '0' to a '1' when a clock transition sequence is initiated. Clearing the OSWEN control bit will abort a clock transition in progress (used for hang-up situations).

If Configuration bits FCKSM<1:0> = 1x, then the clock switching and Fail-Safe Clock monitoring functions are disabled. This is the default Configuration bit setting.

If clock switching is disabled, then the FOS<2:0> and FPR<4:0> bits directly control the oscillator selection and the COSC<2:0> bits do not control the clock selection. However, these bits will reflect the clock source selection.

**Note:** The application should not attempt to switch to a clock of frequency lower than 100 kHz when the Fail-Safe Clock Monitor is enabled. If such clock switching is performed, the device may generate an oscillator fail trap and switch to the Fast RC oscillator.

#### 17.2.8 PROTECTION AGAINST ACCIDENTAL WRITES TO OSCCON

A write to the OSCCON register is intentionally made difficult because it controls clock switching and clock scaling.

To write to the OSCCON low byte, the following code sequence must be executed without any other instructions in between:

Byte Write 0x46 to OSCCON low Byte Write 0x57 to OSCCON low

*Byte write is allowed for one instruction cycle.* Write the desired value or use bit manipulation instruction.

To write to the OSCCON high byte, the following instructions must be executed without any other instructions in between:

Byte Write 0x78 to OSCCON high Byte Write 0x9A to OSCCON high

*Byte write is allowed for one instruction cycle.* Write the desired value or use bit manipulation instruction.

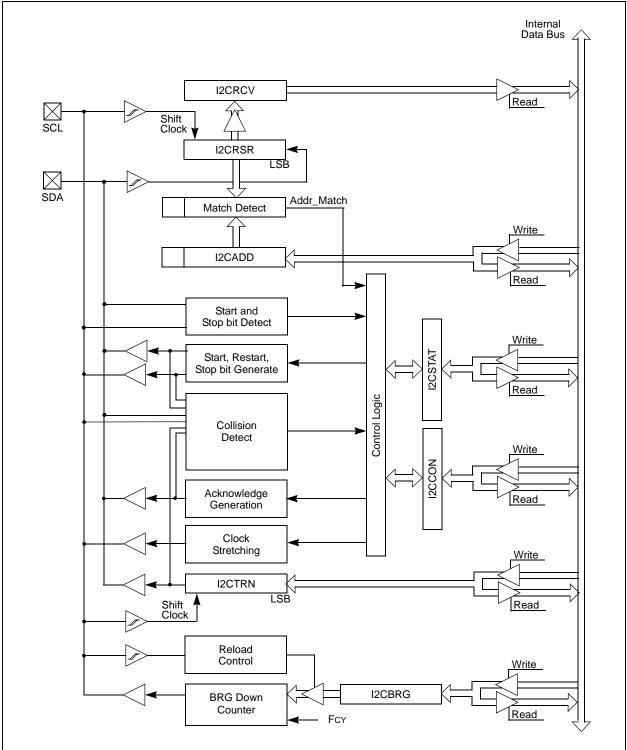

### 17.3 Reset

The dsPIC30F2011/2012/3012/3013 devices differentiate between various kinds of Reset:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during Sleep

- d) Watchdog Timer (WDT) Reset (during normal operation)

- e) Programmable Brown-out Reset (BOR)

- f) RESET Instruction

- g) Reset caused by trap lockup (TRAPR)

- Reset caused by illegal opcode or by using an uninitialized W register as an address pointer (IOPUWR)

Different registers are affected in different ways by various Reset conditions. Most registers are not affected by a WDT wake-up since this is viewed as the resumption of normal operation. Status bits from the RCON register are set or cleared differently in different Reset situations, as indicated in Table 17-5. These bits are used in software to determine the nature of the Reset.

A block diagram of the On-Chip Reset Circuit is shown in Figure 17-2.

A MCLR noise filter is provided in the MCLR Reset path. The filter detects and ignores small pulses.

Internally generated Resets do not drive MCLR pin low.

### 17.3.1 POR: POWER-ON RESET

A power-on event will generate an internal POR pulse when a VDD rise is detected. The Reset pulse will occur at the POR circuit threshold voltage (VPOR) which is nominally 1.85V. The device supply voltage characteristics must meet specified starting voltage and rise rate requirements. The POR pulse will reset a POR timer and place the device in the Reset state. The POR also selects the device clock source identified by the oscillator configuration fuses.

The POR circuit inserts a small delay, TPOR, which is nominally 10  $\mu$ s and ensures that the device bias circuits are stable. Furthermore, a user selected power-up time-out (TPWRT) is applied. The TPWRT parameter is based on device Configuration bits and can be 0 ms (no delay), 4 ms, 16 ms or 64 ms. The total delay is at device power-<u>up</u>, <u>TPOR</u> + <u>TPWRT</u>. When these delays have expired, SYSRST will be negated on the next leading edge of the Q1 clock and the PC will jump to the Reset vector.

The timing for the SYSRST signal is shown in Figure 17-3 through Figure 17-5.

#### TABLE 17-7: SYSTEM INTEGRATION REGISTER MAP

| SFR<br>Name | Address | Bit 15 | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9    | Bit 8 | Bit 7 | Bit 6               | Bit 5  | Bit 4 | Bit 3  | Bit 2 | Bit 1   | Bit 0 | Reset State         |

|-------------|---------|--------|--------|----------|--------|--------|--------|----------|-------|-------|---------------------|--------|-------|--------|-------|---------|-------|---------------------|

| RCON        | 0740    | TRAPR  | IOPUWR | BGST     | LVDEN  |        | LVDL   | <3:0>    |       | EXTR  | SWR                 | SWDTEN | WDTO  | SLEEP  | IDLE  | BOR     | POR   | (Note 1)            |

| OSCCON      | 0742    | _      | CC     | OSC<2:0: | >      | —      | Ν      | IOSC<2:0 | )>    | POS   | Г<1:0>              | LOCK   | _     | CF     | _     | LPOSCEN | OSWEN | (Note 2)            |

| OSCTUN      | 0744    | _      | _      | _        | _      | —      | -      |          |       |       | _                   | _      | _     | TUN3   | TUN2  | TUN1    | TUN0  | (Note 2)            |

| PMD1        | 0770    | _      | _      | T3MD     | T2MD   | T1MD   | -      |          |       | I2CMD | U2MD <sup>(3)</sup> | U1MD   | _     | SPI1MD | _     | _       | ADCMD | 0000 0000 0000 0000 |

| PMD2        | 0772    | _      | _      | _        | _      | —      | -      | IC2MD    | IC1MD |       | _                   | _      | _     | _      | _     | OC2MD   | OC1MD | 0000 0000 0000 0000 |

Legend: — = unimplemented bit, read as '0'

Note 1: Reset state depends on type of reset.

2: Reset state depends on Configuration bits.

3: Only available on dsPIC30F3013 devices.

#### TABLE 17-8: DEVICE CONFIGURATION REGISTER MAP

| Name    | Address | Bit 15 | Bit 14 | Bit 13 | Bit 12             | Bit 11 | Bit 10                | Bit 9               | Bit 8                   | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2                   | Bit 1             | Bit 0  |

|---------|---------|--------|--------|--------|--------------------|--------|-----------------------|---------------------|-------------------------|-------|-------|-------|--------|-------|-------------------------|-------------------|--------|

| FOSC    | F80000  | FCKSN  | 1<1:0> | —      | —                  | —      |                       | FOS<2:0>            |                         |       |       |       |        |       | FPR<4:0>                |                   |        |

| FWDT    | F80002  | FWDTEN | _      | _      | _                  | _      | _                     | _                   | _                       | _     | _     | FWPS  | A<1:0> |       | FWPSB                   | <3:0>             |        |

| FBORPOR | F80004  | MCLREN | _      | _      | _                  | _      | PWMPIN <sup>(1)</sup> | HPOL <sup>(1)</sup> | LPOL <sup>(1)</sup>     | BOREN | _     | BOR\  | /<1:0> | _     | _                       | FPWR              | Г<1:0> |

| FBS     | F80006  | _      | _      | Reser  | ved <sup>(2)</sup> | _      | _                     | _                   | Reserved <sup>(2)</sup> | _     | _     | _     | _      |       | Reserv                  | ed <sup>(2)</sup> |        |

| FSS     | F80008  | _      | _      | Reser  | ved <sup>(2)</sup> | _      | _                     | Rese                | erved <sup>(2)</sup>    | _     | _     | _     | _      |       | Reserv                  | ed <sup>(2)</sup> |        |

| FGS     | F8000A  | _      | _      | _      | _                  | _      | _                     | _                   | _                       | _     | _     | _     | _      | _     | Reserved <sup>(3)</sup> | GCP               | GWRP   |

| FICD    | F8000C  | BKBUG  | COE    | —      | —                  | _      | —                     | —                   | —                       | _     | _     | _     |        |       | —                       | ICS<              | 1:0>   |

Legend: — = unimplemented bit, read as '0'

Note 1: These bits are reserved (read as '1' and must be programmed as '1').

2: Reserved bits read as '1' and must be programmed as '1'.

3: The FGS<2> bit is a read-only copy of the GCP bit (FGS<1>).

### 18.0 INSTRUCTION SET SUMMARY

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "dsPIC30F Programmer's Reference Manual" (DS70030).

The dsPIC30F instruction set adds many enhancements to the previous PIC<sup>®</sup> MCU instruction sets, while maintaining an easy migration from PIC MCU instruction sets.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word divided into an 8-bit opcode which specifies the instruction type, and one or more operands which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into five basic categories:

- Word or byte-oriented operations

- Bit-oriented operations

- · Literal operations

- DSP operations

- · Control operations

Table 18-1showsthegeneralsymbolsusedindescribing the instructions.

The dsPIC30F instruction set summary in Table 18-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand which is typically a register 'Wb' without any address modifier

- The second source operand which is typically a register 'Ws' with or without an address modifier

- The destination of the result which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- The file register specified by the value 'f'

- The destination, which could either be the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement may use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by the value of 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand which is a register 'Wb' without any address modifier

- The second source operand which is a literal value

- The destination of the result (only if not the same as the first source operand) which is typically a register 'Wd' with or without an address modifier

The MAC class of DSP instructions may use some of the following operands:

- The accumulator (A or B) to be used (required operand)

- The W registers to be used as the two operands

- The X and Y address space prefetch operations

- The X and Y address space prefetch destinations

- The accumulator write-back destination

The other DSP instructions do not involve any multiplication, and may include:

- The accumulator to be used (required)

- The source or destination operand (designated as Wso or Wdo, respectively) with or without an address modifier

- The amount of shift specified by a W register 'Wn' or a literal value

The control instructions may use some of the following operands:

- A program memory address

- The mode of the table read and table write instructions

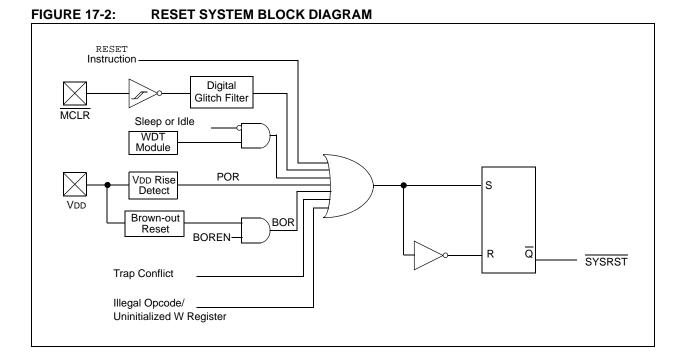

#### TABLE 20-23: TYPE A TIMER (TIMER1) EXTERNAL CLOCK TIMING REQUIREMENTS

| АС СНА       | RACTERIST | ICS                                                             |                      | (unles | ard Operating<br>s otherwise st<br>ing temperatur | <b>ated)</b><br>e -40° | C ≤TA ≤+8 | 35°C for | Industrial<br>pr Extended                |

|--------------|-----------|-----------------------------------------------------------------|----------------------|--------|---------------------------------------------------|------------------------|-----------|----------|------------------------------------------|

| Param<br>No. | Symbol    | Characte                                                        | eristic              |        | Min                                               | Тур                    | Max       | Units    | Conditions                               |

| TA10         | ТтхН      | TxCK High Time                                                  | Synchro<br>no presc  |        | 0.5 TCY + 20                                      |                        | _         | ns       | Must also meet parameter TA15            |

|              |           |                                                                 | Synchro<br>with pres |        | 10                                                |                        | —         | ns       |                                          |

|              |           |                                                                 | Asynchr              | onous  | 10                                                | —                      | —         | ns       |                                          |

| TA11         |           |                                                                 | Synchro<br>no presc  |        | 0.5 TCY + 20                                      |                        | _         | ns       | Must also meet parameter TA15            |

|              |           |                                                                 | Synchro<br>with pres |        | 10                                                |                        | _         | ns       |                                          |

|              |           |                                                                 | Asynchr              | onous  | 10                                                | _                      | —         | ns       |                                          |

| TA15         | ΤτχΡ      | TxCK Input Period                                               | Synchro<br>no presc  |        | Tcy + 10                                          |                        | —         | ns       |                                          |

|              |           |                                                                 | Synchro<br>with pres |        | Greater of:<br>20 ns or<br>(TCY + 40)/N           |                        | _         |          | N = prescale<br>value<br>(1, 8, 64, 256) |

|              |           |                                                                 | Asynchr              | onous  | 20                                                | _                      | —         | ns       |                                          |

| OS60         | Ft1       | SOSC1/T1CK oscil<br>frequency range (or<br>by setting bit TCS ( | scillator e          | nabled | DC                                                | —                      | 50        | kHz      |                                          |

| TA20         | TCKEXTMRL | Delay from Externa<br>Edge to Timer Incre                       |                      | lock   | 0.5 TCY                                           | _                      | 1.5 TCY   |          |                                          |

Note: Timer1 is a Type A.

#### TABLE 20-32: SPI MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHA       | RACTERIST             | TICS                                                            | Standard Op<br>(unless othe<br>Operating ter | rwise state        | ed)<br>-40°C ≤⊺ | ГА ≤+85°C | 5 <b>.5V</b><br>for Industrial<br>C for Extended |

|--------------|-----------------------|-----------------------------------------------------------------|----------------------------------------------|--------------------|-----------------|-----------|--------------------------------------------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                   | Min                                          | Тур <sup>(2)</sup> | Max             | Units     | Conditions                                       |

| SP70         | TscL                  | SCKx Input Low Time                                             | 30                                           | _                  | _               | ns        | —                                                |

| SP71         | TscH                  | SCKx Input High Time                                            | 30                                           | _                  | _               | ns        | —                                                |

| SP72         | TscF                  | SCKx Input Fall Time <sup>(3)</sup>                             | _                                            | 10                 | 25              | ns        | —                                                |

| SP73         | TscR                  | SCKx Input Rise Time <sup>(3)</sup>                             | —                                            | 10                 | 25              | ns        | —                                                |

| SP30         | TdoF                  | SDOx Data Output Fall Time <sup>(3)</sup>                       | _                                            | _                  |                 | ns        | See parameter DO32                               |

| SP31         | TdoR                  | SDOx Data Output Rise Time <sup>(3)</sup>                       | —                                            | _                  | _               | ns        | See parameter DO31                               |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                       | —                                            | _                  | 30              | ns        | —                                                |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                      | 20                                           | _                  | _               | ns        | —                                                |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                       | 20                                           | _                  | _               | ns        | —                                                |

| SP50         | TssL2scH,<br>TssL2scL | SSx↓to SCKx↓or SCKx↑ input                                      | 120                                          | _                  | _               | ns        | —                                                |

| SP51         | TssH2doZ              | SS <sup>↑</sup> to SDOx Output<br>high impedance <sup>(4)</sup> | 10                                           | —                  | 50              | ns        | —                                                |

| SP52         | TscH2ssH<br>TscL2ssH  | SSx↑ after SCKx Edge                                            | 1.5 Tcy + 40                                 | —                  | _               | ns        | —                                                |

| SP60         | TssL2doV              | SDOx Data Output Valid after<br>SCKx Edge                       | —                                            | _                  | 50              | ns        | —                                                |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** The minimum clock period for SCK is 100 ns. Therefore, the clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPI pins.

| AC CH        | ARACTERI        | STICS                                                    | (unless   | otherwise | e stated)<br>ature-40° | °C ≤TA ≤+8 | 7V to 5.5V<br>5°C for Industrial<br>5°C for Extended            |

|--------------|-----------------|----------------------------------------------------------|-----------|-----------|------------------------|------------|-----------------------------------------------------------------|

| Param<br>No. | Symbol          | Characteristic                                           | Min.      | Тур       | Max.                   | Units      | Conditions                                                      |

|              |                 | Cloc                                                     | k Parame  | ters      |                        |            |                                                                 |

| AD50         | TAD             | A/D Clock Period                                         | 334       | —         | _                      | ns         | VDD = 3-5.5V (Note 1)                                           |

| AD51         | tRC             | A/D Internal RC Oscillator Period                        | 1.2       | 1.5       | 1.8                    | μs         |                                                                 |

|              |                 | Con                                                      | version R | ate       |                        |            |                                                                 |

| AD55         | tCONV           | Conversion Time                                          | _         | 14 Tad    |                        | ns         |                                                                 |

| AD56a        | FCNV            | Throughput Rate                                          | _         | 200       | _                      | ksps       | VDD = VREF = 5V,<br>Industrial temperature                      |

| AD56b        | FCNV            | Throughput Rate                                          |           | 100       | _                      | ksps       | VDD = VREF = 5V,<br>Extended temperature                        |

| AD57         | TSAMP           | Sampling Time                                            | 1 Tad     | —         | —                      | ns         | $V_{DD}$ = 3-5.5V source<br>resistance<br>Rs = 0-2.5 k $\Omega$ |

|              |                 | Timin                                                    | g Parame  | eters     |                        |            |                                                                 |

| AD60         | tPCS            | Conversion Start from Sample<br>Trigger                  | —         | 1 Tad     | _                      | ns         |                                                                 |

| AD61         | tPSS            | Sample Start from Setting<br>Sample (SAMP) Bit           | 0.5 Tad   | —         | 1.5<br>Tad             | ns         |                                                                 |

| AD62         | tCSS            | Conversion Completion to<br>Sample Start (ASAM = 1)      | _         | 0.5 Tad   | _                      | ns         |                                                                 |

| AD63         | tDPU <b>(2)</b> | Time to Stabilize Analog Stage<br>from A/D Off to A/D On | _         | —         | 20                     | μs         |                                                                 |

#### TABLE 20-37: 12-BIT A/D CONVERSION TIMING REQUIREMENTS

**Note 1:** Because the sample caps will eventually lose charge, clock rates below 10 kHz can affect linearity performance, especially at elevated temperatures.

**2:** tDPU is the time required for the ADC module to stabilize when it is turned on (ADCON1<ADON> = 1). During this time the ADC result is indeterminate.

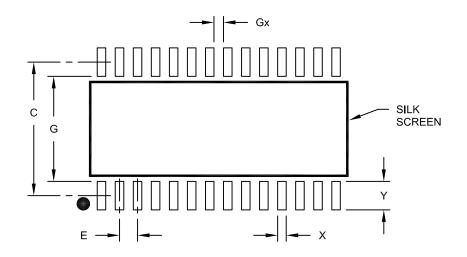

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### RECOMMENDED LAND PATTERN

|                          | Units | Units MILLIMETERS |      | S    |

|--------------------------|-------|-------------------|------|------|

| Dimension Limits         |       | MIN               | NOM  | MAX  |

| Contact Pitch            | E     | 1.27 BSC          |      |      |

| Contact Pad Spacing      | С     |                   | 9.40 |      |

| Contact Pad Width (X28)  | X     |                   |      | 0.60 |

| Contact Pad Length (X28) | Y     |                   |      | 2.00 |

| Distance Between Pads    | Gx    | 0.67              |      |      |

| Distance Between Pads    | G     | 7.40              |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

| Reset                       | 165 |

|-----------------------------|-----|

| Simple OC/PWM Mode          | 171 |

| SPI Module                  |     |

| Master Mode (CKE = 0)       | 172 |

| Master Mode (CKE = 1)       | 173 |

| Slave Mode (CKE = 0)        | 174 |

| Slave Mode (CKE = 1)        | 176 |

| Type A Timer External Clock |     |

| Type B Timer External Clock |     |

| Type C Timer External Clock |     |

| Watchdog Timer              |     |

| Timing Specifications       |     |

| PLL Clock                   |     |

| Trap Vectors                | 69  |

### U

| UART Module                                  |    |

|----------------------------------------------|----|

| Address Detect Mode 10                       | )9 |

| Auto-Baud Support10                          | )9 |

| Baud Rate Generator10                        | )9 |

| Enabling and Setting Up10                    | )7 |

| Framing Error (FERR)10                       | )9 |

| Idle Status 10                               | )9 |

| Loopback Mode10                              | )9 |

| Operation During CPU Sleep and Idle Modes 11 | 0  |

| Overview                                     | )5 |

| Parity Error (PERR)10                        | )9 |

| Receive Break10                              |    |

| Receive Buffer (UxRXB)10                     | )8 |

| Receive Buffer Overrun Error (OERR Bit) 10   | )8 |

| Receive Interrupt10                          | )8 |

| Receiving Data10                             | )8 |

| Receiving in 8-bit or 9-bit Data Mode10      |    |

| Reception Error Handling10                   | )8 |

| Transmit Break10                             | )8 |

| Transmit Buffer (UxTXB)10                    |    |

| Transmit Interrupt10                         | )8 |

| Transmitting Data10                          | )7 |

| Transmitting in 8-bit Data Mode10            | )7 |

| Transmitting in 9-bit Data Mode10            | )7 |

| UART1 Register Map11                         | 1  |

| UART2 Register Map 11                        | 1  |

| UART Operation                               |    |

| Idle Mode11                                  | 0  |

| Sleep Mode11                                 | 0  |

| Unit ID Locations                            | 23 |

| Universal Asynchronous Receiver Transmitter  |    |

| (UART) Module 10                             | )5 |

| w                                            |    |

|                                              |    |

| Wake-up from Sleep                           |    |

| Wake-up from Sleep and Idle                  | 0  |

| Watchdog Timer                               | _  |

| Timing Characteristics16                     |    |

| Timing Requirements                          |    |

| Watchdog Timer (WDT) 123, 13                 |    |

| Enabling and Disabling13                     |    |

| Operation13                                  |    |

| WWW Address                                  |    |

| WWW, On-Line Support                         | 9  |

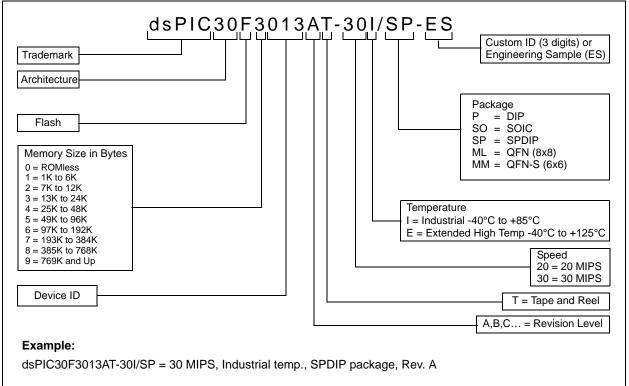

### **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

## **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://support.microchip.com Web Address:

www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-6578-300 Fax: 886-3-6578-370

Taiwan - Kaohsiung Tel: 886-7-213-7830 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820