Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 201010                     |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | dsPIC                                                                         |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 20 MIPS                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 12                                                                            |

| Program Memory Size        | 24KB (8K x 24)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 1K x 8                                                                        |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x12b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 44-QFN (8x8)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f3012-20e-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U S A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2010, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

#### ISBN: 978-1-60932-631-9

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL00® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

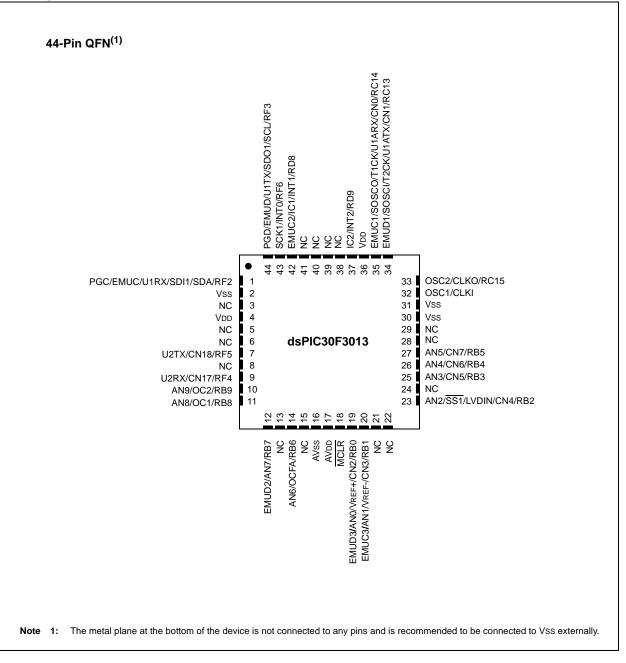

### **Pin Diagrams**

NOTES:

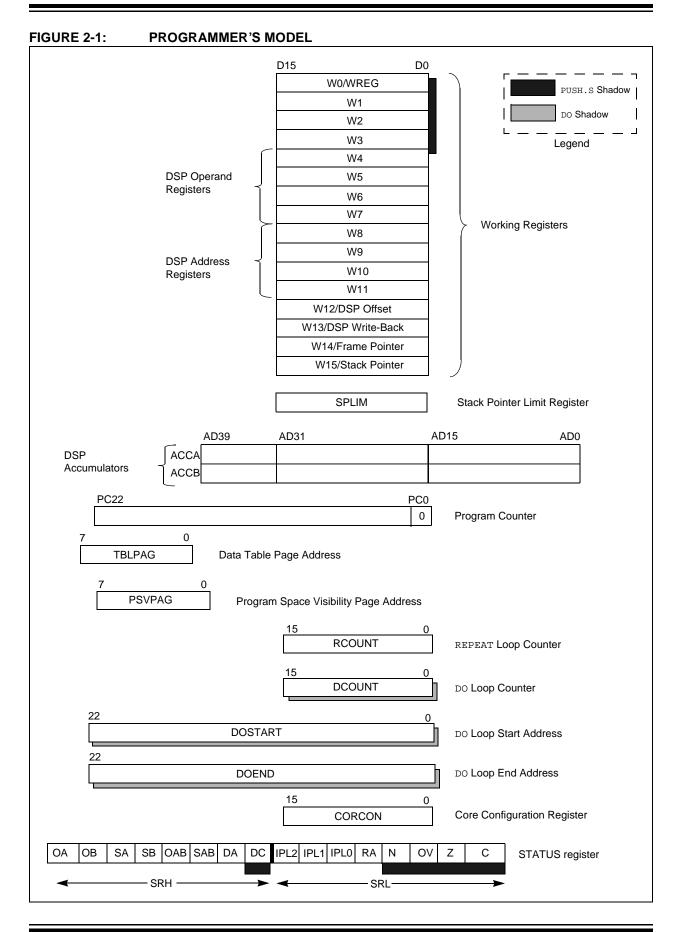

### TABLE 3-3: CORE REGISTER MAP

| SFR Name | Address<br>(Home) | Bit 15 | Bit 14     | Bit 13  | Bit 12      | Bit 11  | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6               | Bit 5               | Bit 4               | Bit 3 | Bit 2               | Bit 1 | Bit 0 | Reset State         |

|----------|-------------------|--------|------------|---------|-------------|---------|--------|-------|--------|-------|---------------------|---------------------|---------------------|-------|---------------------|-------|-------|---------------------|

| W0       | 0000              |        |            | •       |             |         |        |       | W0/WRE | G     |                     |                     |                     |       |                     | •     |       | 0000 0000 0000 0000 |

| W1       | 0002              |        |            |         |             |         |        |       | W1     |       |                     |                     |                     |       |                     |       |       | 0000 0000 0000 0000 |

| W2       | 0004              |        |            |         |             |         |        |       | W2     |       |                     |                     |                     |       |                     |       |       | 0000 0000 0000 0000 |

| W3       | 0006              |        |            |         |             |         |        |       | W3     |       |                     |                     |                     |       |                     |       |       | 0000 0000 0000 0000 |

| W4       | 0008              |        | W4         |         |             |         |        |       |        |       |                     |                     |                     |       | 0000 0000 0000 0000 |       |       |                     |

| W5       | 000A              |        | W5         |         |             |         |        |       |        |       |                     |                     | 0000 0000 0000 0000 |       |                     |       |       |                     |

| W6       | 000C              |        |            |         |             |         |        |       | W6     |       |                     |                     |                     |       |                     |       |       | 0000 0000 0000 0000 |

| W7       | 000E              |        |            |         |             |         |        |       | W7     |       |                     |                     |                     |       |                     |       |       | 0000 0000 0000 0000 |

| W8       | 0010              |        |            |         |             |         |        |       | W8     |       |                     |                     |                     |       |                     |       |       | 0000 0000 0000 0000 |

| W9       | 0012              |        |            |         |             |         |        |       | W9     |       |                     |                     |                     |       |                     |       |       | 0000 0000 0000 0000 |

| W10      | 0014              |        |            |         |             |         |        |       | W10    |       |                     |                     |                     |       |                     |       |       | 0000 0000 0000 0000 |

| W11      | 0016              |        |            |         |             |         |        |       | W11    |       |                     |                     |                     |       |                     |       |       | 0000 0000 0000 0000 |

| W12      | 0018              |        |            |         |             |         |        |       | W12    |       |                     |                     |                     |       |                     |       |       | 0000 0000 0000 0000 |

| W13      | 001A              |        |            |         |             |         |        |       | W13    |       |                     |                     |                     |       |                     |       |       | 0000 0000 0000 0000 |

| W14      | 001C              |        |            |         |             |         |        |       | W14    |       |                     |                     |                     |       |                     |       |       | 0000 0000 0000 0000 |

| W15      | 001E              |        |            |         |             |         |        |       | W15    |       |                     |                     |                     |       |                     |       |       | 0000 1000 0000 0000 |

| SPLIM    | 0020              |        |            |         |             |         |        |       | SPLIM  | l     |                     |                     |                     |       |                     |       |       | 0000 0000 0000 0000 |

| ACCAL    | 0022              |        |            |         |             |         |        |       | ACCAL  | -     |                     |                     |                     |       |                     |       |       | 0000 0000 0000 0000 |

| ACCAH    | 0024              |        |            |         |             |         |        |       | ACCAH  | ł     |                     |                     |                     |       |                     |       |       | 0000 0000 0000 0000 |

| ACCAU    | 0026              |        |            | Sign E: | xtension (/ | ACCA<39 | >)     |       |        |       |                     |                     | ACC                 | AU    |                     |       |       | 0000 0000 0000 0000 |

| ACCBL    | 0028              |        |            |         |             |         |        |       | ACCBL  | -     |                     |                     |                     |       |                     |       |       | 0000 0000 0000 0000 |

| ACCBH    | 002A              |        |            |         |             |         |        |       | ACCBH  | ł     |                     |                     |                     |       |                     |       |       | 0000 0000 0000 0000 |

| ACCBU    | 002C              |        |            | Sign Ex | ktension (/ | ACCB<39 | >)     |       |        |       |                     |                     | ACCI                | BU    |                     |       |       | 0000 0000 0000 0000 |

| PCL      | 002E              |        |            |         |             |         |        |       | PCL    |       |                     |                     |                     |       |                     |       |       | 0000 0000 0000 0000 |

| PCH      | 0030              | _      | —          | —       | _           | _       | —      |       | —      | _     |                     |                     |                     | PCH   |                     |       |       | 0000 0000 0000 0000 |

| TBLPAG   | 0032              | _      | —          | —       | _           | _       | —      |       | —      |       |                     |                     | TBLP                | AG    |                     |       |       | 0000 0000 0000 0000 |

| PSVPAG   | 0034              | _      | —          | —       | _           | _       | —      | _     | _      |       |                     |                     | PSVP                | PAG   |                     |       |       | 0000 0000 0000 0000 |

| RCOUNT   | 0036              |        |            |         |             |         |        |       | RCOUN  | IT    |                     |                     |                     |       |                     |       |       | uuuu uuuu uuuu uuuu |

| DCOUNT   | 0038              |        | DCOUNT     |         |             |         |        |       |        |       |                     |                     | uuuu uuuu uuuu uuuu |       |                     |       |       |                     |

| DOSTARTL | 003A              |        | DOSTARTL 0 |         |             |         |        |       |        |       |                     | 0                   | uuuu uuuu uuuu uuu0 |       |                     |       |       |                     |

| DOSTARTH | 003C              | _      | DOSTARTH   |         |             |         |        |       |        |       |                     | 0000 0000 0uuu uuuu |                     |       |                     |       |       |                     |

| DOENDL   | 003E              |        |            |         |             |         |        | D     | OENDL  |       |                     |                     |                     |       |                     |       | 0     | uuuu uuuu uuuu uuu0 |

| DOENDH   | 0040              | _      | DOENDH     |         |             |         |        |       |        |       | 0000 0000 0uuu uuuu |                     |                     |       |                     |       |       |                     |

| SR       | 0042              | OA     | ОВ         | SA      | SB          | OAB     | SAB    | DA    | DC     | IPL2  | IPL1                | IPL0                | RA                  | N     | OV                  | Z     | С     | 0000 0000 0000 0000 |

Legend: u = uninitialized bit; — = unimplemented bit, read as '0'

**Note:** Refer to the "*dsPIC30F Family Reference Manual*" (DS70046) for descriptions of register bit fields.

### TABLE 5-1: NVM REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14       | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6    | Bit 5 | Bit 4               | Bit 3          | Bit 2 | Bit 1 | Bit 0 | AII RESETS          |

|-----------|-------|--------|--------------|--------|--------|--------|--------|-------|-------|-------|----------|-------|---------------------|----------------|-------|-------|-------|---------------------|

| NVMCON    | 0760  | WR     | WREN         | WRERR  | —      | —      | —      | —     | TWRI  | —     |          |       | 0000 0000 0000 0000 |                |       |       |       |                     |

| NVMADR    | 0762  |        | NVMADR<15:0> |        |        |        |        |       |       |       |          |       |                     | uuuu uuuu uuuu |       |       |       |                     |

| NVMADRU   | 0764  | _      |              | _      | —      | -      | —      | —     |       |       |          |       | NVMAD               | R<23:16        | >     |       |       | 0000 0000 uuuu uuuu |

| NVMKEY    | 0766  | —      | _            |        | —      | —      | —      |       | _     |       | KEY<7:0> |       |                     |                |       |       |       | 0000 0000 0000 0000 |

Legend: u = uninitialized bit; - = unimplemented bit, read as '0'

Note: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

### 8.6 Fast Context Saving

A context saving option is available using shadow registers. Shadow registers are provided for the DC, N, OV, Z and C bits in SR, and the registers W0 through W3. The shadows are only one level deep. The shadow registers are accessible using the PUSH.S and POP.S instructions only.

When the processor vectors to an interrupt, the PUSH.S instruction can be used to store the current value of the aforementioned registers into their respective shadow registers.

If an ISR of a certain priority uses the PUSH.S and POP.S instructions for fast context saving, then a higher priority ISR should not include the same instructions. Users must save the key registers in software during a lower priority interrupt if the higher priority ISR uses fast context saving.

### 8.7 External Interrupt Requests

The interrupt controller supports three external interrupt request signals, INT0-INT2. These inputs are edge sensitive; they require a low-to-high or a high-to-low transition to generate an interrupt request. The INTCON2 register has three bits, INT0EP-INT2EP, that select the polarity of the edge detection circuitry.

### 8.8 Wake-up from Sleep and Idle

The interrupt controller may be used to wake-up the processor from either Sleep or Idle modes, if Sleep or Idle mode is active when the interrupt is generated.

If an enabled interrupt request of sufficient priority is received by the interrupt controller, then the standard interrupt request is presented to the processor. At the same time, the processor wakes up from Sleep or Idle and begins execution of the ISR needed to process the interrupt request.

### 9.1 Timer Gate Operation

The 16-bit timer can be placed in the Gated Time Accumulation mode. This mode allows the internal TCY to increment the respective timer when the gate input signal (T1CK pin) is asserted high. Control bit, TGATE (T1CON<6>), must be set to enable this mode. The timer must be enabled (TON = 1) and the timer clock source set to internal (TCS = 0).

When the CPU goes into Idle mode, the timer stops incrementing unless TSIDL = 0. If TSIDL = 1, the timer resumes the incrementing sequence upon termination of the CPU Idle mode.

### 9.2 Timer Prescaler

The input clock (FOSC/4 or external clock) to the 16-bit Timer has a prescale option of 1:1, 1:8, 1:64 and 1:256, selected by control bits, TCKPS<1:0> (T1CON<5:4>). The prescaler counter is cleared when any of the following occurs:

- A write to the TMR1 register

- A write to the T1CON register

- A device Reset, such as a POR and BOR

However, if the timer is disabled (TON = 0), then the timer prescaler cannot be reset since the prescaler clock is halted.

The TMR1 register is not cleared when the T1CON register is written. It is cleared by writing to the TMR1 register.

### 9.3 Timer Operation During Sleep Mode

The timer operates during CPU Sleep mode, if:

- The timer module is enabled (TON = 1), and

- The timer clock source is selected as external (TCS = 1), and

- The TSYNC bit (T1CON<2>) is asserted to a logic '0' which defines the external clock source as asynchronous.

When all three conditions are true, the timer continues to count up to the Period register and be reset to 0x0000.

When a match between the timer and the Period register occurs, an interrupt can be generated if the respective timer interrupt enable bit is asserted.

### 9.4 Timer Interrupt

The 16-bit timer has the ability to generate an interrupt-on-period match. When the timer count matches the Period register, the T1IF bit is asserted and an interrupt is generated, if enabled. The T1IF bit must be cleared in software. The timer interrupt flag, T1IF, is located in the IFS0 Control register in the interrupt controller.

When the Gated Time Accumulation mode is enabled, an interrupt is also generated on the falling edge of the gate signal (at the end of the accumulation cycle).

Enabling an interrupt is accomplished via the respective timer interrupt enable bit, T1IE. The timer interrupt enable bit is located in the IEC0 Control register in the interrupt controller.

### 9.5 Real-Time Clock

Timer1, when operating in Real-Time Clock (RTC) mode, provides time of day and event time-stamping capabilities. Key operational features of the RTC are:

- Operation from 32 kHz LP oscillator

- 8-bit prescaler

- Low power

- Real-Time Clock interrupts

These operating modes are determined by setting the appropriate bit(s) in the T1CON register.

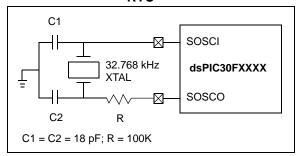

FIGURE 9-2:

#### RECOMMENDED COMPONENTS FOR TIMER1 LP OSCILLATOR RTC

### 9.5.1 RTC OSCILLATOR OPERATION

When the TON = 1, TCS = 1 and TGATE = 0, the timer increments on the rising edge of the 32 kHz LP oscillator output signal, up to the value specified in the Period register and is then reset to '0'.

The TSYNC bit must be asserted to a logic '0' (Asynchronous mode) for correct operation.

Enabling the LPOSCEN bit (OSCCON<1>) disables the normal Timer and Counter modes and enables a timer carry-out wake-up event.

When the CPU enters Sleep mode, the RTC continues to operate, provided the 32 kHz external crystal oscillator is active and the control bits have not been changed. The TSIDL bit should be cleared to '0' in order for RTC to continue operation in Idle mode.

### 9.5.2 RTC INTERRUPTS

When an interrupt event occurs, the respective interrupt flag, T1IF, is asserted and an interrupt is generated if enabled. The T1IF bit must be cleared in software. The respective Timer interrupt flag, T1IF, is located in the IFS0 register in the interrupt controller.

### TABLE 10-1: TIMER2/3 REGISTER MAP

| 0        |  |

|----------|--|

| © 2010   |  |

| 10       |  |

| ≦.       |  |

| Microch  |  |

| ch       |  |

| ₽.       |  |

| Tec      |  |

|          |  |

| <u>o</u> |  |

| nology   |  |

| _        |  |

| nc.      |  |

| SFR Name | Addr. | Bit 15 | Bit 14                                                     | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7        | Bit 6 | Bit 5  | Bit 4               | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset State         |

|----------|-------|--------|------------------------------------------------------------|--------|--------|--------|--------|-------|-------|--------------|-------|--------|---------------------|-------|-------|-------|-------|---------------------|

| TMR2     | 0106  |        |                                                            |        |        |        |        |       | Ti    | mer2 Regist  | er    |        |                     |       |       |       |       | uuuu uuuu uuuu uuuu |

| TMR3HLD  | 0108  |        | Timer3 Holding Register (for 32-bit timer operations only) |        |        |        |        |       |       |              |       |        | uuuu uuuu uuuu uuuu |       |       |       |       |                     |

| TMR3     | 010A  |        |                                                            |        |        |        |        |       | Ti    | mer3 Regist  | ər    |        |                     |       |       |       |       | uuuu uuuu uuuu uuuu |

| PR2      | 010C  |        |                                                            |        |        |        |        |       | Pe    | riod Registe | r 2   |        |                     |       |       |       |       | 1111 1111 1111 1111 |

| PR3      | 010E  |        |                                                            |        |        |        |        |       | Pe    | riod Registe | r 3   |        |                     |       |       |       |       | 1111 1111 1111 1111 |

| T2CON    | 0110  | TON    | ON – TSIDL – – – – – TGATE TCKPS1 TCKPS0 T32 – TCS –       |        |        |        |        |       |       |              |       |        | 0000 0000 0000 0000 |       |       |       |       |                     |

| T3CON    | 0112  | TON    | _                                                          | TSIDL  | —      | —      | _      | _     | _     | -            | TGATE | TCKPS1 | TCKPS0              | —     | _     | TCS   | -     | 0000 0000 0000 0000 |

**Legend:** u = uninitialized bit; — = unimplemented bit, read as '0'

Note: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

NOTES:

### 12.1 Timer2 and Timer3 Selection Mode

Each output compare channel can select between one of two 16-bit timers, Timer2 or Timer3.

The selection of the timers is controlled by the OCTSEL bit (OCxCON<3>). Timer2 is the default timer resource for the output compare module.

## 12.2 Simple Output Compare Match Mode

When control bits OCM<2:0> (OCxCON<2:0>) = 001, 010 or 011, the selected output compare channel is configured for one of three simple Output Compare Match modes:

- Compare forces I/O pin low

- Compare forces I/O pin high

- Compare toggles I/O pin

The OCxR register is used in these modes. The OCxR register is loaded with a value and is compared to the selected incrementing timer count. When a compare occurs, one of these Compare Match modes occurs. If the counter resets to zero before reaching the value in OCxR, the state of the OCx pin remains unchanged.

### 12.3 Dual Output Compare Match Mode

When control bits OCM<2:0> (OCxCON<2:0>) = 100 or 101, the selected output compare channel is configured for one of two Dual Output Compare modes, which are:

- Single Output Pulse mode

- Continuous Output Pulse mode

### 12.3.1 SINGLE PULSE MODE

For the user to configure the module for the generation of a single output pulse, the following steps are required (assuming timer is off):

- Determine instruction cycle time Tcy.

- Calculate desired pulse width value based on Tcy.

- Calculate time to start pulse from timer start value of 0x0000.

- Write pulse width start and stop times into OCxR and OCxRS Compare registers (x denotes channel 1 to N).

- Set Timer Period register to value equal to or greater than value in OCxRS Compare register.

- Set OCM<2:0> = 100.

- Enable timer, TON bit (TxCON<15>) = 1.

To initiate another single pulse, issue another write to set OCM<2:0> = 100.

### 12.3.2 CONTINUOUS PULSE MODE

For the user to configure the module for the generation of a continuous stream of output pulses, the following steps are required:

- Determine instruction cycle time Tcy.

- Calculate desired pulse value based on Tcy.

- Calculate timer to start pulse width from timer start value of 0x0000.

- Write pulse width start and stop times into OCxR and OCxRS (x denotes channel 1 to N) Compare registers, respectively.

- Set Timer Period register to value equal to or greater than value in OCxRS Compare register.

- Set OCM<2:0> = 101.

- Enable timer, TON bit (TxCON<15>) = 1.

### 12.4 Simple PWM Mode

When control bits OCM<2:0> (OCxCON<2:0>) = 110 or 111, the selected output compare channel is configured for the PWM mode of operation. When configured for the PWM mode of operation, OCxR is the main latch (read-only) and OCxRS is the secondary latch. This enables glitchless PWM transitions.

The user must perform the following steps in order to configure the output compare module for PWM operation:

- 1. Set the PWM period by writing to the appropriate period register.

- 2. Set the PWM duty cycle by writing to the OCxRS register.

- 3. Configure the output compare module for PWM operation.

- 4. Set the TMRx prescale value and enable the Timer, TON bit (TxCON<15>) = 1.

### 12.4.1 INPUT PIN FAULT PROTECTION FOR PWM

When control bits OCM<2:0> (OCxCON<2:0>) = 111, the selected output compare channel is again configured for the PWM mode of operation with the additional feature of input Fault protection. While in this mode, if a logic '0' is detected on the OCFA/B pin, the respective PWM output pin is placed in the high impedance input state. The OCFLT bit (OCxCON<4>) indicates whether a Fault condition has occurred. This state is maintained until both of the following events have occurred:

- The external Fault condition has been removed.

- The PWM mode has been re-enabled by writing to the appropriate control bits.

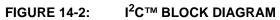

### TABLE 14-2: I<sup>2</sup>C REGISTER MAP

| SFR Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8                 | Bit 7               | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1               | Bit 0               | Reset State         |

|----------|-------|---------|--------|---------|--------|--------|--------|--------|-----------------------|---------------------|-------|-------|-------|-------|-------|---------------------|---------------------|---------------------|

| I2CRCV   | 0200  | —       | _      |         | —      | _      |        |        | Receive Register      |                     |       |       |       |       |       |                     | 0000 0000 0000 0000 |                     |

| I2CTRN   | 0202  | -       | —      | _       | _      | —      | _      | _      | — — Transmit Register |                     |       |       |       |       |       | 0000 0000 1111 1111 |                     |                     |

| I2CBRG   | 0204  | -       | —      | _       | _      | _      | _      | _      |                       | Baud Rate Generator |       |       |       |       |       |                     |                     | 0000 0000 0000 0000 |

| I2CCON   | 0206  | I2CEN   | —      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN                  | GCEN                | STREN | ACKDT | ACKEN | RCEN  | PEN   | RSEN                | SEN                 | 0001 0000 0000 0000 |

| I2CSTAT  | 0208  | ACKSTAT | TRSTAT | _       | —      | _      | BCL    | GCSTAT | ADD10                 | IWCOL               | I2COV | D_A   | Р     | S     | R_W   | RBF                 | TBF                 | 0000 0000 0000 0000 |

| I2CADD   | 020A  | _       | _      |         | —      | —      | _      |        | Address Register      |                     |       |       |       |       |       |                     | 0000 0000 0000 0000 |                     |

Legend: — = unimplemented bit, read as '0'

Note: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

NOTES:

### TABLE 17-1: OSCILLATOR OPERATING MODES

| Oscillator Mode                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XTL<br>XT<br>XT w/PLL 4x<br>XT w/PLL 8x<br>XT w/PLL 16x<br>LP<br>HS | <ul> <li>200 kHz-4 MHz crystal on OSC1:OSC2.</li> <li>4 MHz-10 MHz crystal on OSC1:OSC2.</li> <li>4 MHz-10 MHz crystal on OSC1:OSC2, 4x PLL enabled.</li> <li>4 MHz-10 MHz crystal on OSC1:OSC2, 8x PLL enabled.</li> <li>4 MHz-7.5 MHz crystal on OSC1:OSC2, 16x PLL enabled<sup>(1)</sup>.</li> <li>32 kHz crystal on SOSCO:SOSCI<sup>(2)</sup>.</li> <li>10 MHz-25 MHz crystal.</li> </ul> |

| HS/2 w/PLL 4x                                                       | 10 MHz-20 MHz crystal, divide by 2, 4x PLL enabled.                                                                                                                                                                                                                                                                                                                                           |

| HS/2 w/PLL 8x                                                       | 10 MHz-20 MHz crystal, divide by 2, 8x PLL enabled.                                                                                                                                                                                                                                                                                                                                           |

| HS/2 w/PLL 16x                                                      | 10 MHz-15 MHz crystal, divide by 2, 16x PLL enabled <sup>(1)</sup> .                                                                                                                                                                                                                                                                                                                          |

| HS/3 w/PLL 4x                                                       | 12 MHz-25 MHz crystal, divide by 3, 4x PLL enabled.                                                                                                                                                                                                                                                                                                                                           |

| HS/3 w/PLL 8x                                                       | 12 MHz-25 MHz crystal, divide by 3, 8x PLL enabled.                                                                                                                                                                                                                                                                                                                                           |

| HS/3 w/PLL 16x                                                      | 12 MHz-22.5 MHz crystal, divide by 3, 16x PLL enabled <sup>(1)</sup> .                                                                                                                                                                                                                                                                                                                        |

| EC                                                                  | External clock input (0-40 MHz).                                                                                                                                                                                                                                                                                                                                                              |

| ECIO                                                                | External clock input (0-40 MHz), OSC2 pin is I/O.                                                                                                                                                                                                                                                                                                                                             |

| EC w/PLL 4x                                                         | External clock input (4-10 MHz), OSC2 pin is I/O, 4x PLL enabled.                                                                                                                                                                                                                                                                                                                             |

| EC w/PLL 8x                                                         | External clock input (4-10 MHz), OSC2 pin is I/O, 8x PLL enabled.                                                                                                                                                                                                                                                                                                                             |

| EC w/PLL 16x                                                        | External clock input (4-7.5 MHz), OSC2 pin is I/O, 16x PLL enabled <sup>(1)</sup> .                                                                                                                                                                                                                                                                                                           |

| ERC                                                                 | External RC oscillator, OSC2 pin is Fosc/4 output <sup>(3)</sup> .                                                                                                                                                                                                                                                                                                                            |

| ERCIO                                                               | External RC oscillator, OSC2 pin is I/O <sup>(3)</sup> .                                                                                                                                                                                                                                                                                                                                      |

| FRC<br>FRC w/PLL 4x<br>FRC w/PLL 8x<br>FRC w/PLL 16x<br>LPRC        | <ul> <li>7.37 MHz internal RC oscillator.</li> <li>7.37 MHz Internal RC oscillator, 4x PLL enabled.</li> <li>7.37 MHz Internal RC oscillator, 8x PLL enabled.</li> <li>7.37 MHz Internal RC oscillator, 16x PLL enabled.</li> <li>512 kHz internal RC oscillator.</li> </ul>                                                                                                                  |

**Note 1:** dsPIC30F maximum operating frequency of 120 MHz must be met.

2: LP oscillator can be conveniently shared as system clock, as well as real-time clock for Timer1.

3: Requires external R and C. Frequency operation up to 4 MHz.

Any interrupt that is individually enabled (using the corresponding IE bit) and meets the prevailing priority level will be able to wake-up the processor. The processor will process the interrupt and branch to the ISR. The Sleep Status bit in the RCON register is set upon wake-up.

Note: In spite of various delays applied (TPOR, TLOCK and TPWRT), the crystal oscillator (and PLL) may not be active at the end of the time-out (e.g., for low-frequency crystals). In such cases, if FSCM is enabled, then the device will detect this as a clock failure and process the clock failure trap, the FRC oscillator will be enabled and the user will have to re-enable the crystal oscillator. If FSCM is not enabled, then the device will simply suspend execution of code until the clock is stable and will remain in Sleep until the oscillator clock has started.

All Resets will wake-up the processor from Sleep mode. Any Reset, other than POR, will set the Sleep Status bit. In a POR, the Sleep bit is cleared.

If the Watchdog Timer is enabled, then the processor will wake-up from Sleep mode upon WDT time-out. The Sleep and WDTO Status bits are both set.

### 17.6.2 IDLE MODE

In Idle mode, the clock to the CPU is shut down while peripherals keep running. Unlike Sleep mode, the clock source remains active.

Several peripherals have a control bit in each module that allows them to operate during Idle.

LPRC Fail-Safe Clock remains active if clock failure detect is enabled.

The processor wakes up from Idle if at least one of the following conditions has occurred:

- any interrupt that is individually enabled (IE bit is '1') and meets the required priority level

- any Reset (POR, BOR, MCLR)

- WDT time-out

Upon wake-up from Idle mode, the clock is re-applied to the CPU and instruction execution begins immediately, starting with the instruction following the PWRSAV instruction.

Any interrupt that is individually enabled (using IE bit) and meets the prevailing priority level will be able to wake-up the processor. The processor will process the interrupt and branch to the ISR. The Idle Status bit in the RCON register is set upon wake-up.

Any Reset other than POR will set the Idle Status bit. On a POR, the Idle bit is cleared.

If Watchdog Timer is enabled, then the processor will wake-up from Idle mode upon WDT time-out. The Idle and WDTO Status bits are both set.

Unlike wake-up from Sleep, there are no time delays involved in wake-up from Idle.

### 17.7 Device Configuration Registers

The Configuration bits in each device Configuration register specify some of the device modes and are programmed by a device programmer, or by using the In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) feature of the device. Each device Configuration register is a 24-bit register, but only the lower 16 bits of each register are used to hold configuration data. There are five device Configuration registers available to the user:

- 1. FOSC (0xF80000): Oscillator Configuration Register

- 2. FWDT (0xF80002): Watchdog Timer Configuration Register

- 3. FBORPOR (0xF80004): BOR and POR Configuration Register

- 4. FGS (0xF8000A): General Code Segment Configuration Register

- 5. FICD (0xF8000C): Debug Configuration Register

The placement of the Configuration bits is automatically handled when you select the device in your device programmer. The desired state of the Configuration bits may be specified in the source code (dependent on the language tool used), or through the programming interface. After the device has been programmed, the application software may read the Configuration bit values through the table read instructions. For additional information, please refer to the Programming Specifications of the device.

Note: If the code protection Configuration fuse bits (FGS<GCP> and FGS<GWRP>) have been programmed, an erase of the entire code-protected device is only possible at voltages  $VDD \ge 4.5V$ .

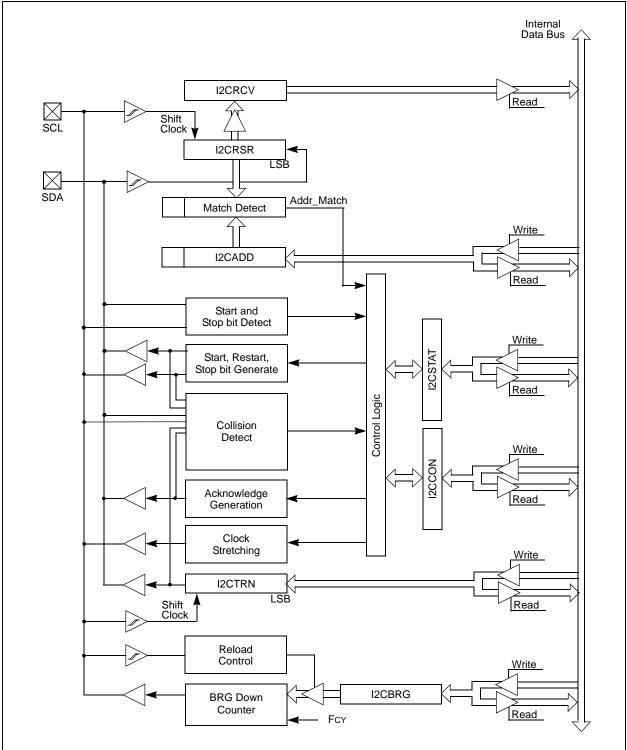

### TABLE 20-35: CAN MODULE I/O TIMING REQUIREMENTS

| AC CHARA     | CTERISTIC | 5                                       | (unless othe | Standard Operating Conditions: 2.5V to 5.5V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |     |       |            |  |  |  |  |  |  |

|--------------|-----------|-----------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------------|--|--|--|--|--|--|

| Param<br>No. | Symbol    | Characteri                              | Min          | Тур <sup>(2)</sup>                                                                                                                                                                       | Max | Units | Conditions |  |  |  |  |  |  |

| CA10         | TioF      | Port Output Fall Ti                     | me           |                                                                                                                                                                                          | 10  | 25    | ns         |  |  |  |  |  |  |

| CA11         | TioR      | Port Output Rise T                      | īme          |                                                                                                                                                                                          | 10  | 25    | ns         |  |  |  |  |  |  |

| CA20         | Tcwf      | Pulse Width to Trig<br>CAN Wake-up Filt |              | 500                                                                                                                                                                                      | —   |       | ns         |  |  |  |  |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

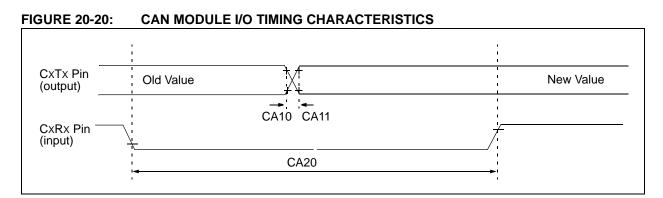

### FIGURE 20-21: 12-BIT A/D CONVERSION TIMING CHARACTERISTICS

| AC CH        | ARACTERI        | STICS                                                    | (unless   | otherwise | e stated)<br>ature-40° | °C ≤TA ≤+8 | 7V to 5.5V<br>5°C for Industrial<br>5°C for Extended       |

|--------------|-----------------|----------------------------------------------------------|-----------|-----------|------------------------|------------|------------------------------------------------------------|

| Param<br>No. | Symbol          | Characteristic                                           | Min.      | Тур       | Max.                   | Units      | Conditions                                                 |

|              |                 | Cloc                                                     | k Parame  | ters      |                        |            |                                                            |

| AD50         | TAD             | A/D Clock Period                                         | 334       | —         | _                      | ns         | VDD = 3-5.5V (Note 1)                                      |

| AD51         | tRC             | A/D Internal RC Oscillator Period                        | 1.2       | 1.5       | 1.8                    | μs         |                                                            |

|              |                 | Con                                                      | version R | ate       |                        |            |                                                            |

| AD55         | tCONV           | Conversion Time                                          | _         | 14 Tad    |                        | ns         |                                                            |

| AD56a        | FCNV            | Throughput Rate                                          | _         | 200       | _                      | ksps       | VDD = VREF = 5V,<br>Industrial temperature                 |

| AD56b        | FCNV            | Throughput Rate                                          | _         | 100       | _                      | ksps       | VDD = VREF = 5V,<br>Extended temperature                   |

| AD57         | TSAMP           | Sampling Time                                            | 1 Tad     | _         | —                      | ns         | VDD = 3-5.5V source<br>resistance<br>Rs = 0-2.5 k $\Omega$ |

|              |                 | Timin                                                    | g Parame  | eters     |                        |            |                                                            |

| AD60         | tPCS            | Conversion Start from Sample<br>Trigger                  | —         | 1 Tad     | _                      | ns         |                                                            |

| AD61         | tPSS            | Sample Start from Setting<br>Sample (SAMP) Bit           | 0.5 Tad   | —         | 1.5<br>Tad             | ns         |                                                            |

| AD62         | tCSS            | Conversion Completion to<br>Sample Start (ASAM = 1)      | _         | 0.5 Tad   | _                      | ns         |                                                            |

| AD63         | tDPU <b>(2)</b> | Time to Stabilize Analog Stage<br>from A/D Off to A/D On | _         | —         | 20                     | μs         |                                                            |

### TABLE 20-37: 12-BIT A/D CONVERSION TIMING REQUIREMENTS

**Note 1:** Because the sample caps will eventually lose charge, clock rates below 10 kHz can affect linearity performance, especially at elevated temperatures.

**2:** tDPU is the time required for the ADC module to stabilize when it is turned on (ADCON1<ADON> = 1). During this time the ADC result is indeterminate.

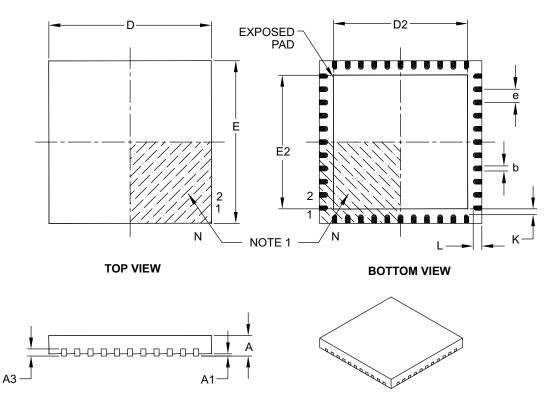

### 44-Lead Plastic Quad Flat, No Lead Package (ML) – 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            |      | MILLIMETERS | 6    |

|------------------------|------------------|------|-------------|------|

|                        | Dimension Limits | MIN  | NOM         | MAX  |

| Number of Pins         | N                |      | 44          |      |

| Pitch                  | e                |      | 0.65 BSC    |      |

| Overall Height         | A                | 0.80 | 0.90        | 1.00 |

| Standoff               | A1               | 0.00 | 0.02        | 0.05 |

| Contact Thickness      | A3               |      | 0.20 REF    |      |

| Overall Width          | E                |      | 8.00 BSC    |      |

| Exposed Pad Width      | E2               | 6.30 | 6.45        | 6.80 |

| Overall Length         | D                |      | 8.00 BSC    |      |

| Exposed Pad Length     | D2               | 6.30 | 6.45        | 6.80 |

| Contact Width          | b                | 0.25 | 0.30        | 0.38 |

| Contact Length         | L                | 0.30 | 0.40        | 0.50 |

| Contact-to-Exposed Pad | К                | 0.20 | -           | -    |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-103B