Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | dsPIC                                                                        |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 20 MIPS                                                                      |

| Connectivity               | I²C, SPI, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 12                                                                           |

| Program Memory Size        | 24KB (8K x 24)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 1K x 8                                                                       |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x12b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Through Hole                                                                 |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                      |

| Supplier Device Package    | 18-PDIP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f3012-20e-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

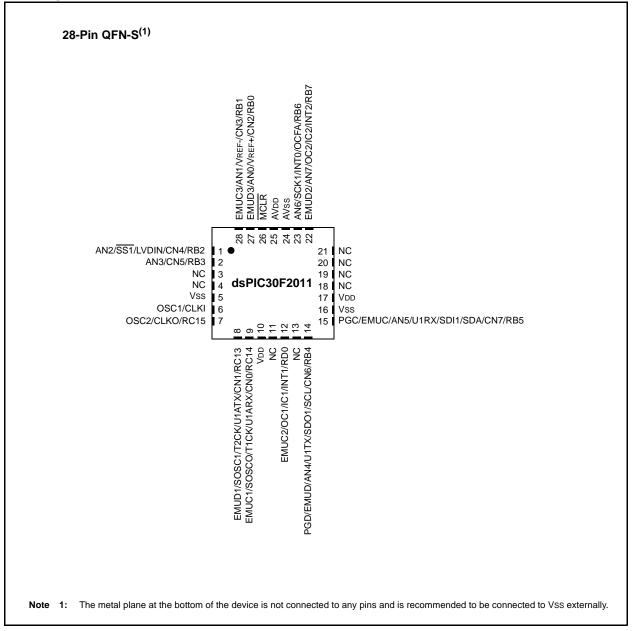

## **Pin Diagrams**

## TABLE 3-3: CORE REGISTER MAP (CONTINUED)

|          | U. U              |        |               |        | 00.11  |        | /      |        |         |        |                     |        |        |       |       |       |       |                     |

|----------|-------------------|--------|---------------|--------|--------|--------|--------|--------|---------|--------|---------------------|--------|--------|-------|-------|-------|-------|---------------------|

| SFR Name | Address<br>(Home) | Bit 15 | Bit 14        | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8   | Bit 7  | Bit 6               | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset State         |

| CORCON   | 0044              | —      | _             | -      | US     | EDT    | DL2    | DL1    | DL0     | SATA   | SATB                | SATDW  | ACCSAT | IPL3  | PSV   | RND   | IF    | 0000 0000 0010 0000 |

| MODCON   | 0046              | XMODEN | YMODEN        | _      |        |        | BWM    | l<3:0> |         |        | YWI                 | M<3:0> |        |       | XWM<  | <3:0> |       | 0000 0000 0000 0000 |

| XMODSRT  | 0048              |        | XS<15:1> 0 u  |        |        |        |        |        |         |        | uuuu uuuu uuuu uuu0 |        |        |       |       |       |       |                     |

| XMODEND  | 004A              |        |               |        |        |        |        | XE     | <15:1>  |        |                     |        |        |       |       |       | 1     | uuuu uuuu uuul      |

| YMODSRT  | 004C              |        |               |        |        |        |        | YS     | 6<15:1> |        |                     |        |        |       |       |       | 0     | uuuu uuuu uuuu uuu0 |

| YMODEND  | 004E              |        | YE<15:1> 1 1  |        |        |        |        |        |         |        | uuuu uuuu uuul      |        |        |       |       |       |       |                     |

| XBREV    | 0050              | BREN   | BREN XB<14:0> |        |        |        |        |        |         |        | uuuu uuuu uuuu uuuu |        |        |       |       |       |       |                     |

| DISICNT  | 0052              | —      | _             |        |        |        |        |        |         | DISICN | <13:0>              |        |        |       |       |       |       | 0000 0000 0000 0000 |

Legend: u = uninitialized bit; — = unimplemented bit, read as '0'

Note: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

## 8.1 Interrupt Priority

The user-assignable interrupt priority bits (IP<2:0>) for each individual interrupt source are located in the LS 3 bits of each nibble within the IPCx register(s). Bit 3 of each nibble is not used and is read as a '0'. These bits define the priority level assigned to a particular interrupt by the user.

| Note: | The user-assignable priority levels start at |

|-------|----------------------------------------------|

|       | 0 as the lowest priority and level 7 as the  |

|       | highest priority.                            |

Natural Order Priority is determined by the position of an interrupt in the vector table, and only affects interrupt operation when multiple interrupts with the same user-assigned priority become pending at the same time.

Table 8-1 lists the interrupt numbers and interrupt sources for the dsPIC30F2011/2012/3012/3013 devices and their associated vector numbers.

- **Note 1:** The natural order priority scheme has 0 as the highest priority and 53 as the lowest priority.

- **2:** The natural order priority number is the same as the INT number.

The ability for the user to assign every interrupt to one of seven priority levels means that the user can assign a very high overall priority level to an interrupt with a low natural order priority. For example, the PLVD (Low Voltage Detect) can be given a priority of 7. The INTO (External Interrupt 0) may be assigned to priority level 1, thus giving it a very low effective priority.

#### TABLE 8-1:INTERRUPT VECTOR TABLE

| Interrupt<br>Number | Vector<br>Number               | Interrupt Source                                     |  |  |  |  |  |  |  |  |

|---------------------|--------------------------------|------------------------------------------------------|--|--|--|--|--|--|--|--|

|                     | Highest Natural Order Priority |                                                      |  |  |  |  |  |  |  |  |

| 0                   | 8                              | INT0 – External Interrupt 0                          |  |  |  |  |  |  |  |  |

| 1                   | 9                              | IC1 – Input Capture 1                                |  |  |  |  |  |  |  |  |

| 2                   | 10                             | OC1 – Output Compare 1                               |  |  |  |  |  |  |  |  |

| 3                   | 11                             | T1 – Timer 1                                         |  |  |  |  |  |  |  |  |

| 4                   | 12                             | IC2 – Input Capture 2                                |  |  |  |  |  |  |  |  |

| 5                   | 13                             | OC2 – Output Compare 2                               |  |  |  |  |  |  |  |  |

| 6                   | 14                             | T2 – Timer2                                          |  |  |  |  |  |  |  |  |

| 7                   | 15                             | T3 – Timer3                                          |  |  |  |  |  |  |  |  |

| 8                   | 16                             | SPI1                                                 |  |  |  |  |  |  |  |  |

| 9                   | 17                             | U1RX – UART1 Receiver                                |  |  |  |  |  |  |  |  |

| 10                  | 18                             | U1TX – UART1 Transmitter                             |  |  |  |  |  |  |  |  |

| 11                  | 19                             | ADC – ADC Convert Done                               |  |  |  |  |  |  |  |  |

| 12                  | 20                             | NVM – NVM Write Complete                             |  |  |  |  |  |  |  |  |

| 13                  | 21                             | SI2C – I <sup>2</sup> C <sup>™</sup> Slave Interrupt |  |  |  |  |  |  |  |  |

| 14                  | 22                             | MI2C – I <sup>2</sup> C Master Interrupt             |  |  |  |  |  |  |  |  |

| 15                  | 23                             | Input Change Interrupt                               |  |  |  |  |  |  |  |  |

| 16                  | 24                             | INT1 – External Interrupt 1                          |  |  |  |  |  |  |  |  |

| 17-22               | 25-30                          | Reserved                                             |  |  |  |  |  |  |  |  |

| 23                  | 31                             | INT2 – External Interrupt 2                          |  |  |  |  |  |  |  |  |

| 24                  | 32                             | U2RX <sup>(1)</sup> – UART2 Receiver                 |  |  |  |  |  |  |  |  |

| 25                  | 33                             | U2TX <sup>(1)</sup> – UART2 Transmitter              |  |  |  |  |  |  |  |  |

| 26-41               | 34-49                          | Reserved                                             |  |  |  |  |  |  |  |  |

| 42                  | 50                             | LVD – Low-Voltage Detect                             |  |  |  |  |  |  |  |  |

| 43-53               | 51-61                          | Reserved                                             |  |  |  |  |  |  |  |  |

|                     | Lowest N                       | Natural Order Priority                               |  |  |  |  |  |  |  |  |

**Note 1:** Only the dsPIC30F3013 has UART2 and the U2RX, U2TX interrupts. These locations are reserved for the dsPIC30F2011/2012/3012.

| TABLE       | 8-2: | dsP    | PIC30F | 2011/2    | 012/30 | 12 INT | ERRU   | PT COI     | NTROL  | LER R  | EGIS  | ER N    | IAP     |         |        |            |        |                     |

|-------------|------|--------|--------|-----------|--------|--------|--------|------------|--------|--------|-------|---------|---------|---------|--------|------------|--------|---------------------|

| SFR<br>Name | ADR  | Bit 15 | Bit 14 | Bit 13    | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8  | Bit 7  | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1      | Bit 0  | Reset State         |

| INTCON1     | 0080 | NSTDIS | _      | _         | _      | _      | OVATE  | OVBTE      | COVTE  | _      |       | _       | MATHERR | ADDRERR | STKERR | OSCFAIL    | _      | 0000 0000 0000 0000 |

| INTCON2     | 0082 | ALTIVT | DISI   |           | _      | I      | _      |            |        | _      |       | -       |         | _       | INT2EP | INT1EP     | INT0EP | 0000 0000 0000 0000 |

| IFS0        | 0084 | CNIF   | MI2CIF | SI2CIF    | NVMIF  | ADIF   | U1TXIF | U1RXIF     | SPI1IF | T3IF   | T2IF  | OC2IF   | IC2IF   | T1IF    | OC1IF  | IC1IF      | INTOIF | 0000 0000 0000 0000 |

| IFS1        | 0086 | _      | _      |           | _      | I      | _      |            |        | INT2IF |       | _       |         | _       | _      | _          | INT1IF | 0000 0000 0000 0000 |

| IFS2        | 0088 | _      | _      |           | _      |        | LVDIF  |            |        | _      |       | _       |         | _       | _      | _          | _      | 0000 0000 0000 0000 |

| IEC0        | 008C | CNIE   | MI2CIE | SI2CIE    | NVMIE  | ADIE   | U1TXIE | U1RXIE     | SPI1IE | T3IE   | T2IE  | OC2IE   | IC2IE   | T1IE    | OC1IE  | IC1IE      | INTOIE | 0000 0000 0000 0000 |

| IEC1        | 008E |        | _      |           |        |        | _      |            |        | INT2IE |       | _       |         | _       | _      | _          | INT1IE | 0000 0000 0000 0000 |

| IEC2        | 0090 |        |        |           |        |        | LVDIE  |            |        | _      |       | _       |         | —       | _      | —          |        | 0000 0000 0000 0000 |

| IPC0        | 0094 | _      | -      | T1IP<2:0> | •      |        | 0      | DC1IP<2:0  | >      | —      |       | IC1IP<  | 2:0>    | _       |        | NT0IP<2:0; | >      | 0100 0100 0100 0100 |

| IPC1        | 0096 | _      | 1      | [31P<2:0  | >      | I      |        | T2IP<2:0>  |        | _      |       | OC2IP<  | 2:0>    | _       |        | IC2IP<2:0> |        | 0100 0100 0100 0100 |

| IPC2        | 0098 | _      | A      | ADIP<2:0> | >      | _      | U      | 1TXIP<2:0  | )>     | —      |       | U1RXIP  | <2:0>   | _       | 5      | SPI1IP<2:0 | >      | 0100 0100 0100 0100 |

| IPC3        | 009A | _      | C      | CNIP<2:0  | >      | I      | N      | 112CIP<2:0 | )>     | _      |       | SI2CIP< | 2:0>    | _       | ١      | NVMIP<2:0  | >      | 0100 0100 0100 0100 |

| IPC4        | 009C | _      | _      |           | _      | I      | _      |            |        | _      |       | _       |         | _       |        | NT1IP<2:0> | >      | 0000 0000 0000 0100 |

| IPC5        | 009E | _      | IN     | T2IP<2:0  | >      |        | _      |            |        | _      |       | _       |         | _       | _      | _          | -      | 0100 0000 0000 0000 |

| IPC6        | 00A0 |        | _      |           |        |        | _      |            |        | _      | 1     | 0       | 0       | —       | 1      | 0          | 0      | 0000 0000 0100 0100 |

| IPC7        | 00A2 |        | -      | I         | -      |        | _      |            |        | -      |       | _       |         | —       | _      | _          | -      | 0000 0000 0000 0000 |

| IPC8        | 00A4 |        | _      | -         | _      |        | _      |            |        | _      | -     | -       |         | _       | _      | _          |        | 0000 0000 0000 0000 |

| IPC9        | 00A6 |        | -      | I         | -      | I      | _      | _          |        | -      |       | _       |         | _       | _      | _          | _      | 0000 0000 0000 0000 |

| IPC10       | 00A8 |        | _      | _         | _      |        | L      | VDIP<2:0   | >      | _      | _     | -       |         | —       | _      | _          | —      | 0000 0100 0000 0000 |

#### TABLE 8-2. dePIC30E2011/2012/3012 INTERRUPT CONTROLLER REGISTER MAP

**Legend:** u = uninitialized bit; — = unimplemented bit, read as '0'

Note: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields. Enabling an interrupt is accomplished via the respective timer interrupt enable bit, T1IE. The timer interrupt enable bit is located in the IEC0 Control register in the interrupt controller.

NOTES:

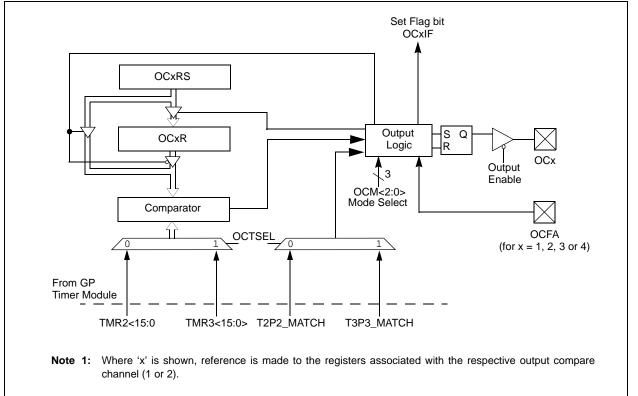

## 12.0 OUTPUT COMPARE MODULE

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

This section describes the output compare module and associated operational modes. The features provided by this module are useful in applications requiring operational modes, such as:

- Generation of Variable Width Output Pulses

- Power Factor Correction

Figure 12-1 depicts a block diagram of the output compare module.

The key operational features of the output compare module include:

- Timer2 and Timer3 Selection mode

- Simple Output Compare Match mode

- Dual Output Compare Match mode

- Simple PWM mode

- Output Compare During Sleep and Idle modes

- Interrupt on Output Compare/PWM Event

These operating modes are determined by setting the appropriate bits in the 16-bit OC1CON and OC2CON registers. The dsPIC30F2011/2012/3012/3013 devices have 2 compare channels.

OCxRS and OCxR in Figure 12-1 represent the Dual Compare registers. In the Dual Compare mode, the OCxR register is used for the first compare and OCxRS is used for the second compare.

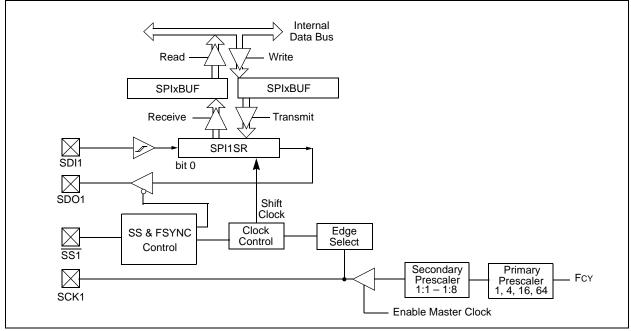

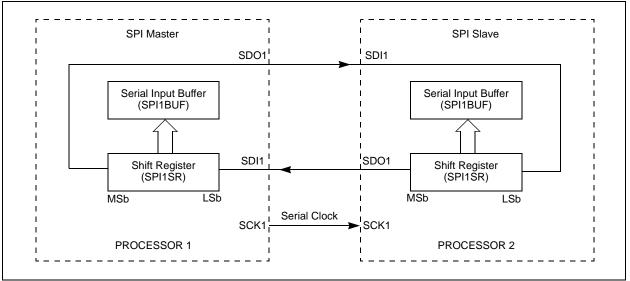

## FIGURE 13-1: SPI BLOCK DIAGRAM

Figure 13-2 depicts the a master/slave connection between two processors. In Master mode, the clock is generated by prescaling the system clock. Data is transmitted as soon as a value is written to SPI1BUF. The interrupt is generated at the middle of the transfer of the last bit.

In Slave mode, data is transmitted and received as external clock pulses appear on SCK. Again, the interrupt is generated when the last bit is latched. If SS1 control is enabled, then transmission and reception are enabled only when SS1 = low. The SDO1 output will be disabled in SS1 mode with SS1 high.

The clock provided to the module is (Fosc/4). This clock is then prescaled by the primary (PPRE<1:0>) and the secondary (SPRE<2:0>) prescale factors. The CKE bit determines whether transmit occurs on transition from active clock state to Idle clock state, or vice versa. The CKP bit selects the Idle state (high or low) for the clock.

#### 13.1.1 WORD AND BYTE COMMUNICATION

A control bit, MODE16 (SPI1CON<10>), allows the module to communicate in either 16-bit or 8-bit mode. 16-bit operation is identical to 8-bit operation except that the number of bits transmitted is 16 instead of 8.

The user software must disable the module prior to changing the MODE16 bit. The SPI module is reset when the MODE16 bit is changed by the user.

A basic difference between 8-bit and 16-bit operation is that the data is transmitted out of bit 7 of the SPI1SR for 8-bit operation, and data is transmitted out of bit 15 of the SPI1SR for 16-bit operation. In both modes, data is shifted into bit 0 of the SPI1SR.

## 13.1.2 SDO1 DISABLE

A control bit, DISSDO, is provided to the SPI1CON register to allow the SDO1 output to be disabled. This will allow the SPI module to be connected in an input only configuration. SDO1 can also be used for general purpose I/O.

## 13.2 Framed SPI Support

The module supports a basic framed SPI protocol in Master or Slave mode. The control bit, FRMEN, enables framed SPI support and causes the SS1 pin to perform the Frame Synchronization Pulse (FSYNC) function. The control bit, SPIFSD, determines whether the SS1 pin is an input or an output (i.e., whether the module receives or generates the Frame Synchronization Pulse). The frame pulse is an active-high pulse for a single SPI clock cycle. When Frame Synchronization is enabled, the data transmission starts only on the subsequent transmit edge of the SPI clock.

## 13.3 Slave Select Synchronization

The  $\overline{SS1}$  pin allows a Synchronous Slave mode. The SPI must be configured in SPI Slave mode with  $\overline{SS1}$  pin control enabled (SSEN = 1). When the  $\overline{SS1}$  pin is low, transmission and reception are enabled and the SDOx pin is driven. When  $\overline{SS1}$  pin goes high, the SDOx pin is no longer driven. Also, the SPI module is resynchronized, and all counters/control circuitry are reset. Therefore, when the  $\overline{SS1}$  pin is asserted low again, transmission/reception will begin at the MSb even if  $\overline{SS1}$  had been de-asserted in the middle of a transmit/receive.

### 13.4 SPI Operation During CPU Sleep Mode

During Sleep mode, the SPI module is shut down. If the CPU enters Sleep mode while an SPI transaction is in progress, then the transmission and reception is aborted.

The transmitter and receiver will stop in Sleep mode. However, register contents are not affected by entering or exiting Sleep mode.

### 13.5 SPI Operation During CPU Idle Mode

When the device enters Idle mode, all clock sources remain functional. The SPISIDL bit (SPI1STAT<13>) selects if the SPI module will stop or continue on idle. If SPISIDL = 0, the module will continue to operate when the CPU enters Idle mode. If SPISIDL = 1, the module will stop when the CPU enters Idle mode.

## 14.12.2 I<sup>2</sup>C MASTER RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (I2CCON<3>). The I<sup>2</sup>C module must be Idle before the RCEN bit is set, otherwise the RCEN bit will be disregarded. The Baud Rate Generator begins <u>counting</u> and on each rollover, the state of the SCL pin ACK and data are shifted into the I2CRSR on the rising edge of each clock.

#### 14.12.3 BAUD RATE GENERATOR

In I<sup>2</sup>C Master mode, the reload value for the BRG is located in the I2CBRG register. When the BRG is loaded with this value, the BRG counts down to '0' and stops until another reload has taken place. If clock arbitration is taking place, for instance, the BRG is reloaded when the SCL pin is sampled high.

As per the I<sup>2</sup>C standard, FSCK may be 100 kHz or 400 kHz. However, the user can specify any baud rate up to 1 MHz. I2CBRG values of '0' or '1' are illegal.

### EQUATION 14-1: SERIAL CLOCK RATE

$I2CBRG = \left(\frac{FCY}{FSCL} - \frac{FCY}{1,111,111}\right) - 1$

## 14.12.4 CLOCK ARBITRATION

Clock arbitration occurs when the master de-asserts the SCL pin (SCL allowed to float high) during any receive, transmit, or Restart/Stop condition. When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of I2CBRG and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device.

#### 14.12.5 MULTI-MASTER COMMUNICATION, BUS COLLISION, AND BUS ARBITRATION

Multi-master operation support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA by letting SDA float high while another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = 0, then a bus collision has taken place. The master will set the MI2CIF pulse and reset the master portion of the  $I^2C$  port to its Idle state.

If a transmit was in progress when the bus collision occurred, the transmission is halted, the TBF flag is cleared, the SDA and SCL lines are de-asserted and a value can now be written to I2CTRN. When the user services the  $I^2C$  master event Interrupt Service Routine, if the  $I^2C$  bus is free (i.e., the P bit is set), the user can resume communication by asserting a Start condition.

If a Start, Restart, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are de-asserted, and the respective control bits in the I2CCON register are cleared to '0'. When the user services the bus collision Interrupt Service Routine, and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins, and if a Stop condition occurs, the MI2CIF bit will be set.

A write to the I2CTRN will start the transmission of data at the first data bit regardless of where the transmitter left off when bus collision occurred.

In a multi-master environment, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$ bus can be taken when the P bit is set in the I2CSTAT register, or the bus is Idle and the S and P bits are cleared.

## 14.13 I<sup>2</sup>C Module Operation During CPU Sleep and Idle Modes

#### 14.13.1 I<sup>2</sup>C OPERATION DURING CPU SLEEP MODE

When the device enters Sleep mode, all clock sources to the module are shut down and stay at logic '0'. If Sleep occurs in the middle of a transmission and the state machine is partially into a transmission as the clocks stop, then the transmission is aborted. Similarly, if Sleep occurs in the middle of a reception, then the reception is aborted.

#### 14.13.2 I<sup>2</sup>C OPERATION DURING CPU IDLE MODE

For the I<sup>2</sup>C, the I2CSIDL bit selects if the module will stop on Idle or continue on Idle. If I2CSIDL = 0, the module will continue operation on assertion of the Idle mode. If I2CSIDL = 1, the module will stop on Idle.

The configuration procedures in the next section provide the required setup values for the conversion speeds above 100 ksps.

#### 16.7.1 200 KSPS CONFIGURATION GUIDELINE

The following configuration items are required to achieve a 200 ksps conversion rate.

- Comply with conditions provided in Table 16-1.

- Connect external VREF+ and VREF- pins following the recommended circuit shown in Figure 16-2.

- Set SSRC<2.0> = 111 in the ADCON1 register to enable the auto convert option.

- Enable automatic sampling by setting the ASAM control bit in the ADCON1 register.

- Write the SMPI<3.0> control bits in the ADCON2 register for the desired number of conversions between interrupts.

- Configure the ADC clock period to be:

$$\frac{1}{(14+1) \times 200,000} = 334 \text{ ns}$$

by writing to the ADCS<5:0> control bits in the ADCON3 register.

• Configure the sampling time to be 1 TAD by writing: SAMC<4:0> = 00001.

The following figure shows the timing diagram of the ADC running at 200 ksps. The TAD selection in conjunction with the guidelines described above allows a conversion speed of 200 ksps. See Example 16-1 for code example.

## 16.8 A/D Acquisition Requirements

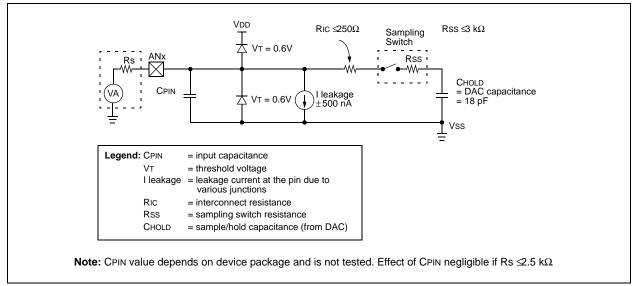

The analog input model of the 12-bit ADC is shown in Figure 16-3. The total sampling time for the A/D is a function of the internal amplifier settling time and the holding capacitor charge time.

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the voltage level on the analog input pin. The impedance source (Rs), the interconnect impedance (RIC) and the internal sampling switch (Rss) impedance combine to directly affect the time required to charge the capacitor CHOLD. The combined impedance of the analog sources must therefore be small enough to fully charge the holding capacitor within the chosen sample time. To minimize the effects of pin leakage currents on the accuracy of the ADC, the maximum recommended source impedance, Rs, is 2.5 k $\Omega$  After the analog input channel is selected (changed), this sampling function must be completed prior to starting the conversion. The internal holding capacitor will be in a discharged state prior to each sample operation.

#### FIGURE 16-3: 12-BIT A/D CONVERTER ANALOG INPUT MODEL

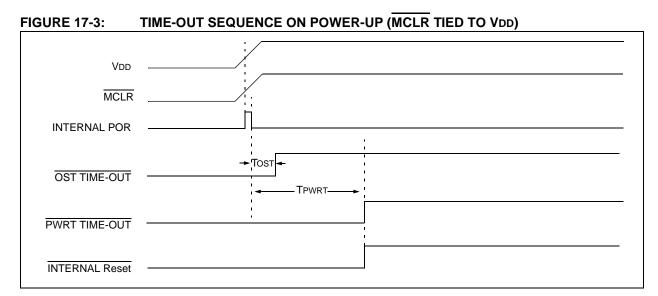

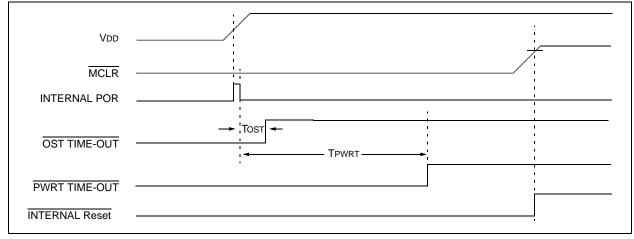

## FIGURE 17-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

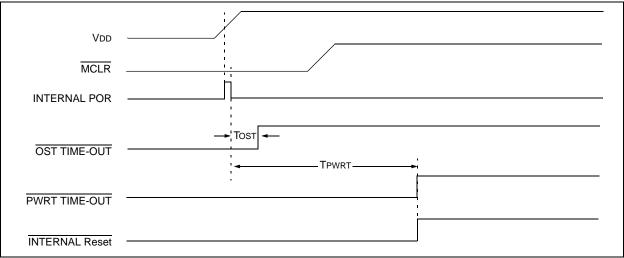

## FIGURE 17-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

## 18.0 INSTRUCTION SET SUMMARY

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "dsPIC30F Programmer's Reference Manual" (DS70030).

The dsPIC30F instruction set adds many enhancements to the previous PIC<sup>®</sup> MCU instruction sets, while maintaining an easy migration from PIC MCU instruction sets.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word divided into an 8-bit opcode which specifies the instruction type, and one or more operands which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into five basic categories:

- Word or byte-oriented operations

- Bit-oriented operations

- · Literal operations

- DSP operations

- · Control operations

Table 18-1 shows the general symbols used in describing the instructions.

The dsPIC30F instruction set summary in Table 18-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand which is typically a register 'Wb' without any address modifier

- The second source operand which is typically a register 'Ws' with or without an address modifier

- The destination of the result which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- The file register specified by the value 'f'

- The destination, which could either be the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement may use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by the value of 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand which is a register 'Wb' without any address modifier

- The second source operand which is a literal value

- The destination of the result (only if not the same as the first source operand) which is typically a register 'Wd' with or without an address modifier

The MAC class of DSP instructions may use some of the following operands:

- The accumulator (A or B) to be used (required operand)

- The W registers to be used as the two operands

- The X and Y address space prefetch operations

- The X and Y address space prefetch destinations

- The accumulator write-back destination

The other DSP instructions do not involve any multiplication, and may include:

- The accumulator to be used (required)

- The source or destination operand (designated as Wso or Wdo, respectively) with or without an address modifier

- The amount of shift specified by a W register 'Wn' or a literal value

The control instructions may use some of the following operands:

- A program memory address

- The mode of the table read and table write instructions

| Field | Description                                                                                                                                                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wb    | Base W register ∈ {W0W15}                                                                                                                                                                                                      |

| Wd    | Destination W register ∈ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                                                                                                                                                              |

| Wdo   | Destination W register ∈<br>{ Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] }                                                                                                                                           |

| Wm,Wn | Dividend, Divisor working register pair (direct addressing)                                                                                                                                                                    |

| Wm*Wm | Multiplicand and Multiplier working register pair for Square instructions ∈ {W4*W4,W5*W5,W6*W6,W7*W7}                                                                                                                          |

| Wm*Wn | Multiplicand and Multiplier working register pair for DSP instructions ∈<br>{W4*W5,W4*W6,W4*W7,W5*W6,W5*W7,W6*W7}                                                                                                              |

| Wn    | One of 16 working registers ∈ {W0W15}                                                                                                                                                                                          |

| Wnd   | One of 16 destination working registers ∈ {W0W15}                                                                                                                                                                              |

| Wns   | One of 16 source working registers ∈ {W0W15}                                                                                                                                                                                   |

| WREG  | W0 (working register used in file register instructions)                                                                                                                                                                       |

| Ws    | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                                                                                                                                                                   |

| Wso   | Source W register ∈<br>{ Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }                                                                                                                                                |

| Wx    | X data space prefetch address register for DSP instructions<br>∈ {[W8]+=6, [W8]+=4, [W8]+=2, [W8], [W8]-=6, [W8]-=4, [W8]-=2,<br>[W9]+=6, [W9]+=4, [W9]+=2, [W9], [W9]-=6, [W9]-=4, [W9]-=2,<br>[W9+W12],none}                 |

| Wxd   | X data space prefetch destination register for DSP instructions ∈ {W4W7}                                                                                                                                                       |

| Wy    | Y data space prefetch address register for DSP instructions<br>∈ {[W10]+=6, [W10]+=4, [W10]+=2, [W10], [W10]-=6, [W10]-=4, [W10]-=2,<br>[W11]+=6, [W11]+=4, [W11]+=2, [W11], [W11]-=6, [W11]-=4, [W11]-=2,<br>[W11+W12], none} |

| Wyd   | Y data space prefetch destination register for DSP instructions ∈ {W4W7}                                                                                                                                                       |

#### TABLE 18-1: SYMBOLS USED IN OPCODE DESCRIPTIONS (CONTINUED)

## 19.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

## 19.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

## 19.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

## 19.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

### 19.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

## 20.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC30F electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

For detailed information about the dsPIC30F architecture and core, refer to the "dsPIC30F Family Reference Manual" (DS70046).

Absolute maximum ratings for the dsPIC30F family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

## Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                        | 40°C to +125°C       |

|-----------------------------------------------------------------------|----------------------|

| Storage temperature                                                   | 65°C to +150°C       |

| Voltage on any pin with respect to Vss (except VDD and MCLR) (Note 1) | 0.3V to (VDD + 0.3V) |

| Voltage on VDD with respect to Vss                                    | 0.3V to +5.5V        |

| Voltage on MCLR with respect to Vss                                   | 0V to +13.25V        |

| Maximum current out of Vss pin                                        | 300 mA               |

| Maximum current into VDD pin (Note 2)                                 | 250 mA               |

| Input clamp current, Iк (VI < 0 or VI > VDD)                          | ±20 mA               |

| Output clamp current, IOK (VO < 0 or VO > VDD)                        | ±20 mA               |

| Maximum output current sunk by any I/O pin                            | 25 mA                |

| Maximum output current sourced by any I/O pin                         | 25 mA                |

| Maximum current sunk by all ports                                     | 200 mA               |

| Maximum current sourced by all ports (Note 2)                         | 200 mA               |

**Note 1:** Voltage spikes below Vss at the MCLR/VPP pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR/VPP pin, rather than pulling this pin directly to Vss.

2: Maximum allowable current is a function of device maximum power dissipation. See Table 20-2 for PDMAX.

**†NOTICE:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

**Note:** All peripheral electrical characteristics are specified. For exact peripherals available on specific devices, please refer to the dsPIC30F2011/2012/3012/3013 Sensor Family table on page 4 of this data sheet.

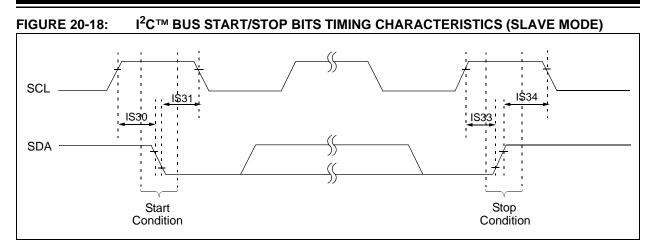

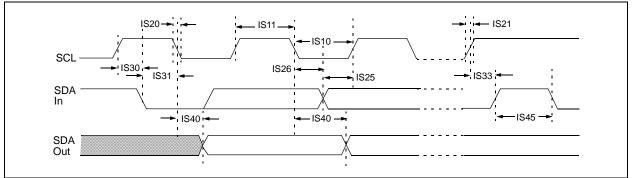

## TABLE 20-34: I<sup>2</sup>C<sup>™</sup> BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

| AC CHA       | RACTERIS | STICS           | Standard Operating Conditions: 2.5V to 5.5V   (unless otherwise stated)   Operating temperature -40°C ≤TA ≤+85°C for Industrial   -40°C ≤TA ≤+125°C for Extended |             |      |       |                                             |  |  |  |  |

|--------------|----------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|-------|---------------------------------------------|--|--|--|--|

| Param<br>No. | Symbol   | Charac          | teristic                                                                                                                                                         | Min         | Max  | Units | Conditions                                  |  |  |  |  |

| IS10         | TLO:SCL  | Clock Low Time  | 100 kHz mode                                                                                                                                                     | 4.7         | _    | μs    | Device must operate at a minimum of 1.5 MHz |  |  |  |  |

|              |          |                 | 400 kHz mode                                                                                                                                                     | 1.3         | —    | μs    | Device must operate at a minimum of 10 MHz. |  |  |  |  |

|              |          |                 | 1 MHz mode <sup>(1)</sup>                                                                                                                                        | 0.5         | —    | μs    |                                             |  |  |  |  |

| IS11         | THI:SCL  | Clock High Time | 100 kHz mode                                                                                                                                                     | 4.0         | —    | μs    | Device must operate at a minimum of 1.5 MHz |  |  |  |  |

|              |          |                 | 400 kHz mode                                                                                                                                                     | 0.6         | _    | μs    | Device must operate at a minimum of 10 MHz  |  |  |  |  |

|              |          |                 | 1 MHz mode <sup>(1)</sup>                                                                                                                                        | 0.5         | —    | μs    |                                             |  |  |  |  |

| IS20         | TF:SCL   | SDA and SCL     | 100 kHz mode                                                                                                                                                     | —           | 300  | ns    | CB is specified to be from                  |  |  |  |  |

|              |          | Fall Time       | 400 kHz mode                                                                                                                                                     | 20 + 0.1 Св | 300  | ns    | 10 to 400 pF                                |  |  |  |  |

|              |          |                 | 1 MHz mode <sup>(1)</sup>                                                                                                                                        | —           | 100  | ns    |                                             |  |  |  |  |

| IS21         | TR:SCL   | SDA and SCL     | 100 kHz mode                                                                                                                                                     | —           | 1000 | ns    | CB is specified to be from                  |  |  |  |  |

|              |          | Rise Time       | 400 kHz mode                                                                                                                                                     | 20 + 0.1 Св | 300  | ns    | 10 to 400 pF                                |  |  |  |  |

|              |          |                 | 1 MHz mode <sup>(1)</sup>                                                                                                                                        | —           | 300  | ns    |                                             |  |  |  |  |

**Note 1:** Maximum pin capacitance = 10 pF for all  $I^2C^{TM}$  pins (for 1 MHz mode only).

| AC CHARACTERISTICS |                 |                                                          |           | Standard Operating Conditions: 2.7V to 5.5V   (unless otherwise stated)   Operating temperature-40°C ≤TA ≤+85°C for Industrial   -40°C ≤TA ≤+125°C for Extended |            |       |                                                                 |  |  |  |  |

|--------------------|-----------------|----------------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|-----------------------------------------------------------------|--|--|--|--|

| Param<br>No.       | Symbol          | Characteristic                                           | Min.      | Тур                                                                                                                                                             | Max.       | Units | Conditions                                                      |  |  |  |  |

|                    |                 | Cloc                                                     | k Parame  | ters                                                                                                                                                            |            |       |                                                                 |  |  |  |  |

| AD50               | TAD             | A/D Clock Period                                         | 334       | —                                                                                                                                                               | _          | ns    | VDD = 3-5.5V (Note 1)                                           |  |  |  |  |

| AD51               | tRC             | A/D Internal RC Oscillator Period                        | 1.2       | 1.5                                                                                                                                                             | 1.8        | μs    |                                                                 |  |  |  |  |

|                    |                 | Con                                                      | version R | ate                                                                                                                                                             |            |       |                                                                 |  |  |  |  |

| AD55               | tCONV           | Conversion Time                                          | _         | 14 Tad                                                                                                                                                          |            | ns    |                                                                 |  |  |  |  |

| AD56a              | FCNV            | Throughput Rate                                          | _         | 200                                                                                                                                                             | _          | ksps  | VDD = VREF = 5V,<br>Industrial temperature                      |  |  |  |  |

| AD56b              | FCNV            | Throughput Rate                                          |           | 100                                                                                                                                                             | _          | ksps  | VDD = VREF = 5V,<br>Extended temperature                        |  |  |  |  |

| AD57               | TSAMP           | Sampling Time                                            | 1 Tad     | —                                                                                                                                                               | —          | ns    | $V_{DD}$ = 3-5.5V source<br>resistance<br>Rs = 0-2.5 k $\Omega$ |  |  |  |  |

|                    |                 | Timin                                                    | g Parame  | eters                                                                                                                                                           |            |       |                                                                 |  |  |  |  |

| AD60               | tPCS            | Conversion Start from Sample<br>Trigger                  | —         | 1 Tad                                                                                                                                                           | _          | ns    |                                                                 |  |  |  |  |

| AD61               | tPSS            | Sample Start from Setting<br>Sample (SAMP) Bit           | 0.5 Tad   | —                                                                                                                                                               | 1.5<br>Tad | ns    |                                                                 |  |  |  |  |

| AD62               | tCSS            | Conversion Completion to<br>Sample Start (ASAM = 1)      | _         | 0.5 Tad                                                                                                                                                         | _          | ns    |                                                                 |  |  |  |  |

| AD63               | tDPU <b>(2)</b> | Time to Stabilize Analog Stage<br>from A/D Off to A/D On | _         | —                                                                                                                                                               | 20         | μs    |                                                                 |  |  |  |  |

#### TABLE 20-37: 12-BIT A/D CONVERSION TIMING REQUIREMENTS

**Note 1:** Because the sample caps will eventually lose charge, clock rates below 10 kHz can affect linearity performance, especially at elevated temperatures.

**2:** tDPU is the time required for the ADC module to stabilize when it is turned on (ADCON1<ADON> = 1). During this time the ADC result is indeterminate.

## **Revision G (November 2010)**

This revision includes minor typographical and formatting changes throughout the data sheet text.

The major changes are referenced by their respective section in Table A-1.

#### TABLE A-1: MAJOR SECTION UPDATES

| Section Name                                             | Update Description                                                                                                                                                        |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "High-Performance, 16-Bit Digital<br>Signal Controllers" | Added Note 1 to all QFN pin diagrams (see "Pin Diagrams").                                                                                                                |

| Section 1.0 "Device Overview"                            | Updated the Pinout I/O Descriptions for AVDD and AVSS (see Table 1-1).                                                                                                    |

| Section 17.0 "System Integration"                        | Added a shaded note on OSCTUN functionality in <b>Section 17.2.5</b> "Fast RC Oscillator (FRC)".                                                                          |

| Section 20.0 "Electrical<br>Characteristics"             | Updated the maximum value for parameter DI19 and the minimum value for parameter DI29 in the I/O Pin Input Specifications (see Table 20-8).                               |

|                                                          | Removed parameter D136 and updated the minimum, typical, maximum, and conditions for parameters D122 and D134 in the Program and EEPROM specifications (see Table 20-12). |

|                                                          | Renamed parameter AD56 to AD56a and added parameter AD56b to the 12-bit A/D Conversion Timing Requirements (see Table 20-37).                                             |

| "Product Identification System"                          | Added the "MM" package definition.                                                                                                                                        |

| Reset                       | 165 |

|-----------------------------|-----|

| Simple OC/PWM Mode          | 171 |

| SPI Module                  |     |

| Master Mode (CKE = 0)       | 172 |

| Master Mode (CKE = 1)       | 173 |

| Slave Mode (CKE = 0)        | 174 |

| Slave Mode (CKE = 1)        | 176 |

| Type A Timer External Clock |     |

| Type B Timer External Clock |     |

| Type C Timer External Clock |     |

| Watchdog Timer              |     |

| Timing Specifications       |     |

| PLL Clock                   |     |

| Trap Vectors                | 69  |

## U

| UART Module                                  |    |

|----------------------------------------------|----|

| Address Detect Mode 10                       | )9 |

| Auto-Baud Support10                          | )9 |

| Baud Rate Generator10                        | )9 |

| Enabling and Setting Up10                    | )7 |

| Framing Error (FERR)10                       | )9 |

| Idle Status 10                               | )9 |

| Loopback Mode10                              | )9 |

| Operation During CPU Sleep and Idle Modes 11 | 0  |

| Overview                                     | )5 |

| Parity Error (PERR)10                        | )9 |

| Receive Break10                              |    |

| Receive Buffer (UxRXB)10                     | )8 |

| Receive Buffer Overrun Error (OERR Bit) 10   | )8 |

| Receive Interrupt10                          | )8 |

| Receiving Data10                             | )8 |

| Receiving in 8-bit or 9-bit Data Mode10      |    |

| Reception Error Handling10                   | )8 |

| Transmit Break10                             | )8 |

| Transmit Buffer (UxTXB)10                    |    |

| Transmit Interrupt10                         | )8 |

| Transmitting Data10                          | )7 |

| Transmitting in 8-bit Data Mode10            | )7 |

| Transmitting in 9-bit Data Mode10            | )7 |

| UART1 Register Map11                         | 1  |

| UART2 Register Map11                         | 1  |

| UART Operation                               |    |

| Idle Mode11                                  | 0  |

| Sleep Mode11                                 | 0  |

| Unit ID Locations                            | 23 |

| Universal Asynchronous Receiver Transmitter  |    |

| (UART) Module 10                             | )5 |

| w                                            |    |

|                                              |    |

| Wake-up from Sleep                           |    |

| Wake-up from Sleep and Idle                  | 0  |

| Watchdog Timer                               | _  |

| Timing Characteristics16                     |    |

| Timing Requirements                          |    |

| Watchdog Timer (WDT) 123, 13                 |    |

| Enabling and Disabling13                     |    |

| Operation13                                  |    |

| WWW Address                                  |    |

| WWW, On-Line Support                         | 9  |