Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                         |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 20 MIPS                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 12                                                                            |

| Program Memory Size        | 24KB (8K x 24)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 1K x 8                                                                        |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x12b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 18-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f3012-20e-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

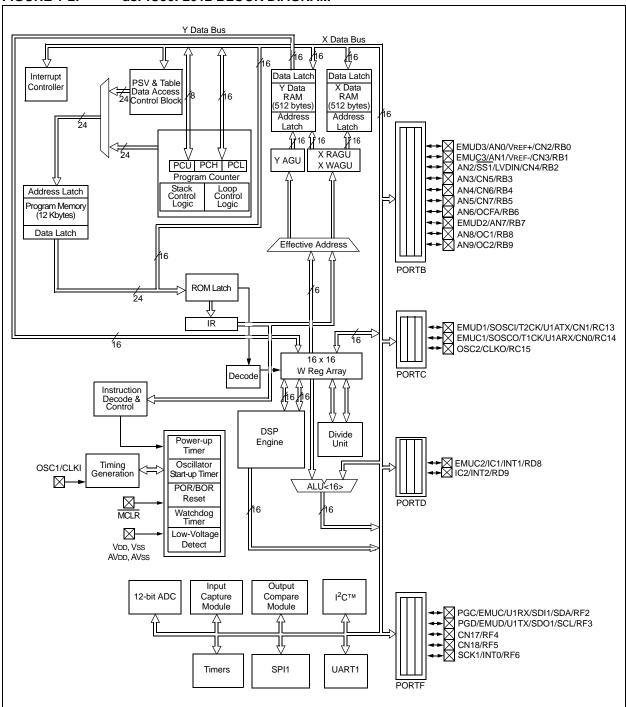

## 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

This data sheet contains information specific to the dsPIC30F2011, dsPIC30F2012, dsPIC30F3012 and dsPIC30F3013 Digital Signal Controllers (DSC). These devices contain extensive Digital Signal Processor (DSP) functionality within a high-performance 16-bit microcontroller (MCU) architecture.

The following block diagrams depict the architecture for these devices:

- Figure 1-1 illustrates the dsPIC30F2011

- Figure 1-2 illustrates the dsPIC30F2012

- Figure 1-3 illustrates the dsPIC30F3012

- Figure 1-4 illustrates the dsPIC30F3013

Following the block diagrams, Table 1-1 relates the I/O functions to pinout information.

Table 1-1 provides a brief description of device I/O pinouts and the functions that may be multiplexed to a port pin. Multiple functions may exist on one port pin. When multiplexing occurs, the peripheral module's functional requirements may force an override of the data direction of the port pin.

| Pin Name                                                           | Pin<br>Type                            | Buffer<br>Type                               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|--------------------------------------------------------------------|----------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| AN0 - AN9                                                          |                                        | Analog                                       | Analog input channels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| AVdd                                                               | Р                                      | Р                                            | Positive supply for analog module. This pin must be connected at all times.                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| AVss                                                               | Р                                      | Р                                            | Ground reference for analog module. This pin must be connected at all times.                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| CLKI<br>CLKO                                                       | I<br>O                                 | ST/CMOS<br>—                                 | External clock source input. Always associated with OSC1 pin function.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in RC and EC modes. Always associated<br>with OSC2 pin function.                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| CN0 - CN7                                                          | Ι                                      | ST                                           | Input change notification inputs.<br>Can be software programmed for internal weak pull-ups on all inputs.                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| EMUD<br>EMUC<br>EMUD1<br>EMUC1<br>EMUC2<br>EMUC2<br>EMUD3<br>EMUC3 | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST | ICD Primary Communication Channel data input/output pin.<br>ICD Primary Communication Channel clock input/output pin.<br>ICD Secondary Communication Channel data input/output pin.<br>ICD Secondary Communication Channel clock input/output pin.<br>ICD Tertiary Communication Channel data input/output pin.<br>ICD Tertiary Communication Channel clock input/output pin.<br>ICD Quaternary Communication Channel clock input/output pin.<br>ICD Quaternary Communication Channel clock input/output pin. |  |  |  |  |  |  |

| IC1 - IC2                                                          | I                                      | ST                                           | Capture inputs 1 through 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| INT0<br>INT1<br>INT2                                               | <br> <br>                              | ST<br>ST<br>ST                               | External interrupt 0.<br>External interrupt 1.<br>External interrupt 2.                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| LVDIN                                                              | I                                      | Analog                                       | Low-Voltage Detect Reference Voltage Input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| MCLR                                                               | I/P                                    | ST                                           | Master Clear (Reset) input or programming voltage input. This pin is an active-low Reset to the device.                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| OC1-OC2<br>OCFA                                                    | 0<br>                                  | ST                                           | Compare outputs 1 through 2.<br>Compare Fault A input.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| OSC1                                                               | I                                      | ST/CMOS                                      | Oscillator crystal input. ST buffer when configured in RC mode; CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| OSC2                                                               | I/O                                    | _                                            | otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| PGD                                                                | I/O                                    | ST                                           | In-Circuit Serial Programming™ data input/output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| PGC                                                                | l                                      | ST                                           | In-Circuit Serial Programming clock input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| RB0 - RB9                                                          | I/O                                    | ST                                           | PORTB is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| RC13 - RC15                                                        | I/O                                    | ST                                           | PORTC is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| RD0,<br>RD8-RD9                                                    | I/O                                    | ST                                           | PORTD is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| RF2 - RF5                                                          | I/O                                    | ST                                           | PORTF is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| SCK1<br>SDI1<br>SDO1<br>SS1                                        | I/O<br>I<br>O<br>I                     | ST<br>ST<br>—<br>ST                          | Synchronous serial clock input/output for SPI1.<br>SPI1 Data In.<br>SPI1 Data Out.<br>SPI1 Slave Synchronization.                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Legend: CM<br>ST<br>I                                              | = S                                    |                                              | ole input or outputAnalog =Analog inputinput with CMOS levelsO=OutputP=Power                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS

NOTES:

The SA and SB bits are modified each time data passes through the adder/subtracter but can only be cleared by the user. When set, they indicate that the accumulator has overflowed its maximum range (bit 31 for 32-bit saturation or bit 39 for 40-bit saturation) and will be saturated if saturation is enabled. When saturation is not enabled, SA and SB default to bit 39 overflow and thus indicate that a catastrophic overflow has occurred. If the COVTE bit in the INTCON1 register is set, SA and SB bits generate an arithmetic warning trap when saturation is disabled.

The overflow and saturation Status bits can optionally be viewed in the STATUS register (SR) as the logical OR of OA and OB (in bit OAB) and the logical OR of SA and SB (in bit SAB). This allows programmers to check one bit in the STATUS register to determine if either accumulator has overflowed, or one bit to determine if either accumulator has saturated. This would be useful for complex number arithmetic which typically uses both the accumulators.

The device supports three saturation and overflow modes:

1. Bit 39 Overflow and Saturation:

When bit 39 overflow and saturation occurs, the saturation logic loads the maximally positive 9.31 (0x7FFFFFFFF) or maximally negative 9.31 value (0x800000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user. This is referred to as 'super saturation' and provides protection against erroneous data or unexpected algorithm problems (e.g., gain calculations).

- 2. Bit 31 Overflow and Saturation: When bit 31 overflow and saturation occurs, the saturation logic then loads the maximally positive 1.31 value (0x007FFFFFF) or maximally negative 1.31 value (0x0080000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user. When this Saturation mode is in effect, the guard bits are not used, so the OA, OB or OAB bits are never set.

- 3. Bit 39 Catastrophic Overflow:

The bit 39 overflow Status bit from the adder is used to set the SA or SB bit which remains set until cleared by the user. No saturation operation is performed and the accumulator is allowed to overflow (destroying its sign). If the COVTE bit in the INTCON1 register is set, a catastrophic overflow can initiate a trap exception.

### 2.4.2.2 Accumulator 'Write-Back'

The MAC class of instructions (with the exception of MPY, MPY.N, ED and EDAC) can optionally write a rounded version of the high word (bits 31 through 16) of the accumulator that is not targeted by the instruction into data space memory. The write is performed across the X bus into combined X and Y address space. The following addressing modes are supported:

1. W13, Register Direct:

The rounded contents of the non-target accumulator are written into W13 as a 1.15 fraction.

[W13]+ = 2, Register Indirect with Post-Increment: The rounded contents of the non-target accumulator are written into the address pointed to by W13 as a 1.15 fraction. W13 is then incremented by 2 (for a word write).

### 2.4.2.3 Round Logic

The round logic is a combinational block which performs a conventional (biased) or convergent (unbiased) round function during an accumulator write (store). The Round mode is determined by the state of the RND bit in the CORCON register. It generates a 16-bit, 1.15 data value, which is passed to the data space write saturation logic. If rounding is not indicated by the instruction, a truncated 1.15 data value is stored and the least significant word (lsw) is simply discarded.

Conventional rounding takes bit 15 of the accumulator, zero-extends it and adds it to the ACCxH word (bits 16 through 31 of the accumulator). If the ACCxL word (bits 0 through 15 of the accumulator) is between 0x8000 and 0xFFFF (0x8000 included), ACCxH is incremented. If ACCxL is between 0x0000 and 0x7FFF, ACCxH is left unchanged. A consequence of this algorithm is that over a succession of random rounding operations, the value tends to be biased slightly positive.

Convergent (or unbiased) rounding operates in the same manner as conventional rounding, except when ACCxL equals 0x8000. If this is the case, the LSb (bit 16 of the accumulator) of ACCxH is examined. If it is '1', ACCxH is incremented. If it is '0', ACCxH is not modified. Assuming that bit 16 is effectively random in nature, this scheme will remove any rounding bias that may accumulate.

The SAC and SAC.R instructions store either a truncated (SAC) or rounded (SAC.R) version of the contents of the target accumulator to data memory via the X bus (subject to data saturation, see **Section 2.4.2.4 "Data Space Write Saturation"**). Note that for the MAC class of instructions, the accumulator write-back operation functions in the same manner, addressing combined MCU (X and Y) data space though the X bus. For this class of instructions, the data is always subject to rounding.

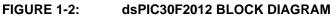

|                          | Access                           | Program Space Address  |          |               |               |     |  |  |  |

|--------------------------|----------------------------------|------------------------|----------|---------------|---------------|-----|--|--|--|

| Access Type              | Space                            | <23>                   | <22:16>  | <15>          | <14:1>        | <0> |  |  |  |

| Instruction Access       | User                             | 0 PC<22:1>             |          |               |               | 0   |  |  |  |

| TBLRD/TBLWT              | User<br>(TBLPAG<7> = 0)          | TBL                    | PAG<7:0> | Data EA<15:0> |               |     |  |  |  |

| TBLRD/TBLWT              | Configuration<br>(TBLPAG<7> = 1) | TBLPAG<7:0>            |          |               | Data EA<15:0> |     |  |  |  |

| Program Space Visibility | User                             | 0 PSVPAG<7:0> Data EA< |          |               | 4:0>          |     |  |  |  |

#### TABLE 3-1: PROGRAM SPACE ADDRESS CONSTRUCTION

#### FIGURE 3-2: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

NOTES:

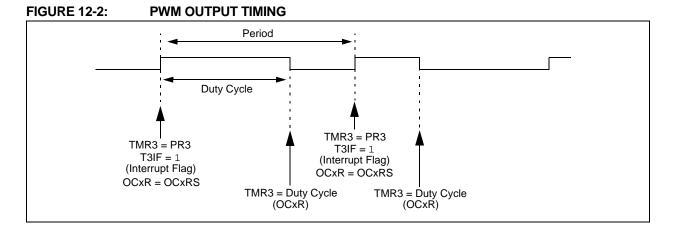

### 12.4.2 PWM PERIOD

The PWM period is specified by writing to the PRx register. The PWM period can be calculated using Equation 12-1.

#### EQUATION 12-1:

$PWM \ period = [(PRx) + 1] \cdot 4 \cdot Tosc \cdot$  $(TMRx \ prescale \ value)$

PWM frequency is defined as 1/[PWM period].

When the selected TMRx is equal to its respective period register, PRx, the following four events occur on the next increment cycle:

- TMRx is cleared.

- The OCx pin is set.

- Exception 1: If PWM duty cycle is 0x0000, the OCx pin remains low.

- Exception 2: If duty cycle is greater than PRx, the pin remains high.

- The PWM duty cycle is latched from OCxRS into OCxR.

- The corresponding timer interrupt flag is set.

See Figure 12-2 for key PWM period comparisons. Timer3 is referred to in Figure 12-2 for clarity.

## TABLE 12-1: OUTPUT COMPARE REGISTER MAP

| SFR Name | Addr.                                          | Bit 15                           | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8               | Bit 7               | Bit 6               | Bit 5 | Bit 4 | Bit 3  | Bit 2    | Bit 1    | Bit 0 | Reset State         |

|----------|------------------------------------------------|----------------------------------|--------|--------|--------|--------|--------|-------|---------------------|---------------------|---------------------|-------|-------|--------|----------|----------|-------|---------------------|

| OC1RS    | OC1RS 0180 Output Compare 1 Secondary Register |                                  |        |        |        |        |        |       |                     |                     | 0000 0000 0000 0000 |       |       |        |          |          |       |                     |

| OC1R     | OC1R 0182 Output Compare 1 Main Register       |                                  |        |        |        |        |        |       | 0000 0000 0000 0000 |                     |                     |       |       |        |          |          |       |                     |

| OC1CON   | 0184                                           | -                                | _      | OCSIDL |        |        | _      |       |                     | _                   | _                   | _     | OCFLT | OCTSEL | OCM<2:0> |          |       | 0000 0000 0000 0000 |

| OC2RS    | 0186 Output Compare 2 Secondary Register       |                                  |        |        |        |        |        |       |                     | 0000 0000 0000 0000 |                     |       |       |        |          |          |       |                     |

| OC2R     | 0188                                           | 3 Output Compare 2 Main Register |        |        |        |        |        |       | 0000 0000 0000 0000 |                     |                     |       |       |        |          |          |       |                     |

| OC2CON   | 018A                                           | -                                | _      | OCSIDL | —      | _      | _      | _     | _                   |                     |                     |       | OCFLT | OCTSEL |          | OCM<2:0> | >     | 0000 0000 0000 0000 |

Legend: — = unimplemented bit, read as '0'

Note: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

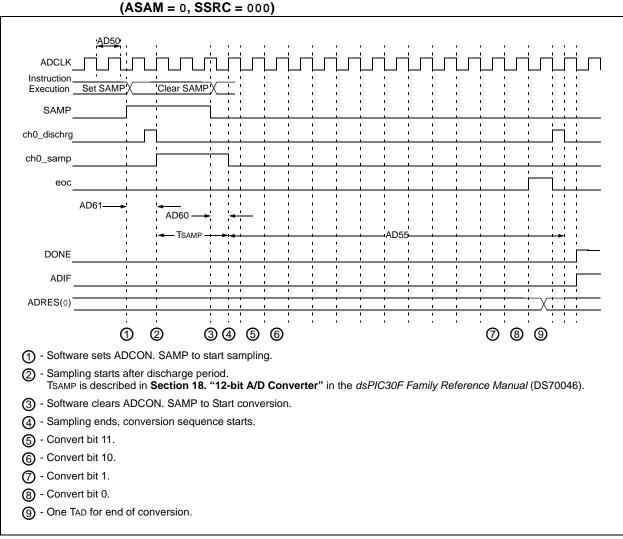

The configuration procedures in the next section provide the required setup values for the conversion speeds above 100 ksps.

#### 16.7.1 200 KSPS CONFIGURATION GUIDELINE

The following configuration items are required to achieve a 200 ksps conversion rate.

- Comply with conditions provided in Table 16-1.

- Connect external VREF+ and VREF- pins following the recommended circuit shown in Figure 16-2.

- Set SSRC<2.0> = 111 in the ADCON1 register to enable the auto convert option.

- Enable automatic sampling by setting the ASAM control bit in the ADCON1 register.

- Write the SMPI<3.0> control bits in the ADCON2 register for the desired number of conversions between interrupts.

- Configure the ADC clock period to be:

$$\frac{1}{(14+1) \times 200,000} = 334 \text{ ns}$$

by writing to the ADCS<5:0> control bits in the ADCON3 register.

• Configure the sampling time to be 1 TAD by writing: SAMC<4:0> = 00001.

The following figure shows the timing diagram of the ADC running at 200 ksps. The TAD selection in conjunction with the guidelines described above allows a conversion speed of 200 ksps. See Example 16-1 for code example.

# 16.8 A/D Acquisition Requirements

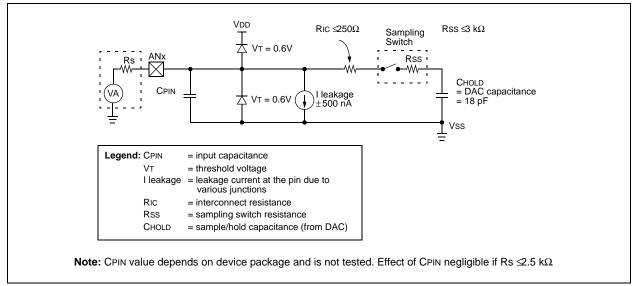

The analog input model of the 12-bit ADC is shown in Figure 16-3. The total sampling time for the A/D is a function of the internal amplifier settling time and the holding capacitor charge time.

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the voltage level on the analog input pin. The impedance source (Rs), the interconnect impedance (RIC) and the internal sampling switch (Rss) impedance combine to directly affect the time required to charge the capacitor CHOLD. The combined impedance of the analog sources must therefore be small enough to fully charge the holding capacitor within the chosen sample time. To minimize the effects of pin leakage currents on the accuracy of the ADC, the maximum recommended source impedance, Rs, is 2.5 k $\Omega$  After the analog input channel is selected (changed), this sampling function must be completed prior to starting the conversion. The internal holding capacitor will be in a discharged state prior to each sample operation.

#### FIGURE 16-3: 12-BIT A/D CONVERTER ANALOG INPUT MODEL

# **17.0 SYSTEM INTEGRATION**

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

There are several features intended to maximize system reliability, minimize cost through elimination of external components, provide Power Saving Operating modes and offer code protection:

- Oscillator Selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Programmable Brown-out Reset (BOR)

- Watchdog Timer (WDT)

- Low-Voltage Detect

- Power-Saving Modes (Sleep and Idle)

- Code Protection

- Unit ID Locations

- In-Circuit Serial Programming (ICSP)

dsPIC30F devices have a Watchdog Timer which is permanently enabled via the Configuration bits or can be software controlled. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT) which provides a delay on power-up only, designed to keep the part in Reset while the power supply stabilizes. With these two timers on-chip, most applications need no external Reset circuitry.

Sleep mode is designed to offer a very low current Power-Down mode. The user can wake-up from Sleep through external Reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit a wide variety of applications. In the Idle mode, the clock sources are still active but the CPU is shut-off. The RC oscillator option saves system cost while the LP crystal option saves power.

#### 17.1 Oscillator System Overview

The dsPIC30F oscillator system has the following modules and features:

- Various external and internal oscillator options as clock sources

- An on-chip PLL to boost internal operating frequency

- A clock switching mechanism between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- Clock Control register (OSCCON)

- · Configuration bits for main oscillator selection

Configuration bits determine the clock source upon Power-on Reset (POR) and Brown-out Reset (BOR). Thereafter, the clock source can be changed between permissible clock sources. The OSCCON register controls the clock switching and reflects system clock related status bits.

Table 17-1 provides a summary of the dsPIC30F Oscillator Operating modes. A simplified diagram of the oscillator system is shown in Figure 17-1.

### TABLE 18-2: INSTRUCTION SET OVERVIEW

| Base<br>Instr<br># | Assembly<br>Mnemonic |       | Assembly Syntax | Description                                   | # of<br>Words | # of<br>Cycle<br>s | Status Flags<br>Affected |

|--------------------|----------------------|-------|-----------------|-----------------------------------------------|---------------|--------------------|--------------------------|

| 1                  | ADD                  | ADD   | Acc             | Add Accumulators                              | 1             | 1                  | OA,OB,SA,SB              |

|                    |                      | ADD   | f               | f = f + WREG                                  | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADD   | f,WREG          | WREG = f + WREG                               | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADD   | #lit10,Wn       | Wd = lit10 + Wd                               | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wb,Ws,Wd        | Wd = Wb + Ws                                  | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wb,#lit5,Wd     | Wd = Wb + lit5                                | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wso,#Slit4,Acc  | 16-bit Signed Add to Accumulator              | 1             | 1                  | OA,OB,SA,SB              |

| 2                  | ADDC                 | ADDC  | f               | f = f + WREG + (C)                            | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADDC  | f,WREG          | WREG = f + WREG + (C)                         | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADDC  | #lit10,Wn       | Wd = lit10 + Wd + (C)                         | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADDC  | Wb,Ws,Wd        | Wd = Wb + Ws + (C)                            | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADDC  | Wb,#lit5,Wd     | Wd = Wb + lit5 + (C)                          | 1             | 1                  | C,DC,N,OV,Z              |

| 3                  | AND                  | AND   | f               | f = f .AND. WREG                              | 1             | 1                  | N,Z                      |

|                    |                      | AND   | f,WREG          | WREG = f .AND. WREG                           | 1             | 1                  | N,Z                      |

|                    |                      | AND   | #lit10,Wn       | Wd = lit10 .AND. Wd                           | 1             | 1                  | N,Z                      |

|                    |                      | AND   | Wb,Ws,Wd        | Wd = Wb .AND. Ws                              | 1             | 1                  | N,Z                      |

|                    |                      | AND   | Wb,#lit5,Wd     | Wd = Wb .AND. lit5                            | 1             | 1                  | N,Z                      |

| 4                  | ASR                  | ASR   | f               | f = Arithmetic Right Shift f                  | 1             | 1                  | C,N,OV,Z                 |

|                    |                      | ASR   | f,WREG          | WREG = Arithmetic Right Shift f               | 1             | 1                  | C,N,OV,Z                 |

|                    |                      | ASR   | Ws,Wd           | Wd = Arithmetic Right Shift Ws                | 1             | 1                  | C,N,OV,Z                 |

|                    |                      | ASR   | Wb,Wns,Wnd      | Wnd = Arithmetic Right Shift Wb by Wns        | 1             | 1                  | N,Z                      |

|                    |                      | ASR   | Wb,#lit5,Wnd    | Wnd = Arithmetic Right Shift Wb by lit5       | 1             | 1                  | N,Z                      |

| 5                  | BCLR                 | BCLR  | f,#bit4         | Bit Clear f                                   | 1             | 1                  | None                     |

| 0                  | DOLIN                | BCLR  | Ws,#bit4        | Bit Clear Ws                                  | 1             | 1                  | None                     |

| 6                  | BRA                  | BRA   | C,Expr          | Branch if Carry                               | 1             | 1 (2)              | None                     |

| 0                  | Divi                 | BRA   | GE, Expr        | Branch if greater than or equal               | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | GEU, Expr       | Branch if unsigned greater than or equal      | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | GEO, Expr       | Branch if greater than                        | 1             | 1 (2)              | None                     |

|                    |                      | BRA   |                 | Branch if unsigned greater than               | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | GTU, Expr       | Branch if less than or equal                  | 1             | 1 (2)              | None                     |

|                    |                      |       | LE, Expr        | Branch if unsigned less than or equal         | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | LEU, Expr       | Branch if less than                           | 1             | . ,                |                          |

|                    |                      | BRA   | LT,Expr         |                                               |               | 1 (2)              | None                     |

|                    |                      | BRA   | LTU, Expr       | Branch if unsigned less than                  | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | N,Expr          | Branch if Negative                            | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | NC,Expr         | Branch if Not Carry<br>Branch if Not Negative | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | NN, Expr        |                                               |               | 1 (2)              | None                     |

|                    |                      | BRA   | NOV,Expr        | Branch if Not Overflow                        | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | NZ,Expr         | Branch if Not Zero                            | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | OA,Expr         | Branch if Accumulator A overflow              | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | OB,Expr         | Branch if Accumulator B overflow              | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | OV,Expr         | Branch if Overflow                            | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | SA,Expr         | Branch if Accumulator A saturated             | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | SB,Expr         | Branch if Accumulator B saturated             | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | Expr            | Branch Unconditionally                        | 1             | 2                  | None                     |

|                    |                      | BRA   | Z,Expr          | Branch if Zero                                | 1             | 1 (2)              | None                     |

| _                  |                      | BRA   | Wn              | Computed Branch                               | 1             | 2                  | None                     |

| 7                  | BSET                 | BSET  | f,#bit4         | Bit Set f                                     | 1             | 1                  | None                     |

|                    |                      | BSET  | Ws,#bit4        | Bit Set Ws                                    | 1             | 1                  | None                     |

| 8                  | BSW                  | BSW.C | Ws,Wb           | Write C bit to Ws <wb></wb>                   | 1             | 1                  | None                     |

|                    |                      | BSW.Z | Ws,Wb           | Write Z bit to Ws <wb></wb>                   | 1             | 1                  | None                     |

#### 20.1 DC Characteristics

#### TABLE 20-1: OPERATING MIPS VS. VOLTAGE

| Voo Benge | Town Dongo     | Max MIPS        |                 |  |  |  |

|-----------|----------------|-----------------|-----------------|--|--|--|

| VDD Range | Temp Range     | dsPIC30FXXX-30I | dsPIC30FXXX-20E |  |  |  |

| 4.5-5.5V  | -40°C to 85°C  | 30              | —               |  |  |  |

| 4.5-5.5V  | -40°C to 125°C | _               | 20              |  |  |  |

| 3.0-3.6V  | -40°C to 85°C  | 20              | —               |  |  |  |

| 3.0-3.6V  | -40°C to 125°C | —               | 15              |  |  |  |

| 2.5-3.0V  | -40°C to 85°C  | 10              | —               |  |  |  |

#### TABLE 20-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                                                     | Symbol         | Min | Тур          | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----|--------------|------|------|

| dsPIC30F201x-30I                                                                                                                                                                                                           |                |     |              |      |      |

| dsPIC30F301x-30I                                                                                                                                                                                                           |                |     |              |      |      |

| Operating Junction Temperature Range                                                                                                                                                                                       | TJ             | -40 | —            | +125 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                                                        | TA             | -40 |              | +85  | °C   |

| dsPIC30F201x-20E                                                                                                                                                                                                           |                |     |              |      |      |

| dsPIC30F301x-20E                                                                                                                                                                                                           |                |     |              |      |      |

|                                                                                                                                                                                                                            |                |     |              |      |      |

| Operating Junction Temperature Range                                                                                                                                                                                       | TJ             | -40 |              | +150 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                                                        | TA             | -40 | —            | +125 | °C   |

| Power Dissipation:                                                                                                                                                                                                         |                |     |              |      |      |

| Internal chip power dissipation:                                                                                                                                                                                           |                |     |              |      |      |

| $P_{INT} = V_{DD} \times (I_{DD} - \Sigma I_{OH})$                                                                                                                                                                         | PD PINT + PI/O |     |              |      | W    |

| I/O Pin power dissipation:                                                                                                                                                                                                 |                |     |              |      |      |

| $\mathbf{P}_{\mathrm{I/O}} = \sum \left( \{ \mathbf{V}_{\mathrm{DD}} - \mathbf{V}_{\mathrm{OH}} \} \times \mathbf{I}_{\mathrm{OH}} \right) + \sum \left( \mathbf{V}_{\mathrm{OL}} \times \mathbf{I}_{\mathrm{OL}} \right)$ |                |     |              |      |      |

| Maximum Allowed Power Dissipation                                                                                                                                                                                          | PDMAX          | ۲)  | 「J - TA) / θ | JA   | W    |

#### TABLE 20-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                                | Symbol | Тур | Max | Unit | Notes |

|-----------------------------------------------|--------|-----|-----|------|-------|

| Package Thermal Resistance, 18-pin PDIP (P)   | θJA    | 44  |     | °C/W | 1     |

| Package Thermal Resistance, 18-pin SOIC (SO)  | θJA    | 57  | _   | °C/W | 1     |

| Package Thermal Resistance, 28-pin SPDIP (SP) | θJA    | 42  | _   | °C/W | 1     |

| Package Thermal Resistance, 28-pin (SOIC)     | θJA    | 49  | _   | °C/W | 1     |

| Package Thermal Resistance, 44-pin QFN        | θJA    | 28  | _   | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-ja ( $\theta$ JA) numbers are achieved by package simulations.

| DC CHA       | RACTER | Standard Operating Conditions: 2.5V to 5.5V   (unless otherwise stated)   Operating temperature -40°C ≤TA ≤+85°C for Industrial   -40°C ≤TA ≤+125°C for Extended |         |                    |         |       |                                           |

|--------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------|---------|-------|-------------------------------------------|

| Param<br>No. | Symbol | Characteristic                                                                                                                                                   | Min     | Тур <sup>(1)</sup> | Max     | Units | Conditions                                |

|              | VIL    | Input Low Voltage <sup>(2)</sup>                                                                                                                                 |         |                    |         |       |                                           |

| DI10         |        | I/O pins:<br>with Schmitt Trigger buffer                                                                                                                         | Vss     | _                  | 0.2 Vdd | V     |                                           |

| DI15         |        | MCLR                                                                                                                                                             | Vss     | _                  | 0.2 Vdd | V     |                                           |

| DI16         |        | OSC1 (in XT, HS and LP modes)                                                                                                                                    | Vss     | —                  | 0.2 Vdd | V     |                                           |

| DI17         |        | OSC1 (in RC mode) <sup>(3)</sup>                                                                                                                                 | Vss     | —                  | 0.3 Vdd | V     |                                           |

| DI18         |        | SDA, SCL                                                                                                                                                         | Vss     | —                  | 0.3 Vdd | V     | SM bus disabled                           |

| DI19         |        | SDA, SCL                                                                                                                                                         | Vss     | —                  | 0.8     | V     | SM bus enabled                            |

|              | Vih    | Input High Voltage <sup>(2)</sup>                                                                                                                                |         |                    |         |       |                                           |

| DI20         |        | I/O pins:<br>with Schmitt Trigger buffer                                                                                                                         | 0.8 Vdd | _                  | Vdd     | V     |                                           |

| DI25         |        | MCLR                                                                                                                                                             | 0.8 Vdd | _                  | Vdd     | V     |                                           |

| DI26         |        | OSC1 (in XT, HS and LP modes)                                                                                                                                    | 0.7 Vdd | _                  | Vdd     | V     |                                           |

| DI27         |        | OSC1 (in RC mode) <sup>(3)</sup>                                                                                                                                 | 0.9 Vdd | _                  | Vdd     | V     |                                           |

| DI28         |        | SDA, SCL                                                                                                                                                         | 0.7 Vdd | _                  | Vdd     | V     | SM bus disabled                           |

| DI29         |        | SDA, SCL                                                                                                                                                         | 2.1     | _                  | Vdd     | V     | SM bus enabled                            |

|              | ICNPU  | CNxx Pull-up Current <sup>(2)</sup>                                                                                                                              |         |                    |         |       |                                           |

| DI30         |        |                                                                                                                                                                  | 50      | 250                | 400     | μA    | VDD = 5V, VPIN = VSS                      |

|              | lı∟    | Input Leakage Current <sup>(2)(4)(5)</sup>                                                                                                                       |         |                    |         |       |                                           |

| DI50         |        | I/O ports                                                                                                                                                        | —       | 0.01               | ±1      | μA    | Vss ≤VPıN ≤VDD,<br>Pin at high impedance  |

| DI51         |        | Analog input pins                                                                                                                                                | —       | 0.50               | —       | μA    | Vss ⊴VPiN ⊴VDD,<br>Pin at high impedance  |

| DI55         |        | MCLR                                                                                                                                                             | —       | 0.05               | ±5      | μA    | Vss ⊴Vpin ⊴Vdd                            |

| DI56         |        | OSC1                                                                                                                                                             | _       | 0.05               | ±5      | μA    | Vss ⊴VPiN ⊴VDD, XT, HS<br>and LP Osc mode |

#### TABLE 20-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: These parameters are characterized but not tested in manufacturing.

**3:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the dsPIC30F device be driven with an external clock while in RC mode.

4: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

5: Negative current is defined as current sourced by the pin.

| Clock<br>Oscillator<br>Mode | Fosc<br>(MHz) <sup>(1)</sup> | Τ <b>C</b> Υ (μsec) <sup>(2)</sup> | MIPS <sup>(3)</sup><br>w/o PLL | MIPS <sup>(3)</sup><br>w PLL x4 | MIPS <sup>(3)</sup><br>w PLL x8 | MIPS <sup>(3)</sup><br>w PLL x16 |

|-----------------------------|------------------------------|------------------------------------|--------------------------------|---------------------------------|---------------------------------|----------------------------------|

| EC                          | 0.200                        | 20.0                               | 0.05                           | —                               | —                               | —                                |

|                             | 4                            | 1.0                                | 1.0                            | 4.0                             | 8.0                             | 16.0                             |

|                             | 10                           | 0.4                                | 2.5                            | 10.0                            | 20.0                            | —                                |

|                             | 25                           | 0.16                               | 6.25                           | —                               | —                               | —                                |

| XT                          | 4                            | 1.0                                | 1.0                            | 4.0                             | 8.0                             | 16.0                             |

|                             | 10                           | 0.4                                | 2.5                            | 10.0                            | 20.0                            | —                                |

#### TABLE 20-17: INTERNAL CLOCK TIMING EXAMPLES

Note 1: Assumption: Oscillator Postscaler is divide by 1.

**2:** Instruction Execution Cycle Time: TCY = 1/MIPS.

**3:** Instruction Execution Frequency: MIPS = (Fosc \* PLLx)/4 [since there are 4 Q clocks per instruction cycle].

#### TABLE 20-18: AC CHARACTERISTICS: INTERNAL FRC ACCURACY

| АС СНА       | RACTERISTICS            | Standard Operating Conditions: 2.5V to 5.5V   (unless otherwise stated)   Operating temperature -40°C ≤TA ≤+85°C for Industrial   -40°C ≤TA ≤+125°C for Extended |           |                      |       |                                  |                |  |  |

|--------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------|-------|----------------------------------|----------------|--|--|

| Param<br>No. | Characteristic          | Min                                                                                                                                                              | Тур       | Max                  | Units | Conditions                       |                |  |  |

|              | Internal FRC Accuracy @ | FRC Fr                                                                                                                                                           | eq. = 7.3 | 7 MHz <sup>(1)</sup> |       |                                  |                |  |  |

| OS63         | FRC                     | —                                                                                                                                                                | —         | ±2.00                | %     | -40°C ≤TA ≤+85°C                 | VDD = 3.0-5.5V |  |  |

|              |                         | _                                                                                                                                                                |           | ±5.00                | %     | -40°C ≤TA ≤+125°C VDD = 3.0-5.5V |                |  |  |

**Note 1:** Frequency calibrated at 7.372 MHz ±2%, 25°C and 5V. TUN bits (OSCCON<3:0>) can be used to compensate for temperature drift.

#### TABLE 20-19: AC CHARACTERISTICS: INTERNAL LPRC ACCURACY

| AC CHA       | RACTERISTICS                          | Standard Operating Conditions: 2.5V to 5.5V   (unless otherwise stated)   Operating temperature -40°C ≤TA ≤+85°C for Industrial   -40°C ≤TA ≤+125°C for Extended |   |     |   |                  |  |

|--------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|---|------------------|--|

| Param<br>No. | Characteristic                        | Min Typ Max Units Conditions                                                                                                                                     |   |     |   | Conditions       |  |

|              | LPRC @ Freq. = 512 kHz <sup>(1)</sup> |                                                                                                                                                                  |   |     |   |                  |  |

| OS65A        |                                       | -50                                                                                                                                                              | — | +50 | % | VDD = 5.0V, ±10% |  |

| OS65B        |                                       | -60                                                                                                                                                              |   | +60 | % | VDD = 3.3V, ±10% |  |

| OS65C        |                                       | -70                                                                                                                                                              |   | +70 | % | VDD = 2.5V       |  |

Note 1: Change of LPRC frequency as VDD changes.

# TABLE 20-33: I<sup>2</sup>C<sup>™</sup> BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| AC CHARACTERISTICS |         |                               |                           | Standard Operating Conditions: 2.5V to 5.5V   (unless otherwise stated)   Operating temperature -40°C ≤TA ≤+85°C for Industrial   -40°C ≤TA ≤+125°C for Extended |      |       |                        |  |  |

|--------------------|---------|-------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------------------|--|--|

| Param<br>No.       | Symbol  | Characteristic                |                           | Min <sup>(1)</sup>                                                                                                                                               | Max  | Units | Conditions             |  |  |

| IM10               | TLO:SCL | Clock Low Time                | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                  | _    | μs    |                        |  |  |

|                    |         |                               | 400 kHz mode              | TCY/2 (BRG + 1)                                                                                                                                                  | —    | μs    |                        |  |  |

|                    |         |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                  | —    | μs    |                        |  |  |

| IM11               | THI:SCL | Clock High Time               | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                  | —    | μs    |                        |  |  |

|                    |         |                               | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                  | —    | μs    |                        |  |  |

|                    |         |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                  | _    | μs    |                        |  |  |

| IM20               | TF:SCL  | SDA and SCL                   | 100 kHz mode              | —                                                                                                                                                                | 300  | ns    | CB is specified to be  |  |  |

|                    |         | Fall Time                     | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                      | 300  | ns    | from 10 to 400 pF      |  |  |

|                    |         |                               | 1 MHz mode <sup>(2)</sup> | _                                                                                                                                                                | 100  | ns    |                        |  |  |

| IM21               | TR:SCL  | SDA and SCL<br>Rise Time      | 100 kHz mode              | _                                                                                                                                                                | 1000 | ns    | CB is specified to be  |  |  |

|                    |         |                               | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                      | 300  | ns    | from 10 to 400 pF      |  |  |

|                    |         |                               | 1 MHz mode <sup>(2)</sup> | _                                                                                                                                                                | 300  | ns    |                        |  |  |

| IM25               | TSU:DAT | Data Input<br>Setup Time      | 100 kHz mode              | 250                                                                                                                                                              | —    | ns    |                        |  |  |

|                    |         |                               | 400 kHz mode              | 100                                                                                                                                                              | —    | ns    |                        |  |  |

|                    |         |                               | 1 MHz mode <sup>(2)</sup> | —                                                                                                                                                                | _    | ns    |                        |  |  |

| IM26               | THD:DAT | Data Input<br>Hold Time       | 100 kHz mode              | 0                                                                                                                                                                | —    | ns    |                        |  |  |

|                    |         |                               | 400 kHz mode              | 0                                                                                                                                                                | 0.9  | μs    |                        |  |  |

|                    |         |                               | 1 MHz mode <sup>(2)</sup> | —                                                                                                                                                                | _    | ns    |                        |  |  |

| IM30               | TSU:STA | Start Condition<br>Setup Time | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                  | —    | μs    | Only relevant for      |  |  |

|                    |         |                               | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                  | —    | μs    | Repeated Start         |  |  |

|                    |         |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                  | _    | μs    | condition              |  |  |

| IM31               | THD:STA | Start Condition<br>Hold Time  | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                  | —    | μs    | After this period the  |  |  |

|                    |         |                               | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                  | —    | μs    | first clock pulse is   |  |  |

|                    |         |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                  | _    | μs    | generated              |  |  |

| IM33               | Tsu:sto | Stop Condition<br>Setup Time  | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                  | _    | μs    |                        |  |  |

|                    |         |                               | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                  | —    | μs    |                        |  |  |

|                    |         |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                  | _    | μs    |                        |  |  |

| IM34               | THD:STO | Stop Condition                | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                  | _    | ns    |                        |  |  |

| -                  |         | Hold Time                     | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                  | _    | ns    |                        |  |  |

|                    |         |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                  | _    | ns    |                        |  |  |

| IM40               | TAA:SCL | Output Valid<br>From Clock    | 100 kHz mode              | —                                                                                                                                                                | 3500 | ns    |                        |  |  |

|                    |         |                               | 400 kHz mode              | —                                                                                                                                                                | 1000 | ns    |                        |  |  |

|                    |         |                               | 1 MHz mode <sup>(2)</sup> | _                                                                                                                                                                |      | ns    |                        |  |  |

| IM45               | TBF:SDA | Bus Free Time                 | 100 kHz mode              | 4.7                                                                                                                                                              |      | μs    | Time the bus must be   |  |  |

|                    |         |                               | 400 kHz mode              | 1.3                                                                                                                                                              |      | μs    | free before a new      |  |  |

|                    |         |                               | 1 MHz mode <sup>(2)</sup> | _                                                                                                                                                                |      | μs    | transmission can start |  |  |

| IM50               | Св      | Bus Capacitive L              |                           |                                                                                                                                                                  | 400  | pF    |                        |  |  |

Note 1: BRG is the value of the I<sup>2</sup>C Baud Rate Generator. Refer to Section 21. "Inter-Integrated Circuit™ (I<sup>2</sup>C)" (DS70068) in the *dsPIC30F Family Reference Manual* (DS70046).

**2:** Maximum pin capacitance = 10 pF for all  $I^2C^{TM}$  pins (for 1 MHz mode only).

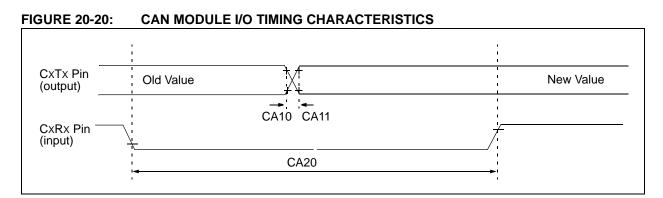

#### TABLE 20-35: CAN MODULE I/O TIMING REQUIREMENTS

| AC CHARA     | CTERISTIC | Standard Operating Conditions: 2.5V to 5.5V(unless otherwise stated)Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for Industrial $-40^{\circ}C \leq TA \leq +125^{\circ}C$ for Extended |  |     |                    |     |       |            |

|--------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-----|--------------------|-----|-------|------------|

| Param<br>No. | Symbol    | Characteristic <sup>(1)</sup>                                                                                                                                                                            |  | Min | Тур <sup>(2)</sup> | Max | Units | Conditions |

| CA10         | TioF      | Port Output Fall Time                                                                                                                                                                                    |  |     | 10                 | 25  | ns    |            |