Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detalls                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | dsPIC                                                                        |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 20 MIPS                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 12                                                                           |

| Program Memory Size        | 24KB (8K x 24)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 1K x 8                                                                       |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x12b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Through Hole                                                                 |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                      |

| Supplier Device Package    | 18-PDIP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f3012-20i-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

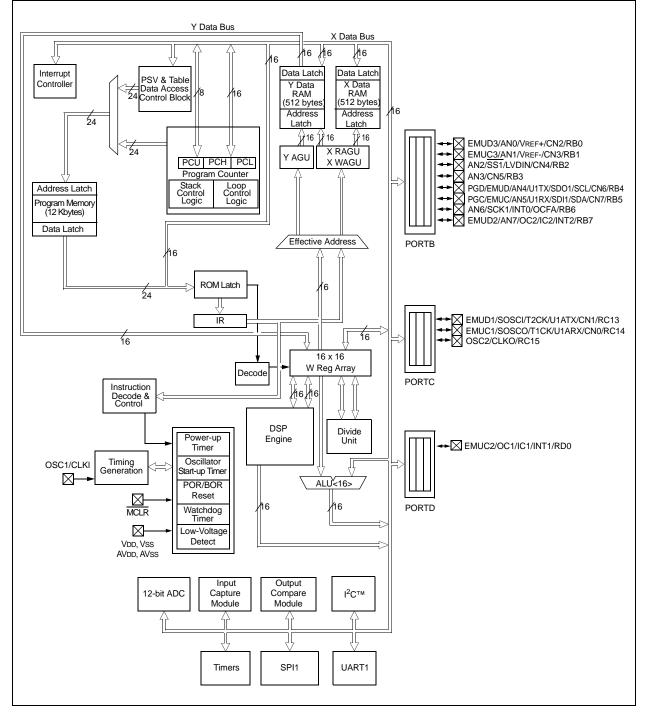

## FIGURE 1-1: dsPIC30F2011 BLOCK DIAGRAM

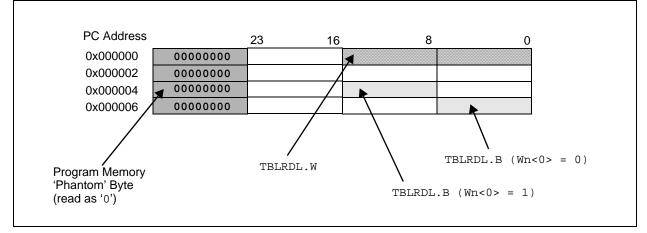

#### 3.1.1 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

This architecture fetches 24-bit wide program memory. Consequently, instructions are always aligned. However, as the architecture is modified Harvard, data can also be present in program space.

There are two methods by which program space can be accessed: via special table instructions, or through the remapping of a 16K word program space page into the upper half of data space (see Section 3.1.2 "Data Access from Program Memory Using Program Space Visibility"). The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lsw of any address within program space, without going through data space. The TBLRDH and TBLWTH instructions are the only method whereby the upper 8 bits of a program space word can be accessed as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit word wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the lsw, and TBLRDH and TBLWTH access the space which contains the MSB.

Figure 3-2 shows how the EA is created for table operations and data space accesses (PSV = 1). Here, P<23:0> refers to a program space word, whereas D<15:0> refers to a data space word.

A set of table instructions are provided to move byte or word-sized data to and from program space. See Figure 3-4 and Figure 3-5.

TBLRDL: Table Read Low Word: Read the LS Word of the program address; P<15:0> maps to D<15:0>. Byte: Read one of the LSB of the program

address; P < 7:0 > maps to the destination byte when byte select = 0;

P<15:8> maps to the destination byte when byte select = 1.

- TBLWTL: Table Write Low (refer to Section 5.0 "Flash Program Memory" for details on Flash Programming)

- TBLRDH: Table Read High Word: Read the MS Word of the program address; P<23:16> maps to D<7:0>; D<15:8> will always be = 0.

*Byte:* Read one of the MSB of the program address;

P<23:16> maps to the destination byte when byte select = 0;

The destination byte will always be = 0 when byte select = 1.

TBLWTH: Table Write High (refer to Section 5.0 "Flash Program Memory" for details on Flash Programming)

## FIGURE 3-3: PROGRAM DATA TABLE ACCESS (Isw)

## 3.2 Data Address Space

The core has two data spaces. The data spaces can be considered either separate (for some DSP instructions), or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths.

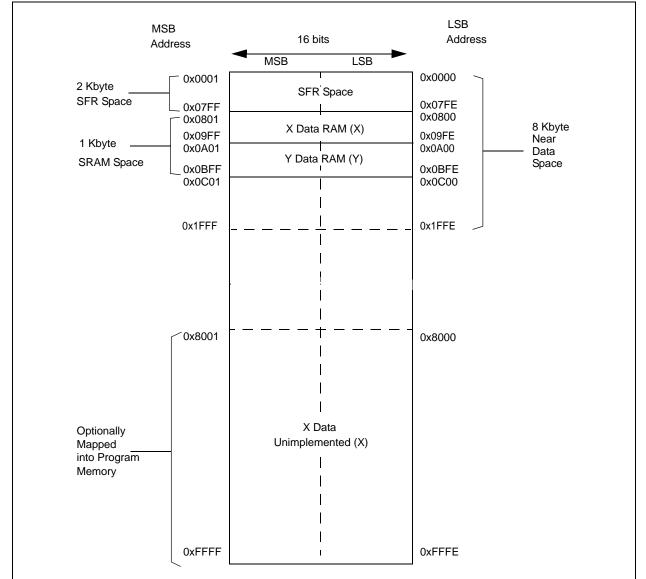

#### 3.2.1 DATA SPACE MEMORY MAP

The data space memory is split into two blocks, X and Y data space. A key element of this architecture is that Y space is a subset of X space, and is fully contained within X space. In order to provide an apparent Linear Addressing space, X and Y spaces have contiguous addresses.

When executing any instruction other than one of the MAC class of instructions, the X block consists of the 64 Kbyte data address space (including all Y addresses). When executing one of the MAC class of instructions, the X block consists of the 64 Kbyte data address space, excluding the Y address block (for data reads only). In other words, all other instructions regard the entire data memory as one composite address space. The MAC class instructions extract the Y address space from data space and address it using EAs sourced from W10 and W11. The remaining X data space is addressed using W8 and W9. Both address spaces are concurrently accessed only with the MAC class instructions.

The data space memory map for the dsPIC30F2011 and dsPIC30F2012 is shown in Figure 3-6. The data space memory map for the dsPIC30F3012 and dsPIC30F3013 is shown in Figure 3-7.

#### FIGURE 3-6: dsPIC30F2011/2012 DATA SPACE MEMORY MAP

## 5.4 RTSP Operation

The dsPIC30F Flash program memory is organized into rows and panels. Each row consists of 32 instructions or 96 bytes. Each panel consists of 128 rows or 4K x 24 instructions. RTSP allows the user to erase one row (32 instructions) at a time and to program four instructions at one time. RTSP may be used to program multiple program memory panels, but the table pointer must be changed at each panel boundary.

Each panel of program memory contains write latches that hold 32 instructions of programming data. Prior to the actual programming operation, the write data must be loaded into the panel write latches. The data to be programmed into the panel is loaded in sequential order into the write latches; instruction 0, instruction 1, etc. The instruction words loaded must always be from a 32 address boundary.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the write latches. Programming is performed by setting the special bits in the NVMCON register. 32 TBLWTL and four TBLWTH instructions are required to load the 32 instructions. If multiple panel programming is required, the Table Pointer needs to be changed and the next set of multiple write latches written.

All of the table write operations are single-word writes (2 instruction cycles), because only the table latches are written. A programming cycle is required for programming each row.

The Flash Program Memory is readable, writable and erasable during normal operation over the entire VDD range.

#### 5.5 Control Registers

The four SFRs used to read and write the program Flash memory are:

- NVMCON

- NVMADR

- NVMADRU

- NVMKEY

#### 5.5.1 NVMCON REGISTER

The NVMCON register controls which blocks are to be erased, which memory type is to be programmed, and start of the programming cycle.

#### 5.5.2 NVMADR REGISTER

The NVMADR register is used to hold the lower two bytes of the Effective Address. The NVMADR register captures the EA<15:0> of the last table instruction that has been executed and selects the row to write.

#### 5.5.3 NVMADRU REGISTER

The NVMADRU register is used to hold the upper byte of the Effective Address. The NVMADRU register captures the EA<23:16> of the last table instruction that has been executed.

#### 5.5.4 NVMKEY REGISTER

NVMKEY is a write-only register that is used for write protection. To start a programming or an erase sequence, the user must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 5.6** "**Programming Operations**" for further details.

Note: The user can also directly write to the NVMADR and NVMADRU registers to specify a program memory address for erasing or programming.

# dsPIC30F2011/2012/3012/3013

### 8.4 Interrupt Sequence

All interrupt event flags are sampled in the beginning of each instruction cycle by the IFSx registers. A pending Interrupt Request (IRQ) is indicated by the flag bit being equal to a '1' in an IFSx register. The IRQ causes an interrupt to occur if the corresponding bit in the Interrupt Enable (IECx) register is set. For the remainder of the instruction cycle, the priorities of all pending interrupt requests are evaluated.

If there is a pending IRQ with a priority level greater than the current processor priority level in the IPL bits, the processor is interrupted.

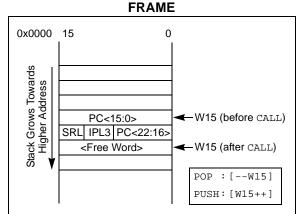

The processor then stacks the current program counter and the low byte of the processor STATUS register (SRL), as shown in Figure 8-2. The low byte of the STATUS register contains the processor priority level at the time prior to the beginning of the interrupt cycle. The processor then loads the priority level for this interrupt into the STATUS register. This action disables all lower priority interrupts until the completion of the Interrupt Service Routine (ISR).

## FIGURE 8-2: INTERRUPT STACK

- Note 1: The user can always lower the priority level by writing a new value into SR. The Interrupt Service Routine must clear the interrupt flag bits in the IFSx register before lowering the processor interrupt priority, in order to avoid recursive interrupts.

- 2: The IPL3 bit (CORCON<3>) is always clear when interrupts are being processed. It is set only during execution of traps.

The RETFIE (return from interrupt) instruction unstacks the program counter and STATUS registers to return the processor to its state prior to the interrupt sequence.

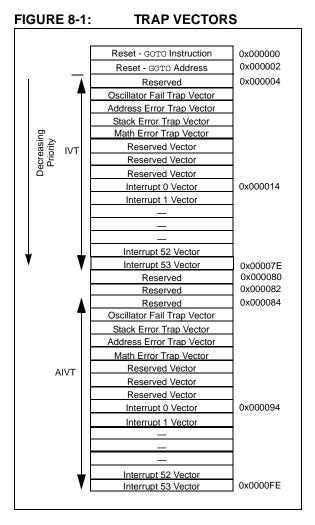

## 8.5 Alternate Vector Table

In program memory, the Interrupt Vector Table (IVT) is followed by the Alternate Interrupt Vector Table (AIVT), as shown in Figure 8-1. Access to the alternate vector table is provided by the ALTIVT bit in the INTCON2 register. If the ALTIVT bit is set, all interrupt and exception processes use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors. The AIVT supports emulation and debugging efforts by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time.

If the AIVT is not required, the program memory allocated to the AIVT may be used for other purposes. AIVT is not a protected section and may be freely programmed by the user.

#### TABLE 9-1: TIMER1 REGISTER MAP

| SFR Name | Addr. | Bit 15 | Bit 14            | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6               | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset State         |

|----------|-------|--------|-------------------|--------|--------|--------|--------|-------|-------|-------|---------------------|--------|--------|-------|-------|-------|-------|---------------------|

| TMR1     | 0100  |        | Timer1 Register   |        |        |        |        |       |       |       | uuuu uuuu uuuu uuuu |        |        |       |       |       |       |                     |

| PR1      | 0102  |        | Period Register 1 |        |        |        |        |       |       |       | 1111 1111 1111 1111 |        |        |       |       |       |       |                     |

| T1CON    | 0104  | TON    | —                 | TSIDL  | —      | _      | —      | —     | —     | _     | TGATE               | TCKPS1 | TCKPS0 | _     | TSYNC | TCS   | _     | 0000 0000 0000 0000 |

Legend: u = uninitialized bit; - = unimplemented bit, read as '0'

Note: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

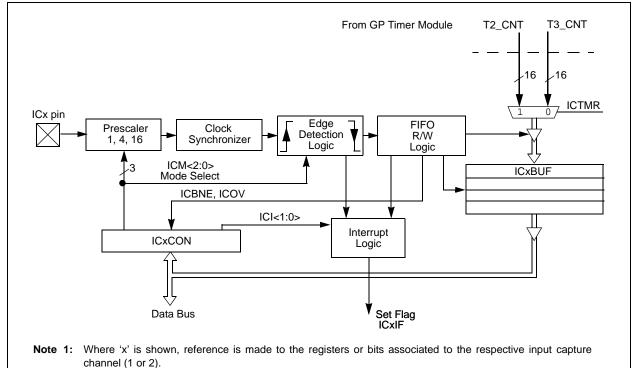

## 11.0 INPUT CAPTURE MODULE

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

This section describes the input capture module and associated operational modes. The features provided by this module are useful in applications requiring frequency (period) and pulse measurement.

Figure 11-1 depicts a block diagram of the input capture module. Input capture is useful for such modes as:

- Frequency/Period/Pulse Measurements

- · Additional Sources of External Interrupts

Important operational features of the input capture module are:

- Simple Capture Event mode

- Timer2 and Timer3 mode selection

- · Interrupt on input capture event

These operating modes are determined by setting the appropriate bits in the IC1CON and IC2CON registers. The dsPIC30F2011/2012/3012/3013 devices have two capture channels.

## 11.1 Simple Capture Event Mode

The simple capture events in the dsPIC30F product family are:

- · Capture every falling edge

- Capture every rising edge

- Capture every 4th rising edge

- · Capture every 16th rising edge

- · Capture every rising and falling edge

These simple Input Capture modes are configured by setting the appropriate bits, ICM<2:0> (ICxCON<2:0>).

#### 11.1.1 CAPTURE PRESCALER

There are four input capture prescaler settings specified by bits ICM<2:0> (ICxCON<2:0>). Whenever the capture channel is turned off, the prescaler counter is cleared. In addition, any Reset clears the prescaler counter.

#### FIGURE 11-1: INPUT CAPTURE MODE BLOCK DIAGRAM<sup>(1)</sup>

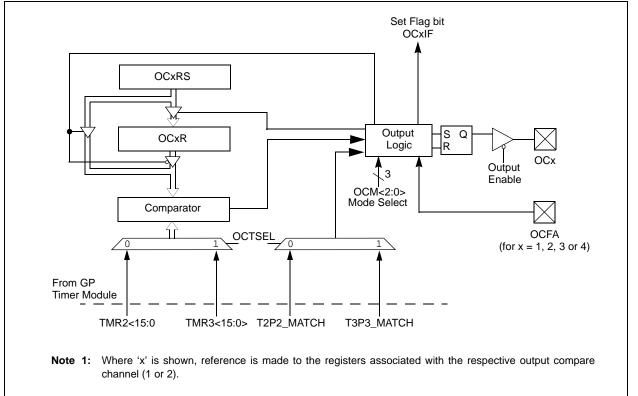

## 12.0 OUTPUT COMPARE MODULE

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

This section describes the output compare module and associated operational modes. The features provided by this module are useful in applications requiring operational modes, such as:

- Generation of Variable Width Output Pulses

- Power Factor Correction

Figure 12-1 depicts a block diagram of the output compare module.

The key operational features of the output compare module include:

- Timer2 and Timer3 Selection mode

- Simple Output Compare Match mode

- Dual Output Compare Match mode

- Simple PWM mode

- Output Compare During Sleep and Idle modes

- Interrupt on Output Compare/PWM Event

These operating modes are determined by setting the appropriate bits in the 16-bit OC1CON and OC2CON registers. The dsPIC30F2011/2012/3012/3013 devices have 2 compare channels.

OCxRS and OCxR in Figure 12-1 represent the Dual Compare registers. In the Dual Compare mode, the OCxR register is used for the first compare and OCxRS is used for the second compare.

## dsPIC30F2011/2012/3012/3013

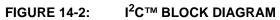

## 14.12.2 I<sup>2</sup>C MASTER RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (I2CCON<3>). The I<sup>2</sup>C module must be Idle before the RCEN bit is set, otherwise the RCEN bit will be disregarded. The Baud Rate Generator begins <u>counting</u> and on each rollover, the state of the SCL pin ACK and data are shifted into the I2CRSR on the rising edge of each clock.

#### 14.12.3 BAUD RATE GENERATOR

In I<sup>2</sup>C Master mode, the reload value for the BRG is located in the I2CBRG register. When the BRG is loaded with this value, the BRG counts down to '0' and stops until another reload has taken place. If clock arbitration is taking place, for instance, the BRG is reloaded when the SCL pin is sampled high.

As per the I<sup>2</sup>C standard, FSCK may be 100 kHz or 400 kHz. However, the user can specify any baud rate up to 1 MHz. I2CBRG values of '0' or '1' are illegal.

#### EQUATION 14-1: SERIAL CLOCK RATE

$I2CBRG = \left(\frac{FCY}{FSCL} - \frac{FCY}{1,111,111}\right) - 1$

### 14.12.4 CLOCK ARBITRATION

Clock arbitration occurs when the master de-asserts the SCL pin (SCL allowed to float high) during any receive, transmit, or Restart/Stop condition. When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of I2CBRG and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device.

#### 14.12.5 MULTI-MASTER COMMUNICATION, BUS COLLISION, AND BUS ARBITRATION

Multi-master operation support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA by letting SDA float high while another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = 0, then a bus collision has taken place. The master will set the MI2CIF pulse and reset the master portion of the  $I^2C$  port to its Idle state.

If a transmit was in progress when the bus collision occurred, the transmission is halted, the TBF flag is cleared, the SDA and SCL lines are de-asserted and a value can now be written to I2CTRN. When the user services the  $I^2C$  master event Interrupt Service Routine, if the  $I^2C$  bus is free (i.e., the P bit is set), the user can resume communication by asserting a Start condition.

If a Start, Restart, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are de-asserted, and the respective control bits in the I2CCON register are cleared to '0'. When the user services the bus collision Interrupt Service Routine, and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins, and if a Stop condition occurs, the MI2CIF bit will be set.

A write to the I2CTRN will start the transmission of data at the first data bit regardless of where the transmitter left off when bus collision occurred.

In a multi-master environment, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$ bus can be taken when the P bit is set in the I2CSTAT register, or the bus is Idle and the S and P bits are cleared.

## 14.13 I<sup>2</sup>C Module Operation During CPU Sleep and Idle Modes

#### 14.13.1 I<sup>2</sup>C OPERATION DURING CPU SLEEP MODE

When the device enters Sleep mode, all clock sources to the module are shut down and stay at logic '0'. If Sleep occurs in the middle of a transmission and the state machine is partially into a transmission as the clocks stop, then the transmission is aborted. Similarly, if Sleep occurs in the middle of a reception, then the reception is aborted.

#### 14.13.2 I<sup>2</sup>C OPERATION DURING CPU IDLE MODE

For the I<sup>2</sup>C, the I2CSIDL bit selects if the module will stop on Idle or continue on Idle. If I2CSIDL = 0, the module will continue operation on assertion of the Idle mode. If I2CSIDL = 1, the module will stop on Idle.

## 17.3.1.1 POR with Long Crystal Start-up Time (with FSCM Enabled)

The oscillator start-up circuitry is not linked to the POR circuitry. Some crystal circuits (especially low frequency crystals) will have a relatively long start-up time. Therefore, one or more of the following conditions is possible after the POR timer and the PWRT have expired:

- The oscillator circuit has not begun to oscillate.

- The Oscillator Start-up Timer has not expired (if a crystal oscillator is used).

- The PLL has not achieved a LOCK (if PLL is used).

If the FSCM is enabled and one of the above conditions is true, then a clock failure trap will occur. The device will automatically switch to the FRC oscillator and the user can switch to the desired crystal oscillator in the trap ISR.

### 17.3.1.2 Operating without FSCM and PWRT

If the FSCM is disabled and the Power-up Timer (PWRT) is also disabled, then the device will exit rapidly from Reset on power-up. If the clock source is FRC, LPRC, ERC or EC, it will be active immediately.

If the FSCM is disabled and the system clock has not started, the device will be in a frozen state at the Reset vector until the system clock starts. From the user's perspective, the device will appear to be in Reset until a system clock is available.

#### 17.3.2 BOR: PROGRAMMABLE BROWN-OUT RESET

The BOR (Brown-out Reset) module is based on an internal voltage reference circuit. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (i.e., missing portions of the AC cycle waveform due to bad power transmission lines, or voltage sags due to excessive current draw when a large inductive load is turned on).

The BOR module allows selection of one of the following voltage trip points (see Table 20-11):

- 2.6V-2.71V

- 4.1V-4.4V

- 4.58V-4.73V

**Note:** The BOR voltage trip points indicated here are nominal values provided for design guidance only. Refer to the Electrical Specifications in the specific device data sheet for BOR voltage limit specifications.

A BOR will generate a Reset pulse which will reset the device. The BOR will select the clock source based on the device Configuration bit values (FOS<2:0> and FPR<4:0>). Furthermore, if an Oscillator mode is selected, the BOR will activate the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, then the clock will be held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the POR time-out (TPOR) and the PWRT time-out (TPWRT) will be applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM = 100  $\mu$ s is applied. The total delay in this case is (TPOR + TFSCM).

The BOR Status bit (RCON<1>) will be set to indicate that a BOR has occurred. The BOR circuit, if enabled, will continue to operate while in Sleep or Idle modes and will reset the device should VDD fall below the BOR threshold voltage.

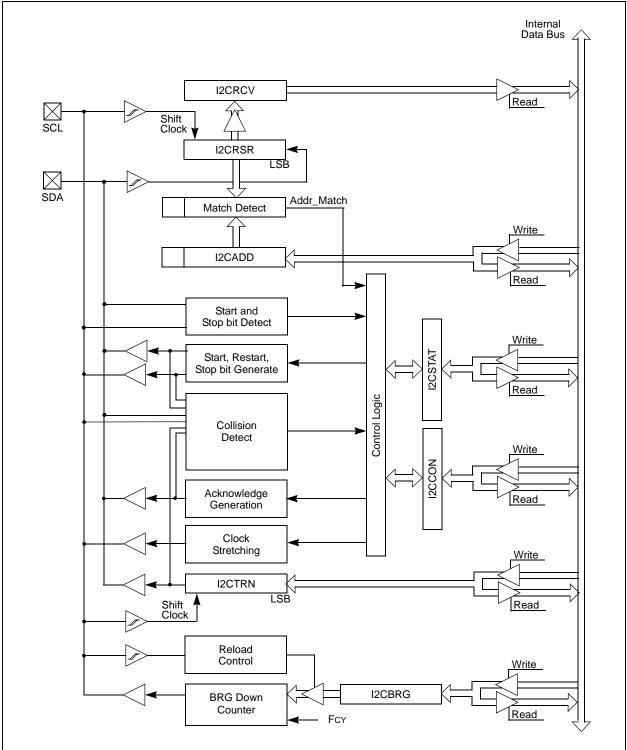

### FIGURE 17-6: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

the MCP1XX and MCP8XX, may also be used as an external Power-on Reset circuit.

| Field | Description                                                                                                                                                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wb    | Base W register ∈ {W0W15}                                                                                                                                                                                                      |

| Wd    | Destination W register ∈ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                                                                                                                                                              |

| Wdo   | Destination W register ∈<br>{ Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] }                                                                                                                                           |

| Wm,Wn | Dividend, Divisor working register pair (direct addressing)                                                                                                                                                                    |

| Wm*Wm | Multiplicand and Multiplier working register pair for Square instructions ∈ {W4*W4,W5*W5,W6*W6,W7*W7}                                                                                                                          |

| Wm*Wn | Multiplicand and Multiplier working register pair for DSP instructions ∈<br>{W4*W5,W4*W6,W4*W7,W5*W6,W5*W7,W6*W7}                                                                                                              |

| Wn    | One of 16 working registers ∈ {W0W15}                                                                                                                                                                                          |

| Wnd   | One of 16 destination working registers ∈ {W0W15}                                                                                                                                                                              |

| Wns   | One of 16 source working registers ∈ {W0W15}                                                                                                                                                                                   |

| WREG  | W0 (working register used in file register instructions)                                                                                                                                                                       |

| Ws    | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                                                                                                                                                                   |

| Wso   | Source W register ∈<br>{ Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }                                                                                                                                                |

| Wx    | X data space prefetch address register for DSP instructions<br>∈ {[W8]+=6, [W8]+=4, [W8]+=2, [W8], [W8]-=6, [W8]-=4, [W8]-=2,<br>[W9]+=6, [W9]+=4, [W9]+=2, [W9], [W9]-=6, [W9]-=4, [W9]-=2,<br>[W9+W12],none}                 |

| Wxd   | X data space prefetch destination register for DSP instructions ∈ {W4W7}                                                                                                                                                       |

| Wy    | Y data space prefetch address register for DSP instructions<br>∈ {[W10]+=6, [W10]+=4, [W10]+=2, [W10], [W10]-=6, [W10]-=4, [W10]-=2,<br>[W11]+=6, [W11]+=4, [W11]+=2, [W11], [W11]-=6, [W11]-=4, [W11]-=2,<br>[W11+W12], none} |

| Wyd   | Y data space prefetch destination register for DSP instructions ∈ {W4W7}                                                                                                                                                       |

#### TABLE 18-1: SYMBOLS USED IN OPCODE DESCRIPTIONS (CONTINUED)

## 20.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC30F electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

For detailed information about the dsPIC30F architecture and core, refer to the "dsPIC30F Family Reference Manual" (DS70046).

Absolute maximum ratings for the dsPIC30F family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

## Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                        | 40°C to +125°C       |

|-----------------------------------------------------------------------|----------------------|

| Storage temperature                                                   | 65°C to +150°C       |

| Voltage on any pin with respect to Vss (except VDD and MCLR) (Note 1) | 0.3V to (VDD + 0.3V) |

| Voltage on VDD with respect to Vss                                    | 0.3V to +5.5V        |

| Voltage on MCLR with respect to Vss                                   | 0V to +13.25V        |

| Maximum current out of Vss pin                                        | 300 mA               |

| Maximum current into VDD pin (Note 2)                                 | 250 mA               |

| Input clamp current, Iк (VI < 0 or VI > VDD)                          | ±20 mA               |

| Output clamp current, IOK (VO < 0 or VO > VDD)                        | ±20 mA               |

| Maximum output current sunk by any I/O pin                            | 25 mA                |

| Maximum output current sourced by any I/O pin                         | 25 mA                |

| Maximum current sunk by all ports                                     | 200 mA               |

| Maximum current sourced by all ports (Note 2)                         | 200 mA               |

**Note 1:** Voltage spikes below Vss at the MCLR/VPP pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR/VPP pin, rather than pulling this pin directly to Vss.

2: Maximum allowable current is a function of device maximum power dissipation. See Table 20-2 for PDMAX.

**†NOTICE:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

**Note:** All peripheral electrical characteristics are specified. For exact peripherals available on specific devices, please refer to the dsPIC30F2011/2012/3012/3013 Sensor Family table on page 4 of this data sheet.

| DC CHARACT       | ERISTICS                   |      | Standard Operating Conditions: 2.5V to 5.5V   (unless otherwise stated)   Operating temperature -40°C ≤TA ≤+85°C for Industrial   -40°C ≤TA ≤+125°C for Extended |            |              |                |  |  |  |

|------------------|----------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|----------------|--|--|--|

| Parameter<br>No. | Typical <sup>(1)</sup>     | Max  | Units                                                                                                                                                            | Conditions |              |                |  |  |  |

| Operating Cu     | rrent (IDD) <sup>(2)</sup> |      |                                                                                                                                                                  |            |              |                |  |  |  |

| DC51a            | 1.3                        | 2.5  | mA                                                                                                                                                               | 25°C       |              |                |  |  |  |

| DC51b            | 1.3                        | 2.5  | mA                                                                                                                                                               | 85°C       | 3.3V         |                |  |  |  |

| DC51c            | 1.2                        | 2.5  | mA                                                                                                                                                               | 125°C      |              | 0.128 MIPS     |  |  |  |

| DC51e            | 3.2                        | 5.0  | mA                                                                                                                                                               | 25°C       |              | LPRC (512 kHz) |  |  |  |

| DC51f            | 2.9                        | 5.0  | mA                                                                                                                                                               | 85°C       | 5V           |                |  |  |  |

| DC51g            | 2.8                        | 5.0  | mA                                                                                                                                                               | 125°C      |              |                |  |  |  |

| DC50a            | 3.0                        | 5.0  | mA                                                                                                                                                               | 25°C       |              |                |  |  |  |

| DC50b            | 3.0                        | 5.0  | mA                                                                                                                                                               | 85°C       | 3.3V         |                |  |  |  |

| DC50c            | 3.0                        | 5.0  | mA                                                                                                                                                               | 125°C      |              | (1.8 MIPS)     |  |  |  |

| DC50e            | 6.0                        | 9.0  | mA                                                                                                                                                               | 25°C       |              | FRC (7.37 MHz) |  |  |  |

| DC50f            | 5.8                        | 9.0  | mA                                                                                                                                                               | 85°C       | 5V           |                |  |  |  |

| DC50g            | 5.7                        | 9.0  | mA                                                                                                                                                               | 125°C      |              |                |  |  |  |

| DC43a            | 5.2                        | 8.0  | mA                                                                                                                                                               | 25°C       |              |                |  |  |  |

| DC43b            | 5.3                        | 8.0  | mA                                                                                                                                                               | 85°C       | 3.3V         |                |  |  |  |

| DC43c            | 5.4                        | 8.0  | mA                                                                                                                                                               | 125°C      |              |                |  |  |  |

| DC43e            | 9.7                        | 15.0 | mA                                                                                                                                                               | 25°C       |              | 4 MIPS         |  |  |  |

| DC43f            | 9.6                        | 15.0 | mA                                                                                                                                                               | 85°C       | 5V           |                |  |  |  |

| DC43g            | 9.5                        | 15.0 | mA                                                                                                                                                               | 125°C      |              |                |  |  |  |

| DC44a            | 11.0                       | 17.0 | mA                                                                                                                                                               | 25°C       |              |                |  |  |  |

| DC44b            | 11.0                       | 17.0 | mA                                                                                                                                                               | 85°C       | 3.3V         |                |  |  |  |

| DC44c            | 11.0                       | 17.0 | mA                                                                                                                                                               | 125°C      |              |                |  |  |  |

| DC44e            | 19.0                       | 29.0 | mA                                                                                                                                                               | 25°C       |              | 10 MIPS        |  |  |  |

| DC44f            | 19.0                       | 29.0 | mA                                                                                                                                                               | 85°C       | 5V           |                |  |  |  |

| DC44g            | 20.0                       | 30.0 | mA                                                                                                                                                               | 125°C      |              |                |  |  |  |

| DC47a            | 20.0                       | 35.0 | mA                                                                                                                                                               | 25°C       | 2.01/        |                |  |  |  |

| DC47b            | 21.0                       | 35.0 | mA                                                                                                                                                               | 85°C       | 3.3V         |                |  |  |  |

| DC47d            | 35.0                       | 50.0 | mA                                                                                                                                                               | 25°C       |              | 20 MIPS        |  |  |  |

| DC47e            | 36.0                       | 50.0 | mA                                                                                                                                                               | 85°C       | 5V           |                |  |  |  |

| DC47f            | 36.0                       | 50.0 | mA                                                                                                                                                               | 125°C      | 1            |                |  |  |  |

| DC49a            | 51.0                       | 70.0 | mA                                                                                                                                                               | 25°C       | <b>C</b> ) ( |                |  |  |  |

| DC49b            | 51.0                       | 70.0 | mA                                                                                                                                                               | 85°C       | 5V           | 30 MIPS        |  |  |  |

## TABLE 20-6: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

**Note 1:** Data in "Typical" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: Base IIDLE current is measured with Core off, Clock on and all modules turned off.

## dsPIC30F2011/2012/3012/3013

#### TABLE 20-32: SPI MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHA       | RACTERIST             | īCS                                                             | Standard Operating Conditions: 2.5V to 5.5V   (unless otherwise stated)   Operating temperature -40°C ≤TA ≤+85°C for Industrial   -40°C ≤TA ≤+125°C for Extended |                    |     |       |                       |  |  |

|--------------|-----------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|-----------------------|--|--|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                   | Min                                                                                                                                                              | Тур <sup>(2)</sup> | Max | Units | Conditions            |  |  |

| SP70         | TscL                  | SCKx Input Low Time                                             | 30                                                                                                                                                               | _                  | _   | ns    | —                     |  |  |

| SP71         | TscH                  | SCKx Input High Time                                            | 30                                                                                                                                                               | _                  | _   | ns    | —                     |  |  |

| SP72         | TscF                  | SCKx Input Fall Time <sup>(3)</sup>                             | —                                                                                                                                                                | 10                 | 25  | ns    | —                     |  |  |

| SP73         | TscR                  | SCKx Input Rise Time <sup>(3)</sup>                             | —                                                                                                                                                                | 10                 | 25  | ns    | —                     |  |  |

| SP30         | TdoF                  | SDOx Data Output Fall Time <sup>(3)</sup>                       | _                                                                                                                                                                | —                  |     | ns    | See parameter<br>DO32 |  |  |

| SP31         | TdoR                  | SDOx Data Output Rise Time <sup>(3)</sup>                       | —                                                                                                                                                                | _                  | _   | ns    | See parameter<br>DO31 |  |  |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                       | —                                                                                                                                                                | _                  | 30  | ns    | —                     |  |  |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                      | 20                                                                                                                                                               | _                  | _   | ns    | —                     |  |  |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                       | 20                                                                                                                                                               | _                  | _   | ns    | —                     |  |  |

| SP50         | TssL2scH,<br>TssL2scL | SSx↓to SCKx↓or SCKx↑ input                                      | 120                                                                                                                                                              |                    |     | ns    | —                     |  |  |

| SP51         | TssH2doZ              | SS <sup>↑</sup> to SDOx Output<br>high impedance <sup>(4)</sup> | 10                                                                                                                                                               | —                  | 50  | ns    | —                     |  |  |

| SP52         | TscH2ssH<br>TscL2ssH  | SSx↑ after SCKx Edge                                            | 1.5 Tcy + 40                                                                                                                                                     | _                  | _   | ns    | —                     |  |  |

| SP60         | TssL2doV              | SDOx Data Output Valid after<br>SCKx Edge                       | —                                                                                                                                                                | —                  | 50  | ns    | —                     |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** The minimum clock period for SCK is 100 ns. Therefore, the clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPI pins.

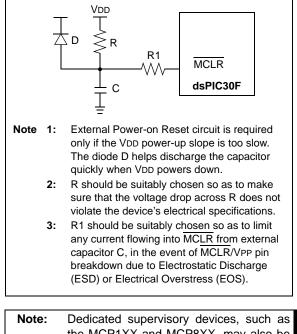

#### TABLE 20-35: CAN MODULE I/O TIMING REQUIREMENTS

| AC CHARA     | CTERISTIC | 5                                       | Standard Operating Conditions: 2.5V to 5.5V   (unless otherwise stated)   Operating temperature -40°C ≤TA ≤+85°C for Industrial   -40°C ≤TA ≤+125°C for Extended |                    |     |       |            |  |  |  |

|--------------|-----------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|------------|--|--|--|

| Param<br>No. | Symbol    | Characteri                              | Min                                                                                                                                                              | Тур <sup>(2)</sup> | Max | Units | Conditions |  |  |  |

| CA10         | TioF      | Port Output Fall Ti                     | me                                                                                                                                                               |                    | 10  | 25    | ns         |  |  |  |

| CA11         | TioR      | Port Output Rise T                      | īme                                                                                                                                                              |                    | 10  | 25    | ns         |  |  |  |

| CA20         | Tcwf      | Pulse Width to Trig<br>CAN Wake-up Filt |                                                                                                                                                                  | 500                | —   |       | ns         |  |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

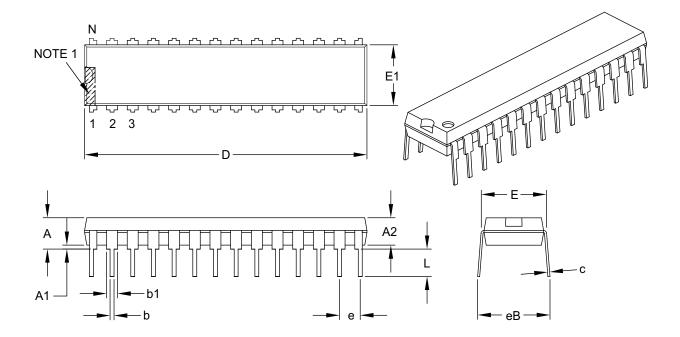

## 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    |       | INCHES   |       |

|----------------------------|----------|-------|----------|-------|

| Dimension                  | n Limits | MIN   | NOM      | MAX   |

| Number of Pins             | Ν        |       | 28       |       |

| Pitch                      | е        |       | .100 BSC |       |

| Top to Seating Plane       | Α        | -     | -        | .200  |

| Molded Package Thickness   | A2       | .120  | .135     | .150  |

| Base to Seating Plane      | A1       | .015  | -        | -     |

| Shoulder to Shoulder Width | Е        | .290  | .310     | .335  |

| Molded Package Width       | E1       | .240  | .285     | .295  |

| Overall Length             | D        | 1.345 | 1.365    | 1.400 |

| Tip to Seating Plane       | L        | .110  | .130     | .150  |

| Lead Thickness             | С        | .008  | .010     | .015  |

| Upper Lead Width           | b1       | .040  | .050     | .070  |

| Lower Lead Width           | b        | .014  | .018     | .022  |

| Overall Row Spacing §      | eВ       | -     | -        | .430  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

## INDEX

#### Numerics

12-bit Analog-to-Digital Converter (A/D) Module ...... 113

| Α                                         |         |

|-------------------------------------------|---------|

| A/D                                       | 113     |

| Aborting a Conversion                     |         |

| ADCHS Register                            |         |

| ADCON1 Register                           | 113     |

| ADCON2 Register                           | 113     |

| ADCON3 Register                           | 113     |

| ADCSSL Register                           |         |

| ADPCFG Register                           |         |

| Configuring Analog Port Pins              | 60, 119 |

| Connection Considerations                 | 119     |

| Conversion Operation                      |         |

| Effects of a Reset                        |         |

| Operation During CPU Idle Mode            | 118     |

| Operation During CPU Sleep Mode           | 118     |

| Output Formats                            |         |

| Power-Down Modes                          |         |

| Programming the Sample Trigger            |         |

| Register Map                              |         |

| Result Buffer                             |         |

| Sampling Requirements                     |         |

| Selecting the Conversion Sequence         |         |

| AC Characteristics                        |         |

| Load Conditions                           |         |

| AC Temperature and Voltage Specifications | 160     |

| ADC                                       |         |

| Selecting the Conversion Clock            |         |

| ADC Conversion Speeds                     | 116     |

| Address Generator Units                   |         |

| Alternate Vector Table                    |         |

| Analog-to-Digital Converter. See ADC.     |         |

| Assembler                                 |         |

| MPASM Assembler                           |         |

| Automatic Clock Stretch                   |         |

| During 10-bit Addressing (STREN = 1)      |         |

| During 7-bit Addressing (STREN = 1)       |         |

| Receive Mode                              |         |

| Transmit Mode                             | 100     |

## В

| Bandgap Start-up Time              |

|------------------------------------|

| Requirements166                    |

| Timing Characteristics166          |

| Barrel Shifter                     |

| Bit-Reversed Addressing 46         |

| Example                            |

| Implementation46                   |

| Modifier Values Table 47           |

| Sequence Table (16-Entry)47        |

| Block Diagrams                     |

| 12-bit ADC Functional113           |

| 16-bit Timer1 Module73             |

| 16-bit Timer279                    |

| 16-bit Timer379                    |

| 32-bit Timer2/378                  |

| DSP Engine24                       |

| dsPIC30F201112                     |

| dsPIC30F201213                     |

| dsPIC30F301315                     |

| External Power-on Reset Circuit131 |

| I <sup>2</sup> C                         |

|------------------------------------------|

| Input Capture Mode 83                    |

| Oscillator System                        |

| Output Compare Mode 87                   |

| Reset System 129                         |

| Shared Port Structure                    |

| SPI                                      |

| SPI Master/Slave Connection              |

| UART Receiver                            |

| UART Transmitter                         |

| BOR Characteristics                      |

| BOR. See Brown-out Reset.                |

| Brown-out Reset                          |

| Characteristics                          |

|                                          |

| Timing Requirements 165                  |

| C                                        |

| C Compilers                              |

| MPLAB C18 146                            |

| CAN Module                               |

| I/O Timing Characteristics               |

|                                          |

| I/O Timing Requirements                  |

| CLROOT and 1/O Timing<br>Characteristics |

|                                          |

| Requirements                             |

| Code Examples                            |

| Data EEPROM Block Erase                  |

| Data EEPROM Block Write                  |

| Data EEPROM Read                         |

| Data EEPROM Word Erase                   |

| Data EEPROM Word Write                   |

| Erasing a Row of Program Memory 51       |

| Initiating a Programming Sequence        |

| Loading Write Latches                    |

| Code Protection 123                      |

| Control Registers 50                     |

| NVMADR 50                                |

| NVMADRU 50                               |

| NVMCON                                   |

| NVMKEY 50                                |

| Core Architecture                        |

| Overview19                               |

| CPU Architecture Overview 19             |

| Customer Change Notification Service     |

| Customer Notification Service            |

| Customer Support 205                     |

| D                                        |

| Data Accumulators and Adder/Subtractor   |

|                                          |

| Data Accumulators and Adder/Subtractor       | . 25 |

|----------------------------------------------|------|

| Data Space Write Saturation                  | . 27 |

| Overflow and Saturation                      | . 25 |

| Round Logic                                  | . 26 |

| Write-Back                                   | . 26 |

| Data Address Space                           | . 35 |

| Alignment                                    | . 38 |

| Alignment (Figure)                           | . 38 |

| Effect of Invalid Memory Accesses (Table)    | . 38 |

| MCU and DSP (MAC Class) Instructions Example | . 37 |

| Memory Map 35                                | , 36 |

| Near Data Space                              | . 39 |

| Software Stack                               | . 39 |

| Spaces                                       | . 38 |

| Width                                        | . 38 |

| Data EEPROM Memory                           | . 55 |

| Erasing                                      | . 56 |

| Erasing, Block                               | . 56 |

## dsPIC30F2011/2012/3012/3013

NOTES:

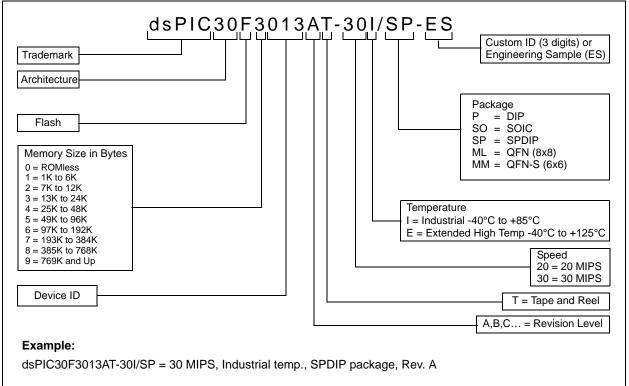

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.