Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detalls                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | dsPIC                                                                        |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 30 MIPs                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 12                                                                           |

| Program Memory Size        | 24KB (8K x 24)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 1K x 8                                                                       |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x12b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Through Hole                                                                 |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                      |

| Supplier Device Package    | 18-PDIP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f3012-30i-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **High-Performance, 16-bit Digital Signal Controllers**

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

### High-Performance Modified RISC CPU:

- Modified Harvard architecture

- C compiler optimized instruction set architecture

- Flexible addressing modes

- 83 base instructions

- 24-bit wide instructions, 16-bit wide data path

- Up to 24 Kbytes on-chip Flash program space

- · Up to 2 Kbytes of on-chip data RAM

- Up to 1 Kbytes of nonvolatile data EEPROM

- 16 x 16-bit working register array

- Up to 30 MIPS operation:

- DC to 40 MHz external clock input

- 4 MHz 10 MHz oscillator input with PLL active (4x, 8x, 16x)

- Up to 21 interrupt sources:

- 8 user-selectable priority levels

- 3 external interrupt sources

- 4 processor trap sources

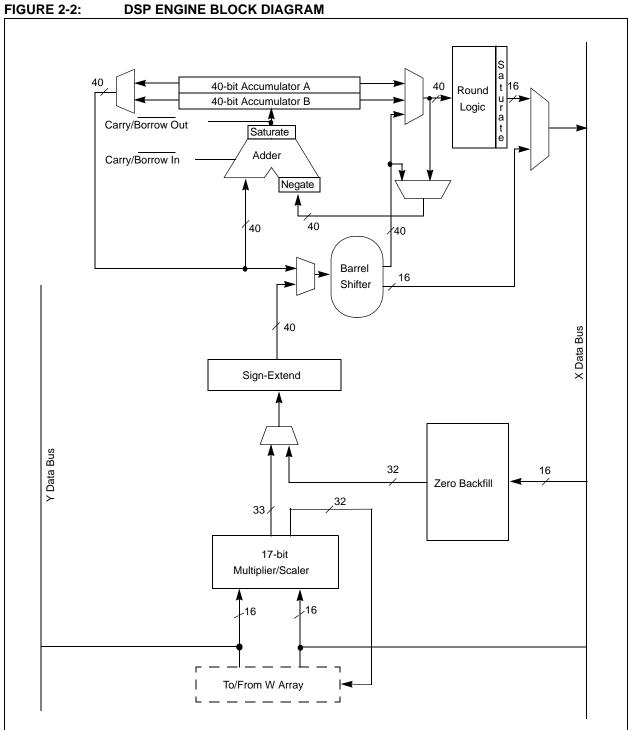

### **DSP Features:**

- Dual data fetch

- · Modulo and Bit-Reversed modes

- Two 40-bit wide accumulators with optional saturation logic

- 17-bit x 17-bit single-cycle hardware fractional/ integer multiplier

- All DSP instructions are single cycle

- Multiply-Accumulate (MAC) operation

- Single-cycle ±16 shift

### **Peripheral Features:**

- High-current sink/source I/O pins: 25 mA/25 mA

- Three 16-bit timers/counters; optionally pair up 16-bit timers into 32-bit timer modules

- 16-bit Capture input functions

- 16-bit Compare/PWM output functions

- 3-wire SPI modules (supports four Frame modes)

- I<sup>2</sup>C<sup>™</sup> module supports Multi-Master/Slave mode and 7-bit/10-bit addressing

- Up to two addressable UART modules with FIFO buffers

### **Analog Features:**

- 12-bit Analog-to-Digital Converter (ADC) with:

- 200 ksps conversion rate

- Up to 10 input channels

- Conversion available during Sleep and Idle

- Programmable Low-Voltage Detection (PLVD)

- Programmable Brown-out Reset

### **Special Microcontroller Features:**

- Enhanced Flash program memory:

- 10,000 erase/write cycle (min.) for industrial temperature range, 100K (typical)

- Data EEPROM memory:

- 100,000 erase/write cycle (min.) for industrial temperature range, 1M (typical)

- Self-reprogrammable under software control

- Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Flexible Watchdog Timer (WDT) with on-chip low-power RC oscillator for reliable operation

- Fail-Safe Clock Monitor operation:

- Detects clock failure and switches to on-chip low-power RC oscillator

- Programmable code protection

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- Selectable Power Management modes:

- Sleep, Idle and Alternate Clock modes

### **CMOS Technology:**

- Low-power, high-speed Flash technology

- Wide operating voltage range (2.5V to 5.5V)

- Industrial and Extended temperature ranges

- Low-power consumption

### 3.0 MEMORY ORGANIZATION

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

### 3.1 Program Address Space

The program address space is 4M instruction words. The program space memory maps for the dsPIC30F2011/2012/3012/3013 devices is shown in Figure 3-1.

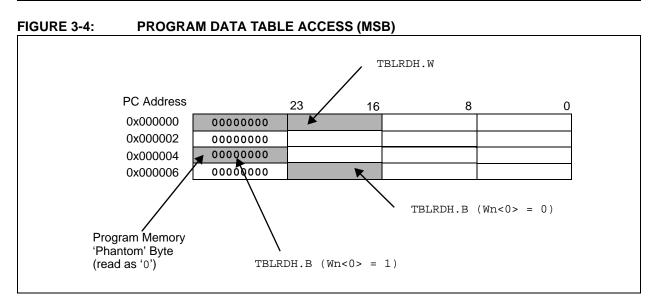

Program memory is addressable by a 24-bit value from either the 23-bit PC, table instruction Effective Address (EA), or data space EA, when program space is mapped into data space as defined by Table 3-1. Note that the program space address is incremented by two between successive program words in order to provide compatibility with data space addressing.

User program space access is restricted to the lower 4M instruction word address range (0x000000 to 0x7FFFFE) for all accesses other than TBLRD/TBLWT, which uses TBLPAG<7> to determine user or configuration space access. In Table 3-1, Program Space Address Construction, bit 23 allows access to the Device ID, the User ID and the Configuration bits. Otherwise, bit 23 is always clear.

#### 3.1.2 DATA ACCESS FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word program space page. This provides transparent access of stored constant data from X data space without the need to use special instructions (i.e., TBLRDL/H, TBLWTL/H instructions).

Program space access through the data space occurs if the MSb of the data space EA is set and program space visibility is enabled by setting the PSV bit in the Core Control register (CORCON). The functions of CORCON are discussed in **Section 2.4** "**DSP Engine**".

Data accesses to this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Note that the upper half of addressable data space is always part of the X data space. Therefore, when a DSP operation uses program space mapping to access this memory region, Y data space should typically contain state (variable) data for DSP operations, whereas X data space should typically contain coefficient (constant) data.

Although each data space address, 0x8000 and higher, maps directly into a corresponding program memory address (see Figure 3-5), only the lower 16 bits of the 24-bit program word are used to contain the data. The upper 8 bits should be programmed to force an illegal instruction to maintain machine robustness. Refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157) for details on instruction encoding. Note that by incrementing the PC by 2 for each program memory word, the LS 15 bits of data space addresses directly map to the LS 15 bits in the corresponding program space addresses. The remaining bits are provided by the Program Space Visibility Page register, PSVPAG<7:0>, as shown in Figure 3-5.

Note: PSV access is temporarily disabled during table reads/writes.

For instructions that use PSV which are executed outside a REPEAT loop:

- The following instructions require one instruction cycle in addition to the specified execution time:

- MAC class of instructions with data operand prefetch

- MOV instructions

- MOV.D instructions

- All other instructions require two instruction cycles in addition to the specified execution time of the instruction.

For instructions that use PSV which are executed inside a REPEAT loop:

- The following instances require two instruction cycles in addition to the specified execution time of the instruction:

- Execution in the first iteration

- Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

- Any other iteration of the REPEAT loop allow the instruction accessing data, using PSV, to execute in a single cycle.

### 4.2.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. It is important to realize that the address boundaries check for addresses less than, or greater than the upper (for incrementing buffers), and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes may, therefore, jump beyond boundaries and still be adjusted correctly.

**Note:** The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the EA. When an address offset (e.g., [W7+W2]) is used, Modulo address correction is performed, but the contents of the register remain unchanged.

### 4.3 Bit-Reversed Addressing

Bit-Reversed Addressing is intended to simplify data re-ordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which may be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

### 4.3.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing is enabled when:

- BWM (W register selection) in the MODCON register is any value other than '15' (the stack cannot be accessed using Bit-Reversed Addressing) and

- The BREN bit is set in the XBREV register and

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment.

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, then the last 'N' bits of the data buffer Start address must be zeros.

XB<14:0> is the bit-reversed address modifier or 'pivot point' which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

| Note: | All bit-reversed EA calculations assume   |

|-------|-------------------------------------------|

|       | word-sized data (LSb of every EA is       |

|       | always clear). The XB value is scaled     |

|       | accordingly to generate compatible (byte) |

|       | addresses.                                |

When enabled, Bit-Reversed Addressing is only executed for register indirect with pre-increment or post-increment addressing and word-sized data writes. It does not function for any other addressing mode or for byte-sized data. Normal addresses are generated instead. When Bit-Reversed Addressing is active, the W address pointer is always added to the address modifier (XB) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

| Note: | Modulo Addressing and Bit-Reversed         |

|-------|--------------------------------------------|

|       | Addressing should not be enabled           |

|       | together. In the event that the user       |

|       | attempts to do this, Bit-Reversed Address- |

|       | ing assumes priority when active for the X |

|       | WAGU, and X WAGU Modulo Addressing         |

|       | is disabled. However, Modulo Addressing    |

|       | continues to function in the X RAGU.       |

If Bit-Reversed Addressing has already been enabled by setting the BREN bit (XBREV<15>), then a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the bit-reversed pointer.

### 5.6.3 LOADING WRITE LATCHES

Example 5-2 shows a sequence of instructions that can be used to load the 96 bytes of write latches. 32 TBLWTL and 32 TBLWTH instructions are needed to load the write latches selected by the Table Pointer.

### 5.6.4 INITIATING THE PROGRAMMING SEQUENCE

For protection, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPs as shown in Example 5-3.

### EXAMPLE 5-2: LOADING WRITE LATCHES

| ; Set up a pointer to the first program memory 3 | location to be written                  |

|--------------------------------------------------|-----------------------------------------|

| ; program memory selected, and writes enabled    |                                         |

| MOV #0x0000,W0                                   | i                                       |

| MOV W0, TBLPAG                                   | ; Initialize PM Page Boundary SFR       |

| MOV #0x6000,W0                                   | ; An example program memory address     |

| ; Perform the TBLWT instructions to write the la | atches                                  |

| ; 0th_program_word                               |                                         |

| MOV #LOW_WORD_0,W2                               | ;                                       |

| MOV #HIGH_BYTE_0,W3                              | i                                       |

| TBLWTL W2 <sub>,</sub> [W0]                      | ; Write PM low word into program latch  |

| TBLWTH W3,[W0++]                                 | ; Write PM high byte into program latch |

| ; lst_program_word                               |                                         |

| MOV #LOW_WORD_1,W2                               | ;                                       |

| MOV #HIGH_BYTE_1,W3                              | ;                                       |

| TBLWTL W2,[W0]                                   | ; Write PM low word into program latch  |

| TBLWTH W3,[W0++]                                 | ; Write PM high byte into program latch |

| ; 2nd_program_word                               |                                         |

| MOV #LOW_WORD_2,W2                               | ;                                       |

| MOV #HIGH_BYTE_2,W3                              | ;                                       |

| TBLWTL W2 <sub>,</sub> [W0]                      | ; Write PM low word into program latch  |

| TBLWTH W3 <sub>,</sub> [W0++]                    | ; Write PM high byte into program latch |

| •                                                |                                         |

| •                                                |                                         |

| •                                                |                                         |

| ; 31st_program_word                              |                                         |

| MOV #LOW_WORD_31,W2                              | ;                                       |

| MOV #HIGH_BYTE_31,W3                             | ;                                       |

| TBLWTL W2 <sub>,</sub> [W0]                      | ; Write PM low word into program latch  |

| TBLWTH W3, [W0++]                                | ; Write PM high byte into program latch |

|                                                  |                                         |

Note: In Example 5-2, the contents of the upper byte of W3 has no effect.

### EXAMPLE 5-3: INITIATING A PROGRAMMING SEQUENCE

| DISI | #5          | ; Block all interrupts with priority <7 for |

|------|-------------|---------------------------------------------|

|      |             | ; next 5 instructions                       |

| MOV  | #0x55,W0    | i                                           |

| MOV  | WONVMKEY    | ; Write the 0x55 key                        |

| MOV  | #0xAA,W1    | ;                                           |

| MOV  | W1,NVMKEY   | ; Write the OxAA key                        |

| BSET | NVMCON, #WR | ; Start the erase sequence                  |

| NOP  |             | ; Insert two NOPs after the erase           |

| NOP  |             | ; command is asserted                       |

|      |             |                                             |

### EXAMPLE 6-5: DATA EEPROM BLOCK WRITE

| MOV        | <pre>#LOW_ADDR_WORD,W0</pre>       | ; | Init pointer                                                     |

|------------|------------------------------------|---|------------------------------------------------------------------|

| MOV        | #HIGH_ADDR_WORD,W1                 |   |                                                                  |

| MOV        | W1,TBLPAG                          |   |                                                                  |

| MOV        | #data1,W2                          | ; | Get 1st data                                                     |

| TBLWTL     | W2 [ W0]++                         | ; | write data                                                       |

| MOV        | #data2,W2                          | ; | Get 2nd data                                                     |

| TBLWTL     | W2,[ W0]++                         | ; | write data                                                       |

| MOV        | #data3,W2                          | ; | Get 3rd data                                                     |

| TBLWTL     | W2,[ W0]++                         | ; | write data                                                       |

| MOV        | #data4,W2                          | ; | Get 4th data                                                     |

| TBLWTL     | W2,[ W0]++                         | ; | write data                                                       |

| MOV        | #data5,W2                          | ; | Get 5th data                                                     |

| TBLWTL     | W2,[ W0]++                         | ; | write data                                                       |

| MOV        | #data6,W2                          | ; | Get 6th data                                                     |

| TBLWTL     | W2,[ W0]++                         | ; | write data                                                       |

| MOV        | #data7,W2                          |   | Get 7th data                                                     |

| TBLWTL     | W2,[ W0]++                         |   | write data                                                       |

| MOV        | #data8,W2                          |   | Get 8th data                                                     |

| TBLWTL     | W2,[ W0]++                         |   | write data                                                       |

| MOV        | #data9,W2                          |   | Get 9th data                                                     |

| TBLWTL     | W2,[ W0]++                         |   | write data                                                       |

| MOV        | #data10,W2                         |   | Get 10th data                                                    |

| TBLWTL     | W2,[ W0]++                         |   | write data                                                       |

| MOV        | #data11,W2                         |   | Get 11th data                                                    |

| TBLWTL     | W2,[ W0]++                         |   | write data                                                       |

| MOV        | #data12,W2                         |   | Get 12th data                                                    |

| TBLWTL     | W2,[ W0]++                         |   | write data                                                       |

| MOV        | #data13,W2                         |   | Get 13th data                                                    |

| TBLWTL     | W2 [ W0]++                         |   | write data                                                       |

| MOV        | #data14,W2                         |   | Get 14th data                                                    |

| TBLWTL     | W2 [ W0]++                         |   | write data                                                       |

| MOV        | #data15,W2                         |   | Get 15th data                                                    |

| TBLWTL     | W2 [ W0]++                         |   | write data                                                       |

| MOV        | #data16,W2                         |   | Get 16th data                                                    |

| TBLWTL     | W2 [ W0]++                         |   | write data. The NVMADR captures last table access address.       |

| MOV        | #0x400A,W0                         |   | Select data EEPROM for multi word op                             |

| MOV        | W0,NVMCON<br>#5                    |   | Operate Key to allow program operation                           |

| DISI       | # 5                                |   | Block all interrupts with priority <7 for<br>next 5 instructions |

| MOV        | #0x55,W0                           | ' | liext 5 filstructions                                            |

|            |                                    |   | Write the Over key                                               |

| MOV<br>MOV | W0 <sub>,</sub> NVMKEY<br>#0xAA,W1 | ' | Write the 0x55 key                                               |

| MOV        |                                    |   | Write the 0xAA key                                               |

| BSET       | W1,NVMKEY<br>NVMCON,#WR            |   | Start write cycle                                                |

| NOP        | TAALICOTA / WAIL                   | ' | Deale wille Cycle                                                |

| NOP        |                                    |   |                                                                  |

| INCE       |                                    |   |                                                                  |

|            |                                    |   |                                                                  |

### 6.4 Write Verify

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

### 6.5 Protection Against Spurious Write

There are conditions when the device may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been built-in. On power-up, the WREN bit is cleared; also, the Power-up Timer prevents EEPROM write.

The write initiate sequence and the WREN bit together help prevent an accidental write during brown-out, power glitch, or software malfunction.

### TABLE 7-1: PORTB REGISTER MAP FOR dsPIC30F2011/3012

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset State         |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| TRISB       | 02C6  | _      | _      | —      | _      | _      | _      | _     | —     | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 0000 0000 1111 1111 |

| PORTB       | 02C8  |        | _      | -      | _      | _      | -      |       | _     | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | 0000 0000 0000 0000 |

| LATB        | 02CB  | —      | _      | _      | _      | _      | _      |       | _     | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | 0000 0000 0000 0000 |

Legend: — = unimplemented bit, read as '0'

#### TABLE 7-2: PORTB REGISTER MAP FOR dsPIC30F2012/3013

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset State         |

|-------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| TRISB       | 02C6  | —      | —      | _      | _      | —      | _      | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 0000 0011 1111 1111 |

| PORTB       | 02C8  | _      | _      |        |        | -      | _      | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | 0000 0000 0000 0000 |

| LATB        | 02CB  | _      | —      | _      | _      | _      | —      | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | 0000 0000 0000 0000 |

Legend: — = unimplemented bit, read as '0'

### TABLE 7-3: PORTC REGISTER MAP FOR dsPIC30F2011/2012/3012/3013

| SFR<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset State         |

|-------------|-------|---------|---------|---------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------------|

| TRISC       | 02CC  | TRISC15 | TRISC14 | TRISC13 | _      |        | —      | _     |       |       |       | —     | _     | —     |       | _     | _     | 1110 0000 0000 0000 |

| PORTC       | 02CE  | RC15    | RC14    | RC13    | _      | _      | _      | _     | _     | _     | _     | _     | _     | -     |       | _     | _     | 0000 0000 0000 0000 |

| LATC        | 02D0  | LATC15  | LATC14  | LATC13  |        | -      | _      |       |       | -     | -     | —     |       | —     | _     |       | _     | 0000 0000 0000 0000 |

Legend: — = unimplemented bit, read as '0'

### TABLE 7-4: PORTD REGISTER MAP FOR dsPIC30F2011/3012

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Reset State         |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--------|---------------------|

| TRISD       | 02D2  | —      | —      | —      | —      | —      | —      | _     | —     | —     | —     | _     | —     | _     | _     | —     | TRISD0 | 0000 0000 0000 0001 |

| PORTD       | 02D4  |        | _      | _      | _      | _      | _      | _     | _     | _     |       | _     | _     | _     | _     | _     | RD0    | 0000 0000 0000 0000 |

| LATD        | 02D6  | -      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     | _     | _     | _     | _     | LATD0  | 0000 0000 0000 0000 |

Legend: — = unimplemented bit, read as '0'

### TABLE 10-1: TIMER2/3 REGISTER MAP

| 0       |

|---------|

| © 2010  |

| 10      |

| ≦       |

| Microch |

| ch      |

| ÷.      |

| Te      |

| echi    |

| nol     |

| nology  |

| _       |

| nc.     |

|         |

| SFR Name | Addr. | Bit 15 | Bit 14                                                     | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7        | Bit 6 | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset State         |

|----------|-------|--------|------------------------------------------------------------|--------|--------|--------|--------|-------|-------|--------------|-------|--------|--------|-------|-------|-------|-------|---------------------|

| TMR2     | 0106  |        |                                                            |        |        |        |        |       | Ti    | mer2 Registe | er    |        |        |       |       |       |       | uuuu uuuu uuuu uuuu |

| TMR3HLD  | 0108  |        | Timer3 Holding Register (for 32-bit timer operations only) |        |        |        |        |       |       |              |       |        |        |       |       |       |       | uuuu uuuu uuuu      |

| TMR3     | 010A  |        | Timer3 Register                                            |        |        |        |        |       |       |              |       |        |        |       |       |       |       | uuuu uuuu uuuu uuuu |

| PR2      | 010C  |        |                                                            |        |        |        |        |       | Pe    | riod Registe | r 2   |        |        |       |       |       |       | 1111 1111 1111 1111 |

| PR3      | 010E  |        |                                                            |        |        |        |        |       | Pe    | riod Registe | r 3   |        |        |       |       |       |       | 1111 1111 1111 1111 |

| T2CON    | 0110  | TON    | —                                                          | TSIDL  | _      | —      | -      | Ι     | —     | _            | TGATE | TCKPS1 | TCKPS0 | T32   | _     | TCS   |       | 0000 0000 0000 0000 |

| T3CON    | 0112  | TON    | _                                                          | TSIDL  | —      | —      | _      | _     | _     | —            | TGATE | TCKPS1 | TCKPS0 | —     | _     | TCS   | —     | 0000 0000 0000 0000 |

**Legend:** u = uninitialized bit; — = unimplemented bit, read as '0'

Note: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

NOTES:

### 15.5.2 FRAMING ERROR (FERR)

The FERR bit (UxSTA<2>) is set if a '0' is detected instead of a Stop bit. If two Stop bits are selected, both Stop bits must be '1', otherwise FERR will be set. The read-only FERR bit is buffered along with the received data. It is cleared on any Reset.

### 15.5.3 PARITY ERROR (PERR)

The PERR bit (UxSTA<3>) is set if the parity of the received word is incorrect. This error bit is applicable only if a Parity mode (odd or even) is selected. The read-only PERR bit is buffered along with the received data bytes. It is cleared on any Reset.

### 15.5.4 IDLE STATUS

When the receiver is active (i.e., between the initial detection of the Start bit and the completion of the Stop bit), the RIDLE bit (UxSTA<4>) is '0'. Between the completion of the Stop bit and detection of the next Start bit, the RIDLE bit is '1', indicating that the UART is Idle.

### 15.5.5 RECEIVE BREAK

The receiver will count and expect a certain number of bit times based on the values programmed in the PDSEL (UxMODE<2:1>) and STSEL (UxMODE<0>) bits.

If the break is longer than 13 bit times, the reception is considered complete after the number of bit times specified by PDSEL and STSEL. The URXDA bit is set, FERR is set, zeros are loaded into the receive FIFO, interrupts are generated if appropriate and the RIDLE bit is set.

When the module receives a long break signal and the receiver has detected the Start bit, the data bits and the invalid Stop bit (which sets the FERR), the receiver must wait for a valid Stop bit before looking for the next Start bit. It cannot assume that the break condition on the line is the next Start bit.

Break is regarded as a character containing all '0's with the FERR bit set. The Break character is loaded into the buffer. No further reception can occur until a Stop bit is received. Note that RIDLE goes high when the Stop bit has not yet been received.

### 15.6 Address Detect Mode

Setting the ADDEN bit (UxSTA<5>) enables this special mode in which a 9th bit (URX8) value of '1' identifies the received word as an address, rather than data. This mode is only applicable for 9-bit data communication. The URXISEL control bit does not have any impact on interrupt generation in this mode since an interrupt (if enabled) will be generated every time the received word has the 9th bit set.

### 15.7 Loopback Mode

Setting the LPBACK bit enables this special mode in which the UxTX pin is internally connected to the UxRX pin. When configured for the Loopback mode, the UxRX pin is disconnected from the internal UART receive logic. However, the UxTX pin still functions as in a normal operation.

To select this mode:

- a) Configure UART for desired mode of operation.

- b) Set LPBACK = 1 to enable Loopback mode.

- c) Enable transmission as defined in **Section 15.3** "**Transmitting Data**".

### 15.8 Baud Rate Generator

The UART has a 16-bit Baud Rate Generator to allow maximum flexibility in baud rate generation. The Baud Rate Generator register (UxBRG) is readable and writable. The baud rate is computed as follows:

- BRG = 16-bit value held in UxBRG register (0 through 65535)

- FCY = Instruction Clock Rate (1/Tcy)

The baud rate is given by Equation 15-1.

### EQUATION 15-1: BAUD RATE

Baud Rate = FCY / (16\*(BRG+1))

Therefore, the maximum baud rate possible is:

FCY /16 (if BRG = 0),

and the minimum baud rate possible is:

Fcy / (16\* 65536).

With a full 16-bit Baud Rate Generator at 30 MIPS operation, the minimum baud rate achievable is 28.5 bps.

### 15.9 Auto-Baud Support

To allow the system to determine baud rates of received characters, the input can be optionally linked to a selected capture input (IC1 for UART1 and IC2 for UART2). To enable this mode, you must program the input capture module to detect the falling and rising edges of the Start bit.

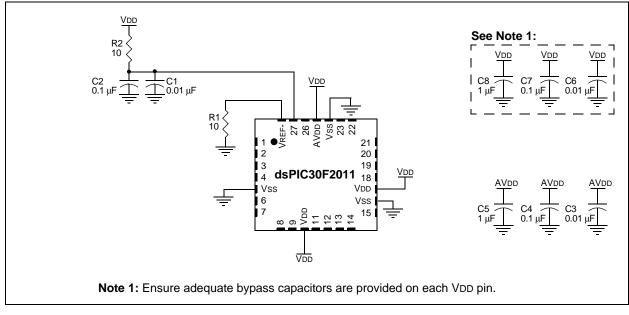

### 16.7 ADC Speeds

The dsPIC30F 12-bit ADC specifications permit a maximum of 200 ksps sampling rate. Table 16-1 summarizes the conversion speeds for the dsPIC30F 12-bit ADC and the required operating conditions.

Figure 16-2 depicts the recommended circuit for the conversion rates above 200 ksps. The dsPIC30F2011 is shown as an example.

|                                  |                | (                    | dsPIC30F           | 12-bit Al          | DC Conversion R | ates                    |

|----------------------------------|----------------|----------------------|--------------------|--------------------|-----------------|-------------------------|

| Speed                            | TAD<br>Minimum | Sampling<br>Time Min | R <sub>s</sub> Max | Vdd                | Temperature     | Channel Configuration   |

| Up to 200<br>ksps <sup>(1)</sup> | 334 ns         | 1 Tad                | 2.5 kΩ             | 4.5V<br>to<br>5.5V | -40°C to +85°C  | ANX CHX ADC             |

| Up to 100<br>ksps                | 668 ns         | 1 Tad                | 2.5 kΩ             | 3.0V<br>to<br>5.5V | -40°C to +125°C | ANX ADC<br>ANX or VREF- |

**Note 1:** External VREF- and VREF+ pins must be used for correct operation. See Figure 16-2 for recommended circuit.

### FIGURE 16-2: ADC VOLTAGE REFERENCE SCHEMATIC

### 16.13 Configuring Analog Port Pins

The use of the ADPCFG and TRIS registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CH0SA<3:0>/CH0SB<3:0> bits and the TRIS bits.

When reading the PORT register, all pins configured as analog input channels will read as cleared.

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin that is defined as a digital input (including the ANx pins) may cause the input buffer to consume current that exceeds the device specifications.

### 16.14 Connection Considerations

The analog inputs have diodes to VDD and VSS as ESD protection. This requires that the analog input be between VDD and VSS. If the input voltage exceeds this range by greater than 0.3V (either direction), one of the diodes becomes forward biased and it may damage the device if the input current specification is exceeded.

An external RC filter is sometimes added for anti-aliasing of the input signal. The R component should be selected to ensure that the sampling time requirements are satisfied. Any external components connected (via high-impedance) to an analog input pin (capacitor, zener diode, etc.) should have very little leakage current at the pin.

### TABLE 17-1: OSCILLATOR OPERATING MODES

| Oscillator Mode                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XTL<br>XT<br>XT w/PLL 4x<br>XT w/PLL 8x<br>XT w/PLL 16x<br>LP<br>HS | <ul> <li>200 kHz-4 MHz crystal on OSC1:OSC2.</li> <li>4 MHz-10 MHz crystal on OSC1:OSC2.</li> <li>4 MHz-10 MHz crystal on OSC1:OSC2, 4x PLL enabled.</li> <li>4 MHz-10 MHz crystal on OSC1:OSC2, 8x PLL enabled.</li> <li>4 MHz-7.5 MHz crystal on OSC1:OSC2, 16x PLL enabled<sup>(1)</sup>.</li> <li>32 kHz crystal on SOSCO:SOSCI<sup>(2)</sup>.</li> <li>10 MHz-25 MHz crystal.</li> </ul> |

| HS/2 w/PLL 4x                                                       | 10 MHz-20 MHz crystal, divide by 2, 4x PLL enabled.                                                                                                                                                                                                                                                                                                                                           |

| HS/2 w/PLL 8x                                                       | 10 MHz-20 MHz crystal, divide by 2, 8x PLL enabled.                                                                                                                                                                                                                                                                                                                                           |

| HS/2 w/PLL 16x                                                      | 10 MHz-15 MHz crystal, divide by 2, 16x PLL enabled <sup>(1)</sup> .                                                                                                                                                                                                                                                                                                                          |

| HS/3 w/PLL 4x                                                       | 12 MHz-25 MHz crystal, divide by 3, 4x PLL enabled.                                                                                                                                                                                                                                                                                                                                           |

| HS/3 w/PLL 8x                                                       | 12 MHz-25 MHz crystal, divide by 3, 8x PLL enabled.                                                                                                                                                                                                                                                                                                                                           |

| HS/3 w/PLL 16x                                                      | 12 MHz-22.5 MHz crystal, divide by 3, 16x PLL enabled <sup>(1)</sup> .                                                                                                                                                                                                                                                                                                                        |

| EC                                                                  | External clock input (0-40 MHz).                                                                                                                                                                                                                                                                                                                                                              |

| ECIO                                                                | External clock input (0-40 MHz), OSC2 pin is I/O.                                                                                                                                                                                                                                                                                                                                             |

| EC w/PLL 4x                                                         | External clock input (4-10 MHz), OSC2 pin is I/O, 4x PLL enabled.                                                                                                                                                                                                                                                                                                                             |

| EC w/PLL 8x                                                         | External clock input (4-10 MHz), OSC2 pin is I/O, 8x PLL enabled.                                                                                                                                                                                                                                                                                                                             |

| EC w/PLL 16x                                                        | External clock input (4-7.5 MHz), OSC2 pin is I/O, 16x PLL enabled <sup>(1)</sup> .                                                                                                                                                                                                                                                                                                           |

| ERC                                                                 | External RC oscillator, OSC2 pin is Fosc/4 output <sup>(3)</sup> .                                                                                                                                                                                                                                                                                                                            |

| ERCIO                                                               | External RC oscillator, OSC2 pin is I/O <sup>(3)</sup> .                                                                                                                                                                                                                                                                                                                                      |

| FRC<br>FRC w/PLL 4x<br>FRC w/PLL 8x<br>FRC w/PLL 16x<br>LPRC        | <ul> <li>7.37 MHz internal RC oscillator.</li> <li>7.37 MHz Internal RC oscillator, 4x PLL enabled.</li> <li>7.37 MHz Internal RC oscillator, 8x PLL enabled.</li> <li>7.37 MHz Internal RC oscillator, 16x PLL enabled.</li> <li>512 kHz internal RC oscillator.</li> </ul>                                                                                                                  |

**Note 1:** dsPIC30F maximum operating frequency of 120 MHz must be met.

2: LP oscillator can be conveniently shared as system clock, as well as real-time clock for Timer1.

3: Requires external R and C. Frequency operation up to 4 MHz.

Any interrupt that is individually enabled (using the corresponding IE bit) and meets the prevailing priority level will be able to wake-up the processor. The processor will process the interrupt and branch to the ISR. The Sleep Status bit in the RCON register is set upon wake-up.

Note: In spite of various delays applied (TPOR, TLOCK and TPWRT), the crystal oscillator (and PLL) may not be active at the end of the time-out (e.g., for low-frequency crystals). In such cases, if FSCM is enabled, then the device will detect this as a clock failure and process the clock failure trap, the FRC oscillator will be enabled and the user will have to re-enable the crystal oscillator. If FSCM is not enabled, then the device will simply suspend execution of code until the clock is stable and will remain in Sleep until the oscillator clock has started.

All Resets will wake-up the processor from Sleep mode. Any Reset, other than POR, will set the Sleep Status bit. In a POR, the Sleep bit is cleared.

If the Watchdog Timer is enabled, then the processor will wake-up from Sleep mode upon WDT time-out. The Sleep and WDTO Status bits are both set.

### 17.6.2 IDLE MODE

In Idle mode, the clock to the CPU is shut down while peripherals keep running. Unlike Sleep mode, the clock source remains active.

Several peripherals have a control bit in each module that allows them to operate during Idle.

LPRC Fail-Safe Clock remains active if clock failure detect is enabled.

The processor wakes up from Idle if at least one of the following conditions has occurred:

- any interrupt that is individually enabled (IE bit is '1') and meets the required priority level

- any Reset (POR, BOR, MCLR)

- WDT time-out

Upon wake-up from Idle mode, the clock is re-applied to the CPU and instruction execution begins immediately, starting with the instruction following the PWRSAV instruction.

Any interrupt that is individually enabled (using IE bit) and meets the prevailing priority level will be able to wake-up the processor. The processor will process the interrupt and branch to the ISR. The Idle Status bit in the RCON register is set upon wake-up.

Any Reset other than POR will set the Idle Status bit. On a POR, the Idle bit is cleared.

If Watchdog Timer is enabled, then the processor will wake-up from Idle mode upon WDT time-out. The Idle and WDTO Status bits are both set.

Unlike wake-up from Sleep, there are no time delays involved in wake-up from Idle.

### 17.7 Device Configuration Registers

The Configuration bits in each device Configuration register specify some of the device modes and are programmed by a device programmer, or by using the In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) feature of the device. Each device Configuration register is a 24-bit register, but only the lower 16 bits of each register are used to hold configuration data. There are five device Configuration registers available to the user:

- 1. FOSC (0xF80000): Oscillator Configuration Register

- 2. FWDT (0xF80002): Watchdog Timer Configuration Register

- 3. FBORPOR (0xF80004): BOR and POR Configuration Register

- 4. FGS (0xF8000A): General Code Segment Configuration Register

- 5. FICD (0xF8000C): Debug Configuration Register

The placement of the Configuration bits is automatically handled when you select the device in your device programmer. The desired state of the Configuration bits may be specified in the source code (dependent on the language tool used), or through the programming interface. After the device has been programmed, the application software may read the Configuration bit values through the table read instructions. For additional information, please refer to the Programming Specifications of the device.

Note: If the code protection Configuration fuse bits (FGS<GCP> and FGS<GWRP>) have been programmed, an erase of the entire code-protected device is only possible at voltages  $VDD \ge 4.5V$ .

### 17.8 Peripheral Module Disable (PMD) Registers

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled via the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The Control and Status registers associated with the peripheral will also be disabled so writes to those registers will have no effect and read values will be invalid.

A peripheral module will only be enabled if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

- **Note 1:** If a PMD bit is set, the corresponding module is disabled after a delay of 1 instruction cycle. Similarly, if a PMD bit is cleared, the corresponding module is enabled after a delay of 1 instruction cycle (assuming the module Control registers are already configured to enable module operation).

- 2: In dsPIC30F2011, dsPIC30F3012 and dsPIC30F2012 devices, the U2MD bit is readable and writable and will be read as '1' when set.

### 17.9 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 2 is selected as a Debugger, the In-Circuit Debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. When the device has this feature enabled, some of the resources are not available for general use. These resources include the first 80 bytes of Data RAM and two I/O pins.

One of four pairs of Debug I/O pins may be selected by the user using configuration options in MPLAB IDE. These pin pairs are named EMUD/EMUC, EMUD1/EMUC1, EMUD2/EMUC2 and EMUD3/EMUC3.

In each case, the selected EMUD pin is the Emulation/Debug Data line, and the EMUC pin is the Emulation/Debug Clock line. These pins will interface to the MPLAB ICD 2 module available from Microchip. The selected pair of Debug I/O pins is used by MPLAB ICD 2 to send commands and receive responses, as well as to send and receive data. To use the In-Circuit Debugger function of the device, the design must implement ICSP connections to MCLR, VDD, VSS, PGC, PGD and the selected EMUDx/EMUCx pin pair.

This gives rise to two possibilities:

- 1. If EMUD/EMUC is selected as the Debug I/O pin pair, then only a 5-pin interface is required, as the EMUD and EMUC pin functions are multiplexed with the PGD and PGC pin functions in all dsPIC30F devices.

- If EMUD1/EMUC1, EMUD2/EMUC2 or EMUD3/EMUC3 is selected as the Debug I/O pin pair, then a 7-pin interface is required, as the EMUDx/EMUCx pin functions (x = 1, 2 or 3) are not multiplexed with the PGD and PGC pin functions.

### TABLE 18-2: INSTRUCTION SET OVERVIEW

| Base<br>Instr<br># | Assembly<br>Mnemonic |       | Assembly Syntax    | Description                              | # of<br>Words | # of<br>Cycle<br>s | Status Flags<br>Affected |

|--------------------|----------------------|-------|--------------------|------------------------------------------|---------------|--------------------|--------------------------|

| 1                  | ADD                  | ADD   | Acc                | Add Accumulators                         | 1             | 1                  | OA,OB,SA,SB              |

|                    |                      | ADD   | f                  | f = f + WREG                             | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADD   | f,WREG             | WREG = f + WREG                          | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADD   | #lit10,Wn          | Wd = lit10 + Wd                          | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wb,Ws,Wd           | Wd = Wb + Ws                             | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wb,#lit5,Wd        | Wd = Wb + lit5                           | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wso,#Slit4,Acc     | 16-bit Signed Add to Accumulator         | 1             | 1                  | OA,OB,SA,SB              |

| 2                  | ADDC                 | ADDC  | f                  | f = f + WREG + (C)                       | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADDC  | f,WREG             | WREG = f + WREG + (C)                    | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADDC  | #lit10,Wn          | Wd = lit10 + Wd + (C)                    | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADDC  | Wb,Ws,Wd           | Wd = Wb + Ws + (C)                       | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADDC  | Wb,#lit5,Wd        | Wd = Wb + lit5 + (C)                     | 1             | 1                  | C,DC,N,OV,Z              |

| 3                  | AND                  | AND   | f                  | f = f .AND. WREG                         | 1             | 1                  | N,Z                      |

|                    |                      | AND   | f,WREG             | WREG = f .AND. WREG                      | 1             | 1                  | N,Z                      |

|                    |                      | AND   | #lit10,Wn          | Wd = lit10 .AND. Wd                      | 1             | 1                  | N,Z                      |

|                    |                      | AND   | Wb,Ws,Wd           | Wd = Wb .AND. Ws                         | 1             | 1                  | N,Z                      |

|                    |                      | AND   | Wb,#lit5,Wd        | Wd = Wb .AND. lit5                       | 1             | 1                  | N,Z                      |

| 4                  | ASR                  | ASR   | f                  | f = Arithmetic Right Shift f             | 1             | 1                  | C,N,OV,Z                 |

|                    |                      | ASR   | f,WREG             | WREG = Arithmetic Right Shift f          | 1             | 1                  | C,N,OV,Z                 |

|                    |                      | ASR   | Ws,Wd              | Wd = Arithmetic Right Shift Ws           | 1             | 1                  | C,N,OV,Z                 |

|                    |                      | ASR   | Wb,Wns,Wnd         | Wnd = Arithmetic Right Shift Wb by Wns   | 1             | 1                  | N,Z                      |

|                    |                      | ASR   | Wb,#lit5,Wnd       | Wnd = Arithmetic Right Shift Wb by lit5  | 1             | 1                  | N,Z                      |

| 5                  | BCLR                 | BCLR  | f,#bit4            | Bit Clear f                              | 1             | 1                  | None                     |

|                    |                      | BCLR  | Ws,#bit4           | Bit Clear Ws                             | 1             | 1                  | None                     |

| 6                  | BRA                  | BRA   | C,Expr             | Branch if Carry                          | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | GE, Expr           | Branch if greater than or equal          | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | GEU, Expr          | Branch if unsigned greater than or equal | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | GT,Expr            | Branch if greater than                   | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | GTU, Expr          | Branch if unsigned greater than          | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | LE, Expr           | Branch if less than or equal             | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | LEU, Expr          | Branch if unsigned less than or equal    | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | LT, Expr           | Branch if less than                      | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | LTU, Expr          | Branch if unsigned less than             | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | N,Expr             | Branch if Negative                       | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | NC,Expr            | Branch if Not Carry                      | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | NN, Expr           | Branch if Not Negative                   | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | NOV, Expr          | Branch if Not Overflow                   | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | NZ,Expr            | Branch if Not Zero                       | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | OA, Expr           | Branch if Accumulator A overflow         | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | OB,Expr            | Branch if Accumulator B overflow         | 1             | 1 (2)              | None                     |

|                    |                      | BRA   |                    | Branch if Overflow                       | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | OV,Expr<br>SA,Expr | Branch if Accumulator A saturated        | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | SB,Expr            | Branch if Accumulator B saturated        | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | Expr               | Branch Unconditionally                   | 1             | 2                  | None                     |

|                    |                      | BRA   |                    | Branch if Zero                           | 1             | 1 (2)              | None                     |

|                    |                      |       | Z,Expr             | Computed Branch                          | 1             | 2                  | None                     |

| 7                  | BSET                 | BRA   | Wn<br>f #bit4      | Bit Set f                                | 1             | 1                  | None                     |

| ı                  |                      | BSET  | f,#bit4            | Bit Set Ws                               | 1             | 1                  |                          |

| 8                  | BSW                  | BSET  | Ws,#bit4           |                                          | -             |                    | None                     |

|                    | 1 D D V V            | BSW.C | Ws,Wb              | Write C bit to Ws <wb></wb>              | 1             | 1                  | None                     |

### TABLE 20-24: TYPE B TIMER (TIMER2 AND TIMER4) EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHA       | RACTERIST | ICS                                       |                       | (unles | Standard Operating Conditions: 2.5V to 5.5V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |     |         |       |                                  |  |

|--------------|-----------|-------------------------------------------|-----------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------|-------|----------------------------------|--|

| Param<br>No. | Symbol    | Characte                                  | eristic               |        | Min                                                                                                                                                                                      | Тур | Max     | Units | Conditions                       |  |

| TB10         | TtxH      | TxCK High Time                            | Synchror<br>no presc  |        | 0.5 TCY + 20                                                                                                                                                                             |     |         | ns    | Must also meet<br>parameter TB15 |  |

|              |           |                                           | Synchror with pres    |        | 10                                                                                                                                                                                       |     |         | ns    |                                  |  |

| TB11         | TtxL      | TxCK Low Time                             | Synchror<br>no presca |        | 0.5 TCY + 20                                                                                                                                                                             |     |         | ns    | Must also meet<br>parameter TB15 |  |

|              |           |                                           | Synchror with pres    |        | 10                                                                                                                                                                                       |     |         | ns    |                                  |  |

| TB15         | TtxP      | TxCK Input Period                         | Synchror<br>no presca |        | Tcy + 10                                                                                                                                                                                 | _   | _       | ns    | N = prescale<br>value            |  |

|              |           |                                           | Synchror<br>with pres |        | Greater of:<br>20 ns or<br>(TcY + 40)/N                                                                                                                                                  |     |         |       | (1, 8, 64, 256)                  |  |

| TB20         | TCKEXTMRL | Delay from Externa<br>Edge to Timer Incre |                       | lock   | 0.5 TCY                                                                                                                                                                                  | _   | 1.5 Tcy |       |                                  |  |

Note: Timer2 and Timer4 are Type B.

### TABLE 20-25: TYPE C TIMER (TIMER3 AND TIMER5) EXTERNAL CLOCK TIMING REQUIREMENTS

| АС СНА       | RACTERIST | rics                                      |                      | (unles | rd Operating (<br>s otherwise sta<br>ing temperature | a <b>ted)</b><br>e -40°( | C ≤TA ≤+8  | 35°C for | Industrial<br>r Extended      |

|--------------|-----------|-------------------------------------------|----------------------|--------|------------------------------------------------------|--------------------------|------------|----------|-------------------------------|

| Param<br>No. | Symbol    | Characte                                  | eristic              |        | Min                                                  | Тур                      | Max        | Units    | Conditions                    |

| TC10         | TtxH      | TxCK High Time                            | Synchro              | nous   | 0.5 TCY + 20                                         | _                        |            | ns       | Must also meet parameter TC15 |

| TC11         | TtxL      | TxCK Low Time                             | Synchro              | nous   | 0.5 TCY + 20                                         | _                        | _          | ns       | Must also meet parameter TC15 |

| TC15         | TtxP      | TxCK Input Period                         | Synchro<br>no preso  |        | Tcy + 10                                             |                          |            | ns       | N = prescale<br>value         |

|              |           |                                           | Synchro<br>with pres |        | Greater of:<br>20 ns or<br>(Tcy + 40)/N              |                          |            |          | (1, 8, 64, 256)               |

| TC20         | TCKEXTMRL | Delay from Externa<br>Edge to Timer Incre |                      | lock   | 0.5 TCY                                              |                          | 1.5<br>Тсү |          |                               |

Note: Timer3 and Timer5 are Type C.

### **Revision G (November 2010)**

This revision includes minor typographical and formatting changes throughout the data sheet text.

The major changes are referenced by their respective section in Table A-1.

### TABLE A-1: MAJOR SECTION UPDATES

| Section Name                                             | Update Description                                                                                                                                                        |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "High-Performance, 16-Bit Digital<br>Signal Controllers" | Added Note 1 to all QFN pin diagrams (see "Pin Diagrams").                                                                                                                |

| Section 1.0 "Device Overview"                            | Updated the Pinout I/O Descriptions for AVDD and AVSS (see Table 1-1).                                                                                                    |

| Section 17.0 "System Integration"                        | Added a shaded note on OSCTUN functionality in <b>Section 17.2.5</b> "Fast RC Oscillator (FRC)".                                                                          |

| Section 20.0 "Electrical<br>Characteristics"             | Updated the maximum value for parameter DI19 and the minimum value for parameter DI29 in the I/O Pin Input Specifications (see Table 20-8).                               |

|                                                          | Removed parameter D136 and updated the minimum, typical, maximum, and conditions for parameters D122 and D134 in the Program and EEPROM specifications (see Table 20-12). |

|                                                          | Renamed parameter AD56 to AD56a and added parameter AD56b to the 12-bit A/D Conversion Timing Requirements (see Table 20-37).                                             |

| "Product Identification System"                          | Added the "MM" package definition.                                                                                                                                        |

| Erasing, Word56                        |

|----------------------------------------|

| Protection Against Spurious Write58    |

| Reading55                              |

| Write Verify58                         |

| Writing                                |

| Writing, Block57                       |

| Writing, Word57                        |

| DC Characteristics                     |

| BOR                                    |

| Brown-out Reset                        |

| I/O Pin Input Specifications           |

| I/O Pin Output Specifications          |

| Idle Current (IIDLE)                   |

| Low-Voltage Detect                     |

| LVDL                                   |

| Operating Current (IDD)                |

| Power-Down Current (IPD)               |

| Program and EEPROM                     |

| Temperature and Voltage Specifications |

| Development Support                    |

| Device Configuration                   |

| Register Map136                        |

| Device Configuration Registers         |

| FBORPOR                                |

| FGS                                    |

| FOSC                                   |

| FWDT                                   |

| Device Overview                        |

| Disabling the UART                     |

| Divide Support                         |

| Instructions (Table)                   |

| DSP Engine                             |

| Multiplier                             |

| Dual Output Compare Match Mode         |

| Continuous Pulse Mode                  |

| Single Pulse Mode                      |

|                                        |

|                                        |

### Ε

| Electrical Characteristics                          |

|-----------------------------------------------------|

| AC                                                  |

| DC150                                               |

| Enabling and Setting Up UART                        |

| Alternate I/O107                                    |

| Setting Up Data, Parity and Stop Bit Selections 107 |

| Enabling the UART 107                               |

| Equations                                           |

| ADC Conversion Clock115                             |

| Baud Rate 109                                       |

| Serial Clock Rate 102                               |

| Errata9                                             |

| Exception Sequence                                  |

| Trap Sources67                                      |

| External Clock Timing Characteristics               |

| Type A, B and C Timer167                            |

| External Clock Timing Requirements161               |

| Type A Timer167                                     |

| Type B Timer168                                     |

| Type C Timer 168                                    |

| External Interrupt Requests70                       |

| F                                                   |

| Fast Context Saving                                 |

| Flash Program Memory                                |

| I                                                   |

| Output 156                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|