Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | dsPIC                                                                         |

| Core Size                  | 16-Bit                                                                        |

|                            | 20 MIPS                                                                       |

| Speed                      |                                                                               |

| Connectivity               | I²C, SPI, UART/USART                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 20                                                                            |

| Program Memory Size        | 24KB (8K x 24)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 1K x 8                                                                        |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 10x12b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 28-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f3013-20e-so |

#### **Table of Contents**

| 1.0   | Device Overview                                           | 11    |

|-------|-----------------------------------------------------------|-------|

| 2.0   | CPU Architecture Overview                                 | 19    |

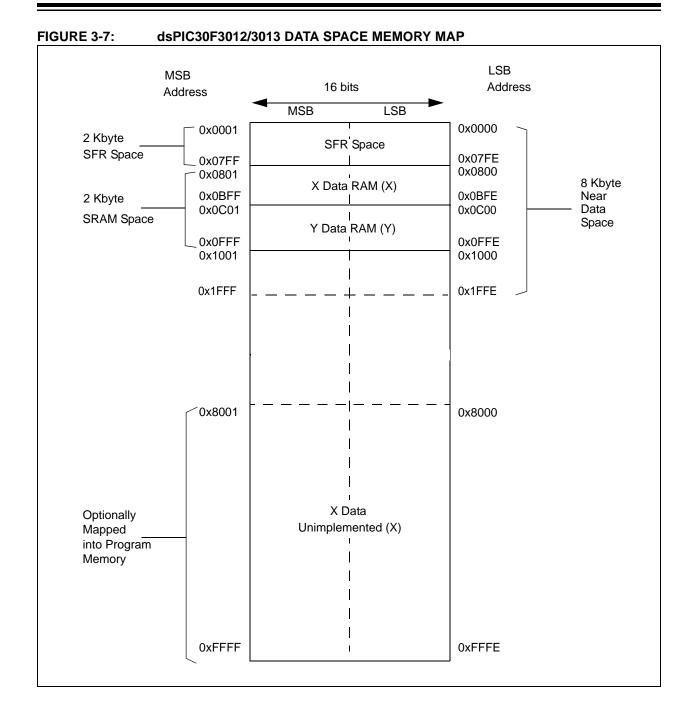

| 3.0   | Memory Organization                                       | 29    |

| 4.0   | Address Generator Units                                   | 43    |

| 5.0   | Flash Program Memory                                      | 49    |

| 6.0   | Data EEPROM Memory                                        | 55    |

| 7.0   | I/O Ports                                                 | 59    |

| 3.0   | Interrupts                                                | 65    |

| 9.0   | Timer1 Module                                             | 73    |

| 10.0  | Timer2/3 Module                                           | 77    |

| 11.0  | Input Capture Module                                      | 83    |

| 12.0  | Output Compare Module                                     | 87    |

| 13.0  | SPITM Module                                              | 93    |

| 14.0  | I2C™ Module                                               | 97    |

| 15.0  | Universal Asynchronous Receiver Transmitter (UART) Module | . 105 |

| 16.0  | 12-bit Analog-to-Digital Converter (ADC) Module           | . 113 |

| 17.0  | System Integration                                        | . 123 |

| 18.0  | Instruction Set Summary                                   | . 137 |

| 19.0  | Development Support                                       | . 145 |

|       | Electrical Characteristics                                |       |

| 21.0  | Packaging Information                                     | . 187 |

| ndex  |                                                           | . 201 |

| The N | ficrochip Web Site                                        | . 207 |

| Custo | mer Change Notification Service                           | . 207 |

| Custo | mer Support                                               | 207   |

| Read  | er Response                                               | 208   |

| ⊃rodu | ct Identification System                                  | 209   |

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

**NOTES:**

DS70139G-page 36

### 4.2.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. It is important to realize that the address boundaries check for addresses less than, or greater than the upper (for incrementing buffers), and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes may, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the EA. When an address offset (e.g., [W7+W2]) is used, Modulo address correction is performed, but the contents of the register remain unchanged.

### 4.3 Bit-Reversed Addressing

Bit-Reversed Addressing is intended to simplify data re-ordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which may be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

## 4.3.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing is enabled when:

- BWM (W register selection) in the MODCON register is any value other than '15' (the stack cannot be accessed using Bit-Reversed Addressing) and

- The BREN bit is set in the XBREV register

and

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment.

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, then the last 'N' bits of the data buffer Start address must be zeros.

XB<14:0> is the bit-reversed address modifier or 'pivot point' which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

Note: All bit-reversed EA calculations assume word-sized data (LSb of every EA is always clear). The XB value is scaled accordingly to generate compatible (byte) addresses.

When enabled, Bit-Reversed Addressing is only executed for register indirect with pre-increment or post-increment addressing and word-sized data writes. It does not function for any other addressing mode or for byte-sized data. Normal addresses are generated instead. When Bit-Reversed Addressing is active, the W address pointer is always added to the address modifier (XB) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

Note: Modulo Addressing and Bit-Reversed Addressing should not be enabled together. In the event that the user attempts to do this, Bit-Reversed Addressing assumes priority when active for the X WAGU, and X WAGU Modulo Addressing is disabled. However, Modulo Addressing continues to function in the X RAGU.

If Bit-Reversed Addressing has already been enabled by setting the BREN bit (XBREV<15>), then a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the bit-reversed pointer.

#### 10.1 Timer Gate Operation

The 32-bit timer can be placed in the Gated Time Accumulation mode. This mode allows the internal Tcy to increment the respective timer when the gate input signal (T2CK pin) is asserted high. Control bit, TGATE (T2CON<6>), must be set to enable this mode. When in this mode, Timer2 is the originating clock source. The TGATE setting is ignored for Timer3. The timer must be enabled (TON = 1) and the timer clock source set to internal (TCS = 0).

The falling edge of the external signal terminates the count operation but does not reset the timer. The user must reset the timer in order to start counting from zero.

### 10.2 ADC Event Trigger

When a match occurs between the 32-bit timer (TMR3/TMR2) and the 32-bit combined period register (PR3/PR2), or between the 16-bit timer TMR3 and the 16-bit period register PR3, a special ADC trigger event signal is generated by Timer3.

#### 10.3 Timer Prescaler

The input clock (Fosc/4 or external clock) to the timer has a prescale option of 1:1, 1:8, 1:64, and 1:256, selected by control bits, TCKPS<1:0> (T2CON<5:4> and T3CON<5:4>). For the 32-bit timer operation, the originating clock source is Timer2. The prescaler operation for Timer3 is not applicable in this mode. The prescaler counter is cleared when any of the following occurs:

- A write to the TMR2/TMR3 register

- A write to the T2CON/T3CON register

- · A device Reset, such as a POR and BOR

However, if the timer is disabled (TON = 0), the Timer 2 prescaler cannot be reset since the prescaler clock is halted.

TMR2/TMR3 is not cleared when T2CON/T3CON is written.

## 10.4 Timer Operation During Sleep Mode

The timer does not operate during CPU Sleep mode because the internal clocks are disabled.

#### 10.5 Timer Interrupt

The 32-bit timer module can generate an interrupt-on-period match or on the falling edge of the external gate signal. When the 32-bit timer count matches the respective 32-bit period register, or the falling edge of the external "gate" signal is detected, the T3IF bit (IFS0<7>) is asserted and an interrupt is generated if enabled. In this mode, the T3IF interrupt flag is used as the source of the interrupt. The T3IF bit must be cleared in software.

Enabling an interrupt is accomplished via the respective timer interrupt enable bit, T3IE (IEC0<7>).

#### 11.1.2 CAPTURE BUFFER OPERATION

Each capture channel has an associated FIFO buffer which is four 16-bit words deep. There are two status flags which provide status on the FIFO buffer:

- ICBNE Input Capture Buffer Not Empty

- ICOV Input Capture Overflow

The ICBNE is set on the first input capture event and remains set until all capture events have been read from the FIFO. As each word is read from the FIFO, the remaining words are advanced by one position within the buffer.

In the event that the FIFO is full with four capture events, and a fifth capture event occurs prior to a read of the FIFO, an overflow condition occurs and the ICOV bit is set to a logic '1'. The fifth capture event is lost and is not stored in the FIFO. No additional events are captured until all four events have been read from the buffer.

If a FIFO read is performed after the last read and no new capture event has been received, the read will yield indeterminate results.

## 11.1.3 TIMER2 AND TIMER3 SELECTION MODE

The input capture module consists of up to 8 input capture channels. Each channel can select between one of two timers for the time base, Timer2 or Timer3.

Selection of the timer resource is accomplished through SFR bit, ICTMR (ICxCON<7>). Timer3 is the default timer resource available for the input capture module.

#### 11.1.4 HALL SENSOR MODE

When the input capture module is set for capture on every edge, rising and falling, ICM<2:0> = 001, the following operations are performed by the input capture logic:

- The input capture interrupt flag is set on every edge, rising and falling.

- The interrupt on Capture mode setting bits, ICI<1:0>, is ignored since every capture generates an interrupt.

- A capture overflow condition is not generated in this mode.

# 11.2 Input Capture Operation During Sleep and Idle Modes

An input capture event generates a device wake-up or interrupt, if enabled, if the device is in CPU Idle or Sleep mode.

Independent of the timer being enabled, the input capture module wakes up from the CPU Sleep or Idle mode when a capture event occurs if ICM<2:0> = 111 and the interrupt enable bit is asserted. The same wake-up can generate an interrupt if the conditions for processing the interrupt have been satisfied. The wake-up feature is useful as a method of adding extra external pin interrupts.

## 11.2.1 INPUT CAPTURE IN CPU SLEEP MODE

CPU Sleep mode allows input capture module operation with reduced functionality. In the CPU Sleep mode, the ICI<1:0> bits are not applicable and the input capture module can only function as an external interrupt source.

The capture module must be configured for interrupt only on rising edge (ICM<2:0>=111) in order for the input capture module to be used while the device is in Sleep mode. The prescale settings of 4:1 or 16:1 are not applicable in this mode.

# 11.2.2 INPUT CAPTURE IN CPU IDLE MODE

CPU Idle mode allows input capture module operation with full functionality. In the CPU Idle mode, the Interrupt mode selected by the ICI<1:0> bits is applicable, as well as the 4:1 and 16:1 capture prescale settings which are defined by control bits ICM<2:0>. This mode requires the selected timer to be enabled. Moreover, the ICSIDL bit must be asserted to a logic '0'.

If the input capture module is defined as ICM<2:0> = 111 in CPU Idle mode, the input capture pin serves only as an external interrupt pin.

### 11.3 Input Capture Interrupts

The input capture channels have the ability to generate an interrupt based on the selected number of capture events. The selection number is set by control bits, ICI<1:0> (ICxCON<6:5>).

Each channel provides an interrupt flag (ICxIF) bit. The respective capture channel interrupt flag is located in the corresponding IFSx register.

Enabling an interrupt is accomplished via the respective capture channel interrupt enable (ICxIE) bit. The capture interrupt enable bit is located in the corresponding IEC Control register.

#### 13.0 SPI™ MODULE

Note:

This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

The Serial Peripheral Interface (SPI<sup>TM</sup>) module is a synchronous serial interface. It is useful for communicating with other peripheral devices, such as EEPROMs, shift registers, display drivers and A/D converters, or other microcontrollers. It is compatible with Motorola's SPI and SIOP interfaces. The dsPIC30F2011/2012/3012/3013 devices feature one SPI module, SPI1.

### 13.1 Operating Function Description

Figure 13-1 is a simplified block diagram of the SPI module, which consists of a 16-bit shift register, SPI1SR, used for shifting data in and out, and a buffer register, SPI1BUF. Control register SPI1CON (not shown) configures the module. Additionally, status register SPI1STAT (not shown) indicates various status conditions.

Note: See "dsPIC30F Family Reference Manual" (DS70046) for detailed information on the control and status registers.

Four I/O pins comprise the serial interface:

- SDI1 (serial data input)

- SDO1 (serial data output)

- SCK1 (shift clock input or output)

- SS1 (active-low slave select).

In Master mode operation, SCK1 is a clock output. In Slave mode, it is a clock input.

A series of eight (8) or sixteen (16) clock pulses shift out bits from the SPI1SR to SDO1 pin and simultaneously shift in data from SDI1 pin. An interrupt is generated when the transfer is complete and the interrupt flag bit (SPI1IF) is set. This interrupt can be disabled through the interrupt enable bit, SPI1IE.

The receive operation is double-buffered. When a complete byte is received, it is transferred from SPI1SR to SPI1BUF.

If the receive buffer is full when new data is being transferred from SPI1SR to SPI1BUF, the module will set the SPIROV bit indicating an overflow condition. The transfer of the data from SPI1SR to SPI1BUF is not completed and the new data is lost. The module will not respond to SCL transitions while SPIROV is '1', effectively disabling the module until SPI1BUF is read by user software.

Transmit writes are also double-buffered. The user writes to SPI1BUF. When the master or slave transfer is completed, the contents of the shift register (SPI1SR) are moved to the receive buffer. If any transmit data has been written to the buffer register, the contents of the transmit buffer are moved to SPI1SR. The received data is thus placed in SPI1BUF and the transmit data in SPI1SR is ready for the next transfer.

**Note:** Both the transmit buffer (SPI1TXB) and the receive buffer (SPI1RXB) are mapped to the same register address, SPI1BUF.

### TABLE 15-1: UART1 REGISTER MAP FOR dsPIC30F2011/2012/3012/3013

| SFR Name | Addr. | Bit 15  | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8      | Bit 7            | Bit 6            | Bit 5 | Bit 4    | Bit 3   | Bit 2               | Bit 1  | Bit 0 | Reset State         |

|----------|-------|---------|--------|--------|--------|--------|--------|-------|------------|------------------|------------------|-------|----------|---------|---------------------|--------|-------|---------------------|

| U1MODE   | 020C  | UARTEN  | _      | USIDL  | _      | _      | ALTIO  | _     | _          | WAKE             | LPBACK           | ABAUD | _        | _       | PDSEL1              | PDSEL0 | STSEL | 0000 0000 0000 0000 |

| U1STA    | 020E  | UTXISEL | _      | _      | _      | UTXBRK | UTXEN  | UTXBF | TRMT       | URXISEL1         | URXISEL0         | ADDEN | RIDLE    | PERR    | FERR                | OERR   | URXDA | 0000 0001 0001 0000 |

| U1TXREG  | 0210  | -       | _      | _      | _      | _      | _      | _     | UTX8       |                  |                  | Tra   | ansmit R | egister |                     |        |       | 0000 000u uuuu uuuu |

| U1RXREG  | 0212  |         | _      | _      | _      | _      | _      | _     | URX8       | Receive Register |                  |       |          |         | 0000 0000 0000 0000 |        |       |                     |

| U1BRG    | 0214  |         |        |        |        |        |        | Baı   | ud Rate Ge | enerator Pres    | erator Prescaler |       |          |         |                     |        |       | 0000 0000 0000 0000 |

**Legend:** u = uninitialized bit; — = unimplemented bit, read as '0'

### TABLE 15-2: UART2 REGISTER MAP FOR dsPIC30F3013<sup>(1)</sup>

| SFR<br>Name | Addr. | Bit 15  | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7            | Bit 6              | Bit 5 | Bit 4     | Bit 3   | Bit 2               | Bit 1  | Bit 0 | Reset State         |

|-------------|-------|---------|--------|--------|--------|--------|--------|-------|-----------|------------------|--------------------|-------|-----------|---------|---------------------|--------|-------|---------------------|

| U2MODE      | 0216  | UARTEN  | _      | USIDL  | _      | _      | _      | _     | _         | WAKE             | LPBACK             | ABAUD | _         | _       | PDSEL1              | PDSEL0 | STSEL | 0000 0000 0000 0000 |

| U2STA       | 0218  | UTXISEL | _      | _      | _      | UTXBRK | UTXEN  | UTXBF | TRMT      | URXISEL1         | URXISEL0           | ADDEN | RIDLE     | PERR    | FERR                | OERR   | URXDA | 0000 0001 0001 0000 |

| U2TXREG     | 021A  | _       | _      | _      | _      | _      | _      | _     | UTX8      |                  |                    | Tr    | ansmit Re | egister |                     |        |       | 0000 000u uuuu uuuu |

| U2RXREG     | 021C  | _       | _      | _      | _      | _      | _      | _     | URX8      | Receive Register |                    |       |           |         | 0000 0000 0000 0000 |        |       |                     |

| U2BRG       | 021E  |         |        |        |        |        |        | Е     | Baud Rate | Generator Pr     | enerator Prescaler |       |           |         |                     |        |       | 0000 0000 0000 0000 |

Legend: u = uninitialized bit; — = unimplemented bit, read as '0'

Note 1: UART2 is not available on dsPIC30F2011/2012/3012 devices.

2: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

### 16.7 ADC Speeds

The dsPIC30F 12-bit ADC specifications permit a maximum of 200 ksps sampling rate. Table 16-1 summarizes the conversion speeds for the dsPIC30F 12-bit ADC and the required operating conditions.

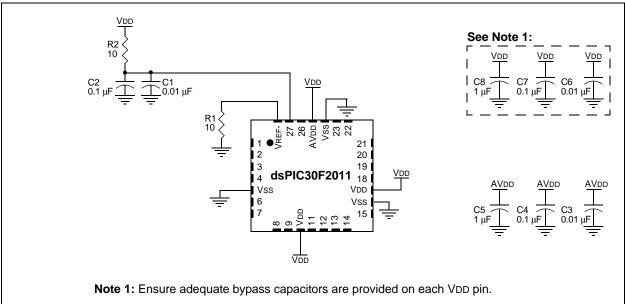

Figure 16-2 depicts the recommended circuit for the conversion rates above 200 ksps. The dsPIC30F2011 is shown as an example.

TABLE 16-1: 12-BIT ADC EXTENDED CONVERSION RATES

|                                  |                            | (                    | dsPIC30F           | 12-bit Al          | DC Conversion R | ates                      |

|----------------------------------|----------------------------|----------------------|--------------------|--------------------|-----------------|---------------------------|

| Speed                            | T <sub>AD</sub><br>Minimum | Sampling<br>Time Min | R <sub>s</sub> Max | VDD                | Temperature     | Channel Configuration     |

| Up to 200<br>ksps <sup>(1)</sup> | 334 ns                     | 1 TAD                | 2.5 kΩ             | 4.5V<br>to<br>5.5V | -40°C to +85°C  | ANX CHX ADC               |

| Up to 100<br>ksps                | 668 ns                     | 1 TAD                | 2.5 kΩ             | 3.0V<br>to<br>5.5V | -40°C to +125°C | ANX CHX ADC  ANX OF VREF- |

Note 1: External VREF+ and VREF+ pins must be used for correct operation. See Figure 16-2 for recommended circuit.

### FIGURE 16-2: ADC VOLTAGE REFERENCE SCHEMATIC

The configuration procedures in the next section provide the required setup values for the conversion speeds above 100 ksps.

## 16.7.1 200 KSPS CONFIGURATION GUIDELINE

The following configuration items are required to achieve a 200 ksps conversion rate.

- Comply with conditions provided in Table 16-1.

- Connect external VREF+ and VREF- pins following the recommended circuit shown in Figure 16-2.

- Set SSRC<2.0> = 111 in the ADCON1 register to enable the auto convert option.

- Enable automatic sampling by setting the ASAM control bit in the ADCON1 register.

- Write the SMPI<3.0> control bits in the ADCON2 register for the desired number of conversions between interrupts.

- · Configure the ADC clock period to be:

$$\frac{1}{(14+1) \times 200,000} = 334 \text{ ns}$$

by writing to the ADCS<5:0> control bits in the ADCON3 register.

Configure the sampling time to be 1 TAD by writing: SAMC<4:0> = 00001. The following figure shows the timing diagram of the ADC running at 200 ksps. The TAD selection in conjunction with the guidelines described above allows a conversion speed of 200 ksps. See Example 16-1 for code example.

### 16.8 A/D Acquisition Requirements

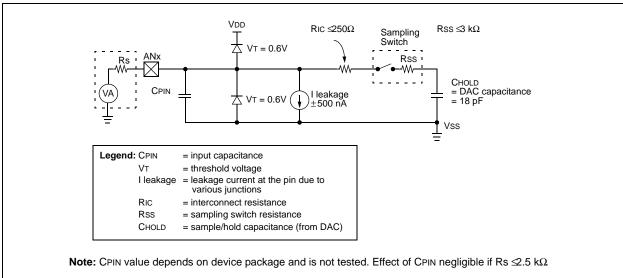

The analog input model of the 12-bit ADC is shown in Figure 16-3. The total sampling time for the A/D is a function of the internal amplifier settling time and the holding capacitor charge time.

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the voltage level on the analog input pin. The impedance source (Rs), the interconnect impedance (Ric) and the internal sampling switch (Rss) impedance combine to directly affect the time required to charge the capacitor CHOLD. The combined impedance of the analog sources must therefore be small enough to fully charge the holding capacitor within the chosen sample time. To minimize the effects of pin leakage currents on the accuracy of the ADC, the maximum recommended source impedance, Rs, is 2.5 k $\Omega$  After the analog input channel is selected (changed), this sampling function must be completed prior to starting the conversion. The internal holding capacitor will be in a discharged state prior to each sample operation.

#### FIGURE 16-3: 12-BIT A/D CONVERTER ANALOG INPUT MODEL

### 17.4 Watchdog Timer (WDT)

#### 17.4.1 WATCHDOG TIMER OPERATION

The primary function of the Watchdog Timer (WDT) is to reset the processor in the event of a software malfunction. The WDT is a free-running timer which runs off an on-chip RC oscillator, requiring no external component. Therefore, the WDT timer will continue to operate even if the main processor clock (e.g., the crystal oscillator) fails.

## 17.4.2 ENABLING AND DISABLING THE WDT

The Watchdog Timer can be "Enabled" or "Disabled" only through a Configuration bit (FWDTEN) in the Configuration register, FWDT.

Setting FWDTEN = 1 enables the Watchdog Timer. The enabling is done when programming the device. By default, after chip erase, FWDTEN bit = 1. Any device programmer capable of programming dsPIC30F devices allows programming of this and other Configuration bits.

If enabled, the WDT will increment until it overflows or "times out". A WDT time-out will force a device Reset (except during Sleep). To prevent a WDT time-out, the user must clear the Watchdog Timer using a CLRWDT instruction.

If a WDT times out during Sleep, the device will wake-up. The WDTO bit in the RCON register will be cleared to indicate a wake-up resulting from a WDT time-out.

Setting FWDTEN = 0 allows user software to enable/disable the Watchdog Timer via the SWDTEN (RCON<5>) control bit.

#### 17.5 Low-Voltage Detect

The Low-Voltage Detect (LVD) module is used to detect when the VDD of the device drops below a threshold value, VLVD, which is determined by the LVDL<3:0> bits (RCON<11:8>) and is thus user programmable. The internal voltage reference circuitry requires a nominal amount of time to stabilize, and the BGST bit (RCON<13>) indicates when the voltage reference has stabilized.

In some devices, the LVD threshold voltage may be applied externally on the LVDIN pin.

The LVD module is enabled by setting the LVDEN bit (RCON<12>).

### 17.6 Power-Saving Modes

There are two power-saving states that can be entered through the execution of a special instruction, PWRSAV; these are Sleep and Idle.

The format of the PWRSAV instruction is as follows:

#### 17.6.1 SLEEP MODE

In Sleep mode, the clock to the CPU and peripherals is shut down. If an on-chip oscillator is being used, it is shut down

The Fail-Safe Clock Monitor is not functional during Sleep since there is no clock to monitor. However, LPRC clock remains active if WDT is operational during Sleep.

The brown-out protection circuit and the Low-Voltage Detect circuit, if enabled, will remain functional during Sleep.

The processor wakes up from Sleep if at least one of the following conditions has occurred:

- any interrupt that is individually enabled and meets the required priority level

- any Reset (POR, BOR and MCLR)

- WDT time-out

On waking up from Sleep mode, the processor will restart the same clock that was active prior to entry into Sleep mode. When clock switching is enabled, bits COSC<2:0> will determine the oscillator source that will be used on wake-up. If clock switch is disabled, then there is only one system clock.

**Note:** If a POR or BOR occurred, the selection of the oscillator is based on the FOS<2:0> and FPR<4:0> Configuration bits.

If the clock source is an oscillator, the clock to the device will be held off until OST times out (indicating a stable oscillator). If PLL is used, the system clock is held off until LOCK = 1 (indicating that the PLL is stable). In either case, TPOR, TLOCK and TPWRT delays are applied.

If EC, FRC, LPRC or ERC oscillators are used, then a delay of TPOR ( $\sim 10~\mu s$ ) is applied. This is the smallest delay possible on wake-up from Sleep.

Moreover, if LP oscillator was active during Sleep and LP is the oscillator used on wake-up, then the start-up delay will be equal to TPOR. PWRT delay and OST timer delay are not applied. In order to have the smallest possible start-up delay when waking up from Sleep, one of these faster wake-up options should be selected before entering Sleep.

TABLE 18-2: INSTRUCTION SET OVERVIEW

| Base<br>Instr<br># | Assembly<br>Mnemonic |       | Assembly Syntax | Description                              | # of<br>Words | # of<br>Cycle<br>s | Status Flags<br>Affected |

|--------------------|----------------------|-------|-----------------|------------------------------------------|---------------|--------------------|--------------------------|

| 1                  | ADD                  | ADD   | Acc             | Add Accumulators                         | 1             | 1                  | OA,OB,SA,SB              |

|                    |                      | ADD   | f               | f = f + WREG                             | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADD   | f,WREG          | WREG = f + WREG                          | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADD   | #lit10,Wn       | Wd = lit10 + Wd                          | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wb,Ws,Wd        | Wd = Wb + Ws                             | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wb,#lit5,Wd     | Wd = Wb + lit5                           | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wso,#Slit4,Acc  | 16-bit Signed Add to Accumulator         | 1             | 1                  | OA,OB,SA,SB              |

| 2                  | ADDC                 | ADDC  | f               | f = f + WREG + (C)                       | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADDC  | f,WREG          | WREG = f + WREG + (C)                    | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADDC  | #lit10,Wn       | Wd = lit10 + Wd + (C)                    | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADDC  | Wb,Ws,Wd        | Wd = Wb + Ws + (C)                       | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADDC  | Wb,#lit5,Wd     | Wd = Wb + lit5 + (C)                     | 1             | 1                  | C,DC,N,OV,Z              |

| 3                  | AND                  | AND   | f               | f = f .AND. WREG                         | 1             | 1                  | N,Z                      |

|                    |                      | AND   | f,WREG          | WREG = f .AND. WREG                      | 1             | 1                  | N,Z                      |

|                    |                      | AND   | #lit10,Wn       | Wd = lit10 .AND. Wd                      | 1             | 1                  | N,Z                      |

|                    |                      | AND   | Wb,Ws,Wd        | Wd = Wb .AND. Ws                         | 1             | 1                  | N,Z                      |

|                    |                      | AND   | Wb,#lit5,Wd     | Wd = Wb .AND. lit5                       | 1             | 1                  | N,Z                      |

| 4                  | ASR                  | ASR   | f               | f = Arithmetic Right Shift f             | 1             | 1                  | C,N,OV,Z                 |

|                    |                      | ASR   | f,WREG          | WREG = Arithmetic Right Shift f          | 1             | 1                  | C,N,OV,Z                 |

|                    |                      | ASR   | Ws,Wd           | Wd = Arithmetic Right Shift Ws           | 1             | 1                  | C,N,OV,Z                 |

|                    |                      | ASR   | Wb, Wns, Wnd    | Wnd = Arithmetic Right Shift Wb by Wns   | 1             | 1                  | N,Z                      |

|                    |                      | ASR   | Wb,#lit5,Wnd    | Wnd = Arithmetic Right Shift Wb by lit5  | 1             | 1                  | N,Z                      |

| 5                  | BCLR                 | BCLR  | f,#bit4         | Bit Clear f                              | 1             | 1                  | None                     |

|                    |                      | BCLR  | Ws,#bit4        | Bit Clear Ws                             | 1             | 1                  | None                     |

| 6                  | BRA                  | BRA   | C,Expr          | Branch if Carry                          | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | GE,Expr         | Branch if greater than or equal          | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | GEU, Expr       | Branch if unsigned greater than or equal | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | GT,Expr         | Branch if greater than                   | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | GTU, Expr       | Branch if unsigned greater than          | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | LE,Expr         | Branch if less than or equal             | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | LEU, Expr       | Branch if unsigned less than or equal    | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | LT,Expr         | Branch if less than                      | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | LTU, Expr       | Branch if unsigned less than             | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | N,Expr          | Branch if Negative                       | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | NC,Expr         | Branch if Not Carry                      | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | NN,Expr         | Branch if Not Negative                   | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | NOV,Expr        | Branch if Not Overflow                   | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | NZ,Expr         | Branch if Not Zero                       | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | OA,Expr         | Branch if Accumulator A overflow         | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | OB,Expr         | Branch if Accumulator B overflow         | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | OV,Expr         | Branch if Overflow                       | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | SA,Expr         | Branch if Accumulator A saturated        | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | SB,Expr         | Branch if Accumulator B saturated        | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | Expr            | Branch Unconditionally                   | 1             | 2                  | None                     |

|                    |                      | BRA   | Z,Expr          | Branch if Zero                           | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | Wn              | Computed Branch                          | 1             | 2                  | None                     |

| 7                  | BSET                 | BSET  | f,#bit4         | Bit Set f                                | 1             | 1                  | None                     |

|                    |                      | BSET  | Ws,#bit4        | Bit Set Ws                               | 1             | 1                  | None                     |

| 8                  | BSW                  | BSW.C | Ws,Wb           | Write C bit to Ws <wb></wb>              | 1             | 1                  | None                     |

|                    |                      | BSW.Z | Ws,Wb           | Write Z bit to Ws <wb></wb>              | 1             | 1                  | None                     |

TABLE 18-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax | Description                           | # of<br>Words | # of<br>Cycle<br>s | Status Flags<br>Affected |

|--------------------|----------------------|--------|-----------------|---------------------------------------|---------------|--------------------|--------------------------|

| 66                 | RRNC                 | RRNC   | f               | f = Rotate Right (No Carry) f         | 1             | 1                  | N,Z                      |

|                    |                      | RRNC   | f,WREG          | WREG = Rotate Right (No Carry) f      | 1             | 1                  | N,Z                      |

|                    |                      | RRNC   | Ws,Wd           | Wd = Rotate Right (No Carry) Ws       | 1             | 1                  | N,Z                      |

| 67                 | SAC                  | SAC    | Acc,#Slit4,Wdo  | Store Accumulator                     | 1             | 1                  | None                     |

|                    |                      | SAC.R  | Acc,#Slit4,Wdo  | Store Rounded Accumulator             | 1             | 1                  | None                     |

| 68                 | SE                   | SE     | Ws,Wnd          | Wnd = sign-extended Ws                | 1             | 1                  | C,N,Z                    |

| 69                 | SETM                 | SETM   | f               | f = 0xFFFF                            | 1             | 1                  | None                     |

|                    |                      | SETM   | WREG            | WREG = 0xFFFF                         | 1             | 1                  | None                     |

|                    |                      | SETM   | Ws              | Ws = 0xFFFF                           | 1             | 1                  | None                     |

| 70                 | SFTAC                | SFTAC  | Acc, Wn         | Arithmetic Shift Accumulator by (Wn)  | 1             | 1                  | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | SFTAC  | Acc,#Slit6      | Arithmetic Shift Accumulator by Slit6 | 1             | 1                  | OA,OB,OAB,<br>SA,SB,SAB  |

| 71                 | SL                   | SL     | f               | f = Left Shift f                      | 1             | 1                  | C,N,OV,Z                 |

|                    |                      | SL     | f,WREG          | WREG = Left Shift f                   | 1             | 1                  | C,N,OV,Z                 |

|                    |                      | SL     | Ws,Wd           | Wd = Left Shift Ws                    | 1             | 1                  | C,N,OV,Z                 |

|                    |                      | SL     | Wb,Wns,Wnd      | Wnd = Left Shift Wb by Wns            | 1             | 1                  | N,Z                      |

|                    |                      | SL     | Wb,#lit5,Wnd    | Wnd = Left Shift Wb by lit5           | 1             | 1                  | N,Z                      |

| 72                 | SUB                  | SUB    | Acc             | Subtract Accumulators                 | 1             | 1                  | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | SUB    | f               | f = f - WREG                          | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | SUB    | f,WREG          | WREG = f - WREG                       | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | SUB    | #lit10,Wn       | Wn = Wn - lit10                       | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | SUB    | Wb,Ws,Wd        | Wd = Wb - Ws                          | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | SUB    | Wb,#lit5,Wd     | Wd = Wb - lit5                        | 1             | 1                  | C,DC,N,OV,Z              |

| 73                 | SUBB                 | SUBB   | f               | $f = f - WREG - (\overline{C})$       | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | SUBB   | f,WREG          | WREG = $f$ - WREG - $(\overline{C})$  | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | SUBB   | #lit10,Wn       | $Wn = Wn - lit10 - (\overline{C})$    | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | SUBB   | Wb,Ws,Wd        | $Wd = Wb - Ws - (\overline{C})$       | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | SUBB   | Wb,#lit5,Wd     | $Wd = Wb - lit5 - (\overline{C})$     | 1             | 1                  | C,DC,N,OV,Z              |

| 74                 | SUBR                 | SUBR   | f               | f = WREG - f                          | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | SUBR   | f,WREG          | WREG = WREG - f                       | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | SUBR   | Wb,Ws,Wd        | Wd = Ws - Wb                          | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | SUBR   | Wb,#lit5,Wd     | Wd = lit5 - Wb                        | 1             | 1                  | C,DC,N,OV,Z              |

| 75                 | SUBBR                | SUBBR  | f               | $f = WREG - f - (\overline{C})$       | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | SUBBR  | f,WREG          | WREG = WREG -f - $\overline{(C)}$     | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | SUBBR  | Wb,Ws,Wd        | $Wd = Ws - Wb - (\overline{C})$       | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | SUBBR  | Wb,#lit5,Wd     | $Wd = lit5 - Wb - (\overline{C})$     | 1             | 1                  | C,DC,N,OV,Z              |

| 76                 | SWAP                 | SWAP.b | Wn              | Wn = nibble swap Wn                   | 1             | 1                  | None                     |

|                    |                      | SWAP   | Wn              | Wn = byte swap Wn                     | 1             | 1                  | None                     |

| 77                 | TBLRDH               | TBLRDH | Ws,Wd           | Read Prog<23:16> to Wd<7:0>           | 1             | 2                  | None                     |

| 78                 | TBLRDL               | TBLRDL | Ws,Wd           | Read Prog<15:0> to Wd                 | 1             | 2                  | None                     |

| 79                 | TBLWTH               | TBLWTH | Ws,Wd           | Write Ws<7:0> to Prog<23:16>          | 1             | 2                  | None                     |

| 80                 | TBLWTL               | TBLWTL | Ws,Wd           | Write Ws to Prog<15:0>                | 1             | 2                  | None                     |

| 81                 | ULNK                 | ULNK   |                 | Unlink frame pointer                  | 1             | 1                  | None                     |

| 82                 | XOR                  | XOR    | f               | f = f .XOR. WREG                      | 1             | 1                  | N,Z                      |

|                    |                      | XOR    | f,WREG          | WREG = f .XOR. WREG                   | 1             | 1                  | N,Z                      |

|                    |                      | XOR    | #lit10,Wn       | Wd = lit10 .XOR. Wd                   | 1             | 1                  | N,Z                      |

|                    |                      | XOR    | Wb,Ws,Wd        | Wd = Wb .XOR. Ws                      | 1             | 1                  | N,Z                      |

|                    |                      | XOR    | Wb,#lit5,Wd     | Wd = Wb .XOR. lit5                    | 1             | 1                  | N,Z                      |

| 83                 | ZE                   | ZE     | Ws,Wnd          | Wnd = Zero-extend Ws                  | 1             | 1                  | C,Z,N                    |

### 20.1 DC Characteristics

TABLE 20-1: OPERATING MIPS VS. VOLTAGE

| Von Benge | Town Bongs     | Max MIPS        |                 |  |  |  |  |

|-----------|----------------|-----------------|-----------------|--|--|--|--|

| VDD Range | Temp Range     | dsPIC30FXXX-30I | dsPIC30FXXX-20E |  |  |  |  |

| 4.5-5.5V  | -40°C to 85°C  | 30              | _               |  |  |  |  |

| 4.5-5.5V  | -40°C to 125°C | _               | 20              |  |  |  |  |

| 3.0-3.6V  | -40°C to 85°C  | 20              | _               |  |  |  |  |

| 3.0-3.6V  | -40°C to 125°C | _               | 15              |  |  |  |  |

| 2.5-3.0V  | -40°C to 85°C  | 10              | _               |  |  |  |  |

### **TABLE 20-2: THERMAL OPERATING CONDITIONS**

| Rating                                                                                                                                                                                                                                             | Symbol | Min         | Тур           | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------|---------------|------|------|

| dsPIC30F201x-30I<br>dsPIC30F301x-30I                                                                                                                                                                                                               |        |             |               |      |      |

| Operating Junction Temperature Range                                                                                                                                                                                                               | TJ     | -40         | _             | +125 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                                                                                | TA     | -40         | _             | +85  | °C   |

| dsPIC30F201x-20E<br>dsPIC30F301x-20E                                                                                                                                                                                                               |        |             |               |      |      |

| Operating Junction Temperature Range                                                                                                                                                                                                               | TJ     | -40         | _             | +150 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                                                                                | TA     | -40         | _             | +125 | °C   |

| Power Dissipation: Internal chip power dissipation: $P_{INT} = V_{DD} \times (I_{DD} - \Sigma I_{OH})$ I/O Pin power dissipation: $P_{I/O} = \Sigma \left( \{V_{DD} - V_{OH}\} \times I_{OH} \right) + \Sigma \left( V_{OL} \times I_{OL} \right)$ | PD     | PINT + PI/O |               |      | W    |

| Maximum Allowed Power Dissipation                                                                                                                                                                                                                  | PDMAX  | (7          | ΓJ - TA) / θ. | JA   | W    |

### **TABLE 20-3: THERMAL PACKAGING CHARACTERISTICS**

| Characteristic                                | Symbol | Тур | Max | Unit | Notes |

|-----------------------------------------------|--------|-----|-----|------|-------|

| Package Thermal Resistance, 18-pin PDIP (P)   | θЈА    | 44  | _   | °C/W | 1     |

| Package Thermal Resistance, 18-pin SOIC (SO)  | θЈА    | 57  | _   | °C/W | 1     |

| Package Thermal Resistance, 28-pin SPDIP (SP) | θЈА    | 42  | _   | °C/W | 1     |

| Package Thermal Resistance, 28-pin (SOIC)     | θЈА    | 49  | _   | °C/W | 1     |

| Package Thermal Resistance, 44-pin QFN        | θЈА    | 28  | _   | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-ja (θJA) numbers are achieved by package simulations.

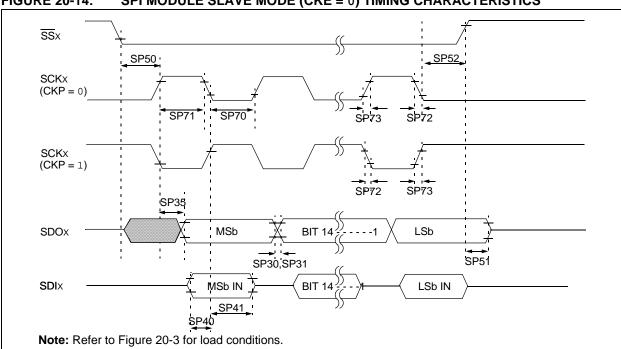

FIGURE 20-14: SPI MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

TABLE 20-31: SPI MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHAP      | RACTERISTIC           | es                                                | Standard Operating Conditions: 2.5V to 5.5V (unless otherwise stated) Operating temperature -40°C ≤TA ≤+85°C for Industrial -40°C ≤TA ≤+125°C for Extended |                    |     |       |            |  |  |

|--------------|-----------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|------------|--|--|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                     | Min                                                                                                                                                        | Typ <sup>(2)</sup> | Max | Units | Conditions |  |  |

| SP70         | TscL                  | SCKx Input Low Time                               | 30                                                                                                                                                         | _                  | _   | ns    | _          |  |  |

| SP71         | TscH                  | SCKx Input High Time                              | 30                                                                                                                                                         | _                  | _   | ns    | _          |  |  |

| SP72         | TscF                  | SCKx Input Fall Time <sup>(3)</sup>               |                                                                                                                                                            | 10                 | 25  | ns    | _          |  |  |

| SP73         | TscR                  | SCKx Input Rise Time <sup>(3)</sup>               |                                                                                                                                                            | 10                 | 25  | ns    | _          |  |  |

| SP30         | TdoF                  | SDOx Data Output Fall Time(3)                     | _                                                                                                                                                          | _                  | _   | ns    | See DO32   |  |  |

| SP31         | TdoR                  | SDOx Data Output Rise Time(3)                     |                                                                                                                                                            | _                  | _   | ns    | See DO31   |  |  |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after SCKx Edge            |                                                                                                                                                            | _                  | 30  | ns    | _          |  |  |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge        | 20                                                                                                                                                         | _                  | _   | ns    | _          |  |  |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge         | 20                                                                                                                                                         | _                  | _   | ns    | _          |  |  |

| SP50         | TssL2scH,<br>TssL2scL | SSx↓to SCKx↑ or SCKx↓Input                        | 120                                                                                                                                                        | _                  | _   | ns    | _          |  |  |

| SP51         | TssH2doZ              | SSx↑ to SDOx Output high impedance <sup>(3)</sup> | 10                                                                                                                                                         | _                  | 50  | ns    | _          |  |  |

| SP52         | TscH2ssH<br>TscL2ssH  | SSx after SCK Edge                                | 1.5 TcY<br>+40                                                                                                                                             | _                  | _   | ns    | _          |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

**<sup>2:</sup>** Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

<sup>3:</sup> Assumes 50 pF load on all SPI pins.

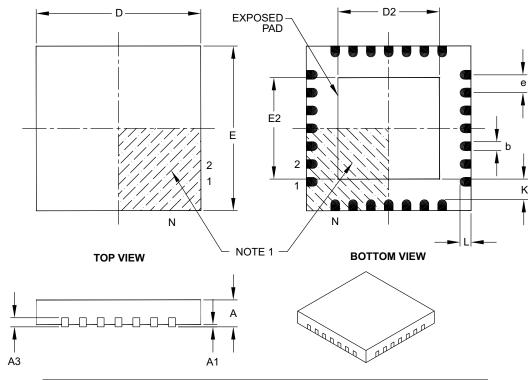

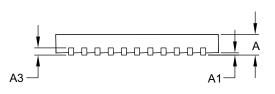

# 28-Lead Plastic Quad Flat, No Lead Package (MM) – 6x6x0.9 mm Body [QFN-S] with 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units    |          | MILLIMETERS | 3    |  |

|------------------------|----------|----------|-------------|------|--|

| Dimensio               | n Limits | MIN      | NOM         | MAX  |  |

| Number of Pins         | N        |          | 28          |      |  |

| Pitch                  | е        |          | 0.65 BSC    |      |  |

| Overall Height         | Α        | 0.80     | 0.90        | 1.00 |  |

| Standoff               | A1       | 0.00     | 0.02        | 0.05 |  |

| Contact Thickness      | A3       | 0.20 REF |             |      |  |

| Overall Width          | Е        |          | 6.00 BSC    |      |  |

| Exposed Pad Width      | E2       | 3.65     | 3.70        | 4.70 |  |

| Overall Length         | D        |          | 6.00 BSC    |      |  |

| Exposed Pad Length     | D2       | 3.65     | 3.70        | 4.70 |  |

| Contact Width          | b        | 0.23     | 0.38        | 0.43 |  |

| Contact Length         | L        | 0.30     | 0.40        | 0.50 |  |

| Contact-to-Exposed Pad | K        | 0.20     | _           | _    |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-124B

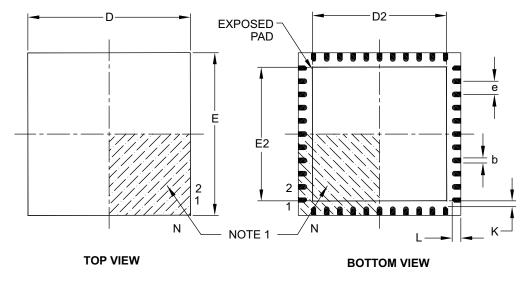

### 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            | MILLIMETERS |          |      |

|------------------------|------------------|-------------|----------|------|

|                        | Dimension Limits | MIN         | NOM      | MAX  |

| Number of Pins         | N                |             | 44       |      |

| Pitch                  | е                | 0.65 BSC    |          |      |

| Overall Height         | А                | 0.80        | 0.90     | 1.00 |

| Standoff               | A1               | 0.00        | 0.02     | 0.05 |

| Contact Thickness      | A3               |             | 0.20 REF |      |

| Overall Width          | E                |             | 8.00 BSC |      |

| Exposed Pad Width      | E2               | 6.30        | 6.45     | 6.80 |

| Overall Length         | D                | 8.00 BSC    |          |      |

| Exposed Pad Length     | D2               | 6.30        | 6.45     | 6.80 |

| Contact Width          | b                | 0.25        | 0.30     | 0.38 |

| Contact Length         | L                | 0.30        | 0.40     | 0.50 |

| Contact-to-Exposed Pad | K                | 0.20        | -        | -    |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-103B

| Interrupt Controller                                  | PLL Clock Timing Specifications                     | 162  |

|-------------------------------------------------------|-----------------------------------------------------|------|

| Register Map71, 72                                    | POR. See Power-on Reset.                            |      |

| Interrupt Priority66                                  | Port Write/Read Example                             | 60   |

| Traps67                                               | PORTB                                               |      |

| Interrupt Sequence                                    | Register Map for dsPIC30F2011/3012                  |      |

| Interrupt Stack Frame69                               | Register Map for dsPIC30F2012/3013                  | 61   |

| Interrupts65                                          | PORTC                                               |      |

| L                                                     | Register Map for dsPIC30F2011/2012/3012/3013        | 3 61 |

|                                                       | PORTD                                               |      |

| Load Conditions                                       | Register Map for dsPIC30F2011/3012                  |      |

| Low Voltage Detect (LVD)                              | Register Map for dsPIC30F2012/3013                  | 62   |

| Low-Voltage Detect Characteristics                    | PORTF                                               |      |

| LVDL Characteristics                                  | Register Map for dsPIC30F2012/3013                  |      |

| M                                                     | Power Saving Modes                                  |      |

| Memory Organization                                   | Idle                                                |      |

| Core Register Map                                     | Sleep                                               |      |

| Microchip Internet Web Site                           | Sleep and Idle                                      |      |

| Modulo Addressing                                     | Power-Down Current (IPD)Power-up Timer              | 154  |

| Applicability                                         | Timing Characteristics                              | 166  |

| Incrementing Buffer Operation Example45               | •                                                   |      |

| Start and End Address                                 | Timing Requirements Program Address Space           |      |

| W Address Register Selection45                        | Construction                                        |      |

| MPLAB ASM30 Assembler, Linker, Librarian              | Data Access from Program Memory Using               | 3    |

| MPLAB Integrated Development Environment Software 145 | Program Space Visibility                            | 3:   |

| MPLAB PM3 Device Programmer148                        | Data Access From Program Memory Using               | 50   |

| MPLAB REAL ICE In-Circuit Emulator System147          | Table Instructions                                  | 30   |

| MPLINK Object Linker/MPLIB Object Librarian146        | Data Access from, Address Generation                |      |

| ,                                                     | Data Space Window into Operation                    |      |

| N                                                     | Data Table Access (LS Word)                         |      |

| NVM                                                   | Data Table Access (MS Byte)                         |      |

| Register Map53                                        | Memory Maps                                         |      |

| 0                                                     | Table Instructions                                  |      |

| 0                                                     | TBLRDH                                              | 32   |

| OC/PWM Module Timing Characteristics171               | TBLRDL                                              |      |

| Operating Current (IDD)152                            | TBLWTH                                              |      |

| Operating Frequency vs Voltage                        | TBLWTL                                              | 32   |

| dsPIC30FXXXX-20 (Extended)                            | Program and EEPROM Characteristics                  | 159  |

| Oscillator                                            | Program Counter                                     |      |

| Configurations                                        | Programmable                                        |      |

| Fail-Safe Clock Monitor                               | Programmer's Model                                  | 20   |

| Fast RC (FRC)                                         | Diagram                                             | 21   |

| Initial Clock Source Selection                        | Programming Operations                              | 51   |

| Low-Power RC (LPRC)                                   | Algorithm for Program Flash                         |      |

| LP Oscillator Control                                 | Erasing a Row of Program Memory                     | 51   |

| Phase Locked Loop (PLL)                               | Initiating the Programming Sequence                 | 52   |

| • • • •                                               | Loading Write Latches                               |      |

| Operating Modes (Table)                               | Protection Against Accidental Writes to OSCCON      | 128  |

| Oscillator Selection                                  | R                                                   |      |

| Oscillator Start-up Timer                             |                                                     |      |

| Timing Characteristics165                             | Reader Response                                     |      |

| Timing Requirements                                   | Reset                                               |      |

| Output Compare Interrupts                             | BOR, Programmable                                   |      |

| Output Compare Module                                 | Brown-out Reset (BOR)                               |      |

| Register Map91                                        | Oscillator Start-up Timer (OST)                     | 123  |

| Timing Characteristics170                             | POR                                                 | 404  |

| Timing Requirements170                                | Operating without FSCM and PWRT                     |      |

| Output Compare Operation During CPU Idle Mode 90      | With Long Crystal Start-up TimePOR (Power-on Reset) |      |

| Output Compare Sleep Mode Operation90                 |                                                     |      |

|                                                       | Power-on Reset (POR)<br>Power-up Timer (PWRT)       |      |

| P                                                     | Reset Sequence                                      |      |

| Packaging Information187                              | Reset Sources                                       |      |

| Marking 187, 188                                      | Reset Sources                                       | 07   |

| Peripheral Module Disable (PMD) Registers 135         | Brown-out Reset (BOR)                               | 67   |

| Pinout Descriptions                                   | Illegal Instruction Trap                            |      |

| Trap Lockout67                                                   | Register Map                               | 75  |

|------------------------------------------------------------------|--------------------------------------------|-----|

| Uninitialized W Register Trap67                                  | Timer2 and Timer3 Selection Mode           |     |

| Watchdog Time-out                                                | Timer2/3 Module                            |     |

| Reset Timing Characteristics                                     | 16-bit Timer Mode                          | 77  |

| Reset Timing Granacteristics                                     | 32-bit Synchronous Counter Mode            |     |

| Run-Time Self-Programming (RTSP)                                 | 32-bit Timer Mode                          |     |

| Kull-Tillie Sell-Flogramming (KTSF)49                            | ADC Event Trigger                          |     |

| \$                                                               |                                            |     |

| Simple Capture Event Mode83                                      | Gate Operation                             |     |

| ·                                                                | Interrupt                                  |     |

| Buffer Operation84                                               | Operation During Sleep Mode                |     |

| Hall Sensor Mode84                                               | Register Map                               |     |

| Prescaler                                                        | Timer Prescaler                            | 80  |

| Timer2 and Timer3 Selection Mode                                 | Timing Characteristics                     |     |

| Simple OC/PWM Mode Timing Requirements171                        | A/D Conversion                             |     |

| Simple Output Compare Match Mode                                 | Low-speed (ASAM = 0, SSRC = 000)           |     |

| Simple PWM Mode                                                  | Bandgap Start-up Time                      |     |

| Input Pin Fault Protection88                                     | CAN Module I/O                             |     |

| Period89                                                         | CLKOUT and I/O                             | 164 |

| Software Simulator (MPLAB SIM)147                                | External Clock                             | 160 |

| Software Stack Pointer, Frame Pointer20                          | I <sup>2</sup> C Bus Data                  |     |

| CALL Stack Frame39                                               | Master Mode                                | 177 |

| SPI Module93                                                     | Slave Mode                                 | 179 |

| Framed SPI Support94                                             | I <sup>2</sup> C Bus Start/Stop Bits       |     |

| Operating Function Description93                                 | Master Mode                                | 177 |

| Operation During CPU Idle Mode95                                 | Slave Mode                                 | 179 |

| Operation During CPU Sleep Mode95                                | Input Capture (CAPX)                       | 169 |

| SDOx Disable94                                                   | OC/PWM Module                              |     |

| Slave Select Synchronization95                                   | Oscillator Start-up Timer                  |     |

| SPI1 Register Map96                                              | Output Compare Module                      |     |

| Timing Characteristics                                           | Power-up Timer                             |     |

| Master Mode (CKE = 0) 172                                        | Reset                                      |     |

| Master Mode (CKE = 1) 173                                        | SPI Module                                 |     |

| Slave Mode (CKE = 1) 174, 175                                    | Master Mode (CKE = 0)                      | 172 |

| Timing Requirements                                              | Master Mode (CKE = 1)                      |     |

| Master Mode (CKE = 0)172                                         | Slave Mode (CKE = 0)                       |     |

| Master Mode (CKE = 1)                                            | Slave Mode (CKE = 1)                       |     |

| Slave Mode (CKE = 0)                                             | Type A, B and C Timer External Clock       |     |

| Slave Mode (CKE = 1)                                             | Watchdog Timer                             |     |

| Word and Byte Communication94                                    | Timing Diagrams                            | 100 |

| Status Bits, Their Significance and the Initialization Condition | o o                                        | 00  |

| for                                                              | PWM Output Timing                          | 89  |

|                                                                  | Time-out Sequence on Power-up              | 400 |

| RCON Register, Case 1                                            | (MCLR Not Tied to VDD), Case 1             | 130 |

| Status Bits, Their Significance and the Initialization Condition | Time-out Sequence on Power-up              |     |

| for RCON Register, Case 2                                        | (MCLR                                      |     |

| Status Register                                                  | Not Tied to VDD), Case 2                   | 130 |

| Symbols Used in Opcode Descriptions                              | Time-out Sequence on Power-up              |     |

| System Integration                                               | (MCLR                                      |     |

| Register Map136                                                  | Tied to VDD)                               | 130 |

| Т                                                                | Timing Diagrams and Specifications         |     |

|                                                                  | DC Characteristics - Internal RC Accuracy  | 163 |

| Table Instruction Operation Summary49                            | Timing Diagrams.See Timing Characteristics |     |

| Temperature and Voltage Specifications                           | Timing Requirements                        |     |

| AC160                                                            | A/D Conversion                             |     |

| DC150                                                            | Low-speed                                  | 185 |

| Timer 2/3 Module77                                               | Bandgap Start-up Time                      | 166 |