Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| D-4-11-                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Details                    |                                                                               |

| Product Status             | Active                                                                        |

| Core Processor             | dsPIC                                                                         |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 20 MIPS                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 20                                                                            |

| Program Memory Size        | 24KB (8K x 24)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 1K x 8                                                                        |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 10x12b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 44-QFN (8x8)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f3013-20i-ml |

Y Data Bus X Data Bus 16 /16 16 Data Latch Data Latch Interrupt PSV & Table

Data Access

24 Control Block Controller Y Data X Data 116 RAM (512 bytes RAM (512 bytes) Address Address 24 Latch Latch 16 1/16 16 EMUD3/AN0/VREF+/CN2/RB0 24 X RAGU EMUC3/AN1/VREF-/CN3/RB1 Y AGU PCU PCH PCL X WAGU AN2/SS1/LVDIN/CN4/RB2 Program Counter AN3/CN5/RB3 Loop Control Logic PGD/EMUD/AN4/U1TX/SDO1/SCL/CN6/RB4 Address Latch PGC/EMUC/AN5/U1RX/SDI1/SDA/CN7/RB5 AN6/SCK1/INT0/OCFA/RB6 Program Memory (12 Kbytes) EMUD2/AN7/OC2/IC2/INT2/RB7 Data Latch Effective Address PORTB 16 ROM Latch 6 IR EMUD1/SOSCI/T2CK/U1ATX/CN1/RC13 EMUC1/SOSCO/T1CK/U1ARX/CN0/RC14 16 16 OSC2/CLKO/RC15 16 x 16 W Reg Array Decode PORTC Instruction 16/16 Decode & Control DSP Divide Power-up Engine Unit EMUC2/OC1/IC1/INT1/RD0 Timing Generation Oscillator OSC1/CLKI Start-up Timer  $\boxtimes$ ALU<16> POR/BOR Reset 16 16 PORTD Watchdog Timer  $\boxtimes$ Low-Voltag Detect VDD, VSSAVDD, AVSS Input Output 12-bit ADC Capture Compare  $\mathsf{I}^2\mathsf{C}^{\scriptscriptstyle\mathsf{TM}}$ Module Module SPI1 Timers UART1

FIGURE 1-1: dsPIC30F2011 BLOCK DIAGRAM

The SA and SB bits are modified each time data passes through the adder/subtracter but can only be cleared by the user. When set, they indicate that the accumulator has overflowed its maximum range (bit 31 for 32-bit saturation or bit 39 for 40-bit saturation) and will be saturated if saturation is enabled. When saturation is not enabled, SA and SB default to bit 39 overflow and thus indicate that a catastrophic overflow has occurred. If the COVTE bit in the INTCON1 register is set, SA and SB bits generate an arithmetic warning trap when saturation is disabled.

The overflow and saturation Status bits can optionally be viewed in the STATUS register (SR) as the logical OR of OA and OB (in bit OAB) and the logical OR of SA and SB (in bit SAB). This allows programmers to check one bit in the STATUS register to determine if either accumulator has overflowed, or one bit to determine if either accumulator has saturated. This would be useful for complex number arithmetic which typically uses both the accumulators.

The device supports three saturation and overflow modes:

- 1. Bit 39 Overflow and Saturation:

- When bit 39 overflow and saturation occurs, the saturation logic loads the maximally positive 9.31 (0x7FFFFFFFFF) or maximally negative 9.31 value (0x8000000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user. This is referred to as 'super saturation' and provides protection against erroneous data or unexpected algorithm problems (e.g., gain calculations).

- 2. Bit 31 Overflow and Saturation:

When bit 31 overflow and saturation occurs, the saturation logic then loads the maximally positive 1.31 value (0x007FFFFFFF) or maximally negative 1.31 value (0x0080000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user. When this Saturation mode is in effect, the guard bits are not used, so the OA, OB or OAB bits are never set.

3. Bit 39 Catastrophic Overflow:

The bit 39 overflow Status bit from the adder is used to set the SA or SB bit which remains set until cleared by the user. No saturation operation is performed and the accumulator is allowed to overflow (destroying its sign). If the COVTE bit in the INTCON1 register is set, a catastrophic overflow can initiate a trap exception.

#### 2.4.2.2 Accumulator 'Write-Back'

The MAC class of instructions (with the exception of MPY, MPY.N, ED and EDAC) can optionally write a rounded version of the high word (bits 31 through 16) of the accumulator that is not targeted by the instruction into data space memory. The write is performed across the X bus into combined X and Y address space. The following addressing modes are supported:

- 1. W13, Register Direct:

- The rounded contents of the non-target accumulator are written into W13 as a 1.15 fraction.

- [W13]+ = 2, Register Indirect with Post-Increment:

The rounded contents of the non-target accumulator are written into the address pointed to by W13 as a 1.15 fraction. W13 is then incremented by 2 (for a word write).

#### 2.4.2.3 Round Logic

The round logic is a combinational block which performs a conventional (biased) or convergent (unbiased) round function during an accumulator write (store). The Round mode is determined by the state of the RND bit in the CORCON register. It generates a 16-bit, 1.15 data value, which is passed to the data space write saturation logic. If rounding is not indicated by the instruction, a truncated 1.15 data value is stored and the least significant word (lsw) is simply discarded.

Conventional rounding takes bit 15 of the accumulator, zero-extends it and adds it to the ACCxH word (bits 16 through 31 of the accumulator). If the ACCxL word (bits 0 through 15 of the accumulator) is between 0x8000 and 0xFFFF (0x8000 included), ACCxH is incremented. If ACCxL is between 0x0000 and 0x7FFF, ACCxH is left unchanged. A consequence of this algorithm is that over a succession of random rounding operations, the value tends to be biased slightly positive.

Convergent (or unbiased) rounding operates in the same manner as conventional rounding, except when ACCxL equals 0x8000. If this is the case, the LSb (bit 16 of the accumulator) of ACCxH is examined. If it is '1', ACCxH is incremented. If it is '0', ACCxH is not modified. Assuming that bit 16 is effectively random in nature, this scheme will remove any rounding bias that may accumulate.

The SAC and SAC.R instructions store either a truncated (SAC) or rounded (SAC.R) version of the contents of the target accumulator to data memory via the X bus (subject to data saturation, see Section 2.4.2.4 "Data Space Write Saturation"). Note that for the MAC class of instructions, the accumulator write-back operation functions in the same manner, addressing combined MCU (X and Y) data space though the X bus. For this class of instructions, the data is always subject to rounding.

#### 3.0 MEMORY ORGANIZATION

Note:

This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

#### 3.1 Program Address Space

The program address space is 4M instruction words. The program space memory maps for the dsPIC30F2011/2012/3012/3013 devices is shown in Figure 3-1.

Program memory is addressable by a 24-bit value from either the 23-bit PC, table instruction Effective Address (EA), or data space EA, when program space is mapped into data space as defined by Table 3-1. Note that the program space address is incremented by two between successive program words in order to provide compatibility with data space addressing.

User program space access is restricted to the lower 4M instruction word address range (0x000000 to 0x7FFFFE) for all accesses other than TBLRD/TBLWT, which uses TBLPAG<7> to determine user or configuration space access. In Table 3-1, Program Space Address Construction, bit 23 allows access to the Device ID, the User ID and the Configuration bits. Otherwise, bit 23 is always clear.

# 4.1.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note:

For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (register offset) field is shared between both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- · Register Direct

- · Register Indirect

- · Register Indirect Post-modified

- · Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- · Register Indirect with Literal Offset

- 8-bit Literal

- 16-bit Literal

Note:

Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.1.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY.N, MOVSAC and MSC), also referred to as MAC instructions, utilize a simplified set of addressing modes to allow the user to effectively manipulate the data pointers through register indirect tables.

The two source operand prefetch registers must belong to the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU. W10 and W11 are always directed to the Y AGU. The effective addresses generated (before and after modification) must, therefore, be valid addresses within X data space for W8 and W9 and Y data space for W10 and W11.

Note:

Register Indirect with Register Offset addressing is only available for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the MAC class of instructions:

- · Register Indirect

- · Register Indirect Post-modified by 2

- · Register Indirect Post-modified by 4

- Register Indirect Post-modified by 6

- Register Indirect with Register Offset (Indexed)

#### 4.1.5 OTHER INSTRUCTIONS

Besides the various addressing modes outlined above, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ADD Acc, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

#### 4.2 Modulo Addressing

Modulo Addressing is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either data or program space (since the data pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into program space) and Y data spaces. Modulo Addressing can operate on any W register pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can only be configured to operate in one direction, as there are certain restrictions on the buffer Start address (for incrementing buffers), or end address (for decrementing buffers) based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-2 length. As these buffers satisfy the Start and the end address criteria, they can operate in a Bidirectional mode (i.e., address boundary checks are performed on both the lower and upper address boundaries).

#### **7.0 I/O PORTS**

Note:

This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

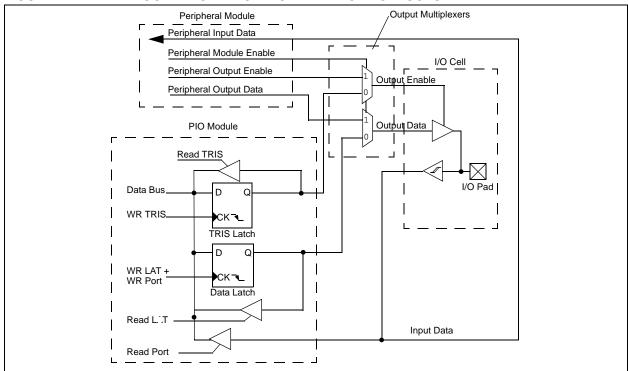

All of the device pins (except VDD, Vss,  $\overline{MCLR}$  and OSC1/CLKI) are shared between the peripherals and the parallel I/O ports.

All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

#### 7.1 Parallel I/O (PIO) Ports

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have three registers directly associated with the operation of the port pin. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx), read the latch.

Writes to the latch, write the latch (LATx). Reads from the port (PORTx), read the port pins and writes to the port pins, write the latch (LATx).

Any bit and its associated data and Control registers that are not valid for a particular device are disabled. That means the corresponding LATx and TRISx registers and the port pin read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

A parallel I/O (PIO) port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pad cell. Figure 7-1 illustrates how ports are shared with other peripherals and the associated I/O cell (pad) to which they are connected.

The format of the registers for the shared ports, (PORTB, PORTC, PORTD and PORTF) are shown in Table 7-1 through Table 7-6.

**Note:** The actual bits in use vary between devices.

FIGURE 7-1: BLOCK DIAGRAM OF A SHARED PORT STRUCTURE

#### TABLE 7-1: PORTB REGISTER MAP FOR dsPIC30F2011/3012

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset State         |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| TRISB       | 02C6  | _      | _      | _      | _      | _      | _      | _     | _     | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 0000 0000 1111 1111 |

| PORTB       | 02C8  | _      | _      | _      | _      | _      | _      | _     | _     | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | 0000 0000 0000 0000 |

| LATB        | 02CB  | _      | _      | _      | _      | _      | _      | _     | _     | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | 0000 0000 0000 0000 |

**Legend:** — = unimplemented bit, read as '0'

#### TABLE 7-2: PORTB REGISTER MAP FOR dsPIC30F2012/3013

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset State         |

|-------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| TRISB       | 02C6  | _      | _      | _      | -      | -      | _      | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 0000 0011 1111 1111 |

| PORTB       | 02C8  | _      | _      |        | -      | -      | _      | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | 0000 0000 0000 0000 |

| LATB        | 02CB  | _      | _      | _      |        |        | _      | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | 0000 0000 0000 0000 |

**Legend:** — = unimplemented bit, read as '0'

#### TABLE 7-3: PORTC REGISTER MAP FOR dsPIC30F2011/2012/3012/3013

| SFR<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset State         |

|-------------|-------|---------|---------|---------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------------|

| TRISC       | 02CC  | TRISC15 | TRISC14 | TRISC13 | _      | _      | _      | _     | _     | _     | _     | _     | _     | _     | _     | -     | _     | 1110 0000 0000 0000 |

| PORTC       | 02CE  | RC15    | RC14    | RC13    | _      | _      | _      | _     | _     | _     | _     | _     | _     | -     | _     | _     | -     | 0000 0000 0000 0000 |

| LATC        | 02D0  | LATC15  | LATC14  | LATC13  | _      | _      | _      | _     | _     | _     | _     | _     | _     | _     | _     | _     | _     | 0000 0000 0000 0000 |

**Legend:** — = unimplemented bit, read as '0'

#### TABLE 7-4: PORTD REGISTER MAP FOR dsPIC30F2011/3012

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Reset State         |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--------|---------------------|

| TRISD       | 02D2  | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     | _     | _     | _     | _     | TRISD0 | 0000 0000 0000 0001 |

| PORTD       | 02D4  |        |        | _      | _      | 1      | _      | 1     | _     | _     | _     | _     | 1     | _     | _     | _     | RD0    | 0000 0000 0000 0000 |

| LATD        | 02D6  | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     | _     | _     | _     | _     | LATD0  | 0000 0000 0000 0000 |

**Legend:** — = unimplemented bit, read as '0'

#### TABLE 7-5: PORTD REGISTER MAP FOR dsPIC30F2012/3013

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset State         |

|-------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|---------------------|

| TRISD       | 02D2  | _      | _      | _      | _      | _      | _      | TRISD9 | TRISD8 | _     | _     | _     | _     | _     | _     | _     | _     | 0000 0011 0000 0000 |

| PORTD       | 02D4  | _      | _      | _      | -      | _      | _      | RD9    | RD8    | _     | _     | _     | _     | _     | _     | _     | _     | 0000 0000 0000 0000 |

| LATD        | 02D6  |        |        | _      |        | _      | _      | LATD9  | LATD8  | _     | _     | _     | _     | _     |       | _     | _     | 0000 0000 0000 0000 |

**Legend:** — = unimplemented bit, read as '0'

#### TABLE 7-6: PORTF REGISTER MAP FOR dsPIC30F2012/3013

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 | Reset State         |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|--------|--------|--------|--------|--------|-------|-------|---------------------|

| TRISF       | 02DE  | _      | _      | _      | _      | _      | _      | _     | _     | _     | TRISF6 | TRISF5 | TRISF4 | TRISF3 | TRISF2 | _     | _     | 0000 0000 0111 1100 |

| PORTF       | 02E0  | -      | _      | -      | _      | _      | -      |       | _     | _     | RF6    | RF5    | RF4    | RF3    | RF2    | _     | _     | 0000 0000 0000 0000 |

| LATF        | 02E2  | _      | _      | _      | _      | _      | _      | _     | _     | _     | LATF6  | LATF5  | LATF4  | LATF3  | LATF2  | _     | _     | 0000 0000 0000 0000 |

**Legend:** — = unimplemented bit, read as '0'

**Note:** The dsPIC30F2011/3012 devices do not have TRISF, PORTF, or LATF.

#### TABLE 13-1: SPI1 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7     | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | Reset State         |

|-------------|-------|--------|--------|---------|--------|--------|--------|-------|-----------|-----------|--------|-------|-------|-------|-------|--------|--------|---------------------|

| SPI1STAT    | 0220  | SPIEN  | _      | SPISIDL | _      | _      | _      | _     | _         | _         | SPIROV |       | _     |       | _     | SPITBF | SPIRBF | 0000 0000 0000 0000 |

| SPI1CON     | 0222  | _      | FRMEN  | SPIFSD  | _      | DISSDO | MODE16 | SMP   | CKE       | SSEN      | CKP    | MSTEN | SPRE2 | SPRE1 | SPRE0 | PPRE1  | PPRE0  | 0000 0000 0000 0000 |

| SPI1BUF     | 0224  |        |        |         |        |        |        | Tra   | ansmit an | d Receive | Buffer |       |       |       |       |        |        | 0000 0000 0000 0000 |

dsPIC30F2011/2012/3012/3013

**Legend:** — = unimplemented bit, read as '0'

Note: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

#### 16.7 ADC Speeds

The dsPIC30F 12-bit ADC specifications permit a maximum of 200 ksps sampling rate. Table 16-1 summarizes the conversion speeds for the dsPIC30F 12-bit ADC and the required operating conditions.

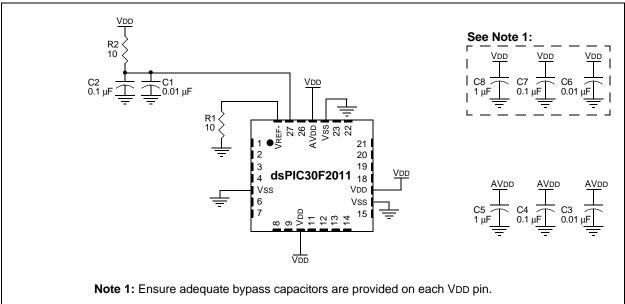

Figure 16-2 depicts the recommended circuit for the conversion rates above 200 ksps. The dsPIC30F2011 is shown as an example.

TABLE 16-1: 12-BIT ADC EXTENDED CONVERSION RATES

|                                  |                            | (                    | dsPIC30F           | 12-bit Al          | DC Conversion R | ates                      |

|----------------------------------|----------------------------|----------------------|--------------------|--------------------|-----------------|---------------------------|

| Speed                            | T <sub>AD</sub><br>Minimum | Sampling<br>Time Min | R <sub>s</sub> Max | VDD                | Temperature     | Channel Configuration     |

| Up to 200<br>ksps <sup>(1)</sup> | 334 ns                     | 1 TAD                | 2.5 kΩ             | 4.5V<br>to<br>5.5V | -40°C to +85°C  | ANX CHX ADC               |

| Up to 100<br>ksps                | 668 ns                     | 1 TAD                | 2.5 kΩ             | 3.0V<br>to<br>5.5V | -40°C to +125°C | ANX CHX ADC  ANX OF VREF- |

Note 1: External VREF+ and VREF+ pins must be used for correct operation. See Figure 16-2 for recommended circuit.

#### FIGURE 16-2: ADC VOLTAGE REFERENCE SCHEMATIC

#### 16.13 Configuring Analog Port Pins

The use of the ADPCFG and TRIS registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CH0SA<3:0>/CH0SB<3:0> bits and the TRIS bits.

When reading the PORT register, all pins configured as analog input channels will read as cleared.

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin that is defined as a digital input (including the ANx pins) may cause the input buffer to consume current that exceeds the device specifications.

#### 16.14 Connection Considerations

The analog inputs have diodes to VDD and VSS as ESD protection. This requires that the analog input be between VDD and VSS. If the input voltage exceeds this range by greater than 0.3V (either direction), one of the diodes becomes forward biased and it may damage the device if the input current specification is exceeded.

An external RC filter is sometimes added for anti-aliasing of the input signal. The R component should be selected to ensure that the sampling time requirements are satisfied. Any external components connected (via high-impedance) to an analog input pin (capacitor, zener diode, etc.) should have very little leakage current at the pin.

TABLE 16-2: A/D CONVERTER REGISTER MAP FOR dsPIC30F2011/3012

| SFR<br>Name | Addr. | Bit 15 | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10                               | Bit 9 | Bit 8   | Bit 7 | Bit 6    | Bit 5       | Bit 4 | Bit 3 | Bit 2  | Bit 1               | Bit 0 | Reset State         |

|-------------|-------|--------|-----------|--------|--------|--------|--------------------------------------|-------|---------|-------|----------|-------------|-------|-------|--------|---------------------|-------|---------------------|

| ADCBUF0     | 0280  | _      | _         | _      | _      |        |                                      |       |         |       | ADC Da   | ta Buffer 0 | )     |       |        |                     |       | 0000 uuuu uuuu uuuu |

| ADCBUF1     | 0282  | _      | _         | _      | _      |        |                                      |       |         |       | ADC Da   | ta Buffer 1 |       |       |        |                     |       | 0000 uuuu uuuu uuuu |

| ADCBUF2     | 0284  |        |           |        |        |        |                                      |       |         |       | ADC Da   | ta Buffer 2 | !     |       |        |                     |       | 0000 uuuu uuuu uuuu |

| ADCBUF3     | 0286  |        |           | _      | _      |        |                                      |       |         |       | ADC Da   | ta Buffer 3 | 1     |       |        |                     |       | 0000 uuuu uuuu uuuu |

| ADCBUF4     | 0288  | _      | _         | _      | _      |        |                                      |       |         |       | ADC Da   | ta Buffer 4 |       |       |        |                     |       | 0000 uuuu uuuu uuuu |

| ADCBUF5     | 028A  |        |           | _      | _      |        |                                      |       |         |       | ADC Da   | ta Buffer 5 | i     |       |        |                     |       | 0000 uuuu uuuu uuuu |

| ADCBUF6     | 028C  |        |           | _      | _      |        |                                      |       |         |       | ADC Da   | ta Buffer 6 | i     |       |        |                     |       | 0000 uuuu uuuu uuuu |

| ADCBUF7     | 028E  |        |           |        |        |        | ADC Data Buffer 7  ADC Data Buffer 8 |       |         |       |          |             |       |       |        | 0000 uuuu uuuu uuuu |       |                     |

| ADCBUF8     | 0290  |        |           |        |        |        | ADC Data Buffer 8                    |       |         |       |          |             |       |       |        | 0000 uuuu uuuu uuuu |       |                     |

| ADCBUF9     | 0292  |        |           |        |        |        |                                      |       |         |       |          |             |       |       |        | 0000 uuuu uuuu uuuu |       |                     |

| ADCBUFA     | 0294  |        | -         | _      | _      |        |                                      |       |         |       | ADC Data | a Buffer 10 | )     |       |        |                     |       | 0000 uuuu uuuu uuuu |

| ADCBUFB     | 0296  | _      | _         | _      | _      |        |                                      |       |         |       | ADC Dat  | a Buffer 1  | 1     |       |        |                     |       | 0000 uuuu uuuu uuuu |

| ADCBUFC     | 0298  | _      | _         | _      | _      |        |                                      |       |         |       | ADC Data | a Buffer 12 | 2     |       |        |                     |       | 0000 uuuu uuuu uuuu |

| ADCBUFD     | 029A  | _      | _         | _      | _      |        |                                      |       |         |       | ADC Data | a Buffer 13 | 3     |       |        |                     |       | 0000 uuuu uuuu uuuu |

| ADCBUFE     | 029C  |        | -         | _      | _      |        |                                      |       |         |       | ADC Data | a Buffer 14 | 4     |       |        |                     |       | 0000 uuuu uuuu uuuu |

| ADCBUFF     | 029E  |        | -         | _      | _      |        |                                      |       |         |       | ADC Data | a Buffer 15 | 5     |       |        |                     |       | 0000 uuuu uuuu uuuu |

| ADCON1      | 02A0  | ADON   | -         | ADSIDL | _      | _      |                                      | FORM  | /l<1:0> | S     | SRC<2:0  | >           | _     | _     | ASAM   | SAMP                | DONE  | 0000 0000 0000 0000 |

| ADCON2      | 02A2  | V      | 'CFG<2:0> | •      | _      | _      | CSCNA                                |       | _       | BUFS  | _        |             | SMPI  | <3:0> |        | BUFM                | ALTS  | 0000 0000 0000 0000 |

| ADCON3      | 02A4  | _      | _         | _      |        | SA     | MC<4:0>                              |       |         | ADRC  | _        |             |       | ADC   | S<5:0> |                     |       | 0000 0000 0000 0000 |

| ADCHS       | 02A6  | _      | _         | _      | CH0NB  |        | CH0SB                                | <3:0> |         | _     | _        | _           | CH0NA |       | CH0S   | SA<3:0>             |       | 0000 0000 0000 0000 |

| ADPCFG      | 02A8  | _      | _         | _      | _      | _      | _                                    | _     | _       | PCFG7 | PCFG6    | PCFG5       | PCFG4 | PCFG3 | PCFG2  | PCFG1               | PCFG0 | 0000 0000 0000 0000 |

| ADCSSL      | 02AA  | _      | _         | _      | _      | _      | _                                    | _     | _       | CSSL7 | CSSL6    | CSSL5       | CSSL4 | CSSL3 | CSSL2  | CSSL1               | CSSL0 | 0000 0000 0000 0000 |

**Legend:** u = uninitialized bit; — = unimplemented bit, read as '0'

Note: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

TABLE 17-1: OSCILLATOR OPERATING MODES

| Oscillator Mode                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XTL XT XT w/PLL 4x XT w/PLL 8x XT w/PLL 16x LP HS      | 200 kHz-4 MHz crystal on OSC1:OSC2. 4 MHz-10 MHz crystal on OSC1:OSC2. 4 MHz-10 MHz crystal on OSC1:OSC2, 4x PLL enabled. 4 MHz-10 MHz crystal on OSC1:OSC2, 8x PLL enabled. 4 MHz-7.5 MHz crystal on OSC1:OSC2, 16x PLL enabled <sup>(1)</sup> . 32 kHz crystal on SOSCO:SOSCI <sup>(2)</sup> . 10 MHz-25 MHz crystal.                                                                                                                      |

| HS/2 w/PLL 4x<br>HS/2 w/PLL 8x<br>HS/2 w/PLL 16x       | 10 MHz-20 MHz crystal, divide by 2, 4x PLL enabled. 10 MHz-20 MHz crystal, divide by 2, 8x PLL enabled. 10 MHz-15 MHz crystal, divide by 2, 16x PLL enabled <sup>(1)</sup> .                                                                                                                                                                                                                                                                 |

| HS/3 w/PLL 4x<br>HS/3 w/PLL 8x<br>HS/3 w/PLL 16x       | 12 MHz-25 MHz crystal, divide by 3, 4x PLL enabled. 12 MHz-25 MHz crystal, divide by 3, 8x PLL enabled. 12 MHz-22.5 MHz crystal, divide by 3, 16x PLL enabled <sup>(1)</sup> .                                                                                                                                                                                                                                                               |

| EC ECIO EC w/PLL 4x EC w/PLL 8x EC w/PLL 16x ERC ERCIO | External clock input (0-40 MHz).  External clock input (0-40 MHz), OSC2 pin is I/O.  External clock input (4-10 MHz), OSC2 pin is I/O, 4x PLL enabled.  External clock input (4-10 MHz), OSC2 pin is I/O, 8x PLL enabled.  External clock input (4-7.5 MHz), OSC2 pin is I/O, 16x PLL enabled <sup>(1)</sup> .  External RC oscillator, OSC2 pin is Fosc/4 output <sup>(3)</sup> .  External RC oscillator, OSC2 pin is I/O <sup>(3)</sup> . |

| FRC w/PLL 4x FRC w/PLL 8x FRC w/PLL 16x LPRC           | 7.37 MHz internal RC oscillator. 7.37 MHz Internal RC oscillator, 4x PLL enabled. 7.37 MHz Internal RC oscillator, 8x PLL enabled. 7.37 MHz Internal RC oscillator, 16x PLL enabled. 512 kHz internal RC oscillator.                                                                                                                                                                                                                         |

- Note 1: dsPIC30F maximum operating frequency of 120 MHz must be met.

- 2: LP oscillator can be conveniently shared as system clock, as well as real-time clock for Timer1.

- **3:** Requires external R and C. Frequency operation up to 4 MHz.

#### 19.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC® DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 19.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 19.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easy-to-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 19.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

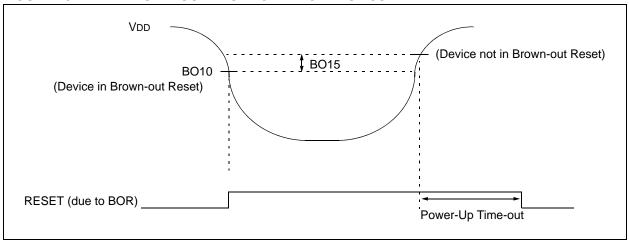

FIGURE 20-2: BROWN-OUT RESET CHARACTERISTICS

TABLE 20-11: ELECTRICAL CHARACTERISTICS: BOR

| DC CHAR      | ACTERIST | ICS                                                  | Standard Opera<br>(unless otherw<br>Operating temp | ise state | <b>ed)</b><br>-40°C ≤ | ≦Ta ≤+85′ | °C for Ir | ndustrial<br>Extended  |

|--------------|----------|------------------------------------------------------|----------------------------------------------------|-----------|-----------------------|-----------|-----------|------------------------|

| Param<br>No. | Symbol   | Character                                            | istic                                              | Min       | Typ <sup>(1)</sup>    | Max       | Units     | Conditions             |

| BO10         | VBOR     | BOR Voltage <sup>(2)</sup> on VDD transition high to | BORV = 11 <sup>(3)</sup>                           | _         | _                     | _         | V         | Not in operating range |

|              |          | low                                                  | BORV = 10                                          | 2.6       | _                     | 2.71      | V         |                        |

|              |          |                                                      | BORV = 01                                          | 4.1       | _                     | 4.4       | V         |                        |

|              |          |                                                      | BORV = 00                                          | 4.58      | _                     | 4.73      | V         |                        |

| BO15         | VBHYS    |                                                      |                                                    | _         | 5                     | _         | mV        |                        |

- **Note 1:** Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: These parameters are characterized but not tested in manufacturing.

- **3:** 11 values not in usable operating range.

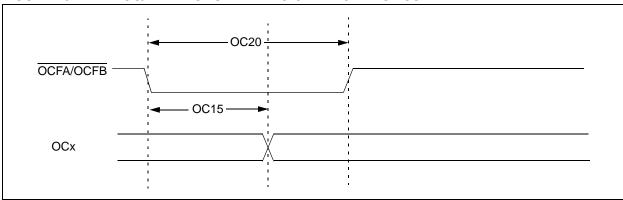

FIGURE 20-11: OC/PWM MODULE TIMING CHARACTERISTICS

TABLE 20-28: SIMPLE OC/PWM MODE TIMING REQUIREMENTS

| AC CHA       | ARACTER | ISTICS                        |     | Standard Operating Conditions: 2.5V to 5.5V (unless otherwise stated)  Operating temperature -40°C ≤TA ≤+85°C for Industrial -40°C ≤TA ≤+125°C for Extended |     |       |            |

|--------------|---------|-------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------------|

| Param<br>No. | Symbol  | Characteristic <sup>(1)</sup> | Min | Typ <sup>(2)</sup>                                                                                                                                          | Max | Units | Conditions |

| OC15         | TFD     | Fault Input to PWM I/O Change |     | _                                                                                                                                                           | 50  | ns    |            |

| OC20         | TFLT    | Fault Input Pulse Width       | 50  |                                                                                                                                                             | _   | ns    |            |

Note 1: These parameters are characterized but not tested in manufacturing.

<sup>2:</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

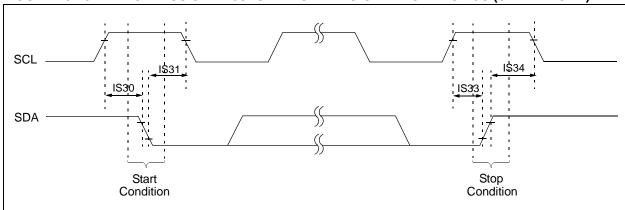

FIGURE 20-18: I<sup>2</sup>C™ BUS START/STOP BITS TIMING CHARACTERISTICS (SLAVE MODE)

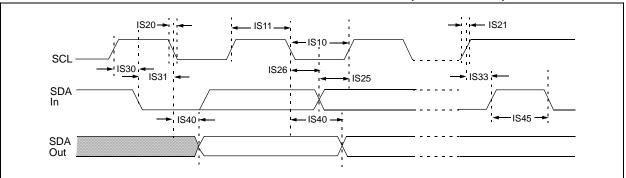

FIGURE 20-19: I<sup>2</sup>C™ BUS DATA TIMING CHARACTERISTICS (SLAVE MODE)

TABLE 20-34: I<sup>2</sup>C™ BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

| AC CHARACTERISTICS | Standard Operating Conditions: 2.5V to 5.5V (unless otherwise stated) |  |  |  |  |  |

|--------------------|-----------------------------------------------------------------------|--|--|--|--|--|

| AC CHARACTERISTICS | Operating temperature -40°C ≤TA ≤+85°C for Industrial                 |  |  |  |  |  |

|                    | -40°C ≤TA ≤+125°C for Extended                                        |  |  |  |  |  |

| Param<br>No. | Symbol  | Charac                   | teristic                  | Min         | Max  | Units | Conditions                                  |

|--------------|---------|--------------------------|---------------------------|-------------|------|-------|---------------------------------------------|

| IS10         | TLO:SCL | Clock Low Time           | 100 kHz mode              | 4.7         | _    | μs    | Device must operate at a minimum of 1.5 MHz |

|              |         |                          | 400 kHz mode              | 1.3         | _    | μs    | Device must operate at a minimum of 10 MHz. |

|              |         |                          | 1 MHz mode <sup>(1)</sup> | 0.5         |      | μs    |                                             |

| IS11         | THI:SCL | Clock High Time          | 100 kHz mode              | 4.0         | _    | μs    | Device must operate at a minimum of 1.5 MHz |

|              |         |                          | 400 kHz mode              | 0.6         | _    | μs    | Device must operate at a minimum of 10 MHz  |

|              |         |                          | 1 MHz mode <sup>(1)</sup> | 0.5         | _    | μs    |                                             |

| IS20         | TF:SCL  | SDA and SCL<br>Fall Time | 100 kHz mode              | _           | 300  | ns    | CB is specified to be from 10 to 400 pF     |

|              |         |                          | 400 kHz mode              | 20 + 0.1 CB | 300  | ns    |                                             |

|              |         |                          | 1 MHz mode <sup>(1)</sup> | _           | 100  | ns    |                                             |

| IS21         | TR:SCL  | SDA and SCL<br>Rise Time | 100 kHz mode              | _           | 1000 | ns    | CB is specified to be from 10 to 400 pF     |

|              |         |                          | 400 kHz mode              | 20 + 0.1 CB | 300  | ns    |                                             |

|              |         |                          | 1 MHz mode <sup>(1)</sup> | _           | 300  | ns    |                                             |

**Note 1:** Maximum pin capacitance = 10 pF for all  $I^2C^{TM}$  pins (for 1 MHz mode only).

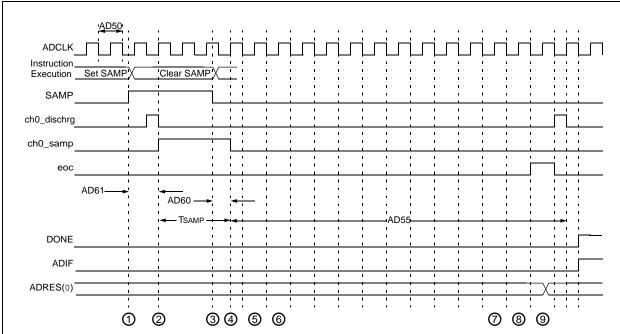

FIGURE 20-21: 12-BIT A/D CONVERSION TIMING CHARACTERISTICS (ASAM = 0, SSRC = 000)

- 1 Software sets ADCON. SAMP to start sampling.

- ② Sampling starts after discharge period.

TSAMP is described in **Section 18. "12-bit A/D Converter"** in the *dsPIC30F Family Reference Manual* (DS70046).

- 3 Software clears ADCON. SAMP to Start conversion.

- 4 Sampling ends, conversion sequence starts.

- (5) Convert bit 11.

- 6 Convert bit 10.

- 7 Convert bit 1.

- 8 Convert bit 0.

- (9) One TAD for end of conversion.

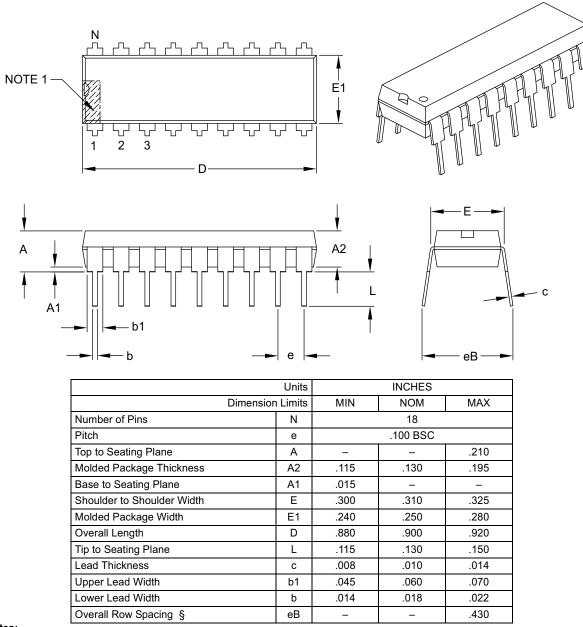

#### 18-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-007B

| Interrupt Controller                                  | PLL Clock Timing Specifications                     | 162  |

|-------------------------------------------------------|-----------------------------------------------------|------|

| Register Map71, 72                                    | POR. See Power-on Reset.                            |      |

| Interrupt Priority66                                  | Port Write/Read Example                             | 60   |

| Traps67                                               | PORTB                                               |      |

| Interrupt Sequence                                    | Register Map for dsPIC30F2011/3012                  |      |

| Interrupt Stack Frame69                               | Register Map for dsPIC30F2012/3013                  | 61   |

| Interrupts65                                          | PORTC                                               |      |

| L                                                     | Register Map for dsPIC30F2011/2012/3012/3013        | 3 61 |

|                                                       | PORTD                                               |      |

| Load Conditions                                       | Register Map for dsPIC30F2011/3012                  |      |

| Low Voltage Detect (LVD)                              | Register Map for dsPIC30F2012/3013                  | 62   |

| Low-Voltage Detect Characteristics                    | PORTF                                               |      |

| LVDL Characteristics                                  | Register Map for dsPIC30F2012/3013                  |      |

| M                                                     | Power Saving Modes                                  |      |

| Memory Organization                                   | Idle                                                |      |

| Core Register Map                                     | Sleep                                               |      |

| Microchip Internet Web Site                           | Sleep and Idle                                      |      |

| Modulo Addressing                                     | Power-Down Current (IPD)Power-up Timer              | 154  |

| Applicability                                         | Timing Characteristics                              | 166  |

| Incrementing Buffer Operation Example45               | •                                                   |      |

| Start and End Address                                 | Timing Requirements Program Address Space           |      |

| W Address Register Selection45                        | Construction                                        |      |

| MPLAB ASM30 Assembler, Linker, Librarian              | Data Access from Program Memory Using               | 3    |

| MPLAB Integrated Development Environment Software 145 | Program Space Visibility                            | 3:   |

| MPLAB PM3 Device Programmer148                        | Data Access From Program Memory Using               | 50   |

| MPLAB REAL ICE In-Circuit Emulator System147          | Table Instructions                                  | 30   |

| MPLINK Object Linker/MPLIB Object Librarian146        | Data Access from, Address Generation                |      |

| ,                                                     | Data Space Window into Operation                    |      |

| N                                                     | Data Table Access (LS Word)                         |      |

| NVM                                                   | Data Table Access (MS Byte)                         |      |

| Register Map53                                        | Memory Maps                                         |      |

| 0                                                     | Table Instructions                                  |      |

| 0                                                     | TBLRDH                                              | 32   |

| OC/PWM Module Timing Characteristics171               | TBLRDL                                              |      |

| Operating Current (IDD)152                            | TBLWTH                                              |      |

| Operating Frequency vs Voltage                        | TBLWTL                                              | 32   |

| dsPIC30FXXXX-20 (Extended)                            | Program and EEPROM Characteristics                  | 159  |

| Oscillator                                            | Program Counter                                     |      |

| Configurations                                        | Programmable                                        |      |

| Fail-Safe Clock Monitor                               | Programmer's Model                                  | 20   |

| Fast RC (FRC)                                         | Diagram                                             | 21   |

| Initial Clock Source Selection                        | Programming Operations                              | 51   |

| Low-Power RC (LPRC)                                   | Algorithm for Program Flash                         |      |

| LP Oscillator Control                                 | Erasing a Row of Program Memory                     | 51   |

| Phase Locked Loop (PLL)                               | Initiating the Programming Sequence                 | 52   |

| • • • •                                               | Loading Write Latches                               |      |

| Operating Modes (Table)                               | Protection Against Accidental Writes to OSCCON      | 128  |

| Oscillator Selection                                  | R                                                   |      |

| Oscillator Start-up Timer                             |                                                     |      |

| Timing Characteristics165                             | Reader Response                                     |      |

| Timing Requirements                                   | Reset                                               |      |

| Output Compare Interrupts                             | BOR, Programmable                                   |      |

| Output Compare Module                                 | Brown-out Reset (BOR)                               |      |

| Register Map91                                        | Oscillator Start-up Timer (OST)                     | 123  |

| Timing Characteristics170                             | POR                                                 | 404  |

| Timing Requirements170                                | Operating without FSCM and PWRT                     |      |

| Output Compare Operation During CPU Idle Mode 90      | With Long Crystal Start-up TimePOR (Power-on Reset) |      |

| Output Compare Sleep Mode Operation90                 |                                                     |      |

|                                                       | Power-on Reset (POR)<br>Power-up Timer (PWRT)       |      |

| P                                                     | Reset Sequence                                      |      |

| Packaging Information187                              | Reset Sources                                       |      |

| Marking 187, 188                                      | Reset Sources                                       | 07   |

| Peripheral Module Disable (PMD) Registers 135         | Brown-out Reset (BOR)                               | 67   |

| Pinout Descriptions                                   | Illegal Instruction Trap                            |      |

| Reset                                               |     |

|-----------------------------------------------------|-----|

| Simple OC/PWM Mode                                  | 171 |

| SPI Module                                          |     |

| Master Mode (CKE = 0)                               | 172 |

| Master Mode (CKE = 1)                               | 173 |

| Slave Mode (CKE = 0)                                | 174 |

| Slave Mode (CKE = 1)                                |     |

| Type A Timer External Clock                         |     |

| Type B Timer External Clock                         |     |

| Type C Timer External Clock                         |     |

| Watchdog Timer                                      |     |

| Timing Specifications                               |     |

| PLL Clock                                           | 162 |

| Trap Vectors                                        |     |

| Trap vectors                                        | 03  |

| U                                                   |     |

| UART Module                                         |     |

|                                                     | 100 |

| Address Detect Mode                                 |     |

| Auto-Baud Support                                   |     |

| Baud Rate Generator                                 |     |

| Enabling and Setting Up                             |     |

| Framing Error (FERR)                                |     |

| Idle Status                                         | 109 |

| Loopback Mode                                       |     |

| Operation During CPU Sleep and Idle Modes           | 110 |

| Overview                                            |     |

| Parity Error (PERR)                                 | 109 |

| Receive Break                                       |     |

| Receive Buffer (UxRXB)                              |     |

| Receive Buffer Overrun Error (OERR Bit)             |     |

| Receive Interrupt                                   |     |

| Receiving Data                                      |     |

| Receiving bataReceiving in 8-bit or 9-bit Data Mode |     |

| Reception Error Handling                            |     |

| Transmit Break                                      |     |

|                                                     |     |

| Transmit Buffer (UxTXB)                             |     |

| Transmit Interrupt                                  |     |

| Transmitting Data                                   |     |

| Transmitting in 8-bit Data Mode                     |     |

| Transmitting in 9-bit Data Mode                     |     |

| UART1 Register Map                                  |     |

| UART2 Register Map                                  | 111 |

| UART Operation                                      |     |

| Idle Mode                                           | 110 |

| Sleep Mode                                          |     |

| Unit ID Locations                                   | 123 |

| Universal Asynchronous Receiver Transmitter         |     |

| (UART) Module                                       | 105 |

| , ,                                                 |     |

| W                                                   |     |

| Wake-up from Sleep                                  | 123 |

| Wake-up from Sleep and Idle                         |     |

| Watchdog Timer                                      |     |

| Timing Characteristics                              | 165 |

| Timing Requirements                                 |     |

|                                                     |     |

| Watchdog Timer (WDT)                                |     |

| Enabling and Disabling                              |     |

| Operation                                           |     |

| WWW Address                                         |     |

| WWW, On-Line Support                                | 9   |