Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | dsPIC                                                                         |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 30 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 20                                                                            |

| Program Memory Size        | 24KB (8K x 24)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 1K x 8                                                                        |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 10x12b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Through Hole                                                                  |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                       |

| Supplier Device Package    | 28-SPDIP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f3013-30i-sp |

The core does not support a multi-stage instruction pipeline. However, a single-stage instruction prefetch mechanism is used, which accesses and partially decodes instructions a cycle ahead of execution, in order to maximize available execution time. Most instructions execute in a single cycle with certain exceptions.

The core features a vectored exception processing structure for traps and interrupts, with 62 independent vectors. The exceptions consist of up to 8 traps (of which 4 are reserved) and 54 interrupts. Each interrupt is prioritized based on a user-assigned priority between 1 and 7 (1 being the lowest priority and 7 being the highest), in conjunction with a predetermined 'natural order'. Traps have fixed priorities ranging from 8 to 15.

### 2.2 Programmer's Model

The programmer's model is shown in Figure 2-1 and consists of 16 x 16-bit working registers (W0 through W15), 2 x 40-bit accumulators (ACCA and ACCB), STATUS register (SR), Data Table Page register (TBLPAG), Program Space Visibility Page register (PSVPAG), DO and REPEAT registers (DOSTART, DOEND, DCOUNT and RCOUNT) and Program Counter (PC). The working registers can act as data, address or offset registers. All registers are memory mapped. W0 acts as the W register for file register addressing.

Some of these registers have a shadow register associated with each of them, as shown in Figure 2-1. The shadow register is used as a temporary holding register and can transfer its contents to or from its host register upon the occurrence of an event. None of the shadow registers are accessible directly. The following rules apply for transfer of registers into and out of shadows.

- PUSH.S and POP.S W0, W1, W2, W3, SR (DC, N, OV, Z and C bits only) are transferred.

- DO instruction DOSTART, DOEND, DCOUNT shadows are pushed on loop start and popped on loop end.

When a byte operation is performed on a working register, only the Least Significant Byte (LSB) of the target register is affected. However, a benefit of memory mapped working registers is that both the Least and Most Significant Bytes (MSB) can be manipulated through byte-wide data memory space accesses.

### 2.2.1 SOFTWARE STACK POINTER/ FRAME POINTER

The dsPIC<sup>®</sup> DSC devices contain a software stack. W15 is the dedicated Software Stack Pointer (SP), which is automatically modified by exception processing and subroutine calls and returns. However, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies the reading, writing and manipulation of the Stack Pointer (e.g., creating stack frames).

**Note:** In order to protect against misaligned stack accesses, W15<0> is always clear.

W15 is initialized to 0x0800 during a Reset. The user may reprogram the SP during initialization to any location within data space.

W14 has been dedicated as a Stack Frame Pointer, as defined by the LNK and ULNK instructions. However, W14 can be referenced by any instruction in the same manner as all other W registers.

#### 2.2.2 STATUS REGISTER

The dsPIC DSC core has a 16-bit STATUS register (SR), the LSB of which is referred to as the SR Low byte (SRL) and the MSB as the SR High byte (SRH). See Figure 2-1 for SR layout.

SRL contains all the MCU ALU operation Status flags (including the Z bit), as well as the CPU Interrupt Priority Level Status bits, IPL<2:0>, and the Repeat Active Status bit, RA. During exception processing, SRL is concatenated with the MSB of the PC to form a complete word value which is then stacked.

The upper byte of the STATUS register contains the DSP Adder/Subtracter Status bits, the DO Loop Active bit (DA) and the Digit Carry (DC) Status bit.

### 2.2.3 PROGRAM COUNTER

The program counter is 23 bits wide; bit 0 is always clear. Therefore, the PC can address up to 4M instruction words.

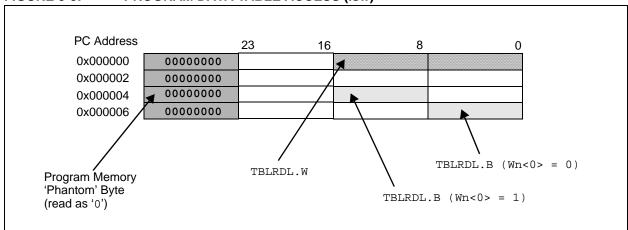

# 3.1.1 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

This architecture fetches 24-bit wide program memory. Consequently, instructions are always aligned. However, as the architecture is modified Harvard, data can also be present in program space.

There are two methods by which program space can be accessed: via special table instructions, or through the remapping of a 16K word program space page into the upper half of data space (see Section 3.1.2 "Data Access from Program Memory Using Program Space Visibility"). The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lsw of any address within program space, without going through data space. The TBLRDH and TBLWTH instructions are the only method whereby the upper 8 bits of a program space word can be accessed as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit word wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the lsw, and TBLRDH and TBLWTH access the space which contains the MSB.

Figure 3-2 shows how the EA is created for table operations and data space accesses (PSV = 1). Here, P<23:0> refers to a program space word, whereas D<15:0> refers to a data space word.

A set of table instructions are provided to move byte or word-sized data to and from program space. See Figure 3-4 and Figure 3-5.

- 1. TBLRDL: Table Read Low

- Word: Read the LS Word of the program address; P<15:0> maps to D<15:0>.

- Byte: Read one of the LSB of the program address:

- P<7:0> maps to the destination byte when byte select = 0:

- P<15:8> maps to the destination byte when byte select = 1.

- TBLWTL: Table Write Low (refer to Section 5.0

"Flash Program Memory" for details on Flash

Programming)

- 3. TBLRDH: Table Read High

- *Word:* Read the MS Word of the program address; P<23:16> maps to D<7:0>; D<15:8> will always be = 0.

- Byte: Read one of the MSB of the program address;

- P<23:16> maps to the destination byte when byte select = 0:

- The destination byte will always be = 0 when byte select = 1.

- TBLWTH: Table Write High (refer to Section 5.0

"Flash Program Memory" for details on Flash

Programming)

**NOTES:**

### **7.0 I/O PORTS**

Note:

This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

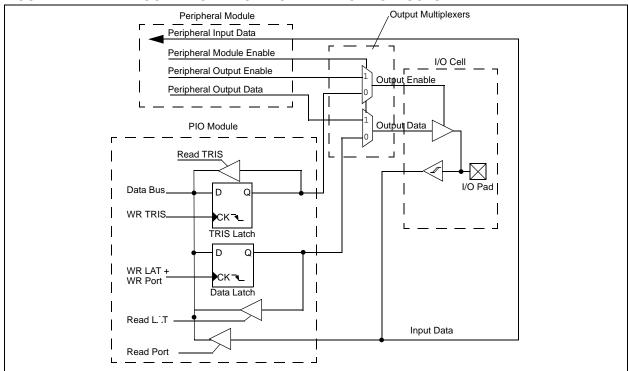

All of the device pins (except VDD, Vss,  $\overline{MCLR}$  and OSC1/CLKI) are shared between the peripherals and the parallel I/O ports.

All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

### 7.1 Parallel I/O (PIO) Ports

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have three registers directly associated with the operation of the port pin. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx), read the latch.

Writes to the latch, write the latch (LATx). Reads from the port (PORTx), read the port pins and writes to the port pins, write the latch (LATx).

Any bit and its associated data and Control registers that are not valid for a particular device are disabled. That means the corresponding LATx and TRISx registers and the port pin read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

A parallel I/O (PIO) port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pad cell. Figure 7-1 illustrates how ports are shared with other peripherals and the associated I/O cell (pad) to which they are connected.

The format of the registers for the shared ports, (PORTB, PORTC, PORTD and PORTF) are shown in Table 7-1 through Table 7-6.

**Note:** The actual bits in use vary between devices.

FIGURE 7-1: BLOCK DIAGRAM OF A SHARED PORT STRUCTURE

Enabling an interrupt is accomplished via the respective timer interrupt enable bit, T1IE. The timer interrupt enable bit is located in the IEC0 Control register in the interrupt controller.

TABLE 14-2: I<sup>2</sup>C REGISTER MAP

| SFR Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9            | Bit 8 | Bit 7               | Bit 6 | Bit 5 | Bit 4               | Bit 3    | Bit 2               | Bit 1 | Bit 0 | Reset State         |

|----------|-------|---------|--------|---------|--------|--------|--------|------------------|-------|---------------------|-------|-------|---------------------|----------|---------------------|-------|-------|---------------------|

| I2CRCV   | 0200  | ı       | _      | ı       | _      | _      | _      | _                | _     |                     |       |       | Receive R           | Register |                     |       |       | 0000 0000 0000 0000 |

| I2CTRN   | 0202  | -       | _      |         | _      | _      | _      | _                | _     |                     |       |       | Transmit F          | Register |                     |       |       | 0000 0000 1111 1111 |

| I2CBRG   | 0204  | _       | _      | _       | _      | _      |        | _                |       | Baud Rate Generator |       |       |                     |          | 0000 0000 0000 0000 |       |       |                     |

| I2CCON   | 0206  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW           | SMEN  | GCEN                | STREN | ACKDT | ACKEN               | RCEN     | PEN                 | RSEN  | SEN   | 0001 0000 0000 0000 |

| I2CSTAT  | 0208  | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT           | ADD10 | IWCOL               | I2COV | D_A   | Р                   | S        | R_W                 | RBF   | TBF   | 0000 0000 0000 0000 |

| I2CADD   | 020A  | _       | _      | _       | _      | _      | _      | Address Register |       |                     |       |       | 0000 0000 0000 0000 |          |                     |       |       |                     |

**Legend:** — = unimplemented bit, read as '0'

Note: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

### 15.2 Enabling and Setting Up UART

#### 15.2.1 ENABLING THE UART

The UART module is enabled by setting the UARTEN bit in the UxMODE register (where x = 1 or 2). Once enabled, the UxTX and UxRX pins are configured as an output and an input respectively, overriding the TRIS and LAT register bit settings for the corresponding I/O port pins. The UxTX pin is at logic '1' when no transmission is taking place.

#### 15.2.2 DISABLING THE UART

The UART module is disabled by clearing the UARTEN bit in the UxMODE register. This is the default state after any Reset. If the UART is disabled, all I/O pins operate as port pins under the control of the LAT and TRIS bits of the corresponding port pins.

Disabling the UART module resets the buffers to empty states. Any data characters in the buffers are lost and the baud rate counter is reset.

All error and status flags associated with the UART module are reset when the module is disabled. The URXDA, OERR, FERR, PERR, UTXEN, UTXBRK and UTXBF bits are cleared, whereas RIDLE and TRMT are set. Other control bits, including ADDEN, URXISEL<1:0>, UTXISEL, as well as the UxMODE and UxBRG registers, are not affected.

Clearing the UARTEN bit while the UART is active will abort all pending transmissions and receptions and reset the module as defined above. Re-enabling the UART will restart the UART in the same configuration.

### 15.2.3 ALTERNATE I/O

The alternate I/O function is enabled by setting the ALTIO bit (UxMODE<10>). If ALTIO = 1, the UxATX and UxARX pins (alternate transmit and alternate receive pins, respectively) are used by the UART module instead of the UxTX and UxRX pins. If ALTIO = 0, the UxTX and UxRX pins are used by the UART module.

## 15.2.4 SETTING UP DATA, PARITY AND STOP BIT SELECTIONS

Control bits PDSEL<1:0> in the UxMODE register are used to select the data length and parity used in the transmission. The data length may either be 8 bits with even, odd or no parity, or 9 bits with no parity.

The STSEL bit determines whether one or two Stop bits will be used during data transmission.

The default (power-on) setting of the UART is 8 bits, no parity and 1 Stop bit (typically represented as 8, N, 1).

### 15.3 Transmitting Data

### 15.3.1 TRANSMITTING IN 8-BIT DATA MODE

The following steps must be performed to transmit 8-bit data:

#### 1. Set up the UART:

First, the data length, parity and number of Stop bits must be selected. Then, the transmit and receive interrupt enable and priority bits are setup in the UxMODE and UxSTA registers. Also, the appropriate baud rate value must be written to the UxBRG register.

- Enable the UART by setting the UARTEN bit (UxMODE<15>).

- Set the UTXEN bit (UxSTA<10>), thereby enabling a transmission.

- 4. Write the byte to be transmitted to the lower byte of UxTXREG. The value will be transferred to the Transmit Shift register (UxTSR) immediately and the serial bit stream will start shifting out during the next rising edge of the baud clock. Alternatively, the data byte may be written while UTXEN = 0, following which, the user may set UTXEN. This will cause the serial bit stream to begin immediately because the baud clock will start from a cleared state.

- A transmit interrupt will be generated, depending on the value of the interrupt control bit UTXISEL (UxSTA<15>).

### 15.3.2 TRANSMITTING IN 9-BIT DATA MODE

The sequence of steps involved in the transmission of 9-bit data is similar to 8-bit transmission, except that a 16-bit data word (of which the upper 7 bits are always clear) must be written to the UxTXREG register.

### 15.3.3 TRANSMIT BUFFER (UXTXB)

The transmit buffer is 9 bits wide and 4 characters deep. Including the Transmit Shift register (UxTSR), the user effectively has a 5-deep FIFO (First-In, First-Out) buffer. The UTXBF bit (UxSTA<9>) indicates whether the transmit buffer is full.

If a user attempts to write to a full buffer, the new data will not be accepted into the FIFO and no data shift will occur within the buffer. This enables recovery from a buffer overrun condition.

The FIFO is reset during any device Reset, but is not affected when the device enters or wakes up from a Power Saving mode.

## 15.10 UART Operation During CPU Sleep and Idle Modes

### 15.10.1 UART OPERATION DURING CPU SLEEP MODE

When the device enters Sleep mode, all clock sources to the module are shut down and stay at logic '0'. If entry into Sleep mode occurs while a transmission is in progress, then the transmission is aborted. The UxTX pin is driven to logic '1'. Similarly, if entry into Sleep mode occurs while a reception is in progress, then the reception is aborted. The UxSTA, UxMODE, transmit and receive registers and buffers, and the UxBRG register are not affected by Sleep mode.

If the WAKE bit (UxMODE<7>) is set before the device enters Sleep mode, then a falling edge on the UxRX pin will generate a receive interrupt. The Receive Interrupt Select mode bit (URXISEL) has no effect for this function. If the receive interrupt is enabled, then this will wake-up the device from Sleep. The UARTEN bit must be set in order to generate a wake-up interrupt.

## 15.10.2 UART OPERATION DURING CPU IDLE MODE

For the UART, the USIDL bit selects if the module will stop operation when the device enters Idle mode or whether the module will continue on Idle. If USIDL=0, the module will continue to operate during Idle mode. If USIDL=1, the module will stop on Idle.

TABLE 16-3: A/D CONVERTER REGISTER MAP FOR dsPIC30F2012/3013

| SFR<br>Name | Addr. | Bit 15 | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10               | Bit 9 | Bit 8  | Bit 7 | Bit 6    | Bit 5       | Bit 4 | Bit 3               | Bit 2  | Bit 1 | Bit 0 | Reset State         |

|-------------|-------|--------|-----------|--------|--------|--------|----------------------|-------|--------|-------|----------|-------------|-------|---------------------|--------|-------|-------|---------------------|

| ADCBUF0     | 0280  | _      |           |        | _      |        |                      |       |        |       | ADC Dat  | ta Buffer 0 |       |                     |        |       |       | 0000 uuuu uuuu uuuu |

| ADCBUF1     | 0282  | _      | _         | _      | _      |        |                      |       |        |       | ADC Dat  | ta Buffer 1 |       |                     |        |       |       | 0000 uuuu uuuu uuuu |

| ADCBUF2     | 0284  | _      | _         | _      | _      |        |                      |       |        |       | ADC Dat  | ta Buffer 2 |       |                     |        |       |       | 0000 uuuu uuuu uuuu |

| ADCBUF3     | 0286  | _      | _         | _      | _      |        |                      |       |        |       | ADC Dat  | ta Buffer 3 |       |                     |        |       |       | 0000 uuuu uuuu uuuu |

| ADCBUF4     | 0288  | _      | _         | _      | _      |        |                      |       |        |       | ADC Dat  | ta Buffer 4 |       |                     |        |       |       | 0000 uuuu uuuu uuuu |

| ADCBUF5     | 028A  | _      | _         | _      | _      |        |                      |       |        |       | ADC Dat  | ta Buffer 5 |       |                     |        |       |       | 0000 uuuu uuuu uuuu |

| ADCBUF6     | 028C  | _      | _         | _      | _      |        |                      |       |        |       | ADC Dat  | ta Buffer 6 |       |                     |        |       |       | 0000 uuuu uuuu uuuu |

| ADCBUF7     | 028E  | _      | _         | _      | _      |        |                      |       |        |       | ADC Dat  | ta Buffer 7 |       |                     |        |       |       | 0000 uuuu uuuu uuuu |

| ADCBUF8     | 0290  | _      | _         | _      | _      |        |                      |       |        |       | ADC Dat  | ta Buffer 8 |       |                     |        |       |       | 0000 uuuu uuuu uuuu |

| ADCBUF9     | 0292  | _      | _         | _      | _      |        |                      |       |        |       | ADC Dat  | ta Buffer 9 |       |                     |        |       |       | 0000 uuuu uuuu uuuu |

| ADCBUFA     | 0294  | _      | _         | _      | _      |        |                      |       |        |       | ADC Data | a Buffer 10 | )     |                     |        |       |       | 0000 uuuu uuuu uuuu |

| ADCBUFB     | 0296  | _      | _         | _      | _      |        |                      |       |        |       | ADC Data | a Buffer 11 |       |                     |        |       |       | 0000 uuuu uuuu uuuu |

| ADCBUFC     | 0298  | _      | _         | _      | _      |        |                      |       |        |       | ADC Data | a Buffer 12 | 2     |                     |        |       |       | 0000 uuuu uuuu uuuu |

| ADCBUFD     | 029A  | _      | _         | _      | _      |        |                      |       |        |       | ADC Data | a Buffer 13 | 3     |                     |        |       |       | 0000 uuuu uuuu uuuu |

| ADCBUFE     | 029C  | _      | _         | _      | _      |        |                      |       |        |       | ADC Data | a Buffer 14 | 1     |                     |        |       |       | 0000 uuuu uuuu uuuu |

| ADCBUFF     | 029E  | _      | _         | _      | _      |        |                      |       |        |       | ADC Data | a Buffer 15 | 5     |                     |        |       |       | 0000 uuuu uuuu uuuu |

| ADCON1      | 02A0  | ADON   | _         | ADSIDL | _      | _      | _                    | FORM  | /<1:0> | S     | SRC<2:0  | >           | _     | _                   | ASAM   | SAMP  | DONE  | 0000 0000 0000 0000 |

| ADCON2      | 02A2  | V      | 'CFG<2:0> | •      | _      | _      | CSCNA                | _     | _      | BUFS  | _        |             | SMPI  | <3:0>               |        | BUFM  | ALTS  | 0000 0000 0000 0000 |

| ADCON3      | 02A4  | _      | _         | _      |        | SA     | MC<4:0>              |       |        | ADRC  | _        |             |       | ADCS                | S<5:0> |       |       | 0000 0000 0000 0000 |

| ADCHS       | 02A6  | _      | _         | _      | CH0NB  |        | CH0SB<3:0> — — CH0NA |       |        |       | CH0S     | SA<3:0>     |       | 0000 0000 0000 0000 |        |       |       |                     |

| ADPCFG      | 02A8  | _      | _         | _      | _      | _      | _                    | PCFG9 | PCFG8  | PCFG7 | PCFG6    | PCFG5       | PCFG4 | PCFG3               | PCFG2  | PCFG1 | PCFG0 | 0000 0000 0000 0000 |

| ADCSSL      | 02AA  | _      | _         | _      | _      | _      | _                    | CSSL9 | CSSL8  | CSSL7 | CSSL6    | CSSL5       | CSSL4 | CSSL3               | CSSL2  | CSSL1 | CSSL0 | 0000 0000 0000 0000 |

**Legend:** u = uninitialized bit; — = unimplemented bit, read as '0'

**Note:** Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

## 17.8 Peripheral Module Disable (PMD) Registers

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled via the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The Control and Status registers associated with the peripheral will also be disabled so writes to those registers will have no effect and read values will be invalid.

A peripheral module will only be enabled if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

- Note 1: If a PMD bit is set, the corresponding module is disabled after a delay of 1 instruction cycle. Similarly, if a PMD bit is cleared, the corresponding module is enabled after a delay of 1 instruction cycle (assuming the module Control registers are already configured to enable module operation).

- 2: In dsPIC30F2011, dsPIC30F3012 and dsPIC30F2012 devices, the U2MD bit is readable and writable and will be read as '1' when set.

### 17.9 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 2 is selected as a Debugger, the In-Circuit Debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. When the device has this feature enabled, some of the resources are not available for general use. These resources include the first 80 bytes of Data RAM and two I/O pins.

One of four pairs of Debug I/O pins may be selected by the user using configuration options in MPLAB IDE. These pin pairs are named EMUD/EMUC, EMUD1/EMUC1, EMUD2/EMUC2 and EMUD3/EMUC3.

In each case, the selected EMUD pin is the Emulation/Debug Data line, and the EMUC pin is the Emulation/Debug Clock line. These pins will interface to the MPLAB ICD 2 module available from Microchip. The selected pair of Debug I/O pins is used by MPLAB ICD 2 to send commands and receive responses, as well as to send and receive data. To use the In-Circuit Debugger function of the device, the design must implement ICSP connections to MCLR, VDD, Vss, PGC, PGD and the selected EMUDx/EMUCx pin pair.

This gives rise to two possibilities:

- If EMUD/EMUC is selected as the Debug I/O pin pair, then only a 5-pin interface is required, as the EMUD and EMUC pin functions are multiplexed with the PGD and PGC pin functions in all dsPIC30F devices.

- 2. If EMUD1/EMUC1, EMUD2/EMUC2 or EMUD3/EMUC3 is selected as the Debug I/O pin pair, then a 7-pin interface is required, as the EMUDx/EMUCx pin functions (x = 1, 2 or 3) are not multiplexed with the PGD and PGC pin functions.

### TABLE 17-7: SYSTEM INTEGRATION REGISTER MAP

| SFR<br>Name | Address | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9    | Bit 8 | Bit 7 | Bit 6               | Bit 5  | Bit 4 | Bit 3  | Bit 2 | Bit 1   | Bit 0 | Reset State         |

|-------------|---------|--------|--------|--------|--------|--------|--------|----------|-------|-------|---------------------|--------|-------|--------|-------|---------|-------|---------------------|

| RCON        | 0740    | TRAPR  | IOPUWR | BGST   | LVDEN  |        | LVDL   | _<3:0>   |       | EXTR  | SWR                 | SWDTEN | WDTO  | SLEEP  | IDLE  | BOR     | POR   | (Note 1)            |

| OSCCON      | 0742    | _      | CC     | SC<2:0 | >      | _      | N      | IOSC<2:0 | )>    | POS   | Γ<1:0>              | LOCK   | _     | CF     | _     | LPOSCEN | OSWEN | (Note 2)            |

| OSCTUN      | 0744    | _      |        | _      | -      | _      | 1      | _        | _     | _     | _                   | -      | _     | TUN3   | TUN2  | TUN1    | TUN0  | (Note 2)            |

| PMD1        | 0770    | _      |        | T3MD   | T2MD   | T1MD   | 1      | _        | _     | I2CMD | U2MD <sup>(3)</sup> | U1MD   | _     | SPI1MD | _     | _       | ADCMD | 0000 0000 0000 0000 |

| PMD2        | 0772    | _      | _      | _      | _      | _      | _      | IC2MD    | IC1MD | _     | _                   | _      | _     | _      | _     | OC2MD   | OC1MD | 0000 0000 0000 0000 |

Legend:

-- = unimplemented bit, read as '0'

Reset state depends on type of reset. Note 1:

Reset state depends on Configuration bits.

Only available on dsPIC30F3013 devices.

### TABLE 17-8: DEVICE CONFIGURATION REGISTER MAP

| Name    | Address | Bit 15 | Bit 14 | Bit 13 | Bit 12             | Bit 11 | Bit 10                | Bit 9               | Bit 8                   | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3      | Bit 2                   | Bit 1             | Bit 0 |

|---------|---------|--------|--------|--------|--------------------|--------|-----------------------|---------------------|-------------------------|-------|-------|-------|--------|------------|-------------------------|-------------------|-------|

| FOSC    | F80000  | FCKSM  | 1<1:0> | _      | _                  | _      | FOS<2:0> FI           |                     | FPR<4:0>                |       |       |       |        |            |                         |                   |       |

| FWDT    | F80002  | FWDTEN | _      | _      | _                  | _      | _                     | _                   | -                       | _     | _     | FWPS  | A<1:0> | FWPSB<3:0> |                         |                   |       |

| FBORPOR | F80004  | MCLREN | _      | _      | _                  | _      | PWMPIN <sup>(1)</sup> | HPOL <sup>(1)</sup> | LPOL <sup>(1)</sup>     | BOREN | _     | BORV  | /<1:0> | _          | — — FPWRT<1:0>          |                   |       |

| FBS     | F80006  | -      | _      | Reser  | ved <sup>(2)</sup> | _      | _                     | _                   | Reserved <sup>(2)</sup> | _     | _     | _     | _      |            | Reserved <sup>(2)</sup> |                   |       |

| FSS     | F80008  | -      | _      | Reser  | ved <sup>(2)</sup> | _      | _                     | Rese                | erved <sup>(2)</sup>    | _     | _     | _     | _      |            | Reserv                  | ed <sup>(2)</sup> |       |

| FGS     | F8000A  | -      | _      | _      | _                  | _      | _                     | _                   | -                       | _     | _     | _     | _      | _          | Reserved <sup>(3)</sup> | GCP               | GWRP  |

| FICD    | F8000C  | BKBUG  | COE    | _      | _                  |        | _                     | _                   |                         | _     | _     |       | _      | ICS<1:0>   |                         | 1:0>              |       |

dsPIC30F2011/2012/3012/3013

Legend: --- = unimplemented bit, read as '0'

Note 1: These bits are reserved (read as '1' and must be programmed as '1').

2: Reserved bits read as '1' and must be programmed as '1'.

The FGS<2> bit is a read-only copy of the GCP bit (FGS<1>).

TABLE 20-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARAC        | TERISTICS                   |       | (unless oth | Standard Operating Conditions: 2.5V to 5.5V  (unless otherwise stated)  Operating temperature -40°C ≤TA ≤+85°C for Industrial -40°C ≤TA ≤+125°C for Extended |            |                |  |  |  |  |  |

|------------------|-----------------------------|-------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------|--|--|--|--|--|

| Parameter<br>No. | Typical <sup>(1)</sup>      | Max   | Units       |                                                                                                                                                              | Conditions |                |  |  |  |  |  |

| Operating Cu     | ırrent (IDD) <sup>(2)</sup> |       |             |                                                                                                                                                              |            |                |  |  |  |  |  |

| DC31a            | 1.6                         | 3.0   | mA          | 25°C                                                                                                                                                         |            |                |  |  |  |  |  |

| DC31b            | 1.6                         | 3.0   | mA          | 85°C                                                                                                                                                         | 3.3V       |                |  |  |  |  |  |

| DC31c            | 1.6                         | 3.0   | mA          | 125°C                                                                                                                                                        | 1          | 0.128 MIPS     |  |  |  |  |  |

| DC31e            | 3.6                         | 6.0   | mA          | 25°C                                                                                                                                                         |            | LPRC (512 kHz) |  |  |  |  |  |

| DC31f            | 3.3                         | 6.0   | mA          | 85°C                                                                                                                                                         | 5V         |                |  |  |  |  |  |

| DC31g            | 3.2                         | 6.0   | mA          | 125°C                                                                                                                                                        | 1          |                |  |  |  |  |  |

| DC30a            | 3.0                         | 5.0   | mA          | 25°C                                                                                                                                                         |            |                |  |  |  |  |  |

| DC30b            | 3.0                         | 5.0   | mA          | 85°C                                                                                                                                                         | 3.3V       |                |  |  |  |  |  |

| DC30c            | 3.1                         | 5.0   | mA          | 125°C                                                                                                                                                        | 1          | (1.8 MIPS)     |  |  |  |  |  |

| DC30e            | 6.0                         | 9.0   | mA          | 25°C                                                                                                                                                         |            | FRC (7.37 MHz) |  |  |  |  |  |

| DC30f            | 5.8                         | 9.0   | mA          | 85°C                                                                                                                                                         | 5V         |                |  |  |  |  |  |

| DC30g            | 5.7                         | 9.0   | mA          | 125°C                                                                                                                                                        | 1          |                |  |  |  |  |  |

| DC23a            | 9.0                         | 15.0  | mA          | 25°C                                                                                                                                                         |            |                |  |  |  |  |  |

| DC23b            | 10.0                        | 15.0  | mA          | 85°C                                                                                                                                                         | 3.3V       |                |  |  |  |  |  |

| DC23c            | 10.0                        | 15.0  | mA          | 125°C                                                                                                                                                        | 1          | 4 MIDC         |  |  |  |  |  |

| DC23e            | 16.0                        | 24.0  | mA          | 25°C                                                                                                                                                         |            | 4 MIPS         |  |  |  |  |  |

| DC23f            | 16.0                        | 24.0  | mA          | 85°C                                                                                                                                                         | 5V         |                |  |  |  |  |  |

| DC23g            | 16.0                        | 24.0  | mA          | 125°C                                                                                                                                                        | 1          |                |  |  |  |  |  |

| DC24a            | 22.0                        | 33.0  | mA          | 25°C                                                                                                                                                         |            |                |  |  |  |  |  |

| DC24b            | 22.0                        | 33.0  | mA          | 85°C                                                                                                                                                         | 3.3V       |                |  |  |  |  |  |

| DC24c            | 22.0                        | 33.0  | mA          | 125°C                                                                                                                                                        | 1          | 40 MIDC        |  |  |  |  |  |

| DC24e            | 37.0                        | 56.0  | mA          | 25°C                                                                                                                                                         |            | 10 MIPS        |  |  |  |  |  |

| DC24f            | 37.0                        | 56.0  | mA          | 85°C                                                                                                                                                         | 5V         |                |  |  |  |  |  |

| DC24g            | 37.0                        | 56.0  | mA          | 125°C                                                                                                                                                        | 1          |                |  |  |  |  |  |

| DC27a            | 41.0                        | 60.0  | mA          | 25°C                                                                                                                                                         | 2.21/      |                |  |  |  |  |  |

| DC27b            | 40.0                        | 60.0  | mA          | 85°C                                                                                                                                                         | 3.3V       |                |  |  |  |  |  |

| DC27d            | 68.0                        | 90.0  | mA          | 25°C                                                                                                                                                         |            | 20 MIPS        |  |  |  |  |  |

| DC27e            | 67.0                        | 90.0  | mA          | 85°C                                                                                                                                                         | 5V         |                |  |  |  |  |  |

| DC27f            | 66.0                        | 90.0  | mA          | 125°C                                                                                                                                                        |            |                |  |  |  |  |  |

| DC29a            | 96.0                        | 140.0 | mA          | 25°C                                                                                                                                                         | 5V         | 20 MIDS        |  |  |  |  |  |

| DC29b            | 94.0                        | 140.0 | mA          | 85°C                                                                                                                                                         | υν         | 30 MIPS        |  |  |  |  |  |

Note 1: Data in "Typical" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

<sup>2:</sup> The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption. The test conditions for all IDD measurements are as follows: OSC1 driven with external square wave from rail to rail. All I/O pins are configured as Inputs and pulled to VDD. MCLR = VDD, WDT, FSCM, LVD and BOR are disabled. CPU, SRAM, Program Memory and Data Memory are operational. No peripheral modules are operating.

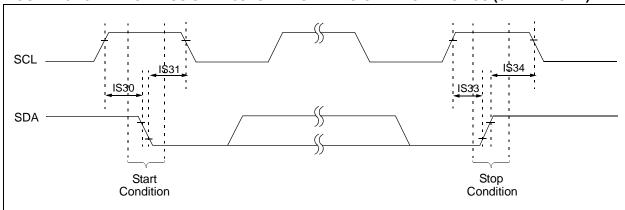

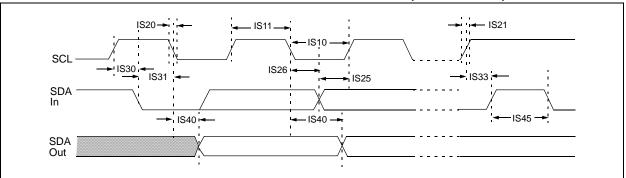

FIGURE 20-18: I<sup>2</sup>C™ BUS START/STOP BITS TIMING CHARACTERISTICS (SLAVE MODE)

FIGURE 20-19: I<sup>2</sup>C™ BUS DATA TIMING CHARACTERISTICS (SLAVE MODE)

TABLE 20-34: I<sup>2</sup>C™ BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

| AC CHARACTERISTICS | Standard Operating Conditions: 2.5V to 5.5V (unless otherwise stated) |  |  |  |  |  |  |

|--------------------|-----------------------------------------------------------------------|--|--|--|--|--|--|

| AC CHARACTERISTICS | Operating temperature -40°C ≤TA ≤+85°C for Industrial                 |  |  |  |  |  |  |

|                    | -40°C ≤TA ≤+125°C for Extended                                        |  |  |  |  |  |  |

| Param<br>No. | Symbol  | Charac          | teristic                  | Min         | Max  | Units | Conditions                                  |

|--------------|---------|-----------------|---------------------------|-------------|------|-------|---------------------------------------------|

| IS10         | TLO:SCL | Clock Low Time  | 100 kHz mode              | 4.7         | _    | μs    | Device must operate at a minimum of 1.5 MHz |

|              |         |                 | 400 kHz mode              | 1.3         | _    | μs    | Device must operate at a minimum of 10 MHz. |

|              |         |                 | 1 MHz mode <sup>(1)</sup> | 0.5         |      | μs    |                                             |

| IS11         | THI:SCL | Clock High Time | 100 kHz mode              | 4.0         | _    | μs    | Device must operate at a minimum of 1.5 MHz |

|              |         |                 | 400 kHz mode              | 0.6         | _    | μs    | Device must operate at a minimum of 10 MHz  |

|              |         |                 | 1 MHz mode <sup>(1)</sup> | 0.5         | _    | μs    |                                             |

| IS20         | TF:SCL  | SDA and SCL     | 100 kHz mode              | _           | 300  | ns    | CB is specified to be from                  |

|              |         | Fall Time       | 400 kHz mode              | 20 + 0.1 CB | 300  | ns    | 10 to 400 pF                                |

|              |         |                 | 1 MHz mode <sup>(1)</sup> | _           | 100  | ns    |                                             |

| IS21         | TR:SCL  | SDA and SCL     | 100 kHz mode              | _           | 1000 | ns    | CB is specified to be from                  |

|              |         | Rise Time       | 400 kHz mode              | 20 + 0.1 CB | 300  | ns    | 10 to 400 pF                                |

|              |         |                 | 1 MHz mode <sup>(1)</sup> | _           | 300  | ns    |                                             |

**Note 1:** Maximum pin capacitance = 10 pF for all  $I^2C^{TM}$  pins (for 1 MHz mode only).

### 21.2 Package Marking Information (Continued)

28-Lead SOIC

Example

28-Lead QFN-S

Example

44-Lead QFN

Example

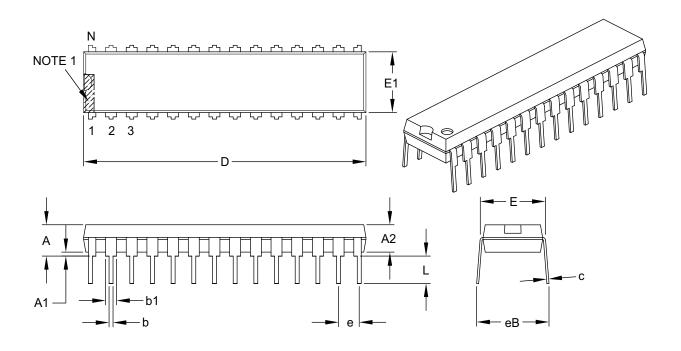

### 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    | INCHES |          |       |  |  |

|----------------------------|----------|--------|----------|-------|--|--|

| Dimensio                   | n Limits | MIN    | NOM      | MAX   |  |  |

| Number of Pins             | N        |        | 28       |       |  |  |

| Pitch                      | е        |        | .100 BSC |       |  |  |

| Top to Seating Plane       | Α        | _      | -        | .200  |  |  |

| Molded Package Thickness   | A2       | .120   | .135     | .150  |  |  |

| Base to Seating Plane      | A1       | .015   | -        | _     |  |  |

| Shoulder to Shoulder Width | Е        | .290   | .310     | .335  |  |  |

| Molded Package Width       | E1       | .240   | .285     | .295  |  |  |

| Overall Length             | D        | 1.345  | 1.365    | 1.400 |  |  |

| Tip to Seating Plane       | L        | .110   | .130     | .150  |  |  |

| Lead Thickness             | С        | .008   | .010     | .015  |  |  |

| Upper Lead Width           | b1       | .040   | .050     | .070  |  |  |

| Lower Lead Width           | b        | .014   | .018     | .022  |  |  |

| Overall Row Spacing §      | eВ       | _      | _        | .430  |  |  |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

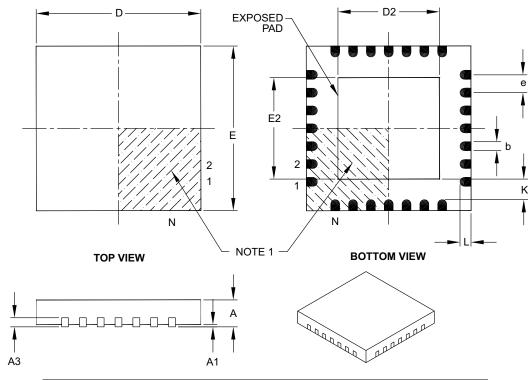

## 28-Lead Plastic Quad Flat, No Lead Package (MM) – 6x6x0.9 mm Body [QFN-S] with 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units    |      | MILLIMETERS | 3    |

|------------------------|----------|------|-------------|------|

| Dimension              | n Limits | MIN  | NOM         | MAX  |

| Number of Pins         | N        |      | 28          |      |

| Pitch                  | е        |      | 0.65 BSC    |      |

| Overall Height         | Α        | 0.80 | 0.90        | 1.00 |

| Standoff               | A1       | 0.00 | 0.02        | 0.05 |

| Contact Thickness      | А3       |      | 0.20 REF    |      |

| Overall Width          | Е        |      | 6.00 BSC    |      |

| Exposed Pad Width      | E2       | 3.65 | 3.70        | 4.70 |

| Overall Length         | D        |      | 6.00 BSC    |      |

| Exposed Pad Length     | D2       | 3.65 | 3.70        | 4.70 |

| Contact Width          | b        | 0.23 | 0.38        | 0.43 |

| Contact Length         | L        | 0.30 | 0.40        | 0.50 |

| Contact-to-Exposed Pad | K        | 0.20 | _           | _    |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-124B

### APPENDIX A: REVISION HISTORY

### **Revision D (August 2006)**

Previous versions of this data sheet contained Advance or Preliminary Information. They were distributed with incomplete characterization data.

This revision reflects these updates:

- Supported I<sup>2</sup>C Slave Addresses (see Table 14-1)

- ADC Conversion Clock selection to allow 200 kHz sampling rate (see Section 16.0 "12-bit Analog-to-Digital Converter (ADC) Module")

- Operating Current (IDD) Specifications (see Table 20-5)

- Idle Current (IIDLE) Specifications (see Table 20-6)

- Power-Down Current (IPD) Specifications (see Table 20-7)

- I/O pin Input Specifications (see Table 20-8)

- BOR voltage limits (see Table 20-11)

- Watchdog Timer time-out limits (see Table 20-21)

### **Revision E (December 2006)**

This revision includes updates to the packaging diagrams.

### Revision F (May 2008)

This revision reflects these updates:

- Added FUSE Configuration Register (FICD) details (see Section 17.7 "Device Configuration Registers" and Table 17-8)

- Added Note 2 to Device Configuration Registers table (Table 17-8)

- Updated Bit 10 in the UART2 Register Map (see Table 15-2). This bit is unimplemented.

- Electrical Specifications:

- Resolved TBD values for parameters DO10, DO16, DO20, and DO26 (see Table 20-9)

- 10-bit High-Speed ADC tPDU timing parameter (time to stabilize) has been updated from 20 μs typical to 20 μs maximum (see Table 20-37)

- Parameter OS65 (Internal RC Accuracy) has been expanded to reflect multiple Min and Max values for different temperatures (see Table 20-19)

- Parameter DC12 (RAM Data Retention Voltage) has been updated to include a Min value (see Table 20-4)

- Parameter D134 (Erase/Write Cycle Time)

has been updated to include Min and Max

values and the Typ value has been removed

(see Table 20-12)

- Removed parameters OS62 (Internal FRC Jitter) and OS64 (Internal FRC Drift) and Note 2 from AC Characteristics (see Table 20-18)

- Parameter OS63 (Internal FRC Accuracy) has been expanded to reflect multiple Min and Max values for different temperatures (see Table 20-18)

- Updated Min and Max values and Conditions for parameter SY11 and updated Min, Typ, and Max values and Conditions for parameter SY20 (see Table 20-21)

- Additional minor corrections throughout the document

| Trap Lockout67                                                   | Register Map                               | 75  |

|------------------------------------------------------------------|--------------------------------------------|-----|

| Uninitialized W Register Trap67                                  | Timer2 and Timer3 Selection Mode           |     |

| Watchdog Time-out                                                | Timer2/3 Module                            | 00  |

| Reset Timing Characteristics                                     | 16-bit Timer Mode                          | 77  |

| Reset Timing Granacteristics                                     | 32-bit Synchronous Counter Mode            |     |

| Run-Time Self-Programming (RTSP)                                 | 32-bit Timer Mode                          |     |

| Kull-Tillie Sell-Flogramming (KTSF)49                            | ADC Event Trigger                          |     |

| \$                                                               |                                            |     |

| Simple Capture Event Mode83                                      | Gate Operation                             |     |

| ·                                                                | Interrupt                                  |     |

| Buffer Operation84                                               | Operation During Sleep Mode                |     |

| Hall Sensor Mode84                                               | Register Map                               |     |

| Prescaler                                                        | Timer Prescaler                            | 80  |

| Timer2 and Timer3 Selection Mode                                 | Timing Characteristics                     |     |

| Simple OC/PWM Mode Timing Requirements171                        | A/D Conversion                             |     |

| Simple Output Compare Match Mode                                 | Low-speed (ASAM = 0, SSRC = 000)           |     |

| Simple PWM Mode                                                  | Bandgap Start-up Time                      |     |

| Input Pin Fault Protection88                                     | CAN Module I/O                             |     |

| Period89                                                         | CLKOUT and I/O                             | 164 |

| Software Simulator (MPLAB SIM)147                                | External Clock                             | 160 |

| Software Stack Pointer, Frame Pointer20                          | I <sup>2</sup> C Bus Data                  |     |

| CALL Stack Frame39                                               | Master Mode                                | 177 |

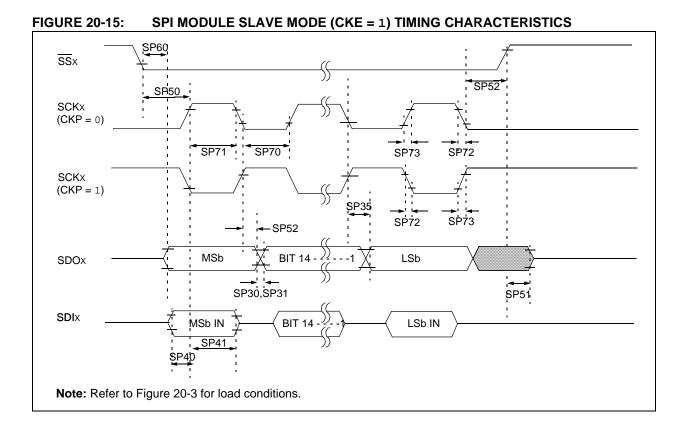

| SPI Module93                                                     | Slave Mode                                 | 179 |

| Framed SPI Support94                                             | I <sup>2</sup> C Bus Start/Stop Bits       |     |

| Operating Function Description93                                 | Master Mode                                | 177 |

| Operation During CPU Idle Mode95                                 | Slave Mode                                 | 179 |

| Operation During CPU Sleep Mode95                                | Input Capture (CAPX)                       | 169 |

| SDOx Disable94                                                   | OC/PWM Module                              |     |

| Slave Select Synchronization95                                   | Oscillator Start-up Timer                  |     |

| SPI1 Register Map96                                              | Output Compare Module                      |     |

| Timing Characteristics                                           | Power-up Timer                             |     |

| Master Mode (CKE = 0) 172                                        | Reset                                      |     |

| Master Mode (CKE = 1) 173                                        | SPI Module                                 |     |

| Slave Mode (CKE = 1) 174, 175                                    | Master Mode (CKE = 0)                      | 172 |

| Timing Requirements                                              | Master Mode (CKE = 1)                      |     |

| Master Mode (CKE = 0)172                                         | Slave Mode (CKE = 0)                       |     |

| Master Mode (CKE = 1)                                            | Slave Mode (CKE = 1)                       |     |

| Slave Mode (CKE = 0)                                             | Type A, B and C Timer External Clock       |     |

| Slave Mode (CKE = 1)                                             | Watchdog Timer                             |     |

| Word and Byte Communication94                                    | Timing Diagrams                            | 100 |

| Status Bits, Their Significance and the Initialization Condition | 0 0                                        | 00  |

| for                                                              | PWM Output Timing                          | 89  |

|                                                                  | Time-out Sequence on Power-up              | 400 |

| RCON Register, Case 1                                            | (MCLR Not Tied to VDD), Case 1             | 130 |

| Status Bits, Their Significance and the Initialization Condition | Time-out Sequence on Power-up              |     |

| for RCON Register, Case 2                                        | (MCLR                                      |     |

| Status Register                                                  | Not Tied to VDD), Case 2                   | 130 |

| Symbols Used in Opcode Descriptions                              | Time-out Sequence on Power-up              |     |

| System Integration                                               | (MCLR                                      |     |

| Register Map136                                                  | Tied to VDD)                               | 130 |

| Т                                                                | Timing Diagrams and Specifications         |     |

|                                                                  | DC Characteristics - Internal RC Accuracy  | 163 |

| Table Instruction Operation Summary49                            | Timing Diagrams.See Timing Characteristics |     |

| Temperature and Voltage Specifications                           | Timing Requirements                        |     |

| AC160                                                            | A/D Conversion                             |     |

| DC150                                                            | Low-speed                                  | 185 |

| Timer 2/3 Module77                                               | Bandgap Start-up Time                      | 166 |

| Timer1 Module73                                                  | Brown-out Reset                            |     |

| 16-bit Asynchronous Counter Mode73                               | CAN Module I/O                             |     |

| 16-bit Synchronous Counter Mode73                                | CLKOUT and I/O                             |     |

| 16-bit Timer Mode73                                              | External Clock                             |     |

| Gate Operation74                                                 | I <sup>2</sup> C Bus Data (Master Mode)    |     |

| Interrupt74                                                      | I <sup>2</sup> C Bus Data (Slave Mode)     |     |

| Operation During Sleep Mode74                                    | Input Capture                              |     |

| Prescaler                                                        |                                            |     |

| Real-Time Clock                                                  | Oscillator Start-up Timer                  |     |

| Interrupts74                                                     | Output Compare Module                      |     |

| Oscillator Operation                                             | Power-up Timer                             | 165 |

|                                                                  |                                            |     |

### Worldwide Sales and Service

#### **AMERICAS**

**Corporate Office**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://support.microchip.com

Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca. IL

Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

Dallas

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit

Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo

Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara

Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto

Mississauga, Ontario,

Canada Tel: 905-673-0699

Fax: 905-673-6509

#### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2401-1200

Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733

Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

China - Chengdu

Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing

Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Hong Kong SAR

Tel: 852-2401-1200 Fax: 852-2401-3431

China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai

Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang

Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen

Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

China - Wuhan

Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xian

Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

China - Zhuhai Tel: 86-756-3210040

Fax: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore

Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

Japan - Yokohama

Tel: 81-45-471- 6166 Fax: 81-45-471-6122

Korea - Daegu

Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul

Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang

Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065

Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu

Tel: 886-3-6578-300 Fax: 886-3-6578-370

Taiwan - Kaohsiung

Tel: 886-7-213-7830 Fax: 886-7-330-9305

Taiwan - Taipei

Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

Thailand - Bangkok

Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Munich

Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen

Tel: 31-416-690399 Fax: 31-416-690340

Spain - Madrid

Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

08/04/10