Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | dsPIC                                                                          |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 30 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                          |

| Number of I/O              | 20                                                                             |

| Program Memory Size        | 24KB (8K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 1K x 8                                                                         |

| RAM Size                   | 2K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                    |

| Data Converters            | A/D 10x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f3013t-30i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

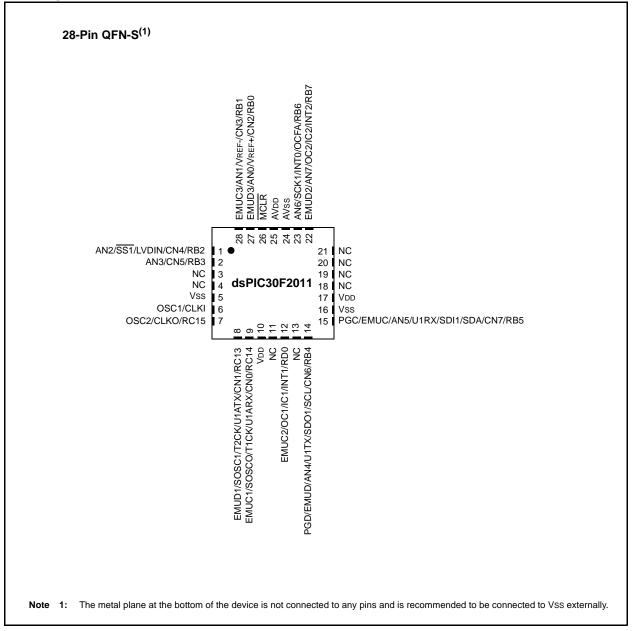

## **Pin Diagrams**

## 2.3 Divide Support

The dsPIC DSC devices feature a 16/16-bit signed fractional divide operation, as well as 32/16-bit and 16/16-bit signed and unsigned integer divide operations, in the form of single instruction iterative divides. The following instructions and data sizes are supported:

- 1. DIVF 16/16 signed fractional divide

- 2. DIV.sd 32/16 signed divide

- 3. DIV.ud 32/16 unsigned divide

- 4. DIV.s 16/16 signed divide

- 5. DIV.u 16/16 unsigned divide

The 16/16 divides are similar to the 32/16 (same number of iterations), but the dividend is either zero-extended or sign-extended during the first iteration.

The divide instructions must be executed within a REPEAT loop. Any other form of execution (e.g., a series of discrete divide instructions) will not function correctly because the instruction flow depends on RCOUNT. The divide instruction does not automatically set up the RCOUNT value and it must, therefore, be explicitly and correctly specified in the REPEAT instruction, as shown in Table 2-1 (REPEAT executes the target instruction {operand value+1} times). The REPEAT loop count must be setup for 18 iterations of the DIV/DIVF instruction. Thus, a complete divide operation requires 19 cycles.

**Note:** The divide flow is interruptible; however, the user needs to save the context as appropriate.

#### TABLE 2-1: DIVIDE INSTRUCTIONS

| Instruction | Function                                                               |

|-------------|------------------------------------------------------------------------|

| DIVF        | Signed fractional divide: Wm/Wn $\rightarrow$ W0; Rem $\rightarrow$ W1 |

| DIV.sd      | Signed divide: (Wm+1:Wm)/Wn $\rightarrow$ W0; Rem $\rightarrow$ W1     |

| DIV.s       | Signed divide: Wm/Wn $\rightarrow$ W0; Rem $\rightarrow$ W1            |

| DIV.ud      | Unsigned divide: (Wm+1:Wm)/Wn $\rightarrow$ W0; Rem $\rightarrow$ W1   |

| DIV.u       | Unsigned divide: Wm/Wn $\rightarrow$ W0; Rem $\rightarrow$ W1          |

#### 2.4.2.4 Data Space Write Saturation

In addition to adder/subtracter saturation, writes to data space may also be saturated but without affecting the contents of the source accumulator. The data space write saturation logic block accepts a 16-bit, 1.15 fractional value from the round logic block as its input, together with overflow status from the original source (accumulator) and the 16-bit round adder. These are combined and used to select the appropriate 1.15 fractional value as output to write to data space memory.

If the SATDW bit in the CORCON register is set, data (after rounding or truncation) is tested for overflow and adjusted accordingly. For input data greater than 0x007FFF, data written to memory is forced to the maximum positive 1.15 value, 0x7FFF. For input data less than 0xFF8000, data written to memory is forced to the maximum negative 1.15 value, 0x8000. The MSb of the source (bit 39) is used to determine the sign of the operand being tested.

If the SATDW bit in the CORCON register is not set, the input data is always passed through unmodified under all conditions.

#### 2.4.3 BARREL SHIFTER

The barrel shifter is capable of performing up to 16-bit arithmetic or logic right shifts, or up to 16-bit left shifts in a single cycle. The source can be either of the two DSP accumulators, or the X bus (to support multi-bit shifts of register or memory data).

The shifter requires a signed binary value to determine both the magnitude (number of bits) and direction of the shift operation. A positive value shifts the operand right. A negative value shifts the operand left. A value of '0' does not modify the operand.

The barrel shifter is 40 bits wide, thereby obtaining a 40-bit result for DSP shift operations and a 16-bit result for MCU shift operations. Data from the X bus is presented to the barrel shifter between bit positions 16 to 31 for right shifts, and bit positions 0 to 16 for left shifts.

NOTES:

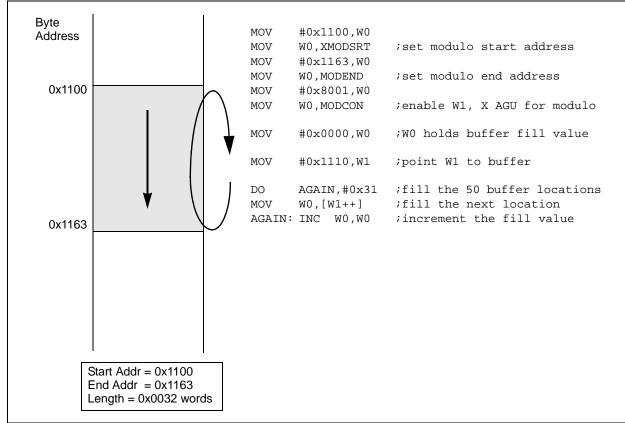

#### 4.2.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and an ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 3-3).

| Note: | Υ                                  | space | Modulo | Addressing | EA   |  |  |  |  |

|-------|------------------------------------|-------|--------|------------|------|--|--|--|--|

|       | calculations                       |       | assume | word-sized | data |  |  |  |  |

|       | (LSb of every EA is always clear). |       |        |            |      |  |  |  |  |

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding Start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

#### 4.2.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W address registers. The XWM and YWM fields select which registers operate with Modulo Addressing. If XWM = 15, X RAGU and X WAGU Modulo Addressing is disabled. Similarly, if YWM = 15, Y AGU Modulo Addressing is disabled.

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 3-3). Modulo Addressing is enabled for X data space when XWM is set to any value other than '15' and the XMODEN bit is set at MODCON<15>.

The Y Address Space Pointer W register (YWM), to which Modulo Addressing is to be applied, is stored in MODCON<7:4>. Modulo Addressing is enabled for Y data space when YWM is set to any value other than '15' and the YMODEN bit is set at MODCON<14>.

### FIGURE 4-1: MODULO ADDRESSING OPERATION EXAMPLE

NOTES:

#### EXAMPLE 6-5: DATA EEPROM BLOCK WRITE

| MOV        | <pre>#LOW_ADDR_WORD,W0</pre>       | ; | Init pointer                                                     |

|------------|------------------------------------|---|------------------------------------------------------------------|

| MOV        | #HIGH_ADDR_WORD,W1                 |   |                                                                  |

| MOV        | W1,TBLPAG                          |   |                                                                  |

| MOV        | #data1,W2                          | ; | Get 1st data                                                     |

| TBLWTL     | W2 [ W0]++                         | ; | write data                                                       |

| MOV        | #data2,W2                          | ; | Get 2nd data                                                     |

| TBLWTL     | W2,[ W0]++                         | ; | write data                                                       |

| MOV        | #data3,W2                          | ; | Get 3rd data                                                     |

| TBLWTL     | W2,[ W0]++                         | ; | write data                                                       |

| MOV        | #data4,W2                          | ; | Get 4th data                                                     |

| TBLWTL     | W2,[ W0]++                         | ; | write data                                                       |

| MOV        | #data5,W2                          | ; | Get 5th data                                                     |

| TBLWTL     | W2,[ W0]++                         | ; | write data                                                       |

| MOV        | #data6,W2                          | ; | Get 6th data                                                     |

| TBLWTL     | W2,[ W0]++                         | ; | write data                                                       |

| MOV        | #data7,W2                          |   | Get 7th data                                                     |

| TBLWTL     | W2,[ W0]++                         |   | write data                                                       |

| MOV        | #data8,W2                          |   | Get 8th data                                                     |

| TBLWTL     | W2,[ W0]++                         |   | write data                                                       |

| MOV        | #data9,W2                          |   | Get 9th data                                                     |

| TBLWTL     | W2,[ W0]++                         |   | write data                                                       |

| MOV        | #data10,W2                         |   | Get 10th data                                                    |

| TBLWTL     | W2,[ W0]++                         |   | write data                                                       |

| MOV        | #data11,W2                         |   | Get 11th data                                                    |

| TBLWTL     | W2,[ W0]++                         |   | write data                                                       |

| MOV        | #data12,W2                         |   | Get 12th data                                                    |

| TBLWTL     | W2,[ W0]++                         |   | write data                                                       |

| MOV        | #data13,W2                         |   | Get 13th data                                                    |

| TBLWTL     | W2 [ W0]++                         |   | write data                                                       |

| MOV        | #data14,W2                         |   | Get 14th data                                                    |

| TBLWTL     | W2 [ W0]++                         |   | write data                                                       |

| MOV        | #data15,W2                         |   | Get 15th data                                                    |

| TBLWTL     | W2 [ W0]++                         |   | write data                                                       |

| MOV        | #data16,W2                         |   | Get 16th data                                                    |

| TBLWTL     | W2 [ W0]++                         |   | write data. The NVMADR captures last table access address.       |

| MOV        | #0x400A,W0                         |   | Select data EEPROM for multi word op                             |

| MOV        | W0,NVMCON<br>#5                    |   | Operate Key to allow program operation                           |

| DISI       | # 5                                |   | Block all interrupts with priority <7 for<br>next 5 instructions |

| MOV        | #0x55,W0                           | ' | liext 5 filstructions                                            |

|            |                                    |   | Write the Over key                                               |

| MOV<br>MOV | W0 <sub>,</sub> NVMKEY<br>#0xAA,W1 | ' | Write the 0x55 key                                               |

| MOV        |                                    |   | Write the 0xAA key                                               |

| BSET       | W1,NVMKEY<br>NVMCON,#WR            |   | Start write cycle                                                |

| NOP        | TAALICOTA / WAIL                   | ' | Deale wille Cycle                                                |

| NOP        |                                    |   |                                                                  |

| INCE       |                                    |   |                                                                  |

|            |                                    |   |                                                                  |

#### 6.4 Write Verify

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

## 6.5 Protection Against Spurious Write

There are conditions when the device may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been built-in. On power-up, the WREN bit is cleared; also, the Power-up Timer prevents EEPROM write.

The write initiate sequence and the WREN bit together help prevent an accidental write during brown-out, power glitch, or software malfunction.

## 7.3 Input Change Notification Module

The input change notification module provides the dsPIC30F devices the ability to generate interrupt requests to the processor, in response to a change of state on selected input pins. This module is capable of detecting input change of states even in Sleep mode, when the clocks are disabled. There are up to 10 external signals (CN0 through CN7, CN17 and CN18) that may be selected (enabled) for generating an interrupt request on a change of state.

#### TABLE 7-7:INPUT CHANGE NOTIFICATION REGISTER MAP FOR dsPIC30F2011/3012 (BITS 7-0)

| SFR<br>Name | Address | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset State         |

|-------------|---------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| CNEN1       | 00C0    | CN7IE  | CN6IE  | CN5IE  | CN4IE  | CN3IE  | CN2IE  | CN1IE  | CN0IE  | 0000 0000 0000 0000 |

| CNEN2       | 00C2    | _      | _      | _      | _      | _      | _      | _      | _      | 0000 0000 0000 0000 |

| CNPU1       | 00C4    | CN7PUE | CN6PUE | CN5PUE | CN4PUE | CN3PUE | CN2PUE | CN1PUE | CN0PUE | 0000 0000 0000 0000 |

| CNPU2       | 00C6    | _      |        |        |        | —      | —      |        |        | 0000 0000 0000 0000 |

Legend: — = unimplemented bit, read as '0'

#### TABLE 7-8: INPUT CHANGE NOTIFICATION REGISTER MAP FOR dsPIC30F2012/3013 (BITS 7-0)

| SFR<br>Name | Address | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3         | Bit 2   | Bit 1   | Bit 0  | Reset State         |

|-------------|---------|--------|--------|--------|--------|---------------|---------|---------|--------|---------------------|

| CNEN1       | 00C0    | CN7IE  | CN6IE  | CN5IE  | CN4IE  | CN3IE         | CN2IE   | CN1IE   | CN0IE  | 0000 0000 0000 0000 |

| CNEN2       | 00C2    | _      | _      | _      | _      | _             | CN18IE  | CN17IE  | _      | 0000 0000 0000 0000 |

| CNPU1       | 00C4    | CN7PUE | CN6PUE | CN5PUE | CN4PUE | <b>CN3PUE</b> | CN2PUE  | CN1PUE  | CN0PUE | 0000 0000 0000 0000 |

| CNPU2       | 00C6    | _      |        |        |        |               | CN18PUE | CN17PUE | -      | 0000 0000 0000 0000 |

Legend: — = unimplemented bit, read as '0'

Note: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

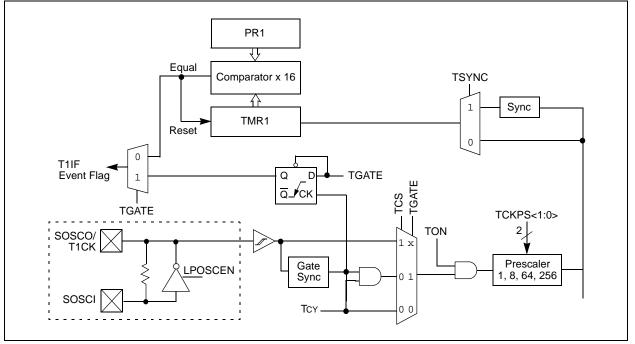

## 9.0 TIMER1 MODULE

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

This section describes the 16-bit general purpose Timer1 module and associated operational modes. Figure 9-1 depicts the simplified block diagram of the 16-bit Timer1 module. The following sections provide detailed descriptions including setup and Control registers, along with associated block diagrams for the operational modes of the timers.

The Timer1 module is a 16-bit timer that serves as the time counter for the real-time clock or operates as a free-running interval timer/counter. The 16-bit timer has the following modes:

- 16-bit Timer

- 16-bit Synchronous Counter

- 16-bit Asynchronous Counter

These operational characteristics are supported:

- Timer gate operation

- Selectable prescaler settings

- Timer operation during CPU Idle and Sleep modes

- Interrupt on 16-bit Period register match or falling edge of external gate signal

These operating modes are determined by setting the appropriate bit(s) in the 16-bit SFR, T1CON. Figure 9-1 presents a block diagram of the 16-bit timer module.

**16-bit Timer Mode:** In the 16-bit Timer mode, the timer increments on every instruction cycle up to a match value preloaded into the Period register PR1, then resets to '0' and continues to count.

When the CPU goes into the Idle mode, the timer stops incrementing unless the TSIDL (T1CON<13>) bit = 0. If TSIDL = 1, the timer module logic resumes the incrementing sequence on termination of CPU Idle mode.

**16-bit Synchronous Counter Mode:** In the 16-bit Synchronous Counter mode, the timer increments on the rising edge of the applied external clock signal which is synchronized with the internal phase clocks. The timer counts up to a match value preloaded in PR1, then resets to '0' and continues.

When the CPU goes into the Idle mode, the timer stops incrementing unless the respective TSIDL bit = 0. If TSIDL = 1, the timer module logic resumes the incrementing sequence upon termination of the CPU Idle mode.

**16-bit Asynchronous Counter Mode:** In the 16-bit Asynchronous Counter mode, the timer increments on every rising edge of the applied external clock signal. The timer counts up to a match value preloaded in PR1, then resets to '0' and continues.

When the timer is configured for the Asynchronous mode of operation and the CPU goes into the Idle mode, the timer stops incrementing if TSIDL = 1.

## 9.1 Timer Gate Operation

The 16-bit timer can be placed in the Gated Time Accumulation mode. This mode allows the internal TCY to increment the respective timer when the gate input signal (T1CK pin) is asserted high. Control bit, TGATE (T1CON<6>), must be set to enable this mode. The timer must be enabled (TON = 1) and the timer clock source set to internal (TCS = 0).

When the CPU goes into Idle mode, the timer stops incrementing unless TSIDL = 0. If TSIDL = 1, the timer resumes the incrementing sequence upon termination of the CPU Idle mode.

## 9.2 Timer Prescaler

The input clock (FOSC/4 or external clock) to the 16-bit Timer has a prescale option of 1:1, 1:8, 1:64 and 1:256, selected by control bits, TCKPS<1:0> (T1CON<5:4>). The prescaler counter is cleared when any of the following occurs:

- A write to the TMR1 register

- A write to the T1CON register

- A device Reset, such as a POR and BOR

However, if the timer is disabled (TON = 0), then the timer prescaler cannot be reset since the prescaler clock is halted.

The TMR1 register is not cleared when the T1CON register is written. It is cleared by writing to the TMR1 register.

## 9.3 Timer Operation During Sleep Mode

The timer operates during CPU Sleep mode, if:

- The timer module is enabled (TON = 1), and

- The timer clock source is selected as external (TCS = 1), and

- The TSYNC bit (T1CON<2>) is asserted to a logic '0' which defines the external clock source as asynchronous.

When all three conditions are true, the timer continues to count up to the Period register and be reset to 0x0000.

When a match between the timer and the Period register occurs, an interrupt can be generated if the respective timer interrupt enable bit is asserted.

## 9.4 Timer Interrupt

The 16-bit timer has the ability to generate an interrupt-on-period match. When the timer count matches the Period register, the T1IF bit is asserted and an interrupt is generated, if enabled. The T1IF bit must be cleared in software. The timer interrupt flag, T1IF, is located in the IFS0 Control register in the interrupt controller.

When the Gated Time Accumulation mode is enabled, an interrupt is also generated on the falling edge of the gate signal (at the end of the accumulation cycle).

Enabling an interrupt is accomplished via the respective timer interrupt enable bit, T1IE. The timer interrupt enable bit is located in the IEC0 Control register in the interrupt controller.

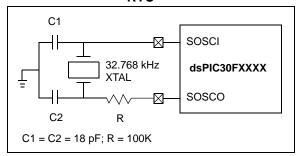

## 9.5 Real-Time Clock

Timer1, when operating in Real-Time Clock (RTC) mode, provides time of day and event time-stamping capabilities. Key operational features of the RTC are:

- Operation from 32 kHz LP oscillator

- 8-bit prescaler

- Low power

- Real-Time Clock interrupts

These operating modes are determined by setting the appropriate bit(s) in the T1CON register.

FIGURE 9-2:

#### RECOMMENDED COMPONENTS FOR TIMER1 LP OSCILLATOR RTC

## 9.5.1 RTC OSCILLATOR OPERATION

When the TON = 1, TCS = 1 and TGATE = 0, the timer increments on the rising edge of the 32 kHz LP oscillator output signal, up to the value specified in the Period register and is then reset to '0'.

The TSYNC bit must be asserted to a logic '0' (Asynchronous mode) for correct operation.

Enabling the LPOSCEN bit (OSCCON<1>) disables the normal Timer and Counter modes and enables a timer carry-out wake-up event.

When the CPU enters Sleep mode, the RTC continues to operate, provided the 32 kHz external crystal oscillator is active and the control bits have not been changed. The TSIDL bit should be cleared to '0' in order for RTC to continue operation in Idle mode.

## 9.5.2 RTC INTERRUPTS

When an interrupt event occurs, the respective interrupt flag, T1IF, is asserted and an interrupt is generated if enabled. The T1IF bit must be cleared in software. The respective Timer interrupt flag, T1IF, is located in the IFS0 register in the interrupt controller.

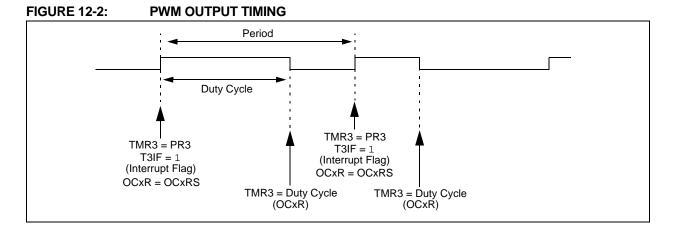

### 12.4.2 PWM PERIOD

The PWM period is specified by writing to the PRx register. The PWM period can be calculated using Equation 12-1.

#### EQUATION 12-1:

$PWM \ period = [(PRx) + 1] \cdot 4 \cdot Tosc \cdot$  $(TMRx \ prescale \ value)$

PWM frequency is defined as 1/[PWM period].

When the selected TMRx is equal to its respective period register, PRx, the following four events occur on the next increment cycle:

- TMRx is cleared.

- The OCx pin is set.

- Exception 1: If PWM duty cycle is 0x0000, the OCx pin remains low.

- Exception 2: If duty cycle is greater than PRx, the pin remains high.

- The PWM duty cycle is latched from OCxRS into OCxR.

- The corresponding timer interrupt flag is set.

See Figure 12-2 for key PWM period comparisons. Timer3 is referred to in Figure 12-2 for clarity.

#### 14.4.1 10-BIT MODE SLAVE TRANSMISSION

Once a slave is addressed in this fashion with the full 10-bit address (we will refer to this state as "PRIOR\_ADDR\_MATCH"), the master can begin sending data bytes for a slave reception operation.

14.4.2 10-BIT MODE SLAVE RECEPTION

Once addressed, the master can generate a Repeated Start, reset the high byte of the address and set the R\_W bit without generating a Stop bit, thus initiating a slave transmit operation.

## 14.5 Automatic Clock Stretch

In the Slave modes, the module can synchronize buffer reads and write to the master device by clock stretching.

### 14.5.1 TRANSMIT CLOCK STRETCHING

Both 10-bit and 7-bit Transmit modes implement clock stretching by asserting the SCLREL bit after the falling edge of the ninth clock, if the TBF bit is cleared, indicating the buffer is empty.

In Slave Transmit modes, clock stretching is always performed irrespective of the STREN bit.

Clock synchronization takes place following the ninth clock of the transmit sequence. If the device samples an ACK on the falling edge of the ninth clock and if the TBF bit is still clear, then the SCLREL bit is automatically cleared. The SCLREL being cleared to '0' will assert the SCL line low. The user's ISR must set the SCLREL bit before transmission is allowed to continue. By holding the SCL line low, the user has time to service the ISR and load the contents of the I2CTRN before the master device can initiate another transmit sequence.

- Note 1: If the user loads the contents of I2CTRN, setting the TBF bit before the falling edge of the ninth clock, the SCLREL bit will not be cleared and clock stretching will not occur.

- **2:** The SCLREL bit can be set in software, regardless of the state of the TBF bit.

## 14.5.2 RECEIVE CLOCK STRETCHING

The STREN bit in the I2CCON register can be used to enable clock stretching in Slave Receive mode. When the STREN bit is set, the SCL pin will be held low at the end of each data receive sequence.

#### 14.5.3 CLOCK STRETCHING DURING 7-BIT ADDRESSING (STREN = 1)

When the STREN bit is set in Slave Receive mode, the SCL line is held low when the buffer register is full. The method for stretching the SCL output is the same for both 7 and 10-bit addressing modes.

Clock stretching takes place following the ninth clock of the receive sequence. <u>On</u> the falling edge of the ninth clock at the end of the ACK sequence, if the RBF bit is set, the SCLREL bit is automatically cleared, forcing the SCL output to be held low. The user's ISR must set the SCLREL bit before reception is allowed to continue. By holding the SCL line low, the user has time to service the ISR and read the contents of the I2CRCV before the master device can initiate another receive sequence. This will prevent buffer overruns from occurring.

| Note 1: | If the user reads the contents of the    |  |  |  |  |  |  |  |

|---------|------------------------------------------|--|--|--|--|--|--|--|

|         | I2CRCV, clearing the RBF bit before the  |  |  |  |  |  |  |  |

|         | falling edge of the ninth clock, the     |  |  |  |  |  |  |  |

|         | SCLREL bit will not be cleared and clock |  |  |  |  |  |  |  |

|         | stretching will not occur.               |  |  |  |  |  |  |  |

2: The SCLREL bit can be set in software regardless of the state of the RBF bit. The user should be careful to clear the RBF bit in the ISR before the next receive sequence in order to prevent an overflow condition.

### 14.5.4 CLOCK STRETCHING DURING 10-BIT ADDRESSING (STREN = 1)

Clock stretching takes place automatically during the addressing sequence. Because this module has a register for the entire address, it is not necessary for the protocol to wait for the address to be updated.

After the address phase is complete, clock stretching will occur on each data receive or transmit sequence as was described earlier.

## 14.6 Software Controlled Clock Stretching (STREN = 1)

When the STREN bit is '1', the SCLREL bit may be cleared by software to allow software to control the clock stretching. The logic will synchronize writes to the SCLREL bit with the SCL clock. Clearing the SCLREL bit will not assert the SCL output until the module detects a falling edge on the SCL output and SCL is sampled low. If the SCLREL bit is cleared by the user while the SCL line has been sampled low, the SCL output will be asserted (held low). The SCL output will remain low until the SCLREL bit is set, and all other devices on the I<sup>2</sup>C bus have de-asserted SCL. This ensures that a write to the SCLREL bit will not violate the minimum high time requirement for SCL.

If the STREN bit is '0', a software write to the SCLREL bit will be disregarded and have no effect on the SCLREL bit.

## 14.12.2 I<sup>2</sup>C MASTER RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (I2CCON<3>). The I<sup>2</sup>C module must be Idle before the RCEN bit is set, otherwise the RCEN bit will be disregarded. The Baud Rate Generator begins <u>counting</u> and on each rollover, the state of the SCL pin ACK and data are shifted into the I2CRSR on the rising edge of each clock.

#### 14.12.3 BAUD RATE GENERATOR

In I<sup>2</sup>C Master mode, the reload value for the BRG is located in the I2CBRG register. When the BRG is loaded with this value, the BRG counts down to '0' and stops until another reload has taken place. If clock arbitration is taking place, for instance, the BRG is reloaded when the SCL pin is sampled high.

As per the I<sup>2</sup>C standard, FSCK may be 100 kHz or 400 kHz. However, the user can specify any baud rate up to 1 MHz. I2CBRG values of '0' or '1' are illegal.

### EQUATION 14-1: SERIAL CLOCK RATE

$I2CBRG = \left(\frac{FCY}{FSCL} - \frac{FCY}{1,111,111}\right) - 1$

## 14.12.4 CLOCK ARBITRATION

Clock arbitration occurs when the master de-asserts the SCL pin (SCL allowed to float high) during any receive, transmit, or Restart/Stop condition. When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of I2CBRG and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device.

#### 14.12.5 MULTI-MASTER COMMUNICATION, BUS COLLISION, AND BUS ARBITRATION

Multi-master operation support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA by letting SDA float high while another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = 0, then a bus collision has taken place. The master will set the MI2CIF pulse and reset the master portion of the  $I^2C$  port to its Idle state.

If a transmit was in progress when the bus collision occurred, the transmission is halted, the TBF flag is cleared, the SDA and SCL lines are de-asserted and a value can now be written to I2CTRN. When the user services the  $I^2C$  master event Interrupt Service Routine, if the  $I^2C$  bus is free (i.e., the P bit is set), the user can resume communication by asserting a Start condition.

If a Start, Restart, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are de-asserted, and the respective control bits in the I2CCON register are cleared to '0'. When the user services the bus collision Interrupt Service Routine, and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins, and if a Stop condition occurs, the MI2CIF bit will be set.

A write to the I2CTRN will start the transmission of data at the first data bit regardless of where the transmitter left off when bus collision occurred.

In a multi-master environment, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$ bus can be taken when the P bit is set in the I2CSTAT register, or the bus is Idle and the S and P bits are cleared.

## 14.13 I<sup>2</sup>C Module Operation During CPU Sleep and Idle Modes

#### 14.13.1 I<sup>2</sup>C OPERATION DURING CPU SLEEP MODE

When the device enters Sleep mode, all clock sources to the module are shut down and stay at logic '0'. If Sleep occurs in the middle of a transmission and the state machine is partially into a transmission as the clocks stop, then the transmission is aborted. Similarly, if Sleep occurs in the middle of a reception, then the reception is aborted.

#### 14.13.2 I<sup>2</sup>C OPERATION DURING CPU IDLE MODE

For the I<sup>2</sup>C, the I2CSIDL bit selects if the module will stop on Idle or continue on Idle. If I2CSIDL = 0, the module will continue operation on assertion of the Idle mode. If I2CSIDL = 1, the module will stop on Idle.

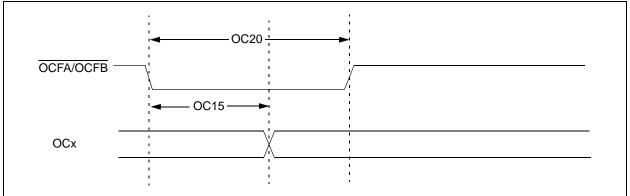

#### FIGURE 20-11: OC/PWM MODULE TIMING CHARACTERISTICS

#### TABLE 20-28: SIMPLE OC/PWM MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                  |     | Standard Operating Conditions: 2.5V to 5.5V   (unless otherwise stated) -40°C ≤TA ≤+85°C for Industrial   Operating temperature -40°C ≤TA ≤+125°C for Extended |     |       |            |  |

|--------------------|--------|----------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>    | Min | Тур <sup>(2)</sup>                                                                                                                                             | Max | Units | Conditions |  |

| OC15               | Tfd    | Fault Input to PWM I/O<br>Change | —   | _                                                                                                                                                              | 50  | ns    |            |  |

| OC20               | TFLT   | Fault Input Pulse Width          | 50  |                                                                                                                                                                |     | ns    |            |  |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

NOTES:

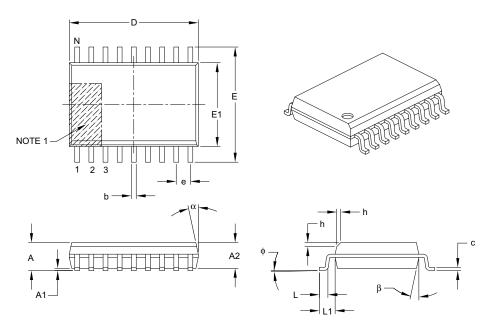

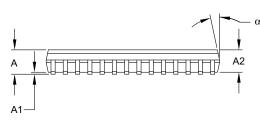

## 18-Lead Plastic Small Outline (SO) – Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units      | MILLIMETERS |           |      |  |

|--------------------------|------------|-------------|-----------|------|--|

| Dimens                   | ion Limits | MIN         | NOM       | MAX  |  |

| Number of Pins           | Ν          |             | 18        |      |  |

| Pitch                    | е          |             | 1.27 BSC  |      |  |

| Overall Height           | А          | -           | -         | 2.65 |  |

| Molded Package Thickness | A2         | 2.05        | -         | -    |  |

| Standoff §               | A1         | 0.10        | -         | 0.30 |  |

| Overall Width            | E          | 10.30 BSC   |           |      |  |

| Molded Package Width     | E1         | 7.50 BSC    |           |      |  |

| Overall Length           | D          |             | 11.55 BSC |      |  |

| Chamfer (optional)       | h          | 0.25        | -         | 0.75 |  |

| Foot Length              | L          | 0.40        | -         | 1.27 |  |

| Footprint                | L1         |             | 1.40 REF  |      |  |

| Foot Angle               | ф          | 0°          | -         | 8°   |  |

| Lead Thickness           | С          | 0.20        | -         | 0.33 |  |

| Lead Width               | b          | 0.31        | -         | 0.51 |  |

| Mold Draft Angle Top     | α          | 5°          | -         | 15°  |  |

| Mold Draft Angle Bottom  | β          | 5°          | _         | 15°  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-051B

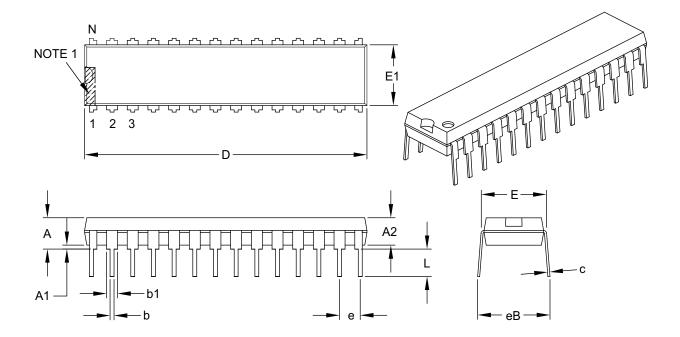

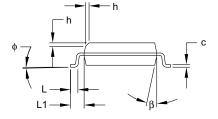

## 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    |       |          |       |

|----------------------------|----------|-------|----------|-------|

| Dimension                  | n Limits | MIN   | NOM      | MAX   |

| Number of Pins             | Ν        |       | 28       |       |

| Pitch                      | е        |       | .100 BSC |       |

| Top to Seating Plane       | Α        | -     | -        | .200  |

| Molded Package Thickness   | A2       | .120  | .135     | .150  |

| Base to Seating Plane      | A1       | .015  | -        | -     |

| Shoulder to Shoulder Width | Е        | .290  | .310     | .335  |

| Molded Package Width       | E1       | .240  | .285     | .295  |

| Overall Length             | D        | 1.345 | 1.365    | 1.400 |

| Tip to Seating Plane       | L        | .110  | .130     | .150  |

| Lead Thickness             | С        | .008  | .010     | .015  |

| Upper Lead Width           | b1       | .040  | .050     | .070  |

| Lower Lead Width           | b        | .014  | .018     | .022  |

| Overall Row Spacing §      | eВ       | -     | -        | .430  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

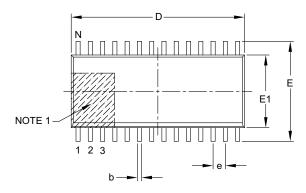

## 28-Lead Plastic Small Outline (SO) – Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS      |           |           |      |  |

|--------------------------|------------------|-----------|-----------|------|--|

| Dimension                | Dimension Limits |           |           | MAX  |  |

| Number of Pins           | Ν                |           | 28        |      |  |

| Pitch                    | е                |           | 1.27 BSC  |      |  |

| Overall Height           | Α                | —         | -         | 2.65 |  |

| Molded Package Thickness | A2               | 2.05      | -         | -    |  |

| Standoff §               | A1               | 0.10      | -         | 0.30 |  |

| Overall Width            | Е                | 10.30 BSC |           |      |  |

| Molded Package Width     | E1               | 7.50 BSC  |           |      |  |

| Overall Length           | D                |           | 17.90 BSC |      |  |

| Chamfer (optional)       | h                | 0.25      | -         | 0.75 |  |

| Foot Length              | L                | 0.40      | -         | 1.27 |  |

| Footprint                | L1               |           | 1.40 REF  |      |  |

| Foot Angle Top           | φ                | 0°        | -         | 8°   |  |

| Lead Thickness           | с                | 0.18      | -         | 0.33 |  |

| Lead Width               | b                | 0.31      | -         | 0.51 |  |

| Mold Draft Angle Top     | α                | 5°        | -         | 15°  |  |

| Mold Draft Angle Bottom  | β                | 5°        | -         | 15°  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-052B

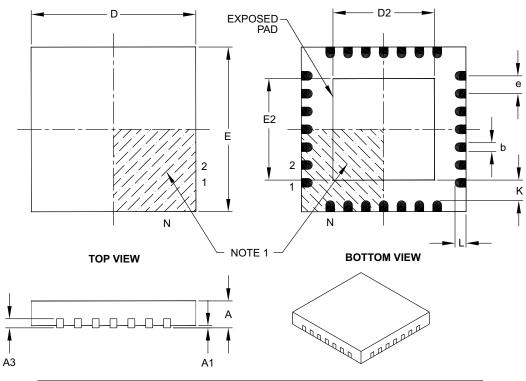

## 28-Lead Plastic Quad Flat, No Lead Package (MM) – 6x6x0.9 mm Body [QFN-S] with 0.40 mm Contact Length

## **Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units    | MILLIMETERS |          |      |

|------------------------|----------|-------------|----------|------|

| Dimension              | n Limits | MIN         | NOM      | MAX  |

| Number of Pins         | Ν        |             | 28       |      |

| Pitch                  | е        |             | 0.65 BSC |      |

| Overall Height         | А        | 0.80        | 0.90     | 1.00 |

| Standoff               | A1       | 0.00        | 0.02     | 0.05 |

| Contact Thickness      | A3       | 0.20 REF    |          |      |

| Overall Width          | Е        |             | 6.00 BSC |      |

| Exposed Pad Width      | E2       | 3.65        | 3.70     | 4.70 |

| Overall Length         | D        |             | 6.00 BSC |      |

| Exposed Pad Length     | D2       | 3.65        | 3.70     | 4.70 |

| Contact Width          | b        | 0.23        | 0.38     | 0.43 |

| Contact Length         | L        | 0.30        | 0.40     | 0.50 |

| Contact-to-Exposed Pad | К        | 0.20        | -        | -    |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-124B